- **Programmable Settling Time to 0.5 LSB 2.5**  $\mu$ s or 12.5  $\mu$ s Typ

- Two 12-Bit CMOS Voltage Output DACs in an 8-Pin Package

- Simultaneous Updates for DAC A and

- **Single Supply Operation**

- 3-Wire Serial Interface

- **High-Impedance Reference Inputs**

- Voltage Output Range ... 2 Times the Reference Input Voltage

- **Software Powerdown Mode**

- **Internal Power-On Reset**

- TMS320 and SPI Compatible

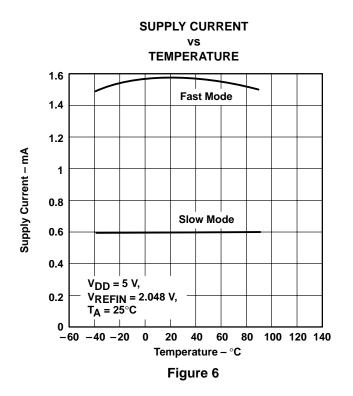

- **Low Power Consumption:**

- 3 mW Typ in Slow Mode,

- 8 mW Typ in Fast Mode

## description

The TLC5618 is a dual 12-bit voltage output digital-to-analog converter (DAC) with buffered reference inputs (high impedance). The DACs have an output voltage range that is two times the reference voltage, and the DACs are monotonic. The device is simple to use, running from a single supply of 5 V. A power-on reset function is incorporated in the device to ensure repeatable start-up conditions.

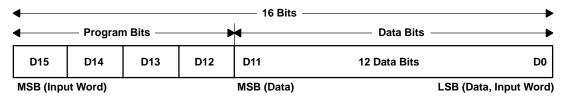

Digital control of the TLC5618 is over a 3-wire CMOS-compatible serial bus. The device receives a 16-bit word for programming and producing the analog output. The digital inputs feature Schmitt triggers for high noise immunity. Digital communication protocols include the SPI™, QSPI™, and Microwire™ standards.

Two versions of the device are available. The TLC5618 does not have an internal state machine

- Input Data Update Rate of 1.21 MHz

- **Monotonic Over Temperature**

- **Available in Q-Temp Automotive HighRel Automotive Applications Configuration Control/Print Support Qualification to Automotive Standards**

# applications

- **Battery Powered Test Instruments**

- **Digital Offset and Gain Adjustment**

- **Battery Operated/Remote Industrial** Controls

- **Machine and Motion Control Devices**

- **Cellular Telephones**

and is dependent on all external timing signals. The TLC5618A has an internal state machine that counts the number of clocks from the falling edge of CS and then updates and disables the device from accepting further data inputs. The TLC5618A is recommended for TMS320 and SPI processors, and the TLC5618 is recommended only for SPI or 3-wire serial port processors. The TLC5618A is backward-compatible and designed to work in TLC5618 designed systems.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI and QSPI are trademarks of Motorola, Inc. Microwire is a trademark of National Semiconductor Corporation.

SLAS156G - JULY 1997 - REVISED APRIL 2001

# description (continued)

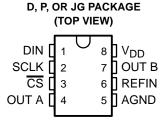

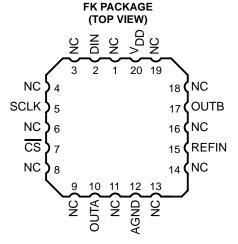

The 8-terminal small-outline D package allows digital control of analog functions in space-critical applications. The TLC5618C is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. The TLC5618I is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C. The TLC5618Q is characterized for operation from  $-40^{\circ}$ C to  $125^{\circ}$ C. The TLC5618M is characterized for operation from  $-55^{\circ}$ C to  $125^{\circ}$ C.

#### **AVAILABLE OPTIONS**

|                | PACKAGE                 |                                             |             |             |  |  |  |  |  |  |  |

|----------------|-------------------------|---------------------------------------------|-------------|-------------|--|--|--|--|--|--|--|

| TA             | SMALL OUTLINE†<br>(D)   | PLASTIC DIP CERAMIC DIP 20 PA<br>(P) (JG) ( |             |             |  |  |  |  |  |  |  |

| 0°C to 70°C    | TLC5618CD<br>TLC5618ACD | TLC5618CP<br>TLC5618ACP                     |             |             |  |  |  |  |  |  |  |

| -40°C to 85°C  | TLC5618ID<br>TLC5618AID | TLC5618IP<br>TLC5618AIP                     |             | _<br>_      |  |  |  |  |  |  |  |

| -40°C to 125°C | TLC5618AQD              | _                                           | _           | _           |  |  |  |  |  |  |  |

| −55°C to 125°C | _                       | _                                           | TLC5618AMJG | TLC5618AMFK |  |  |  |  |  |  |  |

<sup>&</sup>lt;sup>†</sup> The D package is available in tape and reel by adding R to the part number (e.g., TLC5618CDR)

| DEVICE   | COMPATIBILITY                       |

|----------|-------------------------------------|

| TLC5618  | SPI, QSPI and Microwire             |

| TLC5618A | TMS320Cxx, SPI, QSPI, and Microwire |

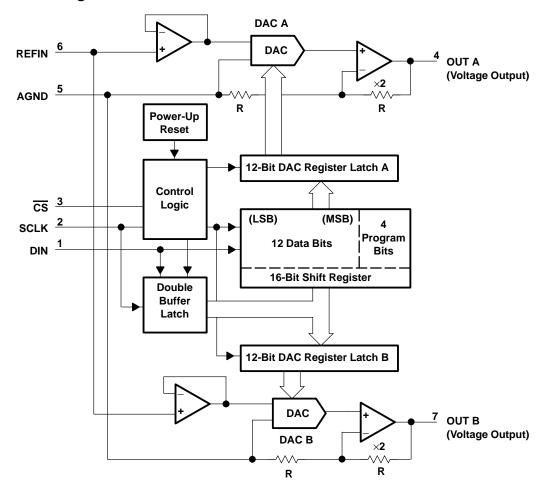

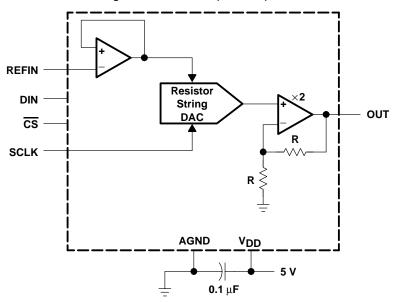

# functional block diagram

# **Terminal Functions**

| TERMIN   | NAL | 1/0 | DESCRIPTION             |

|----------|-----|-----|-------------------------|

| NAME     | NO. | 20  | DESCRIPTION             |

| AGND     | 5   |     | Analog ground           |

| CS       | 3   | 1   | Chip select, active low |

| DIN      | 1   | ı   | Serial data input       |

| OUT A    | 4   | 0   | DAC A analog output     |

| OUT B    | 7   | 0   | DAC B analog output     |

| REFIN    | 6   | -   | Reference voltage input |

| SCLK     | 2   | I   | Serial clock input      |

| $V_{DD}$ | 8   |     | Positive power supply   |

SLAS156G - JULY 1997 - REVISED APRIL 2001

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage (V <sub>DD</sub> to AGND)                                   | 7 V                                        |

|----------------------------------------------------------------------------|--------------------------------------------|

| Digital input voltage range to AGND                                        | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Reference input voltage range to AGND                                      | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Output voltage at OUT from external source                                 | $V_{DD} + 0.3 V$                           |

| Continuous current at any terminal                                         | ±20 mA                                     |

| Operating free-air temperature range, T <sub>A</sub> : TLC5618C, TLC5618AC | 0°C to 70°C                                |

| TLC5618I, TLC5618AI                                                        | –40°C to 85°C                              |

| TLC5618AQ                                                                  | –40°C to 125°C                             |

| TLC5618AM                                                                  | 55°C to 125°C                              |

| Storage temperature range, T <sub>stg</sub>                                | 65°C to 150°C                              |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds               |                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C <sup>‡</sup> | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|-------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| D       | 635 mW                                | 5.08 mW/°C                                                  | 407 mW                                | 330 mW                                | _                                      |

| FK      | 1375 mW                               | 11.00 mW/°C                                                 | 880 mW                                | 715 mW                                | 275 mW                                 |

| JG      | 1050 mW                               | 8.40 mW/°C                                                  | 672 mW                                | 546 mW                                | 210 mW                                 |

| Р       | 1202 mW                               | 9.61 mW/°C                                                  | 769 mW                                | 625 mW                                | _                                      |

This is the inverse of the traditional junction-to-ambient thermal resistance (ROJA). Thermal resistances are not production tested and are for informational purposes only.

# recommended operating conditions

|                                                       |                       | MIN   | NOM   | MAX                  | UNIT |

|-------------------------------------------------------|-----------------------|-------|-------|----------------------|------|

| Supply voltage, V <sub>DD</sub>                       |                       | 4.5   | 5 5   | 5.5                  | V    |

| High-level digital input voltage, VIH                 | V <sub>DD</sub> = 5 V | 0.7 V | OD    |                      | V    |

| Low-level digital input voltage, V <sub>IL</sub>      | V <sub>DD</sub> = 5 V |       |       | 0.3V <sub>DD</sub>   | V    |

| Reference voltage, V <sub>ref</sub> to REFIN terminal |                       | 2     | 2.048 | V <sub>DD</sub> −1.1 | V    |

| Load resistance, R <sub>L</sub>                       |                       | 2     |       |                      | kΩ   |

|                                                       | TLC5618C, TLC5618AC   | (     | )     | 70                   |      |

| Operating free air temperature Te                     | TLC5618I, TLC5618AI   | -40   | )     | 85                   | °C   |

| Operating free-air temperature, T <sub>A</sub>        | TLC5618AQ             | -40   | )     | 125                  |      |

|                                                       | TLC5618AM             | -55   | ;     | 125                  | ]    |

SLAS156G - JULY 1997 - REVISED APRIL 2001

electrical characteristics over recommended operating free-air temperature range,  $V_{DD}$  = 5 V  $\pm$  5%,  $V_{ref(REFIN)}$  = 2.048 V (unless otherwise noted)

## static DAC specifications

|      | PARAMETER                             |             | TEST COND                          | ITIONS           | MIN | TYP  | MAX   | UNIT    |

|------|---------------------------------------|-------------|------------------------------------|------------------|-----|------|-------|---------|

|      | Resolution                            |             |                                    |                  | 12  |      |       | bits    |

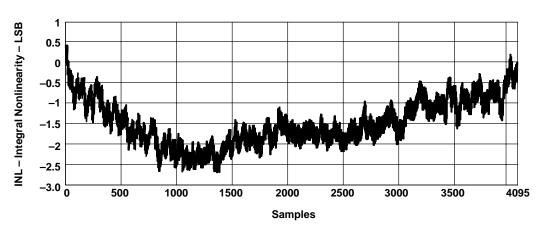

|      | Integral nonlinearity (INL), end poir | nt adjusted | V <sub>ref(REFIN)</sub> = 2.048 V, | See Note 1       |     |      | ±4    | LSB     |

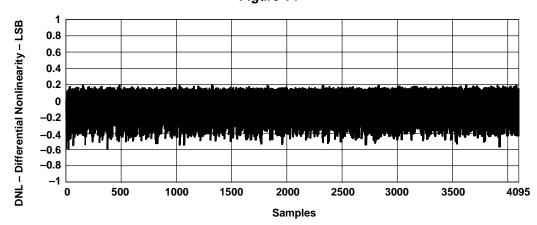

|      | Differential nonlinearity (DNL)       |             | V <sub>ref(REFIN)</sub> = 2.048 V, | See Note 2       |     | ±0.5 | ± 1   | LSB     |

| EZS  | Zero-scale error (offset error at zer | o scale)    | V <sub>ref(REFIN)</sub> = 2.048 V, | See Note 3       |     |      | ±12   | mV      |

|      | Zero-scale-error temperature coeff    |             |                                    | See Note 4       |     | 3    |       | ppm/°C  |

| F    | 0 :                                   |             | V <sub>ref(REFIN)</sub> = 2.048 V, | C and I suffixes |     |      | ±0.29 | % of FS |

| EG   | Gain error                            |             | See Note 5                         | Q and M suffixes |     |      | ±0.60 | voltage |

|      | Gain error temperature coefficient    |             | V <sub>ref(REFIN)</sub> = 2.048 V, | See Note 6       |     | 1    |       | ppm/°C  |

|      |                                       | Zero scale  |                                    | Olavia           |     | 65   |       |         |

| Denn | Dower cumply rejection ratio          | Gain        | Con Noton 7 and 0                  | Slow             |     | 65   |       | dD      |

| PSRR | Power-supply rejection ratio Zero     | Zero scale  | See Notes 7 and 8                  | Fast             |     | 65   |       | dB      |

|      | Gain                                  |             | 1                                  | rasi             |     | 65   |       |         |

- NOTES: 1. The relative accuracy or integral nonlinearity (INL) sometimes referred to as linearity error, is the maximum deviation of the output from the line between zero and full scale excluding the effects of zero code and full-scale errors.

- 2. The differential nonlinearity (DNL) sometimes referred to as differential error, is the difference between the measured and ideal 1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains constant) as a change in the digital input code.

- 3. Zero-scale error is the deviation from zero voltage output when the digital input code is zero.

- 4. Zero-scale-error temperature coefficient is given by:  $E_{ZS}TC = [E_{ZS}(T_{max}) E_{ZS}(T_{min})]/V_{ref} \times 10^6/(T_{max} T_{min})$ .

- 5. Gain error is the deviation from the ideal output ( $V_{ref} 1$  LSB) with an output load of 10 k $\Omega$  excluding the effects of the zero-error.

- 6. Gain temperature coefficient is given by:  $E_G TC = [E_G(T_{max}) E_G(T_{min})]/V_{ref} \times 10^6/(T_{max} T_{min})$ .

- 7. Zero-scale-error rejection ratio (EZS-RR) is measured by varying the V<sub>DD</sub> from 4.5 V to 5.5 V dc and measuring the proportion of this signal imposed on the zero-code output voltage.

- 8. Gain-error rejection ratio (EG-RR) is measured by varying the V<sub>DD</sub> from 4.5 V to 5.5 V dc and measuring the proportion of this signal imposed on the full-scale output voltage after subtracting the zero scale change.

#### **OUT A and OUT B output specifications**

|                        | PARAMETER                                       | TEST CONDIT                              | MIN                   | TYP | MAX | UNIT                 |                 |

|------------------------|-------------------------------------------------|------------------------------------------|-----------------------|-----|-----|----------------------|-----------------|

| VO                     | Voltage output range $R_L = 10 \text{ k}\Omega$ |                                          |                       | 0   |     | V <sub>DD</sub> -0.4 | V               |

|                        | Output load regulation accuracy                 | $V_{O(OUT)} = 4.096 V,$                  | R <sub>L</sub> = 2 kΩ |     |     | ±0.29                | % of FS voltage |

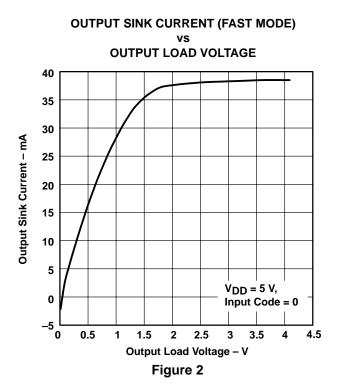

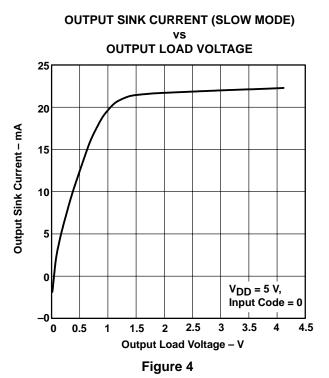

| loog(:,)               | Output short circuit sink current               | $V_{O(A OUT)} = V_{DD}$                  | Fast                  |     | 38  |                      | mA              |

| IOSC(sink)             | Output short circuit sink current               | VO(B OUT) = VDD,<br>Input code zero      | Slow                  |     | 23  |                      | IIIA            |

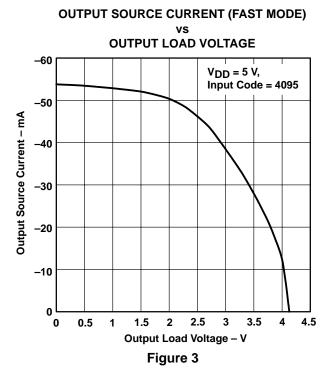

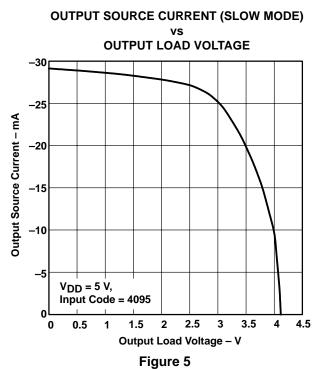

| loog( )                | Output about since it accounts                  | VO(A OUT) = 0 V,                         | Fast                  |     | -54 |                      | mA              |

| IOSC(source)           | Output short circuit source current             | VO(B OUT) = 0 V,<br>Full-scale code Slow |                       |     | -29 |                      | IIIA            |

| I <sub>O(sink)</sub>   | Output sink current                             | V <sub>O(OUT)</sub> = 0.25 V             |                       |     | 5   |                      | mA              |

| I <sub>O(source)</sub> | Output source current                           | V <sub>O(OUT)</sub> = 4.2 V              |                       |     | 5   | ·                    | mA              |

SLAS156G - JULY 1997 - REVISED APRIL 2001

electrical characteristics over recommended operating free-air temperature range,  $V_{DD}$  = 5 V  $\pm$  5%,  $V_{ref(REFIN)}$  = 2.048 V (unless otherwise noted) (continued)

#### reference input (REFIN)

|    | PARAMETER                            | TEST CONDITIONS                                         |       | MIN | TYP | MAX                | UNIT   |  |

|----|--------------------------------------|---------------------------------------------------------|-------|-----|-----|--------------------|--------|--|

| ٧ı | Input voltage range                  |                                                         |       | 0   |     | V <sub>DD</sub> -2 | V      |  |

| Ri | Input resistance                     |                                                         |       |     | 10  |                    | ΜΩ     |  |

| Ci | Input capacitance                    |                                                         |       |     |     |                    | pF     |  |

|    | Reference feedthrough                | REFIN = 1 V <sub>pp</sub> at 1 kHz + 1.024 V dc (see No | te 9) |     | -60 |                    | dB     |  |

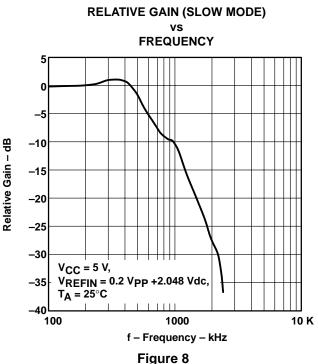

|    | Deference input handwidth (f 2 dD)   | DEEIN 0.2.V + 4.024.V do                                | Slow  |     | 0.5 |                    | N.41.1 |  |

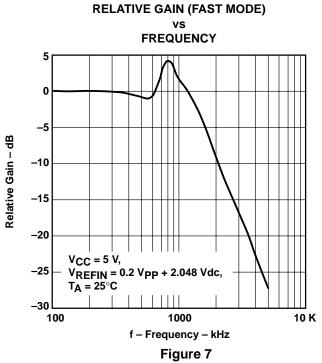

| Re | Reference input bandwidth (f – 3 dB) | REFIN = 0.2 V <sub>pp</sub> + 1.024 V dc Fast           |       |     | 1   |                    | MHz    |  |

NOTE 9: Reference feedthrough is measured at the DAC output with an input code = 000 hex and a V<sub>ref(REFIN)</sub> input = 1.024 V dc + 1 V<sub>pp</sub> at 1 kHz.

# digital inputs (DIN, SCLK, CS)

|                 | PARAMETER                        | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------|----------------------|-----|-----|-----|------|

| Ι <sub>ΙΗ</sub> | High-level digital input current | $V_I = V_{DD}$       |     |     | ±1  | μΑ   |

| IIL             | Low-level digital input current  | V <sub>I</sub> = 0 V |     |     | ±1  | μΑ   |

| Ci              | Input capacitance                |                      |     | 8   |     | pF   |

#### power supply

|     | PARAMETER TEST CONDITIONS |                                          |      | MIN | TYP | MAX | UNIT |

|-----|---------------------------|------------------------------------------|------|-----|-----|-----|------|

|     | Dower cumply current      | V <sub>DD</sub> = 5.5 V,<br>No load.     | Slow |     | 0.6 | 1   | mA   |

| IDD | Power supply current      | All inputs = 0 V or V <sub>DD</sub>      | Fast |     | 1.6 | 2.5 | IIIA |

|     | Power down supply current | own supply current D13 = 0 (see Table 2) |      |     | 1   |     | μΑ   |

operating characteristics over recommended operating free-air temperature range,  $V_{DD}$  = 5 V  $\pm$  5%,  $V_{ref(REFIN)}$  = 2.048 V (unless otherwise noted)

#### analog output dynamic performance

|                | PARAMETER                    | TEST                                                                                  | TEST CONDITIONS                                                                                            |      |      | TYP  | MAX | UNIT |

|----------------|------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-----|------|

| SR+            | C <sub>L</sub> = 100 pF,     |                                                                                       | $V_{ref(REFIN)} = 2.048 \text{ V},$ $T_{\Delta} = 25^{\circ}\text{C},$                                     | Slow | 0.3  | 0.5  |     | V/μs |

| SK+            | Output siew rate, positive   | at slew rate, positive $R_L = 10 \text{ k}\Omega$ , $Code 32 \text{ to Code } 4096$ , |                                                                                                            | Fast | 2.4  | 3    |     | V/μS |

| SR-            | Output slew rate, negative   | C <sub>L</sub> = 100 pF,                                                              | V <sub>ref</sub> (REFIN) = 2.048 V,<br>T <sub>A</sub> = 25°C,                                              | Slow | 0.15 | 0.25 |     | V/μs |

| SK-            | Output siew rate, negative   | $R_L$ = 10 kΩ,<br>Code 4096 to Code 32,                                               | V <sub>O</sub> from 10% to 90%                                                                             | Fast | 1.2  | 1.5  |     | ν/μ5 |

| +              | Output cottling time         | To ±0.5 LSB,                                                                          | C <sub>L</sub> = 100 pF,                                                                                   | Slow |      | 12.5 |     |      |

| t <sub>S</sub> | Output settling time         | $R_L = 10 \text{ k}\Omega$ ,                                                          | See Note 10                                                                                                | Fast |      | 2.5  |     | μs   |

|                | Output settling time,        | To ±0.5 LSB,                                                                          | C <sub>L</sub> = 100 pF,                                                                                   | Slow |      | 2    |     |      |

| ts(c)          | code-to-code                 | $R_L = 10 \text{ k}\Omega$ ,                                                          | See Note 11                                                                                                | Fast |      | 2    |     | μs   |

|                | Glitch energy                | DIN = All 0s to all 1s,<br>f(SCLK) = 100 kHz                                          | $\overline{\text{CS}} = V_{\text{DD}},$                                                                    |      |      | 5    |     | nV-s |

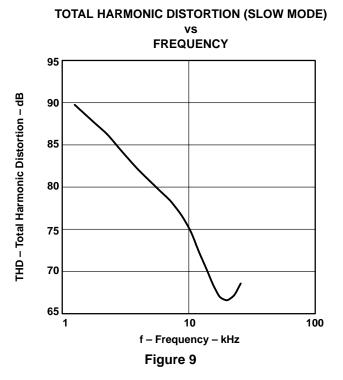

| S/(N+D)        | Signal to noise + distortion | V <sub>ref</sub> (REFIN) = 1 V <sub>pp</sub> at<br>Input code = 10 0000 00            | V <sub>ref(REFIN)</sub> = 1 V <sub>pp</sub> at 1 kHz and 10 kHz + 1.024 V dc,<br>Input_code = 10 0000 0000 |      |      | 78   |     | dB   |

NOTES: 10. Settling time is the time for the output signal to remain within  $\pm 0.5$  LSB of the final measured value for a digital input code change of 020 hex to 3FF hex or 3FF hex to 020 hex.

<sup>11.</sup> Settling time is the time for the output signal to remain within  $\pm 0.5$  LSB of the final measured value for a digital input code change of one count.

operating characteristics over recommended operating free-air temperature range,  $V_{DD}$  = 5 V ± 5%,  $V_{ref(REFIN)}$  = 2.048 V (unless otherwise noted) (continued)

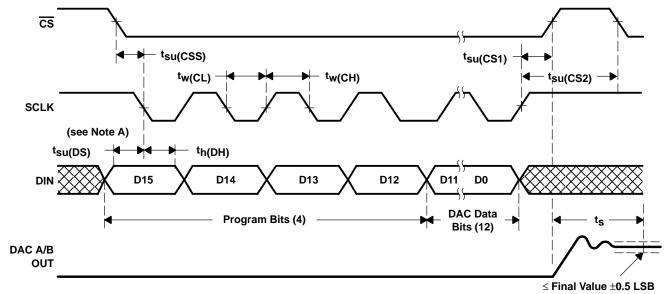

# digital input timing requirements

|                      |                                                                                             |                  | MIN | NOM | MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| t <sub>su(DS)</sub>  | Setup time, DIN before SCLK low                                                             | C and I suffixes | 5   |     |     | ns   |

|                      | Setup time, but before SCLK low                                                             | Q and M suffixes | 8   |     |     | 115  |

| t <sub>h(DH)</sub>   | DH) Hold time, DIN valid after SCLK low                                                     |                  |     |     |     | ns   |

| t <sub>su(CSS)</sub> | Setup time, CS low to SCLK low                                                              | 5                |     |     | ns  |      |

| t <sub>su(CS1)</sub> | Setup time, SCLK $\uparrow$ to $\overline{\text{CS}}$ $\uparrow$ , external end-of-write    | 10               |     |     | ns  |      |

| t <sub>su(CS2)</sub> | Setup time, SCLK $\uparrow$ to $\overline{\text{CS}}\downarrow$ , start of next write cycle | 5†               |     |     | ns  |      |

| tw(CL)               | Pulse duration, SCLK low                                                                    | 25               |     |     | ns  |      |

| tw(CH)               | Pulse duration, SCLK high                                                                   | 25               |     |     | ns  |      |

<sup>†</sup> Not production tested for Q and M suffixes.

NOTE A: SCLK must go high after the 16th falling clock edge.

Figure 1. Timing Diagram for the TLC5618A

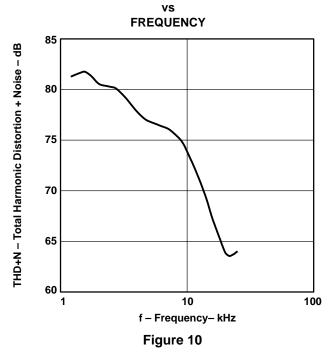

# TOTAL HARMONIC DISTORTION + NOISE (SLOW MODE)

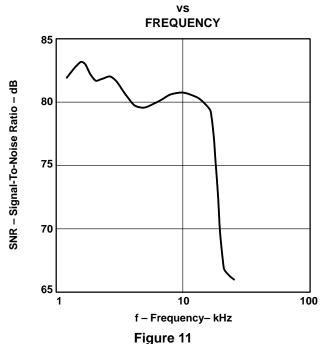

# SIGNAL-TO-NOISE RATIO (SLOW MODE)

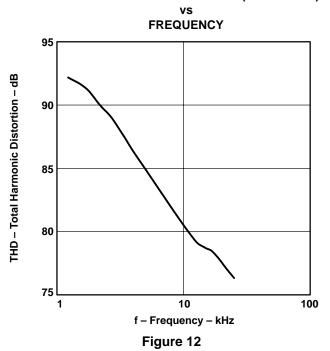

# **TOTAL HARMONIC DISTORTION (FAST MODE)**

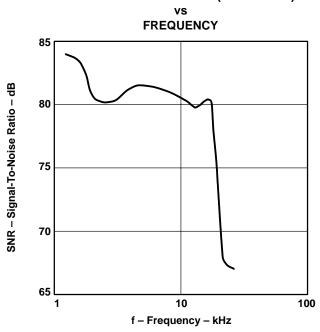

#### TOTAL HARMONIC DISTORTION + NOISE (FAST MODE)

# SIGNAL-TO-NOISE RATIO (FAST MODE)

Figure 14

Figure 15. Differential Nonlinearity With Input Code

Figure 16. Integral Nonlinearity With Input Code

#### **APPLICATION INFORMATION**

# general function

The TLC5618 uses a resistor string network buffered with an op amp to convert 12-bit digital data to analog voltage levels (see functional block diagram and Figure 17). The output is the same polarity as the reference input (see Table 1).

The output code is given by:  $2(V_{REFIN})\frac{CODE}{4096}$

An internal circuit resets the DAC register to all 0s on power up.

Figure 17. TLC5618 Typical Circuit

#### **APPLICATION INFORMATION**

Table 1. Binary Code Table (0 V to 2 V<sub>REFIN</sub> Output) Gain = 2

|      | INPUT |      | OUTPUT                                      |

|------|-------|------|---------------------------------------------|

| 1111 | 1111  | 1111 | $2(V_{REFIN})\frac{4095}{4096}$             |

|      | :     |      | :                                           |

| 1000 | 0000  | 0001 | $2(V_{REFIN})\frac{2049}{4096}$             |

| 1000 | 0000  | 0000 | $2(V_{REFIN})\frac{2048}{4096} = V_{REFIN}$ |

| 0111 | 1111  | 1111 | $2(V_{REFIN})\frac{2047}{4096}$             |

|      | :     |      | :                                           |

| 0000 | 0000  | 0001 | $2(V_{REFIN})\frac{1}{4096}$                |

| 0000 | 0000  | 0000 | 0 V                                         |

# buffer amplifier

The output buffer has a rail-to-rail output with short circuit protection and can drive a  $2-k\Omega$  load with a 100-pF load capacitance. Settling time is a software selectable  $12.5 \,\mu s$  or  $2.5 \,\mu s$ , typical to within  $\pm 0.5 \,LSB$  of final value.

#### external reference

The reference voltage input is buffered, which makes the DAC input resistance not code dependent. Therefore, the REFIN input resistance is 10  $M\Omega$  and the REFIN input capacitance is typically 5 pF, independent of input code. The reference voltage determines the DAC full-scale output.

# logic interface

The logic inputs function with CMOS logic levels. Most of the standard high-speed CMOS logic families may be used.

#### serial clock and update rate

Figure 1 shows the TLC5618 timing. The maximum serial clock rate is:

$$f_{(SCLK)max} \ = \ \frac{1}{t_{W(CH)min} \ ^{+} \ t_{W(CL)min}} \ = \ 20 \ MHz$$

The digital update rate is limited by the chip-select period, which is:

$$t_{p(CS)} = 16 \times \left(t_{w(CH)} + t_{w(CL)}\right) + t_{su(CS1)}$$

This equals an 810-ns or 1.23-MHz update rate. However, the DAC settling time to 12 bits limits the update rate for full-scale input step transitions.

#### **APPLICATION INFORMATION**

#### serial interface

When chip select  $(\overline{CS})$  is low, the input data is read into a 16-bit shift register with the input data clocked in, most significant bit first. The falling edge of the SCLK input shifts the data into the input register.

The rising edge of  $\overline{CS}$  then transfers the data to the DAC register. When  $\overline{CS}$  is high, input data cannot be clocked into the input register.

The 16 bits of data can be transferred with the sequence shown in Figure 18.

Figure 18. Input Data Word Format

Table 2 shows the function of program bits D15 – D12.

Table 2. Program Bits D15 - D12 Function

| PROGRAM BITS |     |     |                                                                                                 | DEVICE FUNCTION                            |  |

|--------------|-----|-----|-------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| D15          | D14 | D13 | D12                                                                                             | DEVICE FUNCTION                            |  |

| 1            | Х   | Х   | X Write to latch A with serial interface register of and latch B updated with buffer latch data |                                            |  |

| 0            | Х   | Х   | 0                                                                                               | 0 Write to latch B and double buffer latch |  |

| 0            | Х   | Х   | 1                                                                                               | Write to double buffer latch only          |  |

| Х            | 0   | Х   | Х                                                                                               | 12.5 μs settling time                      |  |

| Х            | 1   | Х   | Х                                                                                               | 2.5 μs settling time                       |  |

| Х            | Х   | 0   | Х                                                                                               | Powered-up operation                       |  |

| Х            | Х   | 1   | Х                                                                                               | Power down mode                            |  |

# function of the latch control bits (D15 and D12)

Three data transfers are possible. All transfers occur immediately after  $\overline{\text{CS}}$  goes high and are described in the following sections.

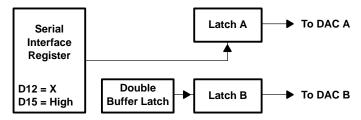

#### latch A write, latch B update (D15 = high, D12 = X)

The serial interface register (SIR) data are written to latch A and the double buffer latch contents are written to latch B. The double buffer contents are unaffected. This program bit condition allows simultaneous output updates of both DACs.

Figure 19. Latch A Write, Latch B Update

#### **APPLICATION INFORMATION**

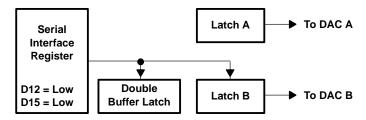

#### latch B and double-buffer 1 write (D15 = low, D12 = low)

The SIR data are written to both latch B and the double buffer. Latch A is unaffected.

Figure 20. Latch B and Double-Buffer Write

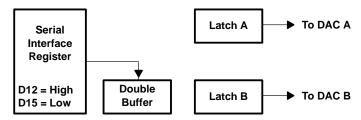

#### double-buffer-only write (D15 = low, D12 = high)

The SIR data are written to the double buffer only. Latch A and B contents are unaffected.

Figure 21. Double-Buffer-Only Write

#### purpose and use of the double buffer

Normally only one DAC output can change after a write. The double buffer allows both DAC outputs to change after a single write. This is achieved by the two following steps.

- 1. A double-buffer-only write is executed to store the new DAC B data without changing the DAC A and B outputs.

- 2. Following the previous step, a write to latch A is executed. This writes the SIR data to latch A and also writes the double-buffer contents to latch B. Thus both DACs receive their new data at the same time, and so both DAC outputs begin to change at the same time.

Unless a double-buffer-only write is issued, the latch B and double-buffer contents are identical. Thus, following a write to latch A or B with another write to latch A does not change the latch B contents.

#### operational examples

## changing the latch A data from zero to full code

Assuming that latch A starts at zero code (e.g., after power up), the latch can be filled with 1s by writing (bit D15 on the left, D0 on the right)

1X0X 1111 1111 1111

to the serial interface. Bit D14 can be zero to select slow mode or one to select fast mode. The other X can be zero or one (don't care).

The latch B contents and the DAC B output are not changed by this write unless the double-buffer contents are different from the latch B contents. This can only be true if the last write was a double-buffer-only write.

#### APPLICATION INFORMATION

#### changing the latch B data from zero to full code

Assuming that latch B starts at zero code (e.g., after power-up), the latch can be filled with 1s by writing (bit D15 on the left, D0 on the right).

0X00 1111 1111 1111

to the serial interface. Bit D14 can be zero to select slow mode or one to select fast mode. The data (bits D0 to D11) are written to both the double buffer and latch B.

The latch A contents and the DAC A output are not changed by this write.

#### double-buffered change of both DAC outputs

Assuming that DACs A and B start at zero code (e.g., after power-up), if DAC A is to be driven to mid-scale and DAC B to full-scale, and if the outputs are to begin rising at the same time, this can be achieved as follows:

First,

0d01 1111 1111 1111

is written (bit D15 on the left, D0 on the right) to the serial interface. This loads the full-scale code into the double buffer but does not change the latch B contents and the DAC B output voltage. The latch A contents and the DAC A output are also unaffected by this write operation.

Changing from fast to slow or slow to fast mode changes the supply current which can glitch the outputs, and so D14 (designated by d in the above data word) should be set to maintain the speed mode set by the previous write.

Next,

1X0X 1000 0000 0000

is written (bit D15 on the left, D0 on the right) to the serial interface. Bit D14 can be zero to select slow mode or one to select fast mode. The other X can be zero or one (don't care). This writes the mid-scale code (100000000000) to latch A and also copies the full-scale code from the double buffer to latch B. Both DAC outputs thus begin to rise after the second write.

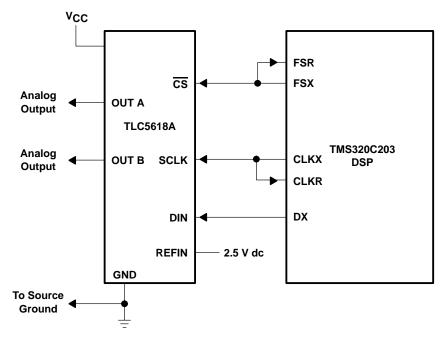

#### **DSP** serial interface

Utilizing a simple 3-wire serial interface shown in Figure 22, the TLC5618A can be interfaced to TMS320 compatible serial ports. The 5618A has an internal state machine that will count 16 clocks after receiving a falling edge of  $\overline{CS}$  and then disable further clocking in of data until the next falling edge is received on  $\overline{CS}$ . Therefore  $\overline{CS}$  can be connected directly to the FS pins of the serial port and only the leading falling edge of the DSP will be used to start the write process. The TLC5618A is designed to be used with the TMS320Cxx DSP in burst mode serial port transmit operation.

#### **APPLICATION INFORMATION**

Figure 22. Interfacing The TLC5618A to the TMS320C203 DSP

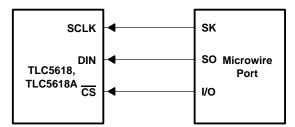

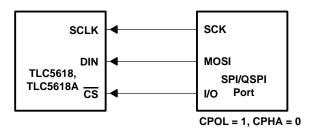

#### general serial interface

Both the TLC5618 and TLC5618A are compatible with SPI, QSPI, or Microwire serial standards. The hardware connections are shown in Figures 23 and 24. The TLC5618A has an internal state machine that will count 16 clocks after the falling edge of  $\overline{CS}$  and then internally disable the device. The internal edge is ORed together with  $\overline{CS}$  so that the rising edge can be provided to  $\overline{CS}$  prior to the occurrence of the internal edge to also disable the device.

The SPI and Microwire interfaces transfer data in 8-bit bytes, therefore, two write cycles are required to input data to the DAC. The QSPI interface, which has a variable input data length from 8 to 16 bits, can load the DAC input register in one write cycle.

Figure 23. Microwire Connection

#### **APPLICATION INFORMATION**

Figure 24. SPI/QSPI Connection

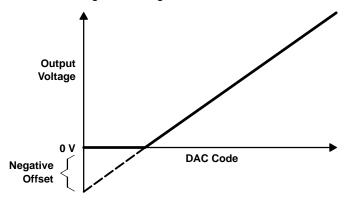

#### linearity, offset, and gain error using single end supplies

When an amplifier is operated from a single supply, the voltage offset can still be either positive or negative. With a positive offset, the output voltage changes on the first code change. With a negative offset the output voltage may not change with the first code depending on the magnitude of the offset voltage.

The output amplifier attempts to drive the output to a negative voltage. However, because the most negative supply rail is ground, the output cannot drive below ground and clamps the output at 0 V.

The output voltage then remains at zero until the input code value produces a sufficient positive output voltage to overcome the negative offset voltage, resulting in the transfer function shown in Figure 25.

Figure 25. Effect of Negative Offset (Single Supply)

This offset error, not the linearity error, produces this breakpoint. The transfer function would have followed the dotted line if the output buffer could drive below the ground rail.

For a DAC, linearity is measured between zero-input code (all inputs 0) and full-scale code (all inputs 1) after offset and full scale are adjusted out or accounted for in some way. However, single supply operation does not allow for adjustment when the offset is negative due to the breakpoint in the transfer function. So the linearity is measured between full-scale code and the lowest code that produces a positive output voltage. The code is calculated from the maximum specification for the negative offset.

#### **APPLICATION INFORMATION**

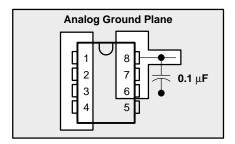

#### power-supply bypassing and ground management

Printed-circuit boards that use separate analog and digital ground planes offer the best system performance. Wire-wrap boards do not perform well and should not be used. The two ground planes should be connected together at the low-impedance power-supply source. The best ground connection may be achieved by connecting the DAC AGND terminal to the system analog ground plane making sure that analog ground currents are well-managed.

A 0.1- $\mu$ F ceramic bypass capacitor should be connected between  $V_{DD}$  and AGND and mounted with short leads as close as possible to the device. Use of ferrite beads may further isolate the system analog and digital power supplies.

Figure 26 shows the ground plane layout and bypassing technique.

Figure 26. Power-Supply Bypassing

# saving power

Setting the DAC register to all 0s minimizes power consumption by the reference resistor array and the output load when the system is not using the DAC.

# ac considerations/analog feedthrough

Higher frequency analog input signals may couple to the output through internal stray capacitance. Analog feedthrough is tested by holding  $\overline{CS}$  high, setting the DAC code to all 0s, sweeping the frequency applied to REFIN, and monitoring the DAC output.

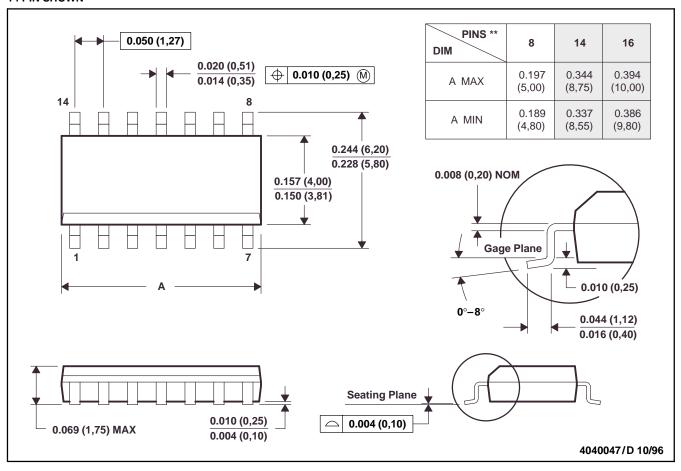

#### **MECHANICAL DATA**

# D (R-PDSO-G\*\*)

# 14 PIN SHOWN

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012

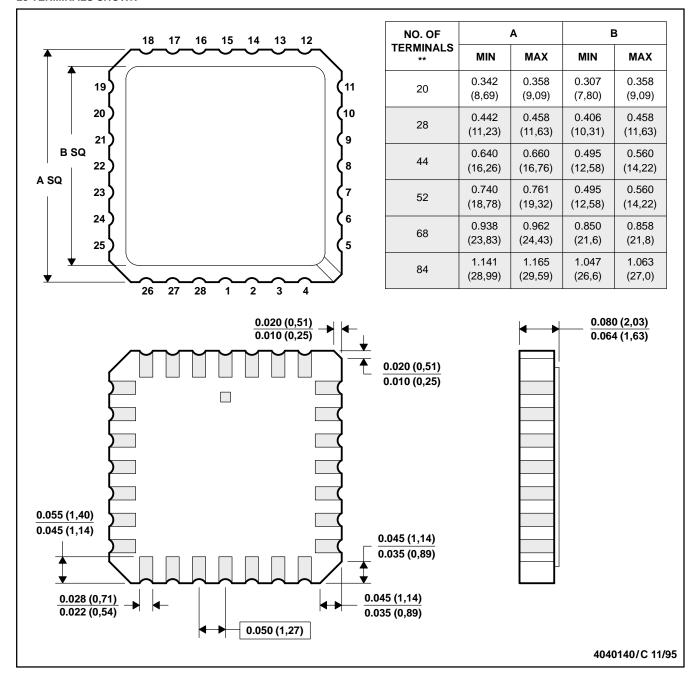

#### **MECHANICAL DATA**

# FK (S-CQCC-N\*\*)

#### **28 TERMINALS SHOWN**

#### LEADLESS CERAMIC CHIP CARRIER

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. The terminals are gold-plated.

- E. Falls within JEDEC MS-004

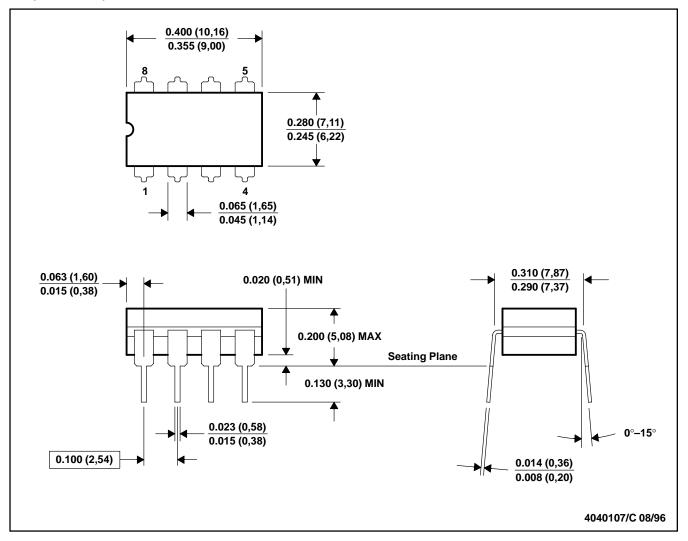

#### **MECHANICAL DATA**

# JG (R-GDIP-T8)

#### **CERAMIC DUAL-IN-LINE**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification.

- E. Falls within MIL STD 1835 GDIP1-T8

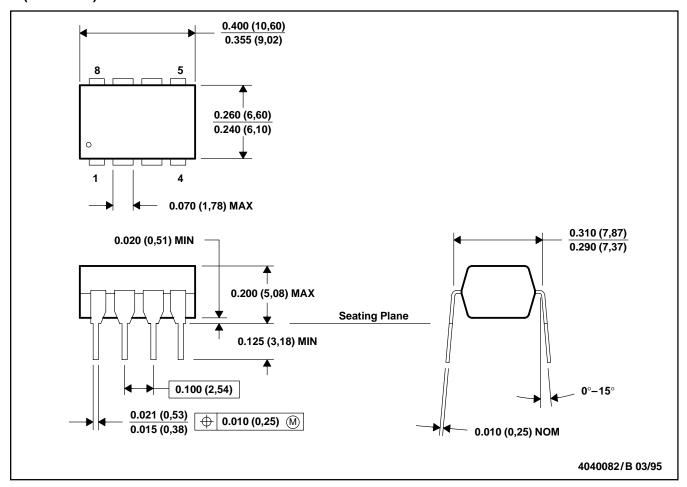

#### **MECHANICAL DATA**

# P (R-PDIP-T8)

# PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products, www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265