#### CMOS 4-BIT MICROCONTROLLER

# TMP47C1238AN, TMP47C1638AN

The 47C1238A/1638A are based on the TLCS-470A series. The 47C1238A/1638A have on-screen display circuit (OSD) to display characters and marks which indicate channel or time on TV screen, A/D converter (Comparator) input, D/A converter output such as TV.

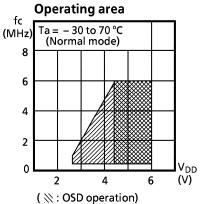

| PART No.     | ROM           | RAM         | PACKAGE           | OTP             |

|--------------|---------------|-------------|-------------------|-----------------|

| TMP47C1238AN | 12288 x 8-bit | 512 × 4-bit | SDIP54-P-600-1.78 | TMP47P1638VN    |

| TMP47C1638AN | 16384 × 8-bit | 312 X 4-DIL | 3D1F34-F-000-1.76 | 11VIP4/P1036VIV |

#### **FEATURES**

- ◆4-bit single chip microcomputer

- $\blacklozenge$ Instruction execution time : 1.3  $\mu$ s (at 6 MHz), 244  $\mu$ s (at 32.8 kHz)

- ◆105 basic instructions

- ◆Subroutine nesting: 15 levels max.

- ◆6 interrupt sources (External : 2, Internal : 4)

All sources have independent latches each, and multiple interrupt control is available

- ◆I/O port (41 pins)

- Input 3 ports 7 pins

I/O 7 ports 26 pins

Output 2 ports 8 pins

- **◆**Two 12-bit Timer/Counters

- ♦Interval Timer

- **♦**Watchdog Timer

- ◆Serial Interface with 8-bit buffer

- ◆On-screen display circuit

- Character patterns: 128 Characters

Characters displayed: 20 columns × 4 lines

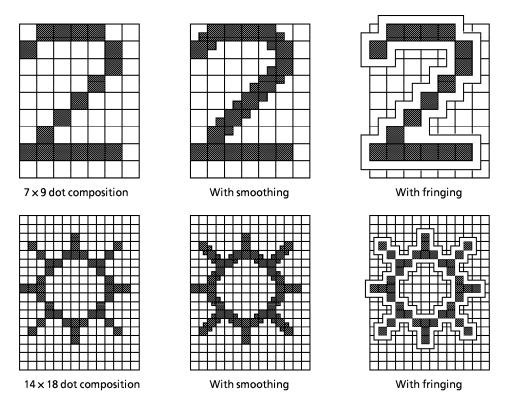

- Composition:

14 × 18 dots (80 Characters)

7 × 9 dots (48 Characters)

- Size of character: 3 kinds (line by line)

- Color of character: 7 kinds (character by character)

Variable display position: Horizontal / Vertical 128 steps

- Fringing, Smoothing function

- ◆D/A converter (Pulse width modulation) outputs

- 14-bit resolution 1 channel

- 7-bit resolution 9 channels

- ◆4-bit A/D converter (Comparator) input (4 Channels)

- ◆Horizontal synchronous signal is detected by timer/counter

- ◆Pulse output (Clock for PLL IC)

- ◆Remote control pulse detector

- ♦ High current outputs: LED direct drive (typ. 20 mA × 8 bits)

- ◆Dual-clock operation

- High-speed/low-power consumption operating mode

- ◆Hold function: Battery/Capacitor back-up ◆Real Time Emulator: BM47C1638N0A

## **PIN ASSIGNMENT (TOP VIEW)**

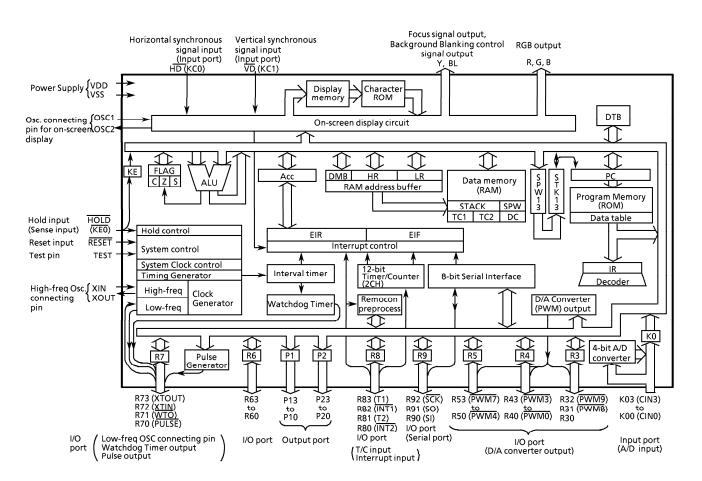

#### **BLOCK DIAGRAM**

# **TOSHIBA**

# **PIN FUNCTION**

| PIN NAME                                  | Input/Output  | FUNC                                                                                  | CTIONS                                                              |  |  |  |  |  |  |

|-------------------------------------------|---------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|--|

| K03 (CIN3) to<br>K00 (CIN0)               | Input         | 4-bit input port.                                                                     | A/D conversion (Comparator) input                                   |  |  |  |  |  |  |

| P13 to P10                                |               | 4-bit output port with latch.                                                         |                                                                     |  |  |  |  |  |  |

| P23 to P20                                | Output        | 8-bit data are output by the 5-bit to 8-bit o                                         | data conversion instruction [OUTB @HL].                             |  |  |  |  |  |  |

| R32 (PWM9),<br>R31 (PWM8)                 | I/O (Output)  | 3-bit I/O port with latch.                                                            | 7-bit D/A converter (PWM) output                                    |  |  |  |  |  |  |

| R30                                       | I/O           | When used as input port or D/A converter                                              | outputs pins, the latch must be set to "1".                         |  |  |  |  |  |  |

| R43 (PWM3) to<br>R41 (PWM1)<br>R40 (PWM0) | I/O (Output)  | 4-bit I/O port with latch.  When used as input port or D/A                            | 7-bit D/A converter (PWM) output  14-bit D/A converter (PWM) output |  |  |  |  |  |  |

| R53 (PWM7) to<br>R50 (PWM4)               | I/O (Output)  | converter outputs pins, the latch must be set to "1".                                 | 7-bit D/A converter (PWM) output                                    |  |  |  |  |  |  |

| R63 to R60                                | 1/0           | 4-bit I/O port with latch. When used as input port, the latch must b                  | · · · · · · · · · · · · · · · · · · ·                               |  |  |  |  |  |  |

| R73 (XTOUT)                               | I/O (Output)  |                                                                                       |                                                                     |  |  |  |  |  |  |

| R72 (XTIN)                                | I/O (Input)   | 4-bit I/O port with latch.  When used as input port watchdog                          | Resonator connecting pin (Low frequency)                            |  |  |  |  |  |  |

| R71 (WTO)                                 |               | output pin, or pulse output pin, the latch must be set to "1".                        | Watchdog timer output                                               |  |  |  |  |  |  |

| R70 (PULSE)                               | I/O (Output)  |                                                                                       | Pulse output (Clock for PLL IC)                                     |  |  |  |  |  |  |

| R83 (T1)                                  |               | 4-bit I/O port with latch.                                                            | Timer/Counter 1 external input                                      |  |  |  |  |  |  |

| R82 ( <del>INT1</del> )                   |               | When used as input port, external                                                     | External interrupt 1 input                                          |  |  |  |  |  |  |

| R81 (T2)                                  | I/O (Input)   | interrupt input pin, or timer/counter external input pin, the latch must be set       | Timer/Counter 2 external input                                      |  |  |  |  |  |  |

| R80 ( <del>INT2</del> )                   |               | to "1".                                                                               | External interrupt 2 or REMO-CON input                              |  |  |  |  |  |  |

| R92 ( <del>SCK</del> )                    | I/O (I/O)     | 3-bit I/O port with latch.                                                            | Serial clock I/O                                                    |  |  |  |  |  |  |

| R91 (SO)                                  | I/O (Output)  | When used as input port or serial port,                                               | Serial data output                                                  |  |  |  |  |  |  |

| R90 (SI)                                  | I/O (Input)   | the latch must be set to "1".                                                         | Serial data input                                                   |  |  |  |  |  |  |

| R, G, B                                   | Output        | RGB output                                                                            |                                                                     |  |  |  |  |  |  |

| Y<br>BL                                   | Output        | Focus signal output  Background blanking control signal outpu                         | ıt                                                                  |  |  |  |  |  |  |

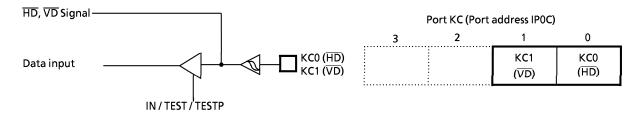

| HD (KC0)<br>VD (KC1)                      | Input         | Horizontal synchronous signal input.  Vertical synchronous signal input.              | 2-bit input port                                                    |  |  |  |  |  |  |

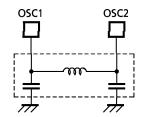

| OSC1, OSC2                                | Input, Output | Resonator connecting pin of on-screen dis                                             |                                                                     |  |  |  |  |  |  |

| XIN, XOUT                                 | Input, Output | Resonator connecting pin (High frequency For inputting external clock, XIN is used as | y).<br>nd XOUT is opened.                                           |  |  |  |  |  |  |

| RESET                                     | Input         | Reset signal input                                                                    |                                                                     |  |  |  |  |  |  |

| HOLD (KEO)                                | Input (Input) | Hold request/release signal input                                                     | Sense input                                                         |  |  |  |  |  |  |

| TEST                                      | Input         | Test pin for out-going test. Be opened or                                             | fixed to low level.                                                 |  |  |  |  |  |  |

| VDD                                       |               | +5 V                                                                                  |                                                                     |  |  |  |  |  |  |

| VSS                                       | Power Supply  | 0 V (GND)                                                                             |                                                                     |  |  |  |  |  |  |

#### **OPERATIONAL DESCRIPTION**

Concerning the 47C1238A/1638A the configuration and functions of hardware are described. As the description has been provided with priority on those parts differing from the 47C1260/1660, the technical data sheets for the 47C1260/1660 shall all so be referred to.

#### 1. SYSTEM CONFIGURATION

**♦** INTERNAL CPU FUNCTION

They are the same as those of the 47C1260/1660 except data memory (RAM).

#### **♦** PERIPHERAL HARDWARE FUNCTION

- ① Input/Output Ports

- 2 Interval Timer

- ③ Timer/Counters (TC1, TC2)

- Watchdog Timer

- 5 Remote control pulse detector

- 6 On-screen display (OSD) control circuit

- A/D converter (Comparator) input

- 8 D/A converter (Pulse width modulation) output

- 9 Pulse output circuit

- **10** Serial Interface

The description has been provide with priority on functions (①, ⑤, ⑦,  $\otimes$  and  $\otimes$ ) added to and changed from 47C1260/1660.

#### 2. INTERNAL CPU FUNCTIONS

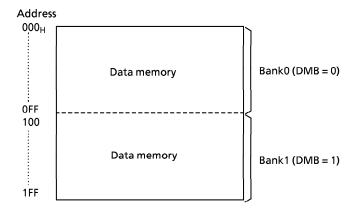

#### 2.1 Data Memory (RAM)

The 47C1238A / 1638A have two built-in 256 × 4-bit banks (bank 0, bank 1) for a total of 512 × 4-bit data memory (RAM). The data memory bank selector (DMB) consists of 2 bits but DMB1 is not decoded when addressing the data memory. For example, when DMB is set to 2 or 3, bank 0 or 1 in data memory is accessed.

Figure 2-2. Data Memory (RAM)

TOSHIBA TMP47C1238AN/1638AN

#### 3. PERIPHERAL HARDWARE FUNCTION

## 3.1 Input / Output Ports

The 47C1238A / 1638A have 12 I/O ports (32 pins) each as follows:

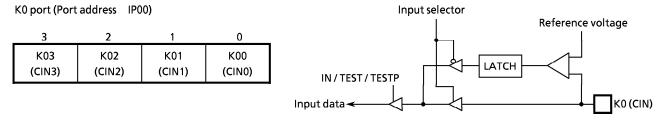

① K0 ; 4-bit input (shared with the comparator input)

2 P1, P2; 4-bit output

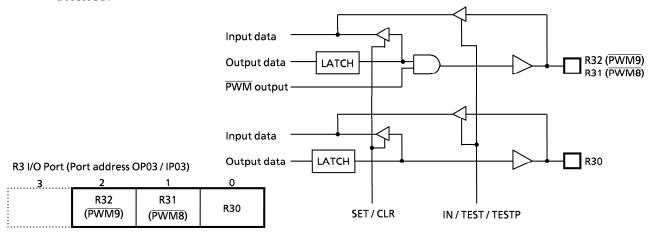

R3 ; 3-bit input / output (shared with the pulse width modulation output)

R4, R5 ; 4-bit input / output (shared with the pulse width modulation output)

⑤ R6 ; 4-bit input / output

© R7; 4-bit input / output (shared with the low-frequency resonator connection pins,

the watchdog timer output, the pulse output)

⑦ R8 ; 4-bit input / output (shared with the external interrupt input and timer/counter

input)

8 R9 ; 3-bit input / output (shared with serial port)

input)

(shared with the hold request / release signal input)

The description has been provide with priority on functions (①, ③, ④, ⑥ and ⑨) added to and changed from 47C1260/1660.

Table 3-1 lists the ports address assignments and the I/O instruction that can access the ports.

#### 3.1.1 I/O Port

## (1) Port K0 (K03 to K00)

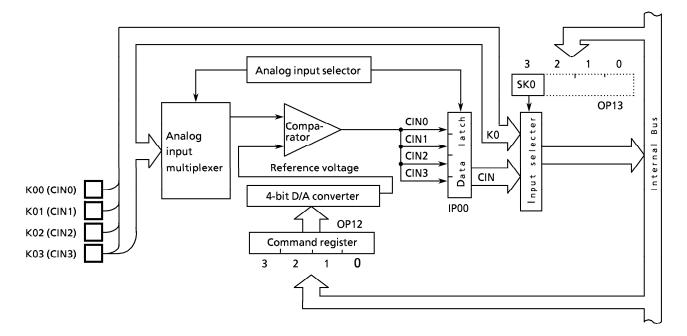

The 4-bit input port. Port K0 is shared digital input with the A/D converter (comparator) input. The K0 port input selector (OP13) determines whether this port is to be used for digital or comparator input. The most significant bit of the K0 port input selector is set to "1" for digital input and to "0" for comparator input.

The K0 port input selector is initialized to "0" during reset.

Figure 3-1. Port K0

#### (2) Port R3 (R32 to R30)

This is a 3-bit input / output port with latch. Pins R32, R31 are also used for D/A converter (pulse width modulation) output. When this port is used for input, the latch should be set to "1". When R32, R31 are used for input, the PWM output should be also set to "H" level (all PWM data latches should be set to "0"). When using for PWM output, set the output latch to "1"; when using for R3 output, set the PWM output to "H" level. The output port latch is initialized to "1" and the PWM output level to "H" during reset. Also, there is no R33 port but "1" is read out when this bit is accessed.

Figure 3-2. Port R3

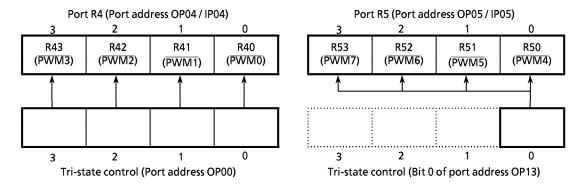

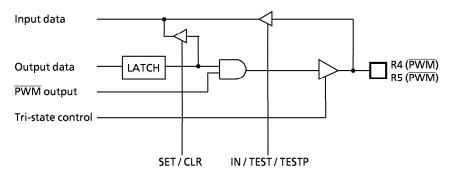

#### (3) Port R4 (R43-R40), Port R5 (R53-R50)

These are 4-bit I/O port with latch. They are also used for D/A converter (PWM) output port. R4 port output buffers are Tri-state, and each bit of them can be controlled independently by the program. R5 port is also Tri-state port and they are controlled by the program. Controlling the Tri-state is performed by the command register accessed as port address OP00 and OP13. When some bit of the command register data is 0, the corresponding bit of the output buffers becomes high impedance state. The output latch should be set to "1" when the port is used as PWM output port, the PWM output should be to "H" level (PWM data is all "0") when the port is used as R4 and R5 port. The output buffers should be set to high impedance state, when the port is used as input port. And the output latch be set to "1", PWM output be set to "High" level, and the output buffer be set to High-Impedance state during reset.

Figure 3-3. Port R4 (PWM), R5 (PWM) (1/2)

Figure 3-3. Port R4 (PWM), R5 (PWM) (2/2)

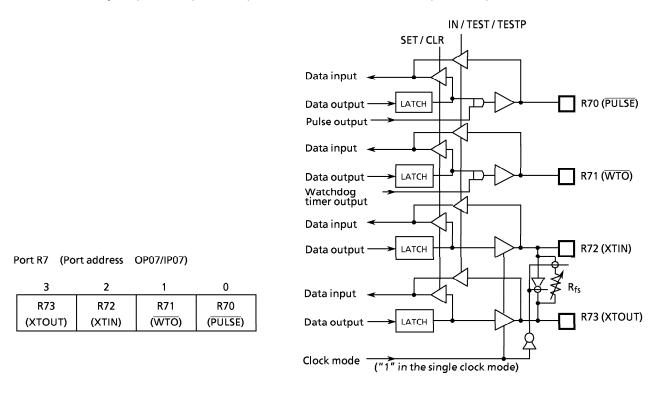

## (4) Port R7 (R73 to R70)

Port R7 is shared by the low-frequency resonator connection pins (XTIN, XTOUT), pulse output pin (PULSE) and the watchdog timer output pin (WTO). For the dual-clock mode operation, the low-frequency resonator (32.768 kHz), is connected to R72 (XTIN) and R73 (XTOUT) pins. For the single-clock mode operation, R72 and R73 pins are used for the ordinary I/O ports. When the watchdog timer is used, R71 (WTO) becomes the watchdog timer output pin.

The watchdog timer output is the logical AND output with the port R71 output latch. To use the R71 pin for an ordinary I/O port, the watchdog timer must be disabled (with the watchdog timer output set to "1"). When the pulse output is used, R70 (PULSE) becomes the pulse output pin. The pulse output is the logical AND output with the port R70 output latch. To use the R70 pin for an ordinary I/O port, the pulse output must be disabled (with the pulse output set to "1").

Figure 3-4. Port R7

## (5) Port KC (KC1, KC0)

This is 2-bit input port. These port is also used as an input for vertical synchronous signal (VD), horizontal synchronous signal (HD). There are not bit 2, 3 of IPOC, however, "1" is read out when IPOC is accessed.

Figure 3-5. Port KC

|                 | b SET @L<br>CLR @L<br>b TEST @L | 1 1                                          | ı               | ı              | 0              | 0              | 0              | 0              | I              | ı              | 1          | ı          | 1                      | ı                     | ı                     |                            | 1                      | 1                   | ı  | ı                           | 1                          | ı  | ı                      | ı                    | ı                    | ı                        | ı                                | ı                    | ı                    | 1                       | ı                       | ı  | _    |

|-----------------|---------------------------------|----------------------------------------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------|------------|------------------------|-----------------------|-----------------------|----------------------------|------------------------|---------------------|----|-----------------------------|----------------------------|----|------------------------|----------------------|----------------------|--------------------------|----------------------------------|----------------------|----------------------|-------------------------|-------------------------|----|------|

|                 | TEST %p,<br>TESTP %p,           | 00                                           | 0               | 0              | 0              | 0              | 0              | 0              | <u> </u>       | 0              | ı          | ı          | 0                      | ı                     | С                     | )                          | l                      | I                   | ı  | ı                           | 1                          | Į  | ı                      | I                    | I                    | I                        | I                                | I                    | I                    | I                       | ı                       | I  |      |

|                 | SET %p, b<br>CLR %p, b          | 10                                           | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | ı          | ı          | ı                      | ı                     | ı                     |                            | ı                      | ı                   | ı  | ı                           | ı                          | ı  | ı                      | ı                    | ı                    | ı                        | ı                                | ı                    | ı                    | ı                       | ı                       | ı  |      |

| I/O instruction | OUTB @HL                        |                                              | (Note 3)        | ı              | I              | ı              | ı              | l              | ı              | ı              | ļ          | ı          | ı                      | ı                     | I                     |                            | 1                      | I                   | ı  | ı                           | ı                          | ı  | ı                      | ı                    | ı                    | ı                        | ı                                | ı                    | ı                    | ı                       | I                       | ı  |      |

|                 | OUT #k, %p                      | 00                                           | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | ı          | ı          | 0                      | <u> </u>              | С                     | )                          | 0                      | I                   | ı  | ı                           | ı                          | ı  | ı                      | ı                    | ı                    | ı                        | ı                                | ı                    | ı                    | ı                       | ı                       | ı  |      |

|                 | OUT A, %p<br>OUT @HL,%p         | 00                                           | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | ı          | ı          | 0(                     | Э<br>                 | С                     | )                          | 0                      | 0                   | ı  | 0                           | 0                          | ı  | 0                      | 0                    | 0                    | 0                        | 0                                | 0                    | 0                    | 0                       | 0                       | 0  | (    |

|                 | IN %p, A<br>IN %p, @HL          | 00                                           | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | ı          | ı          | 0                      | )                     | С                     | )                          | 0                      | 0                   | ı  | ı                           | 0                          | I  | I                      | I                    | 0                    | I                        | I                                | 0                    | I                    | I                       | ı                       | ı  |      |

| Port            | Output (OP**)                   | Tri-state(R4 port) Control<br>P1 output port | P2 output port  | R3 output port | R4 output port | R5 output port | R6 output port | R7 output port | R8 output port | R9 output port | 1          |            | OSD command selector   | REMO-CON offset value | Remote control signal | preprocess circuit control | Serial transmit buffer | Hold operation mode |    | A/D converter input control | Tri-state, DTB, comparator |    | Watchdog timer control | System clock control | PWM buffer selector  | PWM data transfer buffer | Interval timer interrupt control | OSD control          | Pulse output control | Timer/Counter 1 control | Timer/Counter 2 control |    | C. 1 |

| <u> </u>        | Input (IP**)                    | K0 input port<br>P1 output latch             | P2 output latch | R3 input port  | R4 input port  | R5 input port  | R6 input port  | R7 input port  | R8 input port  | R9 input port  |            | -          | KC (HD, VD) input port | REMO-CON count value  | Status input (Note 2) |                            | Serial receive buffer  | HOLD Pin Status     |    | -                           | SK0, DTB, Status           | -  | -                      |                      | Status input for PWM | -                        | -                                | Display line counter | -                    | -                       | 1                       | -  |      |

| Port            | Address<br>(**)                 | 00 <sub>H</sub>                              | 02              | 03             | 40             | 05             | 90             | 20             | <b>8</b> 0     | 60             | <b>V</b> 0 | 0 <b>B</b> | ე :                    | 9                     | 30                    |                            | 0F                     | 10 <sub>H</sub>     | 11 | 12                          | 13                         | 14 | 15                     | 16                   | 17                   | 18                       | 19                               | 14                   | 18                   | 10                      | 10                      | 16 | L    |

Note 1. "——" means the reserved state. Unavailable for the user programs. Note 2 . The status input of serial interface, clock generator, and  $\overline{\text{HOLD}}$  (KE0) pin. Note 3 . The 5-bit to 8-bit data conversion instruction [OUTB @HL], automatic access to ports P1 and P2.

Table 3-1. Port Address Assignments and Available I/O Instructions

#### 3.2 On-Screen Display (OSD) Circuit

A built-in on-screen display circuit enables TV on-screen displays of characters and symbols. Any 80 of a total of 128 character patterns can be displayed in 20 columns x 4 lines. It is possible to display more than 5 lines by using the OSD interrupt.

## 3.2.1 OSD Circuit Functions and Configuration

① Number of character patterns 128

2 Number of display characters 80 (20 columns × 4 lines), more than 5 lines can be

displayed by using the OSD interrupt.

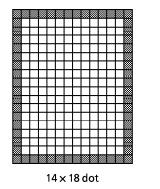

3 Composition of a character  $14 \times 18$  dots (80 characters),  $7 \times 9$  dots (48 characters)

4 Character size 3 sizes (selectable line by line)

**5** Display colors Characters: 7 colors (selectable character by character),

background color: 1 of 7 colors.

6 Fringing and smoothing function

7 Display position: horizontal: 128 steps; vertical: 128 steps

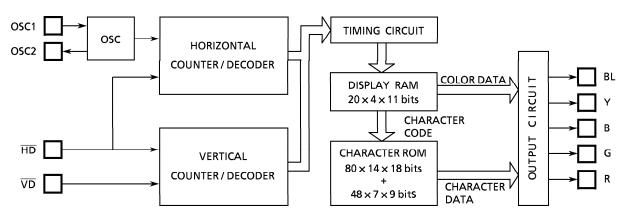

Figure 3-6. OSD Circuit

#### 3.2.2 OSD Display Related Memory

#### (1) Character ROM

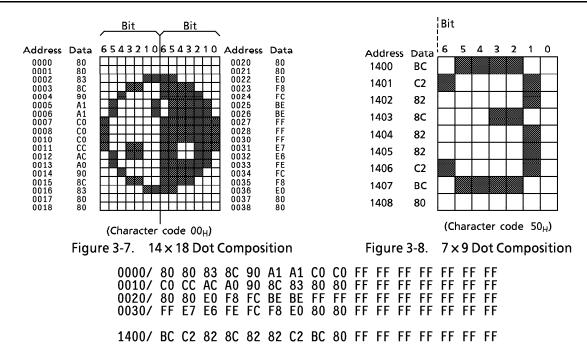

A total of 128 character patterns are built into the character ROM and the patterns can be freely designated by the user. The character ROM contains 80 characters with a 14 x 18 dot composition (character code 00<sub>H</sub> to 4F<sub>H</sub>) and 48 characters with a 7×9 dot composition (character code 50<sub>H</sub> to 7F<sub>H</sub>). Each dot corresponds to 1 bit of ROM. "1" turns on the dot and "0" turns off the dot.

The start address of character ROM can be calculated using the following expression.

For character code  $00_H$  to  $4F_H$ : Character ROM start address = CRA  $\times$  64

For character code  $50_H$  to  $7F_H$ : Character ROM start address =  $5120 + (CRA - 80) \times 16$

Note. CRA: Character code

As the character whose character code is 7E<sub>H</sub> is fixed as a background and the character whose character code is 7FH is fixed as a blank data, these two characters can not be designated by the user. Figure 3-7 shows the  $14 \times 18$  dot composition character (Character code  $00_{\rm H}$ ) and Figure 3-8 shows the 7  $\times$  9 dot composition character (Character code 50<sub>H</sub>), as an example. These figures also show the ROM address and the data of those patterns.

Figure 3-9 shows the ROM dump list for these 2 character patterns. When the ROM data is being submitted for manufacturing engineering samples, the address of character ROM should be placed to 4000<sub>H</sub> to 56F8<sub>H</sub>.

Figure 3-9. Character ROM Dump List

Note. "FF" data have to be written in address "\*\*\*9<sub>H</sub>" to "\*\*\*F<sub>H</sub>" of character data area. And "1" data have to be written in bit "7" of character data area.

## (2) Display memory

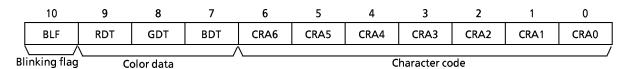

The display memory has a 20-columns  $\times$  11-bit  $\times$  4 lines configuration with a one-to-one correspondence to the number of columns displayed on the screen. The character code, the color data and blinking flag for the display characters and symbols are stored to the display memory. When power on is performed, the contents of display memory becomes unpredictable.

There are two methods for writing data to the display memory. In the first method, the character code, color data and blinking flag are written at the same time. In the second method, only the color data and blinking flag are changed. The method for writing display data to the display memory is described in 3.2.3 (6).

Figure 3-10. Bit Configuration of Display Memory

| Column | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1      | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | ОВ | 0C | 0D | 0E | 0F | 10 | 11 | 12 | 13 |

| 2      | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 2A | 2B | 2C | 2D | 2E | 2F | 30 | 31 | 32 | 33 |

| 3      | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 | 51 | 52 | 53 |

| 4      | 60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 | 68 | 69 | 6A | 6B | 6C | 6D | 6E | 6F | 70 | 71 | 72 | 73 |

Note. The numerals in the chart indicate display memory address (HEX).

Table 3-2. Display Memory Configuration

#### 3.2.3 OSD Circuit Control

The OSD circuit is controlled by the command selector (OP0C) and control register (OP1A). Table 3-3 shows the relationship between OP0C and OP1A. The command selector selects the OSD control register. Writing data to the control register of all bits is performed by accessing OP1A two times. However, the second access is not required unless the second data are changed.

The OSD control register has a 28-word configuration and sets the display start position, display character ornamentation, display memory address and character codes.

After setting all control registers are completed and the command selector is set to  $F_H$ , display is enabled and the display starts. When the command selector is set to  $E_H$ , display is disabled.

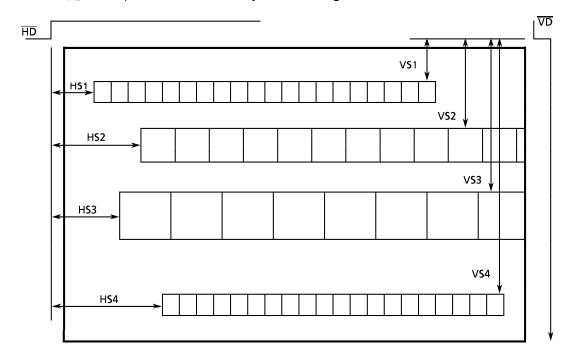

#### (1) Display start position

Display start position of each display line on screen can be set in 128 steps both horizontally and vertically. The horizontal start position of the first line is set with OSD control register HS16 to HS10 while the vertical start position is set with VS16 to VS10. The display start positions of the 2nd to 4th lines are determined by setting HS26 to HS40 and VS26 to VS40 in the same way.

A double scan mode in which each vertical scan line is counted twice is provided to enable use with PAL and double scan mode TVs. It is possible to set the vertical display start position all over the screen area in this mode. Setting WSC (command selector is set to B<sub>H</sub>) of the OSD control register to "1" enables the double scan mode and setting to "0" enables the normal mode.

The display start position can be calculated in following expressions.

Horizontal display start position of line "n"

```

HSn = \{ (HSn6 \text{ to } HSn4) \times 16^{1} + (HSn3 \text{ to } HSn0) \times 16^{0} \} \times 4T_{OSC} + \alpha T_{OSC} \}

```

$\alpha$ : 14 for a small size character, 28 for a middle and 56 for a large

Tosc: The period of OSD clock oscillation

Vertical display start position of line "n"

```

When WSC = 0 VSn = \{ (VSn6 \text{ to } VSn4) \times 16^1 + (VSn3 \text{ to } VSn0) \times 16^0 \} \times 2T_{HD}

```

When WSC = 1  $VSn = \{ (VSn6 \text{ to } VSn4) \times 16^1 + (VSn3 \text{ to } VSn0) \times 16^0 \} \times 4T_{HD}$

T<sub>HD</sub>: The period of horizontal synchronous signal

Figure 3-11. TV Screen Image

| OSD Command selector | OSD control register to be                                                                                                                                               | e accessed through OP1A                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| (OP0C)               | 1 st ACCESS                                                                                                                                                              | 2 nd ACCESS                                                                                                                   |

| 0                    | Horizontal start position of 1st display line 3 2 1 0 HS13 HS12 HS11 HS10                                                                                                | 3 2 1 0<br>HS16 HS15 HS14                                                                                                     |

| 1                    | Vertical start position of 1st display line  3                                                                                                                           | 3 2 1 0<br>VS16 VS15 VS14                                                                                                     |

| 2                    | Horizontal start position of 2nd display line  3 2 1 0  HS23 HS22 HS21 HS20                                                                                              | 3 2 1 0<br>HS26 HS25 HS24                                                                                                     |

| 3                    | Vertical start position of 2nd display line  3                                                                                                                           | 3 2 1 0<br>VS26 VS25 VS24                                                                                                     |

| 4                    | Horizontal start position of 3rd display line  3 2 1 0  HS33 HS32 HS31 HS30                                                                                              | 3 2 1 0<br>HS36 HS35 HS34                                                                                                     |

| 5                    | Vertical start position of 3rd display line 3 2 1 0  VS33 VS32 VS31 VS30                                                                                                 | 3 2 1 0<br>V536 V535 V534                                                                                                     |

| 6                    | Horizontal start position of 4th display line 3 2 1 0 HS43 HS42 HS41 HS40                                                                                                | 3 2 1 0<br>HS46 HS45 HS44                                                                                                     |

| 7                    | Vertical start position of 4th display line  3 2 1 0  VS43 VS42 VS41 VS40                                                                                                | 3 2 1 0<br>VS46 VS45 VS44                                                                                                     |

| 8                    | Character size of 1st and 2nd line  3                                                                                                                                    | Smoothing, OSD outputs polarities  3 2 1 0  ESMZ BLIV YIV RGBIV                                                               |

| 9                    | Character size of 3rd and 4th line  3 2 1 0                                                                                                                              | OSD outputs tri-state control 3 2 1 0                                                                                         |

| А                    | CS41 CS40 CS31 CS30  Blinking flag, Coloring (character) 3 2 1 0                                                                                                         | Fringing, Coloring (back ground) 3 2 1 0                                                                                      |

| В                    | Blinking, Double scan mode  3 2 1 0                                                                                                                                      | OSD interrupt function  3 2 1 0                                                                                               |

| С                    | WSC BKMF SBS DSPF  Display memory address set, Display memory b 3 2 1 0                                                                                                  | 3 2 1 0                                                                                                                       |

| D                    | DMA3         DMA2         DMA1         DMA0           Character code set           3         2         1         0           CRA3         CRA2         CRA1         CRA0 | MBK         DMA6         DMA5         DMA4           3         2         1         0           CRA6         CRA5         CRA4 |

|                      | <u> </u>                                                                                                                                                                 |                                                                                                                               |

| E                    | OSD disable                                                                                                                                                              |                                                                                                                               |

Table 3-3. OSD Control Commands and Control Registers

#### (2) Display character sizes

Character size for screen display can be selected line by line from 3 sizes.

Small, middle and large character size can be set with OSD control register CS41 to CS10 (command selector is set to  $9_H$  or  $A_H$ ). It is also possible to display with mixing  $7 \times 9$  dot and  $14 \times 18$  dot composition characters. When the character size is set the same, both dot composition of characters are displayed in the same size.

| Line             | First disp | olay line | Second di | splay line | Third dis | play line | Fourth di | splay line |

|------------------|------------|-----------|-----------|------------|-----------|-----------|-----------|------------|

| Character size   | CS11       | CS10      | CS21      | CS20       | CS31      | CS30      | CS41      | CS40       |

| Small character  | 1          | 1         | 1         | 1          | 1         | 1         | 1         | 1          |

| Middle character | 1          | 0         | 1         | 0          | 1         | 0         | 1         | 0          |

| Large character  | 0          | 1         | 0         | 1          | 0         | 1         | 0         | 1          |

| Display OFF      | 0          | 0         | 0         | 0          | 0         | 0         | 0         | 0          |

Table 3-4. Designation of Character Size

| Size           |                         | Small character            | Middle character                         | Large character                          |  |  |  |

|----------------|-------------------------|----------------------------|------------------------------------------|------------------------------------------|--|--|--|

| One dot size   | 14 × 18 dot composition | 1T <sub>OSC</sub> × 1T     | HD 2T <sub>OSC</sub> × 2T <sub>HD</sub>  | 4T <sub>OSC</sub> × 4T <sub>HD</sub>     |  |  |  |

| Offic dot size | 7 × 9 dot composition   | 2 T <sub>OSC</sub> × 2 T   | HD 4T <sub>OSC</sub> × 4T <sub>HD</sub>  | 8T <sub>OSC</sub> × 8T <sub>HD</sub>     |  |  |  |

|                | Character size          | 14 T <sub>OSC</sub> × 18 T | 28 T <sub>OSC</sub> × 36 T <sub>HD</sub> | 56 T <sub>OSC</sub> × 72 T <sub>HD</sub> |  |  |  |

Note.  $T_{OSC}$ : The period of OSD clock oscillation.

$T_{HD}$ : The period of horizontal synchronous signal.

Table 3-5. Character Size

#### (3) Smoothing and fringing functions

The smoothing function makes characters look smooth. When smoothing is enabled, additional dots (1/4 size) are displayed in the middle of the place where two dots contact each other only at a corner. However, this function is not available for  $14 \times 18$  dot small character size.

Fringing displays the fringe of characters in a different color from rest of the color of the character. When fringing is enabled, a 1/2 dot width around the character periphery is displayed in a different color, as shown in Figure 3-12.

However, this function is not available for 14 x 18 dot small character size.

Smoothing is enabled by setting ESMZ (command selector is set to  $8_{\rm H}$ ) of the OSD control register to "1". Fringing is enabled by setting EFRG (command selector is set to  $A_{\rm H}$ ) of the OSD control register to "1". When smoothing and fringing are enabled at the same time, smoothing has a priority, as shown in Figure 3-13.

The color of the fringe can be set by BBDT, GBDT, RBDT (command selector is set to A<sub>H</sub>) of the OSD control register. Coloring for fringe is described in the next section.

Note) When used to fringing function, turn off dot which is placed on an edge of character area. (refer to fig. 3.14)

Figure 3-12. Example of Smoothing and Fringing Function

Figure 3-13.

Priority of Smoothing and Fringing

Note) The dot which has hatching must be turned-off.

Figure 3-14

#### (4) Display colors

One out of seven colors can be selected for each character to be displayed. Display character color is set by the color data in the display memory. The color data loaded to RDT, GDT, BDT (command selector is set to  $A_H$ ) of the OSD control register are written to the display memory at the same time as the character code is written.

The entire background for the character area ( $14 \times 18$  or  $7 \times 9$  dots) can be colored. The background color is set by RBDT, GBDT, BBDT of the OSD control register (command selector is set A<sub>H</sub>).

When the fringing is enabled, the color of fringe is set by the background color data (RBDT, GBDT, BBDT). Thus, the entire background for the character area can not be colored at that time.

TOSHIBA TMP47C1238AN/1638AN

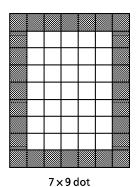

#### (5) Blinking function

Any character displayed on the screen can be caused to blink. The blinking flag (BLF) of the display memory and DSPF, SBS, BKMF (command selector is set to B<sub>H</sub>) of the OSD control register determine the blinking position and period. There are two kinds of setting blinking period; one is for the fixed period by the hardware and the other one is for the programmable period by the user.

To cause a character to blink, first set BLF of the display memory to "1".

The blinking flag BLF (command selector is set to  $A_H$ ) of the OSD control register will then be written to the display memory at the same time as the character code is written.

Next, set BKMF to "1" to enable the blinking function. When SBS is "1", the

Figure 3-15. Control of Blinking Function

character will blink at a period of fc/22. When SBS is "0", the value of DSPF itself determines whether or not the character is displayed. Thus, DSPF is alternately set and cleared with each cycle of the soft timer to produce the blinking.

#### (6) Writing display data to the display memory

Display data, which consist of the character code, color data and blinking flag, are written to the display memory which corresponds to the one to one to the displayed position. Load the display memory address to DMA6 to DMA0 of the OSD control register and load the memory bank to MBK. When all of the display data is changed, clear MBK to "0". When only the color data and blinking flag are changed, set MBK to "1".

To change all of the display data, set the display memory address and clear MBK to "0"; then set the color data and blinking flag with BLF, BDT, GDT, RDT (command selector is set to  $A_H$ ) of the OSD control register. Next, write the character code with CRA6 to CRA0 (command selector is set to  $D_H$ ) of the OSD control register. When OP1A is accessed for the second time, the character code is written to the display memory with the color data and blinking flag which are set beforehand at the same time. Display memory address DMA6 to DMA0 are also automatically incremented at this time; therefore, it is not necessary to set the display memory address again when the display data is written continuously. However, this auto-increment function is only effective within one line of the display memory. Auto-increment does not operate when the line is changed (example: display memory address  $13_H \rightarrow 20_H$ ).

When only the color data and blinking flag setting are changed, set the display memory address as above and set MBK to "1"; then set the color data and blinking flag with BLF, BDT, GDT, RDT of the OSD control register. The data are then sent to the display memory but the character code is not changed. Display memory address DMA6 to DMA0 are also automatically incremented at this time; therefore, it is not necessary to set the display memory address again when the color data and blinking flag is written continuously. However, this auto-increment function is only effective within one line of the display memory. Auto-increment does not operate when the line is changed (example: display memory address  $13_H \rightarrow 20_H$ ).

#### (7) OSD output buffer

The OSD outputs for RGB and Y/BL use tri-state output buffers, which the respective polarities can be inverted. The polarity and the tri-state is controlled by accessing EBFY-EBFB, BLIV, YIV, RGBIV (command selector is set to  $9_{\rm H}$  or  $8_{\rm H}$ ) of the OSD control register.

| Symbol | Output pin | Data "0"          | Data "1"         |

|--------|------------|-------------------|------------------|

| EBFY   | Y, BL      | Output Buffer OFF | Output Buffer ON |

| EBFB   | В          | Output Buffer OFF | Output Buffer ON |

| EBFG   | G          | Output Buffer OFF | Output Buffer ON |

| EBFR   | R          | Output Buffer OFF | Output Buffer ON |

| Symbol | Output port | Data "0"    | Data "1"   |

|--------|-------------|-------------|------------|

| BLIV   | BL          | Active High | Active Low |

| YIV    | Y           | Active High | Active Low |

| RGBIV  | RGB         | Active High | Active Low |

Table 3-7. Control of OSD Output Polarity

Table 3-6. Control of OSD Output

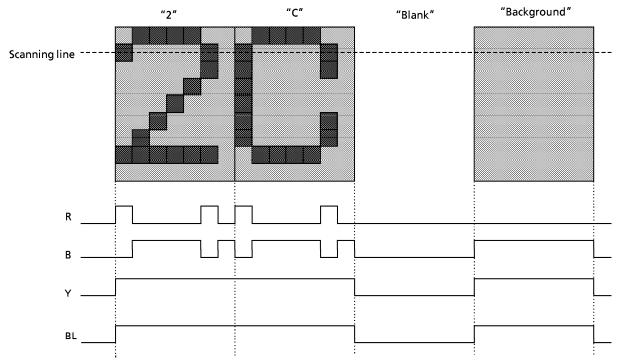

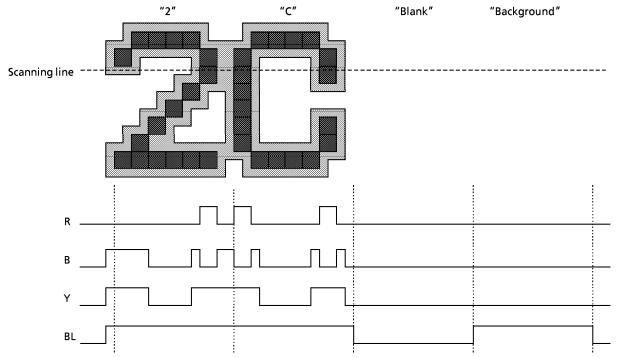

#### (8) OSD output waveform

The OSD output pins comprise the R, G and B color signal outputs, the Y signal which is the logical OR of the R, G and B signals, and the BL signals output to all display character areas (excluding character code 7E<sub>H</sub>). Y and BL signal makes the display clearer by eliminating the video signal only where characters or background are displayed.

Figure 3-16 shows display example (1). The conditions for this example are as follows:

- ① Display data: 2, C, blank data (character code 7F<sub>H</sub>), background (character code 7E<sub>H</sub>).

- $\bigcirc$  Color data: RDT = 1, BDT = 0, GDT = 0.

- ③ Background color data: BRDT = 0, BBDT = 1, BGDT = 0.

- 4 Fringing and smoothing disabled.

- ⑤ This screen display example is controlled by the R, B and BL signals.

Figure 3-17 shows display example (2). The conditions for this example are as follows:

- ① Display data: 2, C, blank data (character code 7F<sub>H</sub>), background (character code 7E<sub>H</sub>).

- $\bigcirc$  Color data: RDT = 1, BDT = 0, GDT = 0.

- 3 Background color data: BRDT = 0, BBDT = 1, BGDT = 0.

- 4 Fringing enabled and smoothing disabled.

- ⑤ This screen display example is controlled by the R, B and Y signals.

Figure 3-16. Example of OSD Display and Its Wave Form (1)

Figure 3-17. Example of OSD Display and Its Wave Form (2)

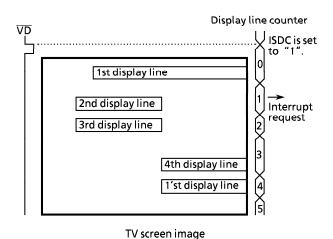

## 3.2.4 Multi-line Displays Using the OSD Interrupt

Up to 4 lines can be displayed on screen with the built-in hardware.

Multi-line displays of more than 5 lines are also available by using the OSD interrupt to rewrite the display start position and display data for the next display after the display of each line has been completed. The hardware related to the OSD interrupt comprises the display line counter, the interrupt generator circuit and its control circuit.

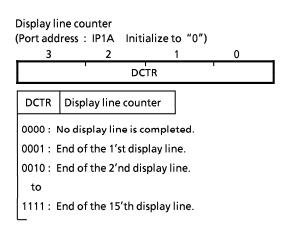

#### (1) Display line counter

The display line counter indicates which line of one TV screen is being displayed. The display line counter is a 4-bit counter which is initialized to "0" by the VD signal and which increments when last scanning of each line is completed. The display line counter can be read out by accessing port address IP1A. The display line counter also increments when the data of the display line are all blank data or the display line is disabled.

#### (2) Interrupt generator circuit

The interrupt generator circuit is controlled by OSD control registers IOSD, SVD, ISDC (command selector is set to  $B_H$ ). One out of the two interrupt sources SIO or OSD can be selected by IOSD of OSD control register. A OSD interrupt request is generated when IOSD is set to "1" and an ISIO interrupt request is generated when IOSD is set to "0". The interrupt request is generated every falling edge of  $\overline{VD}$  signal comes when SVD is set to "1". When the SVD is set to "0", interrupt request is generated at the start point of the first scanning line of the display line specified by ISDC.

Figure 3-20. Multi Line Display Using OSD Interrupt

Figure 3-18. Display Line Counter

- 0: Interrupt request is generated when the display line counter is counted to the certain value which is specified by ISDC.

- 1 : Interrupt request is generated when the falling edge of  $\overline{\text{VD}}$  signal comes.

| ISD  | С   | Display line counter interrupt sources                                                                                                         |

|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 : |     | errupt request is generated at start points of the st scanning line of each display line.                                                      |

| 01 : |     | errupt request is generated at the start point of the st scanning line of the display line when the lower                                      |

| 10:  | Int | oit of the display line counter is "01".  errupt request is generated at the start point of the start point of the display line when the lower |

| 11:  | Int | oit of the display line counter is "10".  errupt request is generated at the start point of the                                                |

Figure 3-19. Control of OSD Interrupt

2-bit of the display line counter is "11".

#### 3.2.5 OSD function

When the level of  $\overline{HD}$  (KE0) or  $\overline{VD}$  (KE1) is pulled-down "Low", change of OSD display disable, character size and ON/OFF of fringing function should be executed.

## 3.3 4bit A/D Conversion (Comparator) Input

The comparator input is analog input to discriminate key input or AFC (Auto Frequency Control) signal. It's composed of 4-bit D/A converter, comparator and control circuit. Analog input level (CIN0 to CIN3) can be detected as 16-stage by setting reference voltage.

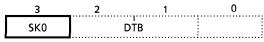

The comparator input can also be used as K0 port (digital input). To use as K0 port, set the most significant bit of the port address OP13 to "1". Which port is selected digital (K0) or comparator (CIN) input can be monitored by accessing the port address IP13. DTB selector/status is also assigned to port address OP13/IP13.

Note. When the comparator input is selected, the comparator consumes typically 700  $\mu$ A current at VDD = 5 V. To reduce the power consumption, K0 port should be set to digital input mode. In the HOLD mode, the comparator current is automatically cut off by hardware. Further, during the slow operating mode, A/D conversion input is automatically disabled by hardware to reduce the power consumption.

## 3.3.1 Circuit Configuration of Comparator Input

Figure 3-21. Circuit of Comparator Input

## 3.3.2 Control of Comparator Input

K0 port input selector command register (Port address : OP13/IP13 Initial value 0110)

| SK0     | Select K0 input mode |

|---------|----------------------|

| 0 : CIN | N comparator input   |

| 1: K0   | digital input        |

Figure 3-22. Command Register, Status Register

Reference voltage (Vref) is set by command register (port address OP12), and it is determined by the following form.

$$V_{REF} = V_{DD} \times (n + 1) / 16 [V] \quad (n = 0 \text{ to } 15)$$

After initialization sequence, 4-channel comparator inputs continue comparison operation successively.

Since 2-instruction cycles are required to complete comparison of 1-channel, it is necessary to wait for 8-instruction cycles after setting a reference voltage to read data from the comparator. When analog input voltage is higher than reference voltage, comparator data latch is set to "1". At the initialization sequence, OP12 is set to "0". There is not latch when used to port K0.

|   | OP | 12 |   | Vref. |

|---|----|----|---|-------|

| 3 | 2  | 1  | 0 | [V]   |

| 0 | 0  | 0  | 0 | 0.31  |

| 0 | 0  | 0  | 1 | 0.62  |

| 0 | 0  | 1  | 0 | 0.94  |

| 0 | 0  | 1  | 1 | 1.25  |

| 0 | 1  | 0  | 0 | 1.56  |

| 0 | 1  | 0  | 1 | 1.87  |

| 0 | 1  | 1  | 0 | 2.19  |

| 0 | 1  | 1  | 1 | 2.50  |

| 1 | 0  | 0  | 0 | 2.81  |

| 1 | 0  | 0  | 1 | 3.12  |

| 1 | 0  | 1  | 0 | 3.44  |

| 1 | 0  | 1  | 1 | 3.75  |

| 1 | 1  | 0  | 0 | 4.06  |

| 1 | 1  | 0  | 1 | 4.37  |

| 1 | 1  | 1  | 0 | 4.69  |

| 1 | 1  | 1  | 1 | 5.00  |

Table 3-8. Reference Voltage

## 3.4 D/A Converter (Pulse Width Modulation) Output

The 47C1238A / 1638A have 10 built-in pulse width modulation (PWM) channels. D/A converter output can easily be obtained by connecting an external low-pass filter.

PWM outputs are multiplexed with general purpose I/O ports as; R31, R32 (PWM8, PWM9), R4 (PWM0 to PWM3), R50 - R53 (PWM4 to PWM7). When these ports are used as PWM outputs, the corresponding bits of R3, R4 and R5 output latches should be set to "1". Resetting initializes the R3, R4 and R5 output latches to "1".

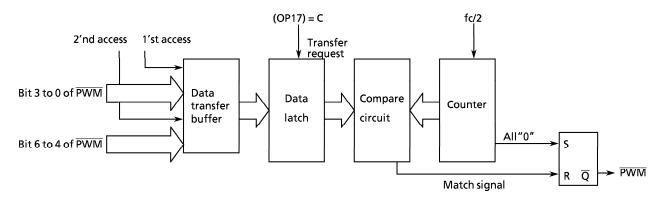

PWM output is controlled by the buffer selector (OP17) and data transfer register (OP18). Writing "C<sub>H</sub>" to the buffer selector transfers the PWM data in the data transfer buffer to the PWM data latch, thus, the PWM output will be changed. The PWM data transferred to the PWM data latch are retained until overwritten.

Resetting and holding clear the buffer selector, data transfer buffer and PWM data latch to "0".

## 3.4.1 Pulse Width Modulation Circuit Output

## (1) PWM0 output

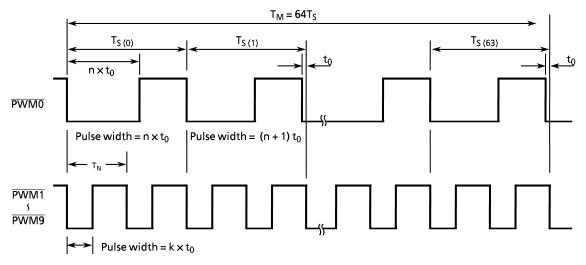

This is 14-bit resolution  $\overline{PWM}$  output and one period is  $T_M = 2^{15}/fc$  [s].

The 8 high-order bits of the PWM data latch control the pulse width of the pulse output with a period of  $T_S$  ( $T_S = T_M/64$ ), which is the sub-period of the  $\overline{PWM0}$ . When the 8-bit data are decimal n ( $0 \le n \le 255$ ), this pulse width becomes  $n \times t_0$ , where  $t_0 = 2/fc$ .

The lower 6-bit of 14 bit data are used to control the generation of additional to wide pulse in each  $T_S$  period. When the 6-bit data are decimal m ( $0 \le m \le 63$ ), the additional pulse is generated in each of m periods out of 64 periods contained in a  $T_M$  period. The relationship between the 6 bits data and the position of TS period where the additional pulse is generated is shown in Table 3-9.

#### (2) PWM1 - PWM9 outputs

These are 7-bit resolution  $\overline{PWM}$  outputs and one period is  $T_N = 28/\text{fc}$  [s]. When the 7bit data are decimal k (0  $\leq k \leq$  127), the pulse width becomes  $k \times t_0$ . The wave form is illustrated in Figure 3-22.

## 3.4.2 Pulse Width Modulation Circuit Control (Data Transfer)

PWM output is controlled by writing the output data to data transfer buffers (OP18). For writing the output data are divided using the buffer selector (OP17). Buffer numbers are assigned to each of the data transfer buffers. Writing is performed in accordance with the corresponding tables shown in Table 3.10.

- ① Write the buffer number of the transfer buffer to which the data are to be written to the buffer selector (OP17).

- ② Write the 4 low-order bits of the corresponding PWM output data to the selected buffer (OP18).

- ③ Next, write the 4 high-order bits of PWM output data to the buffer.

- When writing of the output data is completed, write "C<sub>H</sub>" to the buffer selector. When switching of the output data is completed, the PWM status input becomes "0", indicating that the next data can be written. Do not write PWM data when the PWM status is "1" because write errors can occur in this case. The PWM status can be read by accessing bit "0" of port address IP17.

While the output data are being written to the transfer buffer, the previously written data are being output. The maximum time from the point at which " $C_H$ " is written to the buffer register until  $\overline{PWM}$  output is switched is  $2^{15}$ /fc (at 4 MHz, 8192  $\mu$ s) for  $\overline{PWM0}$  output and  $2^8$ /fc [s] (at 4 MHz, 128  $\mu$ s) for  $\overline{PWM1}$  to  $\overline{PWM9}$  output.

Note. It is shown to the additional pulse  $T_{S(1)}$  and  $T_{S(63)}$  of the  $\overline{PWMO}$ .

Figure 3-23. PWM Output Wave Form

Figure 3-24. PWM Circuit Configuration (7bit Resolution)

| Bit position of 6 bits data | Relative position of $T_S$ where the output pulse is generated (No. i of $T_{S(i)}$ is listed) |

|-----------------------------|------------------------------------------------------------------------------------------------|

| Bit0                        | 32                                                                                             |

| Bit1                        | 16, 48                                                                                         |

| Bit2                        | 8, 24, 40, 56                                                                                  |

| Bit3                        | 4, 12, 20, 28, 36, 44, 52, 60                                                                  |

| Bit4                        | 2, 6, 10, 14, 18, 22, 26, 30,, 58, 62                                                          |

| Bit5                        | 1, 3, 5, 7, 9, 11, 13, 15, 17,, 59, 61, 63                                                     |

Note. When the corresponding bit is "1", it is output.

Table 3-9. Correspondence between 6 Bits Data and the Additional Pulse Generated T<sub>S</sub> Periods

| Buffer number | Correspondence          | Mode                 |          |

|---------------|-------------------------|----------------------|----------|

| (OP17)        | 1'st access 2'nd access |                      | Mode     |

| 0             | Bit 3 to 0 of PWM0      | Bit 5 to 4 of PWM0   | Writing  |

| 1             | Bit 9 to 6 of PWM0      | Bit 13 to 10 of PWM0 | Writing  |

| 2             | Bit 3 to 0 of PWM1      | Bit 6 to 4 of PWM1   | Writing  |

| 3             | Bit 3 to 0 of PWM2      | Bit 6 to 4 of PWM2   | Writing  |

| 4             | Bit 3 to 0 of PWM3      | Bit 6 to 4 of PWM3   | Writing  |

| 5             | Bit 3 to 0 of PWM4      | Bit 6 to 4 of PWM4   | Writing  |

| 6             | Bit 3 to 0 of PWM5      | Bit 6 to 4 of PWM5   | Writing  |

| 7             | Bit 3 to 0 of PWM6      | Bit 6 to 4 of PWM6   | Writing  |

| 8             | Bit 3 to 0 of PWM7      | Bit 6 to 4 of PWM7   | Writing  |

| 9             | Bit 3 to 0 of PWM8      | Bit 6 to 4 of PWM8   | Writing  |

| А             | Bit 3 to 0 of PWM9      | Bit 6 to 4 of PWM9   | Writing  |

| С             | None                    | None                 | Transfer |

Table 3-9. The Bit and Buffer Number of Data

## 3.5 Pulse Output Circuit

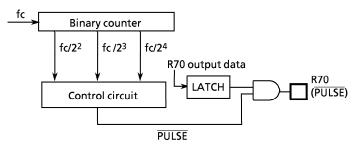

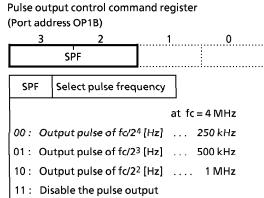

Pulse output circuit generates the pulse clock by dividing the clock frequency to R70 port. The pulse output is used for the basic clock for the PLL IC or peripheral ICs. The pulse output frequency can be set by accessing command register (OP1B). Command register is initialized to '11\*\*' during reset. When R70 port is used as the pulse output, set R70 output latch to "1".

Figure 3-25. Pulse Output Circuit

Figure 3-26. Pulse Output Command Register

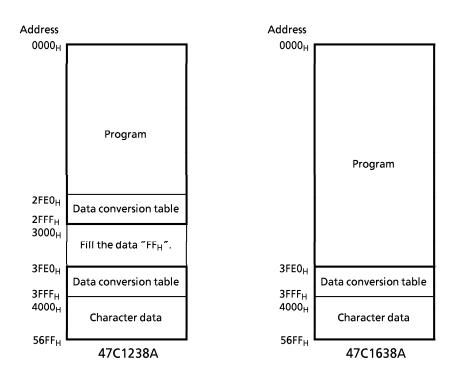

# Notice of ROM code release for masked products

When releasing ROM code for mask products, please take notice as follows,

- (1) The area of program

- Fill the data "FFH" at all addresses of unused area.

- (2) The area of character data table

- Load the character data at the address 4000<sub>H</sub> to 56FF<sub>H</sub>.

- Fill the data 'FFH' at all addresses of unused characters.

- (3) The area between the end of program and the begin of character data

- Fill the data "FFH" at all addresses.

# INPUT/OUTPUT CIRCUITRY

# (1) Control pins Input/output circuitries of the 47C1238A/1638A control pins are shown below.

| CONTROL PIN          | I/O              | CIRCUITRY                                           | REMARKS                                                                                                                                                         |

|----------------------|------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN<br>XOUT          | Input<br>Output  | OSC. enable  R  R  R  XIN  XOUT                     | Resonator connecting pins $R = 1 \text{ k}\Omega \text{ (typ.)}$ $R_f = 1.5 \text{ M}\Omega \text{ (typ.)}$ $R_O = 2 \text{ k}\Omega \text{ (typ.)}$            |

| XTIN<br>XTOUT        | Input<br>Output  | OSC. enable WRfs Rfs RO                             | Resonator connecting pins $ (R = 1 \text{ k}\Omega \text{ typ.}) $ $ (R_{fs} = 6 \text{ M}\Omega \text{ typ.}) $ $ (R_{O} = 220 \text{ k}\Omega \text{ typ.}) $ |

| RESET                | Input            | PIN R R                                             | Hysteresis input Contained pull-up resistor $R_{IN}$ = 220 $k\Omega$ (typ.) $R$ = 1 $k\Omega$ (typ.)                                                            |

| HOLD (KEO)           | Input<br>(Input) |                                                     | Hysteresis input $ (\text{Sense input}) $ $ R = 1 \text{ k}\Omega \text{ (typ.)} $                                                                              |

| TEST                 | Input            | R <sub>IN</sub> &                                   | Contained pull-down resistor $R_{\text{IN}} = 70  \text{k}\Omega   \text{(typ.)}$ $R = 1  \text{k}\Omega   \text{(typ.)}$                                       |

| OSC1<br>OSC2         | Input<br>Output  | OSC. enable $R \not = R_0$ $R \not = R_0$ OSC1 OSC2 | Oscilation terminals for OSD $R = 1 \text{ k}\Omega \text{ (typ.)}$ $R_f = 1.5 \text{ M}\Omega \text{ (typ.)}$ $R_0 = 2 \text{ k}\Omega \text{ (typ.)}$         |

| HD (KC0)<br>∇D (KC1) | Input            |                                                     | Synchronous signal input Hysteresis input $R=1\ k\Omega\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                    |

# (2) I/O ports

The input/output circuitries of the 47C1238A/1638A I/O ports are shown below, designated by code.

| PORT                   | I/O    | INPUT/OUTPUT C                        | RCUITRY (code)                      | REMARKS                                                                                                 |

|------------------------|--------|---------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|

| К0                     | Input  | PA                                    | PC  R <sub>IN</sub> R <sub>IN</sub> | Pull-down resistor $R_{IN}$ = 70 k $\Omega$ (typ.) $R = 1$ k $\Omega$ (typ.)                            |

| P1<br>P2               | Output |                                       |                                     | Sink open drain<br>Initial "Hi-Z"<br>High drive current<br>I <sub>OL</sub> = 20 mA (typ.)               |

| R3                     | 1/0    | ————————————————————————————————————— | oVDD<br>→ R<br>→ R                  | Push-pull output Initial "High" $R=1~\mathrm{k}\Omega~\mathrm{(typ.)}$                                  |

| R4<br>R5               | I/O    | DISABLE                               | oVDD<br>I→<br>R  R                  | Tri-state I/O Initial "Hi-Z" $R=1~\mathrm{k}\Omega~\mathrm{(typ.)}$                                     |

| R6<br>R7<br>R8<br>R9   | I/O    | R6, R7                                | R8, R9                              | Sink open drain Initial "Hi-Z" CMOS input (R6, R7) Hysteresis input (R8, R9) $R = 1 \ k\Omega \ (typ.)$ |

| R<br>G<br>B<br>Y<br>BL | Output | DISABLE                               | OVDD<br>III                         | Tri-state output<br>Initial "Hi-z"                                                                      |

**TOSHIBA**

## **ELECTRICAL CHARACTERISTICS**

ABSOLUTE MAXIMUM RATINGS  $(V_{SS} = 0 V)$

| PARAMETER                    | SYMBOL             | PINS                                            | RATING                         | UNIT |  |

|------------------------------|--------------------|-------------------------------------------------|--------------------------------|------|--|

| Supply Voltage               | $V_{DD}$           |                                                 | – 0.3 to 7                     | ٧    |  |

| Input Voltage                | V <sub>IN</sub>    |                                                 | - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |  |

| Output Voltage               | V <sub>OUT1</sub>  | Except sink open drain pin, but include port R7 | - 0.3 to V <sub>DD</sub> + 0.3 | v    |  |

| Output Voltage               | V <sub>OUT2</sub>  | Sink open drain pin except R7 port              | – 0.3 to 10                    | V    |  |

| Output Compat (Band sin)     | I <sub>OUT1</sub>  | Ports P1, P2                                    | 30                             | 4    |  |

| Output Current (Per 1 pin)   | I <sub>OUT2</sub>  | Ports R3, R6, R7, R8, R9                        | 3.2                            | mA   |  |

| Output Current (Total)       | Σl <sub>OUT1</sub> | Ports P1, P2                                    | 120                            | mA   |  |

| Power Dissipation            | PD                 |                                                 | 600                            | mW   |  |

| Soldering Temperature (time) | T <sub>sld</sub>   |                                                 | 260 (10 s)                     | °C   |  |

| Storage Temperature          | T <sub>stg</sub>   |                                                 | – 55 to 125                    | °C   |  |

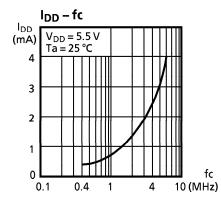

| Operating Temperature        | T <sub>opr</sub>   |                                                 | – 30 to 70                     | °C   |  |

RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0 \text{ V}, T_{opr} = -30 \text{ to } 70 \text{ °C})$

| PARAMETER          | SYMBOL           | PINS                    | CONDITION               | Min.                   | Max.                   | UNIT |

|--------------------|------------------|-------------------------|-------------------------|------------------------|------------------------|------|

|                    |                  |                         | In the Normal mode      | 4.5                    |                        |      |

| Supply Voltage     | $V_{DD}$         |                         | In the SLOW mode        | 2.7                    | 6.0                    | v    |

|                    |                  |                         | In the HOLD mode        | 2.0                    |                        |      |

|                    | V <sub>IH1</sub> | Except Hysteresis Input | V >45V                  | V <sub>DD</sub> × 0.7  |                        |      |

| Input High Voltage | V <sub>IH2</sub> | V <sub>DD</sub> ≥ 4.5 V |                         | V <sub>DD</sub> × 0.75 | $V_{DD}$               | V    |

|                    | V <sub>IH3</sub> |                         | V <sub>DD</sub> <4.5 V  | V <sub>DD</sub> × 0.9  |                        |      |

|                    | V <sub>IL1</sub> | Except Hysteresis Input |                         |                        | $V_{DD} \times 0.3$    |      |

| Input Low Voltage  | V <sub>IL2</sub> | Hysteresis Input        | V <sub>DD</sub> ≧ 4.5 V | 0                      | V <sub>DD</sub> × 0.25 | V    |

|                    | V <sub>IL3</sub> |                         | V <sub>DD</sub> <4.5 V  |                        | V <sub>DD</sub> × 0.1  |      |

|                    | fc               | XIN, XOUT               |                         | 0.4                    | 6.0                    | MHz  |

| Clock Frequency    | fs               | XTIN, XTOUT             |                         | 30.0                   | 34.0                   | kHz  |

|                    | f <sub>OSD</sub> | OSC1, OSC2              |                         | _                      | 8.0                    | MHz  |

Note . Input Voltage  $V_{IH3}$ ,  $V_{IL3}$ : in the SLOW or HOLD operating mode.

D.C. CHARACTERISTICS

$(V_{SS} = 0 \text{ V}, T_{opr} = -30 \text{ to } 70 \text{ °C})$

| PARAMETER                              | SYMBOL           | PINS                                                | CONDITION                                               | Min. | Тур. | Max | UNIT  |

|----------------------------------------|------------------|-----------------------------------------------------|---------------------------------------------------------|------|------|-----|-------|

| Hysteresis Voltage                     | $V_{HS}$         | Hysteresis Input                                    |                                                         | -    | 0.7  | ÷   | V     |

| Input Current                          | I <sub>IN1</sub> | Port K0, TEST,<br>RESET, HOLD                       | V <sub>DD</sub> = 5.5 V,                                | _    |      | ± 2 | μA    |

| input current                          | I <sub>IN2</sub> | Port R (open drain)                                 | V <sub>IN</sub> = 5.5 V / 0 V                           |      |      | ± 2 | μ.,   |

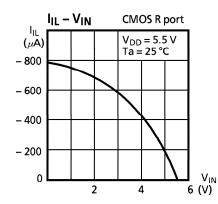

| Input Low Current                      | I <sub>IL</sub>  | Port R (push-pull)                                  | $V_{DD} = 5.5 \text{ V}, V_{IN} = 0.4 \text{ V}$        | -    | _    | - 2 | mA    |

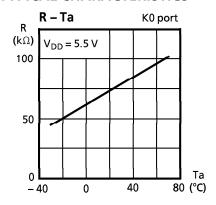

| Input Resistance                       | R <sub>IN1</sub> | Port K0 with pull-up/pull-down                      |                                                         | 30   | 70   | 150 |       |

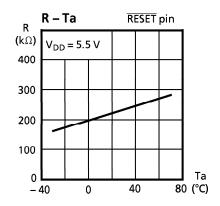

| input resistance                       | R <sub>IN2</sub> | RESET                                               |                                                         | 100  | 220  | 450 | kΩ    |

| Output Leakage<br>Current              | I <sub>LO</sub>  | Tri-state port<br>Ports R3, R6, R8, R9 (open drain) | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V       | _    | 1    | ± 2 | μΑ    |

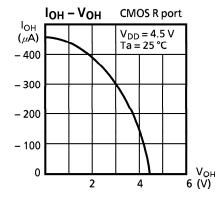

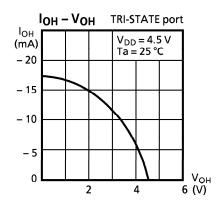

| Output High                            | V <sub>OH1</sub> | Port R (push-pull)                                  | $V_{DD} = 4.5 \text{ V}, \ I_{OH} = -200 \ \mu\text{A}$ | 2.4  | -    | _   |       |

| Voltage                                | V <sub>OH2</sub> | Port R (tri-state), OSD outputs                     | $V_{DD} = 4.5 \text{ V}, I_{OH} = -0.7 \text{ mA}$      | 4.1  | _    | _   | \ \ \ |

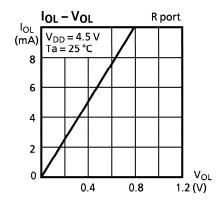

|                                        | V <sub>OL1</sub> | Ports R3, R6-R9                                     | $V_{DD} = 4.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$       |      |      |     |       |

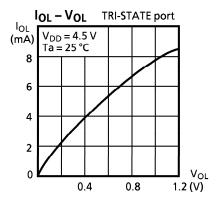

| Output Low Voltage                     | $V_{OL2}$        | Port R (tri-state), OSD outputs                     | $V_{DD} = 4.5 \text{ V}, I_{OL} = 0.7 \text{ mA}$       | ] _  | _    | 0.4 | V     |

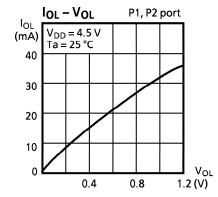

| Output Low Current                     | I <sub>OL</sub>  | Ports P1, P2                                        | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$        | _    | 20   | _   | mA    |

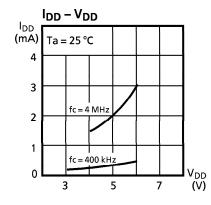

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>  |                                                     | V <sub>DD</sub> = 5.5 V,<br>fc = 4 MHz                  | _    | 3    | 6   | mA    |

| Supply Current<br>(in the SLOW mode)   | I <sub>DDS</sub> |                                                     | V <sub>DD</sub> = 3.0 V                                 | _    | 30   | 60  | μΑ    |

| Supply Current<br>(in the HOLD mode)   | I <sub>DDH</sub> |                                                     | V <sub>DD</sub> = 5.5 V                                 | _    | 0.5  | 10  | μΑ    |

Note 1. Typ. values show those at  $T_{opr} = 25$  °C,  $V_{DD} = 5$  V.

Note 2. Input Current I<sub>IN1</sub>: The current through resistor is not included, when the pull-

up/pull-down resistor is contained.

Note 3. Supply Current

$I_{DD}$ ,  $I_{DDH}$  :  $V_{IN} = 5.3 \text{ V} / 0.2 \text{ V}$

The KO port is open when the pull-up / pull-down resistor is contained. The voltage applied to the R port is within the valid

range V<sub>IL</sub> or V<sub>IH</sub>.

$I_{DDS}$  :  $V_{IN} = 2.8 \text{ V} / 0.2 \text{ V}$

Low frequency clock is only oscillated (connecting XTIN,XTOUT).

Comparator function is disabled.

#### A / D CONVERTER CHARACTERISTICS

| PARAMETER              | SYMBOL | PINS | CONDITION | Min.            | Тур. | Max.     | UNIT |

|------------------------|--------|------|-----------|-----------------|------|----------|------|

| Analog input voltage   | VAIN   | CIN  |           | V <sub>SS</sub> | -    | $V_{DD}$ | V    |

| A / D conversion error | _      |      |           | -               | -    | ± 1/2    | LSB  |

A.C. CHARACTERISTICS

(V<sub>SS</sub> = 0 V, V<sub>DD</sub> = 4.5 to 6.0 V,  $T_{opr}$  = -30 to 70 °C)

| PARAMETER                    | SYMBOL           | CONDITION                    | Min.          | Тур. | Max. | UNIT |  |

|------------------------------|------------------|------------------------------|---------------|------|------|------|--|

| lastication Code Time        |                  | In the Normal mode           | 1.3           | _    | 20   |      |  |

| Instruction Cycle Time       | t <sub>cy</sub>  | In the SLOW mode             | 235           | -    | 267  | μS   |  |

| High level Clock Pulse Width | t <sub>WCH</sub> | For external clock operation | 80            | _    | _    | ns   |  |

| Low level Clock Pulse Width  | t <sub>WCL</sub> | Tor external clock operation | 00            |      |      | 113  |  |

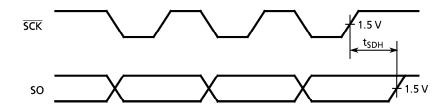

| Shift data Hold Time         | t <sub>SDH</sub> |                              | 0.5 tcy – 300 | -    | -    | ns   |  |

Note. Shift data Hold Time:

External circuit for  $\overline{SCK}$  pin and SO pin.

Serial port (completion of transmission)

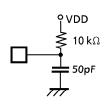

## **RECOMMENDED OSCILLATING CONDITIONS**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}, T_{opr} = -30 \text{ to } 70 ^{\circ}\text{C})$

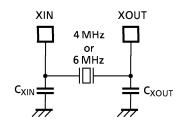

(1) 6 MHz

**Ceramic Resonator**

CSA6.00MGU (MURATA)  $C_{XIN} = C_{XOUT} = 30 \text{ pF}$ KBR-6.00MS (KYOCERA)  $C_{XIN} = C_{XOUT} = 30 \text{ pF}$

(2) 4 MHz

**Ceramic Resonator**

| CSA4.00MG  | (MURATA)  | $C_{XIN} = C_{XOUT} = 30 pF$ |

|------------|-----------|------------------------------|

| KBR-4.00MS | (KYOCERA) | $C_{XIN} = C_{XOUT} = 30 pF$ |

| FCR-4.0MS  | (TDK)     | $C_{XIN} = C_{XOUT} = 33 pF$ |

**Crystal Oscillator**

204B-6F 4.0000 (TOYOCOM)  $C_{XIN} = C_{XOUT} = 20 \text{ pF}$

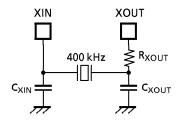

(3) 400 kHz

**Ceramic Resonator**

CSB400B (MURATA)

$$C_{XIN} = C_{XOUT} = 220 \text{ pF},$$

$R_{XOUT} = 6.8 \text{ k}\Omega$

KBR-400B (KYOCERA)  $C_{XIN} = C_{XOUT} = 100 \text{ pF},$   $C_{XOUT} = 10 \text{ k}\Omega$

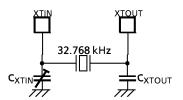

(4) 32.768 kHz (V<sub>SS</sub> = 0 V, V<sub>DD</sub> = 2.7 to 6.0 V, T<sub>opr</sub> = -30 to 70 °C) Crystal Oscillator C<sub>XTIN</sub>, C<sub>XTOUT</sub>; 10 to 33 pF

Note: In order to get the accurate oscillation frequency, the adjustment of capacitors must be required.

- (5) 8 MHz (for OSD) LC Resonator A285TNIS - 11695 (TOKO)

- (6) 7 MHz (for OSD)

LC Resonator

TBEKSES 30375FBY (TOKO)

Note: An electrical shield by metal shield plate on the surface of the IC package should be recommendable in order to prevent the device from the high electric fieldstress applied from CRT (Cathode Ray Tube) for continuous reliable operation.

## **TYPICAL CHARACTERISTICS**