- Provides Two-Chip Modem Solution

- Data Rates from 300 bps to 56 kbps

- Data Modulation Standards

V.90, V.34, V.32bis, V.32, V.22bis, V.22, V.23,

V.21 and V.23 reversible (Minitel), Bell 212,

Bell 103

- V.42 Error Control and V.42bis Compression

- Caller ID

- Field-Proven Modem Algorithms Give Highest Performance, Reliability, and Compatibility

- Worldwide Telecom Approvals

- Protected Against Surge and Overvoltage on the Telephone Line

- Parallel Host Port Interface Supports a Variety of Industry Standard Busses

- Integral Serial Interface (UART)

- State-of-the-Art Integrated Transformerless Silicon DAA for Phone Line Interconnection

- Applications

- Embedded Systems

- Set Top Box

- Gaming Consoles

- Internet Appliances

- Portable Devices (PDAs, digital cameras)

- Remote Data Collection, Point-of-Sale

- Meter Reading, Utility Monitoring

- 40K x 16-Bit Dual-Access On-Chip RAM

- 128K x 16-Bit On-Chip ROM

- On-Chip Peripherals

- Software-Programmable Wait-State Generator and Programmable Bank Switching

- On-Chip Phase-Locked Loop (PLL) Clock Generator With Internal Oscillator or External Clock Source

- Two Multichannel Buffered Serial Ports (McBSPs)

- Enhanced 8-Bit Parallel Host-Port Interface (HPI8)

- Power Consumption Control With IDLE1, IDLE2, and IDLE3 Instructions With Power-Down Modes

- On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1<sup>†</sup> (JTAG) Boundary Scan Logic

- 8.5-ns Single-Cycle Fixed-Point Instruction Execution Time (117.96 MIPS) for 3.3-V Power Supply (1.5-V Core)

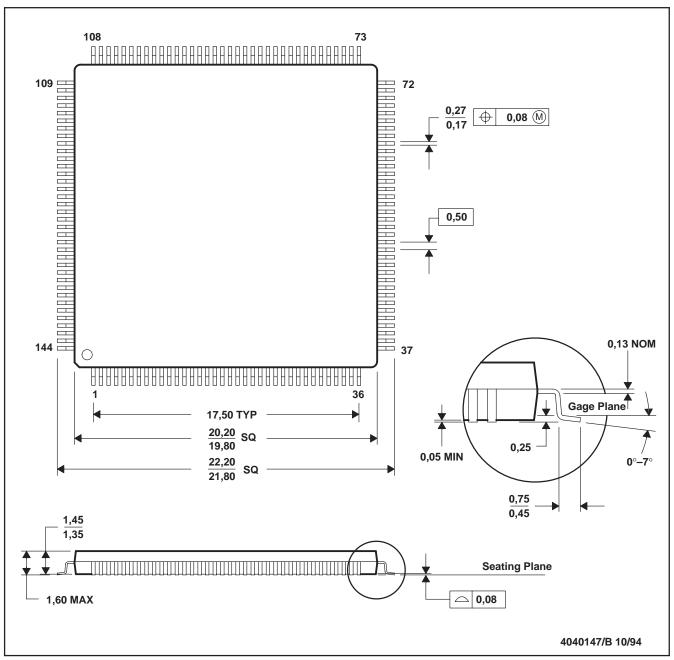

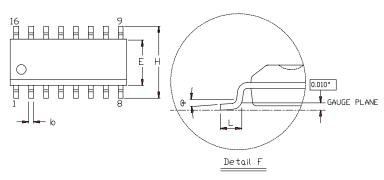

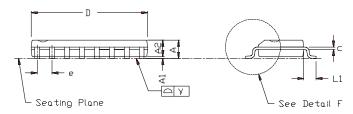

- Available in a 144-Pin Plastic Low-Profile Quad Flatpack (LQFP) (PGE Suffix) and a 144-Pin Ball Grid Array (BGA) (GGU Suffix)

# description

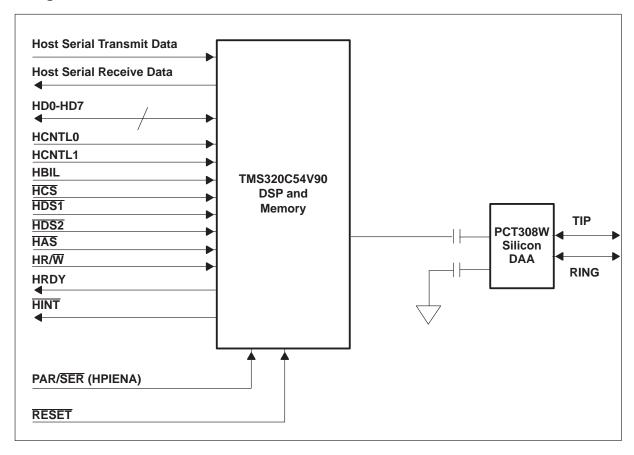

The TMS320C54V90 is used to implement a full-featured, high-performance modem technology, intended for use in embedded systems and similar applications. This highly integrated solution implements a complete modem using only two chips: the TMS320C54V90 DSP with on-chip RAM and ROM, and the PCT308W line-side DAA available from PCTEL, Inc.

The modem can connect to a host system serially (RS-232 functionality), or as an 8-bit peripheral to the processor in a host system. The TMS320C54V90 uses a standard Digital Signal Processor (DSP) and proprietary firmware to perform all the modem signal processing, the V.42/V.42bis compression, and AT commands interpretation for modem control functions.

The TMS320C54V90 also uses the latest silicon DAA technology. This technology does not require a transformer and results in lower cost, lower power, and a smaller area for the DAA function.

For serial interface applications, an integrated UART implements the serial interface with no additional hardware.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

# TMS320C54V90 **EMBEDDED V.90 MODEM** DSP OVERVIEW SPRS004 – SEPTEMBER 2001

| Description 1               | Power Requirements                  |

|-----------------------------|-------------------------------------|

| Pin Assignments 5           | Serial and Parallel Interface Modes |

| Pin Descriptions: PCT308W11 | Serial Interface                    |

| Functional Description      | Host Port Interface (HPI)           |

| Block Diagram 12            | Absolute Maximum Ratings            |

| Mode Selection              | Switching Characteristics           |

| Clock Requirements          | HPI Timing                          |

### **REVISION HISTORY**

| REVISION | DATE      | PRODUCT STATUS       | HIGHLIGHTS |

|----------|-----------|----------------------|------------|

| *        | July 2001 | Advanced Information | Original   |

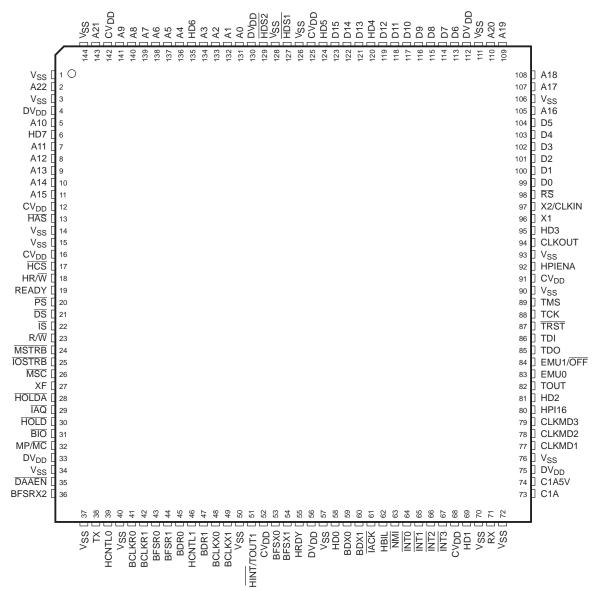

#### PGE PACKAGE† (TOP VIEW)

<sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU. V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

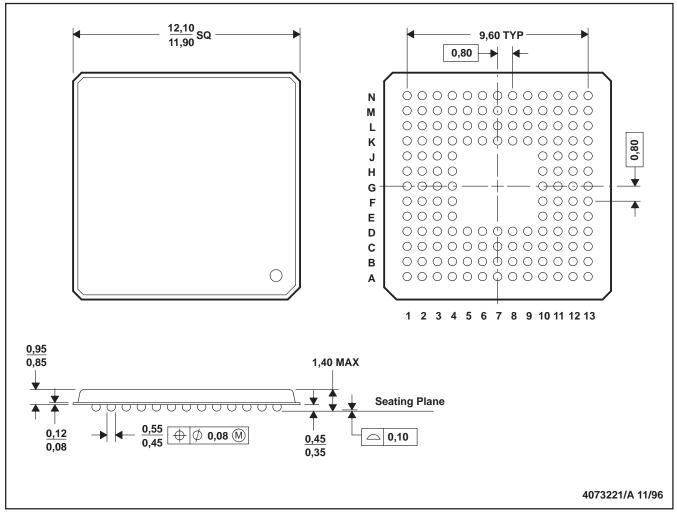

# GGU PACKAGE (BOTTOM VIEW)

|   | $\overline{}$ | 1          | 2          | 3          | 4          | 5          | 6          | 7          | 8          | 9          | 10         | 11         | 12         | _          |

|---|---------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Α |               | $\circ$    | $\circ$    | 0          | 0          | 0          | 0          | 0          | $\circ$    | 0          | 0          | 0          | 0          | $\circ$    |

| В |               | $\bigcirc$ |

| С |               | $\bigcirc$ |

| D |               | $\bigcirc$ |

| Е |               | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| F |               | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| G |               | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| Н |               | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| J |               | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| K |               | $\bigcirc$ |

| L |               | $\bigcirc$ |

| M |               | $\bigcirc$ |

| Ν |               | $\bigcirc$ |

|   |               |            |            |            |            |            |            |            |            |            |            |            |            |            |

The pin assignments table to follow lists each signal name and BGA ball number for the TMS320C54V90 (144-pin BGA) package which is footprint compatible with the TMS320VC5402.

# **ADVANCE INFORMATION**

# Pin Assignments for the TMS320C54V90GGU (144-Pin BGA) Package<sup>†</sup>

| SIGNAL<br>QUADRANT 1 | BGA BALL# | SIGNAL<br>QUADRANT 2 | BGA BALL# | SIGNAL<br>QUADRANT 3 | BGA BALL# | SIGNAL<br>QUADRANT 4 | BGA BALL# |

|----------------------|-----------|----------------------|-----------|----------------------|-----------|----------------------|-----------|

| V <sub>SS</sub>      | A1        | C1A                  | N13       | V <sub>SS</sub>      | N1        | A19                  | A13       |

| A22                  | B1        | C1A5V                | M13       | TX                   | N2        | A20                  | A12       |

| V <sub>SS</sub>      | C2        | DV <sub>DD</sub>     | L12       | HCNTL0               | M3        | V <sub>SS</sub>      | B11       |

| DV <sub>DD</sub>     | C1        | V <sub>SS</sub>      | L13       | V <sub>SS</sub>      | N3        | DV <sub>DD</sub>     | A11       |

| A10                  | D4        | CLKMD1               | K10       | BCLKR0               | K4        | D6                   | D10       |

| HD7                  | D3        | CLKMD2               | K11       | BCLKR1               | L4        | D7                   | C10       |

| A11                  | D2        | CLKMD3               | K12       | BFSR0                | M4        | D8                   | B10       |

| A12                  | D1        | HPI16                | K13       | BFSR1                | N4        | D9                   | A10       |

| A13                  | E4        | HD2                  | J10       | BDR0                 | K5        | D10                  | D9        |

| A14                  | E3        | TOUT                 | J11       | HCNTL1               | L5        | D11                  | C9        |

| A15                  | E2        | EMU0                 | J12       | BDR1                 | M5        | D12                  | B9        |

| CV <sub>DD</sub>     | E1        | EMU1/OFF             | J13       | BCLKX0               | N5        | HD4                  | A9        |

| HAS                  | F4        | TDO                  | H10       | BCLKX1               | K6        | D13                  | D8        |

| V <sub>SS</sub>      | F3        | TDI                  | H11       | V <sub>SS</sub>      | L6        | D14                  | C8        |

| V <sub>SS</sub>      | F2        | TRST                 | H12       | HINT/TOUT1           | M6        | D15                  | B8        |

| CV <sub>DD</sub>     | F1        | TCK                  | H13       | CVDD                 | N6        | HD5                  | A8        |

| HCS                  | G2        | TMS                  | G12       | BFSX0                | M7        | CV <sub>DD</sub>     | B7        |

| HR/W                 | G1        | V <sub>SS</sub>      | G13       | BFSX1                | N7        | V <sub>SS</sub>      | A7        |

| READY                | G3        | CV <sub>DD</sub>     | G11       | HRDY                 | L7        | HDS1                 | C7        |

| PS                   | G4        | HPIENA               | G10       | $DV_DD$              | K7        | V <sub>SS</sub>      | D7        |

| DS                   | H1        | V <sub>SS</sub>      | F13       | V <sub>SS</sub>      | N8        | HDS2                 | A6        |

| ĪS                   | H2        | CLKOUT               | F12       | HD0                  | M8        | $DV_DD$              | B6        |

| R/W                  | H3        | HD3                  | F11       | BDX0                 | L8        | A0                   | C6        |

| MSTRB                | H4        | X1                   | F10       | BDX1                 | K8        | A1                   | D6        |

| ĪOSTRB               | J1        | X2/CLKIN             | E13       | ĪACK                 | N9        | A2                   | A5        |

| MSC                  | J2        | RS                   | E12       | HBIL                 | M9        | A3                   | B5        |

| XF                   | J3        | D0                   | E11       | NMI                  | L9        | HD6                  | C5        |

| HOLDA                | J4        | D1                   | E10       | ĪNT0                 | K9        | A4                   | D5        |

| ĪAQ                  | K1        | D2                   | D13       | ĪNT1                 | N10       | A5                   | A4        |

| HOLD                 | K2        | D3                   | D12       | ĪNT2                 | M10       | A6                   | B4        |

| BIO                  | K3        | D4                   | D11       | ĪNT3                 | L10       | A7                   | C4        |

| MP/MC                | L1        | D5                   | C13       | CV <sub>DD</sub>     | N11       | A8                   | A3        |

| DV <sub>DD</sub>     | L2        | A16                  | C12       | HD1                  | M11       | A9                   | B3        |

| V <sub>SS</sub>      | L3        | V <sub>SS</sub>      | C11       | V <sub>SS</sub>      | L11       | CV <sub>DD</sub>     | C3        |

| DAAEN                | M1        | A17                  | B13       | RX                   | N12       | A21                  | A2        |

| BFSRX2               | M2        | A18                  | B12       | V <sub>SS</sub>      | M12       | V <sub>SS</sub>      | B2        |

$<sup>^{\</sup>dagger}$  DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU. V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

Table 1. TMS320C54V90 Pin Functions

| TERMINAL                                                                                                                                             | 1                              |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                                                                                                                                                 | I/O <sup>†</sup>               |                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                                                                                                                                      | EXTERNAL MEMORY INTERFACE PINS |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| NAME  A22 (MSB) A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 (LSB)  D15 (MSB) D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 | O/Z                            | Parallel address bus<br>multiplexed to addre<br>pins—A22 to A16— | TERNAL MEMORY INTERFACE PINS  A A22 (MSB) through A0 (LSB). The lower sixteen address pins—A0 to A15—are eas all external memory (program, data) or I/O, while the upper seven address are only used to address external program space. These pins are placed in the te when the hold mode is enabled, or when OFF is low.  These pins can be used to address internal memory via the HPI when the HPI16 pin is high. |  |  |  |  |

| D3<br>D2                                                                                                                                             |                                | D3<br>D2                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| D1<br>D0 (LSB)                                                                                                                                       |                                | D1<br>D0 (LSB)                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| ( - /                                                                                                                                                | 1                              | ` ,                                                              | I<br>IZATION, INTERRUPT, AND RESET PINS                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ĪACK                                                                                                                                                 | O/Z                            |                                                                  | ge signal. IACK Indicates receipt of an interrupt and that the program counter is fetching location designated by A15–0. IACK also goes into the high-impedance state when OFF                                                                                                                                                                                                                                        |  |  |  |  |

| INTO<br>INT1<br>INT2<br>INT3                                                                                                                         | I                              | interrupt mode bit. T                                            | upt inputs. INTO-3 are prioritized and maskable via the interrupt mask register and The status of these pins can be polled by way of the interrupt flag register.                                                                                                                                                                                                                                                     |  |  |  |  |

| NMI                                                                                                                                                  | I                              |                                                                  | upt. NMI is an external interrupt that cannot be masked by way of the INTM or the IMR. ted, the processor traps to the appropriate vector location.                                                                                                                                                                                                                                                                   |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply

| TERMINAL<br>NAME | I/O <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                  | INITIALIZATION, INTERRUPT, AND RESET PINS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                 |

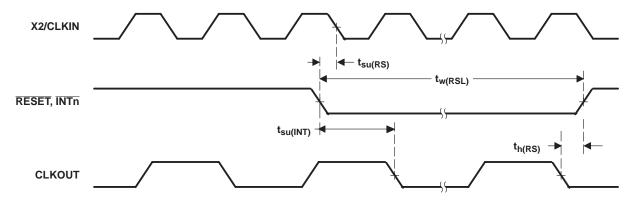

| RS               | I                | Reset input. RS causes the DSP to terminate execution and causes a re-initialization of the CPU and peripherals. When RS is brought to a high level, execution begins at location 0FF80h of program memory. RS affects various registers and status bits.                                                                                                                                                                                                             |

| MP/MC            | I                | Microprocessor/microcomputer mode select pin. If active low at reset, microcomputer mode is selected, and the internal program ROM is mapped into the upper 16K words of program memory space. If the pin is driven high during reset, microprocessor mode is selected, and the on-chip ROM is removed from program space. This pin is only sampled at reset, and the MP/MC bit of the PMST register can override the mode that is selected at reset.                 |

|                  |                  | MULTIPROCESSING AND GENERAL PURPOSE PINS                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BIO              | I                | Branch control input. A branch can be conditionally executed when BIO is active. If low, the processor executes the conditional instruction. The BIO condition is sampled during the decode phase of the pipeline for XC instruction, and all other instructions sample BIO during the read phase of the pipeline.                                                                                                                                                    |

| XF               | O/Z              | External flag output (latched software-programmable signal). XF is set high by the SSBX XF instruction, set low by RSBX XF instruction or by loading ST1. XF is used for signaling other processors in multiprocessor configurations or as a general-purpose output pin. XF goes into the high-impedance state when OFF is low, and is set high at reset.                                                                                                             |

|                  |                  | MEMORY CONTROL PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DS<br>PS<br>IS   | O/Z              | Data, program, and I/O space select signals. DS, PS, and IS are always high unless driven low for accessing a particular external memory space. Active period corresponds to valid address information. Placed into a high-impedance state in hold mode. DS, PS, and IS also go into the high-impedance state when OFF is low.                                                                                                                                        |

| MSTRB            | O/Z              | Memory strobe signal. MSTRB is always high unless low-level asserted to indicate an external bus access to data or program memory. Placed in high-impedance state in hold mode. MSTRB also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                        |

| READY            | I                | Data ready input. READY indicates that an external device is prepared for a bus transaction to be completed. If the device is not ready (READY is low), the processor waits one cycle and checks READY again. Note that the processor performs ready detection if at least two software wait states are programmed. The READY signal is not sampled until the completion of the software wait states.                                                                 |

| R/W              | O/Z              | Read/write signal. R/W indicates transfer direction during communication to an external device. Normally in read mode (high), unless asserted low when the DSP performs a write operation. Placed in high-impedance state in hold mode. R/W also goes into the high-impedance state when OFF is low.                                                                                                                                                                  |

| IOSTRB           | O/Z              | I/O strobe signal. IOSTRB is always high unless low level asserted to indicate an external bus access to an I/O device. Placed in high-impedance state in hold mode. IOSTRB also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                                  |

| HOLD             | I                | Hold input. HOLD is asserted to request control of the address, data, and control lines. When acknowledged by the C54x, these lines go into high-impedance state.                                                                                                                                                                                                                                                                                                     |

| HOLDA            | O/Z              | Hold acknowledge signal. HOLDA indicates that the DSP is in a hold state and that the address, data, and control lines are in a high-impedance state, allowing the external memory interface to be accessed by other devices. HOLDA also goes into the high-impedance state when is OFF low.                                                                                                                                                                          |

| MSC              | O/Z              | Microstate complete. MSC indicates completion of all software wait states. When two or more software wait states are enabled, the MSC pin goes active at the beginning of the first software wait state, and goes inactive (high) at the beginning of the last software wait state. If connected to the ready input, MSC forces one external wait state after the last internal wait state is completed. MSC also goes into the high impedance state when OFF is low. |

| ĪĀQ              | O/Z              | Instruction acquisition signal. IAQ is asserted (active low) when there is an instruction address on the address bus and goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                                                                                          |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply

| TERMINAL<br>NAME           | I/O <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                       |  |  |  |  |  |

|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OSCILLATOR/TIMER PINS      |                  |                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| CLKOUT                     | O/Z              | Master clock output signal. CLKOUT cycles at the machine-cycle rate of the CPU. The internal machine cycle is bounded by the rising edges of this signal. CLKOUT also goes into the high-impedance state when OFF is low.                                         |  |  |  |  |  |

| CLKMD1<br>CLKMD2<br>CLKMD3 | I                | Clock mode external/internal input signals. CLKMD1–CLKMD3 allows you to select and configure different clock modes such as crystal, external clock, various PLL factors.                                                                                          |  |  |  |  |  |

| X2/CLKIN                   | I                | Input pin to internal oscillator from the crystal. If the internal oscillator is not being used, an external clock source can be applied to this pin. The internal machine cycle time is determined by the clock operating mode pins (CLKMD1, CLKMD2 and CLKMD3). |  |  |  |  |  |

| X1                         | 0                | Output pin from the internal oscillator for the crystal. If the internal oscillator is not used, X1 should be left unconnected. X1 does not go into the high-impedance state when OFF is low.                                                                     |  |  |  |  |  |

| TOUT                       | 0                | Timer output. TOUT signals a pulse when the on-chip timer counts down past zero. The pulse is a CLKOUT cycle wide. TOUT also goes into the high-impedance state when OFF is low.                                                                                  |  |  |  |  |  |

| TOUT1                      | I/O/Z            | Timer1 output. TOUT1 signals a pulse when the on-chip timer1 counts down past zero. The pulse is a CLKOUT cycle wide. The TOUT1 output is multiplexed with the HINT pin of the HPI, and TOUT1 is only available when the HPI is disabled.                         |  |  |  |  |  |

|                            |                  | MULTI-CHANNEL BUFFERED SERIAL PORT PINS                                                                                                                                                                                                                           |  |  |  |  |  |

| BCLKR0<br>BCLKR1           | I/O/Z            | Receive clock input. CLKR serves as the serial shift clock for the buffered serial port receiver. BCLKRX2 is McBSP2 transmit AND receive clock. This pin is optionally bondable as C1A (see DAA section).                                                         |  |  |  |  |  |

| BDR0<br>BDR1               | I                | Serial data receive input.                                                                                                                                                                                                                                        |  |  |  |  |  |

| BFSR0<br>BFSR1<br>BFSRX2   | I/O/Z            | Frame synchronization pulse for receive input. The FSR pulse initiates the receive data process over DR.  BFSRX2 is McBSP2 transit AND receive frame sync                                                                                                         |  |  |  |  |  |

| BCLKX0<br>BCLKX1           | I/O/Z            | Transmit clock. CLKX serves as the serial shift clock for the buffered serial port transmitter. The CLKX pins are configured as inputs after reset. CLKX goes into the high-impedance state when OFF is low.                                                      |  |  |  |  |  |

| BDX0<br>BDX1               | O/Z              | Serial data transmit output. DX is placed in the high-impedance state when not transmitting, when RS is asserted or when OFF is low.                                                                                                                              |  |  |  |  |  |

| BFSX0<br>BFSX1             | I/O/Z            | Frame synchronization pulse for transmit output. The FSX pulse initiates the transmit data process over DX. The FSX pins are configured as inputs after reset. FSX goes into the high-impedance state when OFF is low.                                            |  |  |  |  |  |

|                            |                  | INTEGRATED DAA                                                                                                                                                                                                                                                    |  |  |  |  |  |

| C1A                        | I/O              | DAA I/O connection.                                                                                                                                                                                                                                               |  |  |  |  |  |

| C1A5V                      | S                | Dedicated 5.0V power supply for I/O pin C1A.                                                                                                                                                                                                                      |  |  |  |  |  |

| DAAEN                      | I                | DAA Enable Input. Enables the DAA when low.                                                                                                                                                                                                                       |  |  |  |  |  |

|                            |                  | UART                                                                                                                                                                                                                                                              |  |  |  |  |  |

| TX                         | 0                | UART asynchronous serial transmit data output.                                                                                                                                                                                                                    |  |  |  |  |  |

| RX                         | I                | UART asynchronous serial receive data input.                                                                                                                                                                                                                      |  |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply

| TERMINAL<br>NAME | I/O <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                  | HOST PORT INTERFACE PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A0-A15           | 1                | These pins can be used to address internal memory via the HPI when the HPI16 pin is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D0-D15           | I/O              | These pins can be used to read/write internal memory via the HPI when the HPI16 pin is high. The sixteen data pins, D0 to D15, are multiplexed to transfer data between the core CPU and external data/program memory, I/O devices, or HPI in 16-bit mode. The data bus is placed in the high-impedance state when not outputting or when RS or HOLD is asserted. The data bus also goes into the high-impedance state when OFF is low.                                                                                                                                       |

|                  |                  | The data bus includes bus holders to reduce the static power dissipation caused by floating, unused pins. The bus holders also eliminate the need for external bias resistors on unused pins. When the data bus is not being driven by the DSP, the bus holders keep the pins at the logic level that was most recently driven. The data bus holders of the DSP are disabled at reset, and can be enabled/disabled via the BH bit of the BSCR.                                                                                                                                |

| HD0-HD7          | I/O/Z            | Parallel bi-directional data bus. These pins can also be used as general-purpose I/O pins when the HPI16 pin is high. HD0–HD7 is placed in the high-impedance state when not outputting data or when OFF is low. The HPI data bus includes bus holders to reduce the static power dissipation caused by floating, unused pins. When the HPI data bus is not being driven by the DSP, the bus holders keep the pins at the logic level that was most recently driven. The HPI data bus holders are disabled at reset, and can be enabled/disabled via the HBH bit of the BSCR. |

| HCNTL0<br>HCNTL1 | I                | Control inputs. These inputs select a host access to one of the three HPI registers. (Pull-up only enabled when HPIENA=0, HPI16=1)                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HBIL             | I                | Byte identification input. Identifies first or second byte of transfer. (Pull-up only enabled when HPIENA=0, invalid when HPI16=1)                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HCS              | I                | Chip select input. This pin is the select input for the HPI, and must be driven low during accesses. (Pull-up only enabled when HPIENA=0, or HPI16=1)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HDS1<br>HDS2     | I                | Data strobe inputs. These pins are driven by the host read and write strobes to control transfers. (Pull-up only enabled when HPIENA=0)                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HAS              | ı                | Address strobe input. Address strobe input. Hosts with multiplexed address and data pins require this input, to latch the address in the HPIA register. (Pull-up only enabled when HPIENA=0)                                                                                                                                                                                                                                                                                                                                                                                  |

| HR/W             | ı                | Read/write input. This input controls the direction of an HPI transfer. (Pull-up only enabled when HPIENA=0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HRDY             | O/Z              | Ready output. The ready output informs the host when the HPI is ready for the next transfer. HRDY goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                                         |

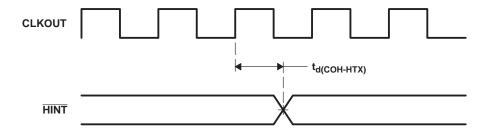

| HINT             | O/Z              | Interrupt output. This output is used to interrupt the host. When the DSP is in reset, this signal is driven high. HINT can also be used for timer 1 output (TOUT1), when the HPI is disabled. The signal goes into the high-impedance state when OFF is low. (invalid when HPI16=1)                                                                                                                                                                                                                                                                                          |

| HPIENA           | I                | HPI enable input. This pin must be driven high during reset to enable the HPI. An internal pull-down resistor is always active and the HPIENA pin is sampled on the rising edge of RS. If HPIENA is left open or driven low during reset, the HPI module is disabled. Once the HPI is disabled, the HPIENA pin has no effect until the DSP is reset.                                                                                                                                                                                                                          |

| HPI16            | I                | HPI 16-bit Select Pin. HPI16=1 selects the non-multiplexed mode. The non-multiplexed mode allows hosts with separate address/data buses to access the HPI address range via the 16 address pins A0–A15. 16-bit Data is also accessible through pins D0–D15. HOST-to-DSP and DSP-to-HOST interrupts are not supported. There are no HPIC and HPIA registers in the non-multiplexed mode since there are HCNTRL0,1 signals available. Internally pulled low.                                                                                                                    |

|                  |                  | SUPPLY PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CV <sub>DD</sub> | S                | +V <sub>DD</sub> . Dedicated 1.5V power supply for the core CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DV <sub>DD</sub> | S                | +V <sub>DD</sub> . Dedicated 3.3V power supply for I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub>  | S                | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply

| TERMINAL<br>NAME | I/O <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | •                | SUPPLY PINS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TCK              | I                | IEEE standard 1149.1 test clock. TCK is normally a free-running clock signal with a 50% duty cycle. The changes on test access port (TAP) of input signals TMS and TDI are clocked into the TAP controller, instruction register, or selected test data register on the rising edge of TCK. Changes at the TAP output signal (TDO) occur on the falling edge of TCK.                                                                                                                                                                                                |

| TDI              | I                | IEEE standard 1149.1 test data input, pin with internal pull-up device. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                    |

| TDO              | O/Z              | IEEE standard 1149.1 test data output. The contents of the selected register (instruction or data) are shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state except when scanning of data is in progress. TDO also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                                                                  |

| TMS              | I                | IEEE standard 1149.1 test mode select. Pin with internal pull-up device. This serial control input is clocked into the test access port (TAP) controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                 |

| TRST             | I                | IEEE standard 1149.1 test reset. TRST, when high, gives the IEEE standard 1149.1 scan system control of the operations of the device. If TRST is not connected or driven low, the device operates in its functional mode, and the IEEE standard 1149.1 signals are ignored. Pin with internal pulldown device.                                                                                                                                                                                                                                                      |

| EMU0             | I/O/Z            | Emulator 0 pin. When TRST is driven low, EMU0 must be high for activation of the OFF condition. When TRST is driven high, EMU0 is used as an interrupt to or from the emulator system and is defined as input/output by way of IEEE standard 1149.1 scan system.                                                                                                                                                                                                                                                                                                    |

| EMU1/OFF         | I/O/Z            | Emulator 1 pin/disable all outputs. When TRST is driven high, EMU1/OFF is used as an interrupt to or from the emulator system and is defined as input/output via IEEE standard 1149.1 scan system. When TRST is driven low, EMU1/OFF is configured as OFF. The EMU1/OFF signal, when active low, puts all output drivers into the high-impedance state. Note that OFF is used exclusively for testing and emulation purposes (not for multiprocessing applications). Thus, for the OFF feature, the following conditions apply: TRST=low, EMU0=high, EMU1/OFF = low |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply

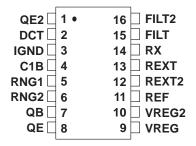

pin descriptions: PCT308W

Table 2. PCT308W Pin Descriptions

| PIN# | PIN NAME | DESCRIPTION                                                                                                                           |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1    | QE2      | TRANSISTOR EMITTER 2. Connects to the emitter of Q4.                                                                                  |

| 2    | DCT      | DC TERMINATION. Provides DC termination to the telephone network.                                                                     |

| 3    | IGND     | ISOLATED GROUND.  Connects to ground on the line-side interface. Also connects to capacitor C2.                                       |

| 4    | C1B      | ISOLATION CAPACITOR 1B.  Connects to one side of isolation capacitor C1. Used to communicate with the system-side module.             |

| 5    | RNG1     | RING 1.  Connects through a capacitor to the TIP lead of the telephone line. Provides the ring and caller ID signals to the PCT308W.  |

| 6    | RNG2     | RING 2.  Connects through a capacitor to the RING lead of the telephone line. Provides the ring and caller ID signals to the PCT308W. |

| 7    | QB       | TRANSISTOR BASE. Connects to the base of transistor Q3. Used to go on/off-hook.                                                       |

| 8    | QE       | TRANSISTOR EMITTER. Connects to the emitter of transistor Q3. Used to go on/off-hook.                                                 |

| 9    | VREG     | Voltage Regulator. Connects to an external capacitor to provide bypassing for an internal power supply.                               |

| 10   | VREG2    | Voltage Regulator 2. Connects to an external capacitor to provide bypassing for an internal power supply.                             |

| 11   | REF      | REFERENCE.  Connects to an external resistor to provide a high accuracy reference current.                                            |

| 12   | REXT2    | EXTERNAL RESISTOR 2. Sets the complex AC termination impedance.                                                                       |

| 13   | REXT     | EXTERNAL RESISTOR. Sets the real AC termination impedance.                                                                            |

| 14   | RX       | RECEIVE INPUT. Serves as the receive side input from the telephone network.                                                           |

| 15   | FILT     | FILTER. Provides filtering for the DC termination circuits.                                                                           |

| 16   | FILT2    | FILTER 2. Provides filtering for the bias circuits.                                                                                   |

# functional description

SPRS004 - SEPTEMBER 2001

# TMS320C54V90 DSP and memory

The DSP is a 16-bit processor operating at up to 117 MIPS. It has 40K x 16 RAM and 128K x 16 program ROM on-chip. This provides complete "controller-based" modem functionality with no external memory.

The DSP firmware implements all the modem signal processing, V.42 error correction, V.42bis compression, AT command parser, and modem controller functions.

# block diagram

Figure 1. TMS320C54V90 Modem Block Diagram

#### PCT308W silicon DAA

The DAA block provides all the functions associated with the telephone line interface and the analog front end, including:

- On hook/off hook control

- DC termination

- AC termination

- Ring detect

- Dielectric isolation

- Surge protection

- Loop current monitor

- 2-wire/4-wire hybrid

- Receive and Transmit filters

- D/A and A/D converters

- On-hook loop voltage sensing (optional)

#### PCT308W silicon DAA (continued)

Certain characteristics of the DAA, such as DC and AC termination, are programmable to meet the requirements of different countries/administrations. Normally, these details are invisible to the user, and the proper characteristics are selected using an AT command and a country code.

Likewise, call origination, dialing, automatic answering, etc. are controlled by AT commands, and the TMS320C54V90 firmware controls the details of DAA functions. The DAA also supports power-down and wake-up-on-ring modes.

The interface between the DSP and the DAA carries both Transmit and Receive line signals as digitized samples, as well as control information for the DAA.

#### mode selection

The CLKMD inputs select various initial conditions for the clocking system and PLLs at power-up. The TMS320C54V90 also uses these inputs to select various operating modes. Use of any of the "reserved" combinations may prevent proper operation of the modem (for example, by disabling the crystal oscillator).

MODE CKLMD1 CLKMD2 **CLKMD3** CONFIGURATION 0 0 0 0 reserved 1 0 0 1 reserved 2 0 1 0 reserved 3 0 1 1 reserved 4 1 0 0 reserved 5 1 0 1 Normal mode, 117 MIPS 6 1 1 0 reserved 7 1 1 1 Normal mode, 58 MIPS

Table 3. Mode Selection with CLKMD pins

# clock requirements

The standard reference design includes a crystal from which clocks are derived for the DSP and the DAA. The nominal clock frequency is 14.7456 MHz.

#### power requirements

The TMS320C54V90 requires 3.3V for the DSP I/Os and the DAA, 1.5V for the DSP core, and 5V for the capacitively-coupled interface between the DSP and DAA. The method of deriving these different voltages will depend on what power is available in the host system, cost, and efficiency considerations.

The reference design assumes that an active low power-on reset signal at 3.3V logic levels is available from the host system.

#### serial and parallel interface modes

The TMS320C54V90 modem can interface with the host system either serially, via an RS-232 connection, or in parallel, via the HPI.

The selection between these two types of interfaces is made using the PAR/SER (HPIENA) input pin.

For either interface, the same set of pins are used, but with different functionality.

Table 4 shows the functionality of the modem host interface pins in both the serial and parallel interface modes.

# serial and parallel interface modes (continued)

Details of the operation of both these types of host interface are presented the following sections of this document.

Table 4. I/O Definition for Serial and Parallel Modes

| SIGNAL NAME | FUNCTION IN PARALLEL MODE (HPIENA=3.3V) | FUNCTION IN SERIAL MODE (HPIENA=0V) |

|-------------|-----------------------------------------|-------------------------------------|

| UARTRX      | Not Used                                | TXD (Serial Transmit Data)          |

| UARTTX      | Modem Constellation X/Y Data            | RXD (Serial Receive Data)           |

| HD0         | Host Port Data Bus bit 0                | DTR (Data Terminal Ready)           |

| HD1         | Host Port Data Bus bit 1                | RTS (Request to Send)               |

| HD2         | Host Port Data Bus bit 2                | CTS (Clear to Send)                 |

| HD3         | Host Port Data Bus bit 3                | DSR (Data Set Ready)                |

| HD4         | Host Port Data Bus bit 4                | DCD (Data Carrier Detect)           |

| HD5         | Host Port Data Bus bit 5                | RI (Ring Indication)                |

| HD6         | Host Port Data Bus bit 6                | Not Used                            |

| HD7         | Host Port Data Bus bit 7                | Not Used                            |

| HCNTL0      | Host Port Control 0                     | Not Used                            |

| HCNTL1      | Host Port Control 1                     | Not Used                            |

| HBIL        | Byte Order Identifier                   | Not Used                            |

| HCS         | Chip Select                             | Not Used                            |

| HDS1        | Data Strobe 1                           | Not Used                            |

| HDS2        | Data Strobe2                            | Not Used                            |

| HAS         | Address Strobe                          | Not Used                            |

| HR/W        | Read/Write                              | Not Used                            |

| HRDY        | Host Port Ready                         | Not Used                            |

| HINT        | Host Port Interrupt                     | Not Used                            |

## serial interface

If the PAR/SER input is held low when RESET is released, the modem will operate with a serial interface instead of a parallel interface. The HD0-7 pins become general purpose I/O pins and are used for EIA-232 control signals as shown in Table 4 on page 14. The serial data is carried on SERIAL TRANSMIT DATA and SERIAL RECEIVE DATA. These signals are at 3.3V logic levels, and the polarity is correct for inverting EIA-232 drivers and receivers.

The serial interfaced is implemented with an on-chip UART. Data rates from 300 bits per second to 230400 bits per second are supported. The default rate is 115200 bits per second. Autobaud (automatic detection of data rate and character format) is not supported. The character format is 10 bit, i.e., 1 start, 8 data, and 1 stop bit. Both RTS/CTS and XON/XOFF flow control are supported.

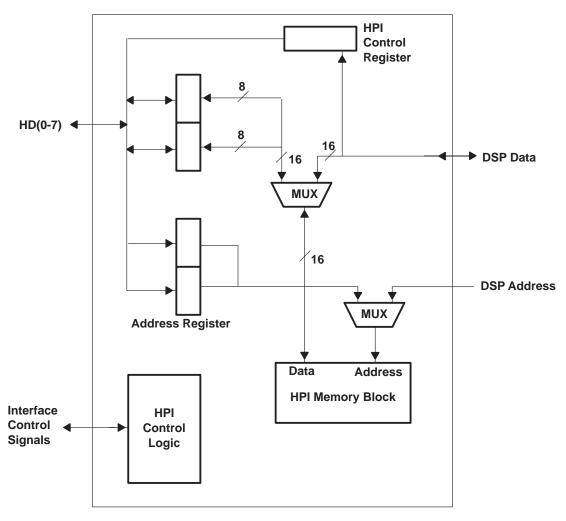

# host port interface (HPI)

The host port interface (HPI) is an 8-bit parallel port used to interface a host processor to the DSP. Information is exchanged between the DSP and the host processor through a 2K-word block of on-chip memory that is accessible by both the host and the DSP. The DSP has access to the HPI control register (HPIC) and the host can address the HPI memory through the HPI address register (HPIA).

Both the host and the DSP have access to the on-chip RAM at all times and host accesses are always synchronized to the DSP clock. If the host and the DSP contend for access to the same location, the host has priority, and the DSP waits for one HPI cycle.

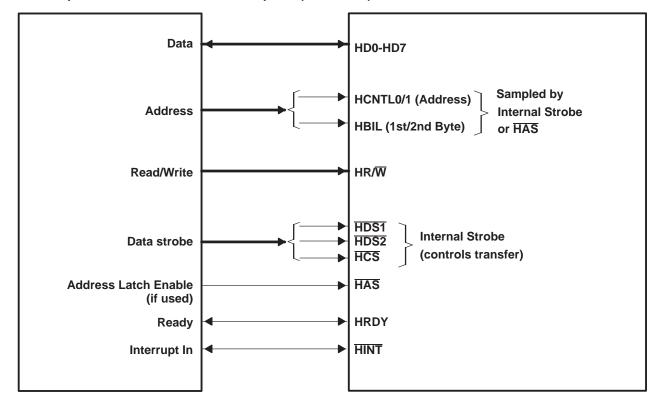

Figure 2. Host Processor Interface Block Diagram

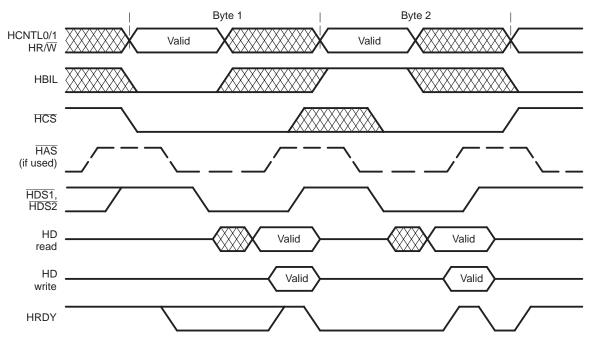

The HPI interface consists of an 8-bit bidirectional data bus and various control signals. Data transfers of 16-bit words occur as two consecutive bytes with a dedicated pin (HBIL) indicating whether the high or low byte is being transmitted. Two control pins, HCNTL1 and HCNTL0, control host access to the HPIA, HPI data (with an optional automatic address increment), or the HPIC. The host can interrupt the DSP device by writing to HPIC. The DSP device can interrupt the host with a dedicated HINT pin that the host can acknowledge and clear.

# TMS320C54V90 EMBEDDED V.90 MODEM DSP OVERVIEW

SPRS004 - SEPTEMBER 2001

# host port interface (HPI) (continued)

The HPI control logic has two data strobes, HDS1 and HDS2, a read/write strobe HR/W, and an address strobe HAS, to enable a glueless interface to a variety of industry-standard host devices. The HPI is interfaced easily to hosts with multiplexed address/data bus, separate address and data buses, one data strobe and a read/write strobe, or two separate strobes for read and write. The HPI supports high-speed back-to-back accesses.

The HPI can handle one byte every five DSP device periods-that is, 64 Mbps with a 40-MIPS DSP, or 160 Mbps with a 100-MIPS DSP. The HPI is designed so that the host can take advantage of this high bandwidth and run at frequencies up to (f \* n)/5, where n is the number of host cycles for an external access and f is the DSP device frequency.

#### basic host port interface functional description

The external HPI consists of the 8-bit HPI data bus and control signals that configure and control the interface. The interface can connect to a variety of host devices with little or no additional logic. Figure 3 shows a simplified diagram of a connection between the HPI and a host device. The 8-bit data bus (HD0-HD7) exchanges information with the host. Because of the 16-bit word structure of the DSP, all transfers with a host must consist of two consecutive bytes. The dedicated HBIL pin indicates whether the first or second byte is being transferred. An internal control register bit determines whether the first or second byte is placed into the most significant byte of a 16-bit word. The host must not break the first byte/second byte (HBIL low/high) sequence of an ongoing HPI access. If this sequence is broken, data can be lost, and unpredictable operation can result.

The two control inputs (HCNTL0 and HCNTL1) indicate which internal HPI register is being accessed and the type of access to the register. These inputs, along with HBIL, are commonly driven by host address bus bits or a function of these bits. Using the HCNTL0/1 inputs, the host can specify an access to the HPI control (HPIC) register, the HPI address (HPIA) register (which serves as the pointer into HPI memory), or HPI data (HPID) register. The HPID register can also be accessed with an optional automatic address increment.

The autoincrement feature provides a convenient way of reading or writing to subsequent word locations. In autoincrement mode, a data read causes a postincrement of the HPIA, and a data write causes a preincrement of the HPIA. By writing to the HPIC, the host can interrupt the DSP CPU, and the HINT output can be used by the DSP to interrupt the host. The host can also acknowledge and clear HINT by writing to the HPIC.

### basic host port interface functional description (continued)

Figure 3. Generic System Block Diagram

Table 5 summarizes the three registers that the HPI utilizes for communication between the host device and the DSP CPU and their functions.

**Table 5. HPI Registers Description**

| NAME | DESCRIPTION                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPIA | Directly accessible only by the host. Contains the address in the HPI memory at which the current access occurs.                                                                                                               |

| HPIC | HPI control register. Directly accessible by either the host or by the DSP. Contains control and status bits for HPI operations.                                                                                               |

| HPID | HPI data register. Directly accessible only by the host. Contains the data that was read from the HPI memory if the current access is a read, or the data that will be written to HPI memory if the current access is a write. |

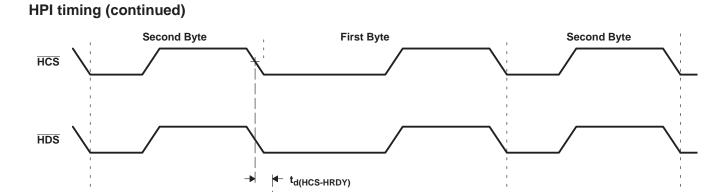

The HPI ready pin (HRDY) allows insertion of wait states for hosts that support a ready input to allow deferred completion of access cycles and have faster cycle times than the HPI can accept due to DSP operating clock rates. If HRDY, when used directly from the DSP, does not meet host timing requirements, the signal can be resynchronized using external logic if necessary. HRDY is useful when the DSP operating frequency is variable, or when the host is capable of accessing at a faster rate than the maximum shared-access mode access rate. In both cases, the HRDY pin provides a convenient way to automatically (no software handshake needed) adjust the host access rate to a faster DSP clock rate.

All of these features combined allow the HPI to provide a flexible and efficient interface to a wide variety of industry-standard host devices. Also, the simplicity of the HPI interface greatly simplifies data transfers both from the host and the DSP sides of the interface. Once the interface is configured, data transfers are made with a minimum of overhead at a maximum speed.

# TMS320C54V90 **EMBEDDED V.90 MODEM DSP OVERVIEW**

SPRS004 - SEPTEMBER 2001

### details of host port interface operation

This subsection includes a detailed description of each HPI external interface pin function, as well as descriptions of the register and control bit functions. Logical interface timings and initialization and read/write sequences are discussed in section, Host Read/Write Access to HPI.

The external HPI interface signals implement a flexible interface to a variety of types of host devices. Devices with single or multiple data strobes and with or without address latch enable (ALE) signals can easily be connected to the HPI.

# HPI signal names and functions

Table 6 describes the function HPI external interface pins in detail.

#### **Table 6. HPI Signal Names and Functions**

| HPI PIN          | HOST PIN                                                           | STATE† | SIGNAL FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HAS              | Address latch enable (ALE) or Address strobe or unused (tied high) | I      | Address strobe input. Hosts with a multiplexed address and data bus connect HAS to their ALE pin or equivalent. HBIL, HCNTL0/1, and HR/W are then latched on HAS falling edge. When used, HAS must precede the later of HCS, HDS1, or HDS2 (see detailed HPI timing specifications on page 29). Hosts with separate address and data bus can connect HAS to a logic-1 level. In this case, HBIL, HCNTL0/1, and HR/W are latched by the later of HDS1, HDS2, or HCS falling edge while HAS stays inactive (high).                                                                                                                                                                                                                                      |

| HBIL             | Address or control lines                                           | I      | Byte identification input. Identifies first or second byte of transfer (but not most significant or least significant - this is specified by the BOB bit in the HPIC register, described later in this section). HBIL is low for the first byte and high for the second byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HCNTL0<br>HCNTL1 | Address or control lines                                           | I      | Host control inputs. Selects a host access to the HPIA register, the HPI data latches (with optional address increment), or the HPIC register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

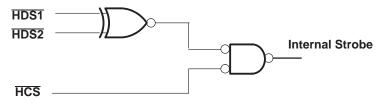

| HCS              | Address or control lines                                           | I      | Chip select. Serves as the enable input for the HPI and must be low during an access but may stay low between accesses. HCS normally precedes HDS1 and HDS2, but this signal also samples HCNTL0/1, HR/W, and HBIL if HAS is not used and HDS1 or HDS2 are already low (this is explained in further detail later in this subsection). Table 7 shows the equivalent circuit of the HCS, HDS1 and HDS2 inputs.                                                                                                                                                                                                                                                                                                                                         |

| HD0-HD7          | Data bus                                                           | I/O/Z  | Parallel bidirectional 3-state data bus. HD7 (MSB) through HD0 (LSB) are placed in the high-impedance state when not outputting (HDS   HCS = 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

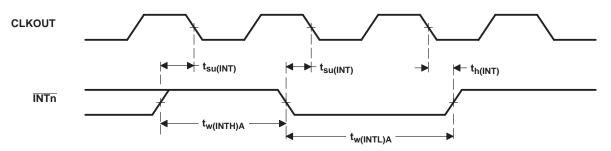

| HDS1<br>HDS2     | Read strobe and<br>write strobe or<br>data strobe                  | I      | Data strobe inputs. Control transfer of data during host access cycles. Also, when HAS is not used, used to sample HBIL, HCNTL0/1, and HR/W when HCS is already low (which is the case in normal operation). Hosts with separate read and write strobes connect those strobes to either HDS1 or HDS2. Hosts with a single data strobe connect it to either HDS1 or HDS2, connecting the unused pin high. Regardless of HDS connections, HR/W is still required to determine direction of transfer. Because HDS1 and HDS2 are internally exclusive-NORed, hosts with a high true data strobe can connect this to one of the HDS inputs with the other HDS input connected low. Table 7 shows the equivalent circuit of the HDS1, HDS2, and HCS inputs. |