#### features

- Low Dropout Voltage Regulator, 1.2-V

- 150-mA Load Current Capability

- Power Okay (POK) Function

- Load Independent, Low Ground Current, 150-uA

- Current Limiting

- Thermal Shutdown

- Low Sleep State Current (Off Mode)

- Fast Transient Response

- Low Variation Due to Load and Line Regulation

- Output Stable With Low ESR Capacitors

- TTL Logic Controlled Enable Input

### applications

- Processor Powerup Sequencing

- Palmtop Computers, Laptops, and Notebooks

#### description

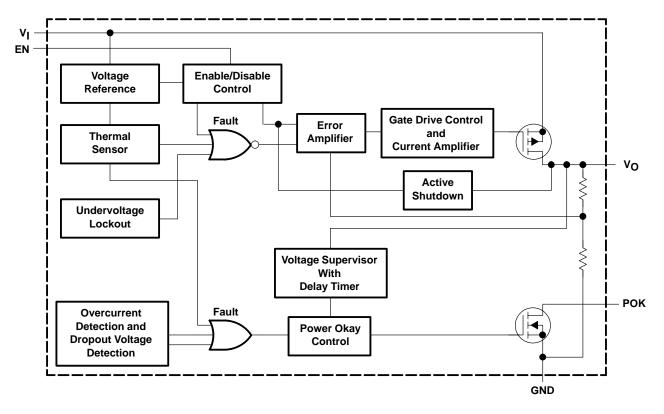

The TPPM0125 is a low dropout voltage regulator with an output tolerance of  $\pm 2\%$  over the operating range. The device is optimized for low noise applications and has a low quiescent current (enable <0.8 V). The device has a low dropout voltage at full load (150 mA). The power okay function monitors the output voltage and indicates when an error occurs in the system (active low). In the event of an output fault such as overcurrent, thermal shutdown, or dropout, the power okay output is pulled low (open drain).

The TPPM0125 has a fast transient response recovery capability in the event of load transition from heavy load to light load. The device also minimizes overshoot during this condition. During power down, the output capacitor and load are de-energized through the internal active shutdown clamp, which is turned on when the device is disabled.

The TPPM0125 requires a small output capacitor for stability with low ESR. An input capacitor is not required unless the bulk ac capacitor is placed away from the device or the power supply is a battery. In this situation, a 1-µF capacitor is recommended for the application. Low ESR ceramic capacitors may be used with the device to reduce board space in power applications, a key concern in hand-held wireless devices.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## functional block diagram

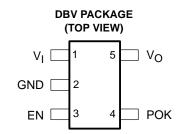

#### **Terminal Functions**

| TERMINAL |     | 1/0 | DESCRIPTION                     |  |

|----------|-----|-----|---------------------------------|--|

| NAME     | NO. | 1/0 | DESCRIPTION                     |  |

| EN       | 3   | 1   | le/shutdown input (active high) |  |

| GND      | 2   | - 1 | nd                              |  |

| POK      | 4   | 1   | r okay indicator                |  |

| VI       | 1   | 1   | Input supply voltage            |  |

| VO       | 5   | 0   | Output voltage                  |  |

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Main input voltage range, V <sub>I</sub> (see Notes 1 and 2)                 | 0 V to 7 V           |

|------------------------------------------------------------------------------|----------------------|

| Enable input voltage range, V <sub>(EN)</sub> (see Notes 1 and 2)            |                      |

| Power okay output voltage range V <sub>(POK)</sub> , (see Notes 1 and 2)     | 0 V – V <sub>I</sub> |

| Regulated output current limit, IO `                                         | 400 mA               |

| Continuous power dissipation, P <sub>D</sub> , T <sub>A</sub> = 25°C         | 0.5 W                |

| Electrostatic discharge susceptibility, V <sub>(HBMESD)</sub> , (see Note 3) | 2 kV                 |

| Junction temperature, T <sub>J</sub> ,                                       |                      |

| Storage temperature range, T <sub>stq</sub>                                  | –55°C to 150°C       |

| Lead temperature (soldering, 10 sec)                                         |                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to GND.

- 2. Absolute negative voltage on these terminals should not go below -0.5 V.

- 3. The human body model is a 100-pF capacitor discharged through a 1.5-kΩ resistor into each terminal. Devices are ESD sensitive. Handling precautions are recommended.

#### recommended operating conditions

|                                                             | MIN | TYP MAX | UNIT |

|-------------------------------------------------------------|-----|---------|------|

| Main input voltage, V <sub>I</sub> (see Notes 1 and 2)      | 3   | 5.25    | V    |

| Enable input voltage, V <sub>(EN)</sub> (see Notes 1 and 2) | 0   | VI      | V    |

| Power okay voltage, V <sub>(POK)</sub> (see Notes 1 and 2)  | 0   | VI      | V    |

| Operating ambient temperature, TA                           | 0   | 70      | °C   |

NOTES: 1. All voltage values are with respect to GND.

2. Absolute negative voltage on these terminals should not go below –0.5 V.

# $electrical\,characteristics, T_{A}=25^{\circ}C, V_{I}=5\,V, V_{\left(EN\right)}=V_{I}, I_{O}=100\,\mu\text{A}, C_{L}=1\,\mu\text{F(unless otherwise noted)}$

#### regulator VO

|                    | PARAMETER                                | TEST CONDITIONS                                          | MIN | TYP | MAX | UNITS |  |

|--------------------|------------------------------------------|----------------------------------------------------------|-----|-----|-----|-------|--|

|                    | Output voltage                           | I <sub>O</sub> = 25 mA                                   |     | 1.2 |     | V     |  |

| ٧o                 |                                          | IO = 0                                                   | -1% |     | 1%  |       |  |

|                    | Output voltage accuracy                  | $I_O = 50$ mA, $T_A = 0$ °C to 70°C (see Note 4)         | -2% |     | 2%  |       |  |

| IQ                 | Quiescent supply current                 | $V_{(EN)} \le 0.8 \text{ V}$                             |     | 1   |     | μΑ    |  |

| I <sub>(GND)</sub> | Ground terminal current (see Note 5)     | IO = 0                                                   |     | 150 |     | μΑ    |  |

|                    |                                          | I <sub>O</sub> = 150 mA                                  |     | 150 |     |       |  |

| IL                 | Output load current                      |                                                          | 150 |     |     | mA    |  |

| I(Limit)           | Output current limit                     | V <sub>O</sub> = 0                                       | 160 | 300 |     | mA    |  |

| $\Delta V(LNR)$    | Line regulation                          | V <sub>I</sub> = 3 V to 5.25 V                           |     | 10  |     | mV    |  |

| $\Delta V$ (LDR)   | Load regulation                          | I <sub>O</sub> = 0.1 mA to150 mA, See Note 6             |     | 2%  | 3%  |       |  |

| ., .,              |                                          | I <sub>O</sub> = 100 μA                                  |     | 1   |     | .,    |  |

| VI – VO            | Dropout voltage                          | I <sub>O</sub> = 150 mA                                  |     | 1   |     | V     |  |

| CL                 | Load capacitance                         | ESR and capacitance tradeoffs                            |     | 1   |     | μF    |  |

| I <sub>(REV)</sub> | Reverse output current on V <sub>I</sub> | V <sub>I</sub> = GND, V <sub>O</sub> = regulated voltage |     |     | 50  | μΑ    |  |

NOTES: 4. Assured by design, not tested in production.

- 5. Ground terminal current is the regulator quiescent current drawn from the supply to support the load current.

- 6. Regulation is measured at constant junction temperature using low duty cycle pulse testing. Devices are tested for load regulation in the load range from 0.1 mA to 150 mA.

#### enable input

|                   | PARAMETER            | TEST CONDITIONS                                   | MIN | TYP  | MAX | UNITS |

|-------------------|----------------------|---------------------------------------------------|-----|------|-----|-------|

| $V_{IL}$          | Regulated shutdown   | V <sub>I</sub> = 3 V to 5.25 V regulated shutdown |     |      | 0.8 | V     |

| $V_{IH}$          | Regulated enabled    | V <sub>I</sub> = 3 V to 5.25 V regulated enabled  | 2   |      |     | V     |

| I <sub>(EN)</sub> |                      | Shutdown, V <sub>IL</sub> ≤ 0.8 V                 |     | 0.01 |     |       |

|                   | Enable input current | Enabled, V <sub>IH</sub> ≥ 2 V                    |     | 0.01 |     | μΑ    |

|                   | Resistance discharge | V <sub>(EN)</sub> ≤ 0.8 V                         |     | 500  |     | Ω     |

#### thermal protection (see Note 4)

|                   | PARAMETER        | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------|------------------|-----------------|-----|-----|-----|-------|

| T <sub>(SD)</sub> | Thermal shutdown |                 |     | 165 |     | °C    |

| T(SDHYS)          | Hysteresis       |                 |     | 15  |     | °C    |

NOTE 4: Assured by design, not tested in production.

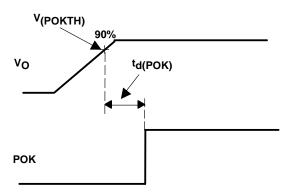

#### power okay (see Note 7)

| PARAMETER        |                      | TEST CONDITIONS                                         |     | TYP | MAX | UNITS |

|------------------|----------------------|---------------------------------------------------------|-----|-----|-----|-------|

| V(POKLO)         | Low threshold        | Output falls % of VO (power NOT okay)                   | 85% |     |     |       |

| V(POKTH)         | High threshold       | Output reaches % of VO, starts delay timer (power okay) | 90% |     |     |       |

| VOL              | VO out of regulation | Fault condition, $I_{OL} = 100 \mu A$                   |     |     | 0.4 | V     |

| l <sub>lkg</sub> | Leakage current      | V <sub>I</sub> = 5 V                                    |     |     | 1   | μΑ    |

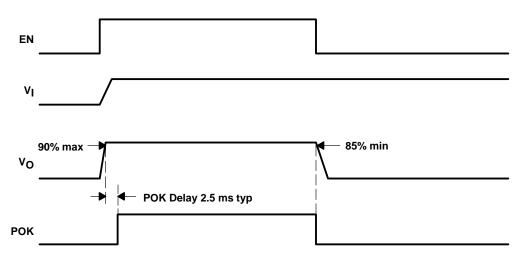

NOTE 7: Power okay is a function of the output voltage being 5% lower than the specified range. The function is a detection of one of the following: over current, over temperature, or dropout.

# switching characteristics (see Note 4), $T_A = 25^{\circ}C$ , $V_I = 5$ V, $V_{(EN)} = V_I$ , $I_O = 100~\mu A$ , $C_L = 1~\mu F$ (unless otherwise noted)

|                      | PARAMETER                      | TEST CONDITIONS                                               | MIN | TYP | MAX | UNIT  |

|----------------------|--------------------------------|---------------------------------------------------------------|-----|-----|-----|-------|

|                      | Power up overshoot             | Maximum voltage overshoot allowed on output during powerup    |     | 1%  |     |       |

| t(STEP)              | Output transient time limit    | Time for output to return within specified regulation range   |     | 5   |     | μs    |

|                      | Output transient voltage limit | Voltage that load step can affect the nominal output voltage  |     | 1%  |     |       |

| I <sub>(SR)</sub>    | Load step current slew rate    | $I_L = 0.1 \text{ mA to } 150 \text{ mA}$                     |     | 10  |     | mA/μs |

| t <sub>r</sub>       | Power up rise time             |                                                               |     | 50  |     | μs    |

| t <sub>f</sub>       | Power down fall time           | Discharge resistance = 500 $\Omega$ , V <sub>O</sub> < 1.08 V |     | 60  |     | μs    |

| t <sub>d</sub> (POK) | Power okay delay time          | V <sub>I</sub> > V <sub>(POKTH)</sub> until POK↑              |     | 2.5 |     | ms    |

NOTE 4: Assured by design, not tested in production.

#### thermal resistance

|                 | PARAMETER                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------|-----------------|-----|-----|-----|------|

| $R_{\theta JC}$ | Thermal impedance, junction-to-case    |                 |     | 145 |     | °C/W |

| $R_{\thetaJA}$  | Thermal impedance, junction-to-ambient |                 |     | 235 |     | °C/W |

#### PARAMETER MEASUREMENT INFORMATION

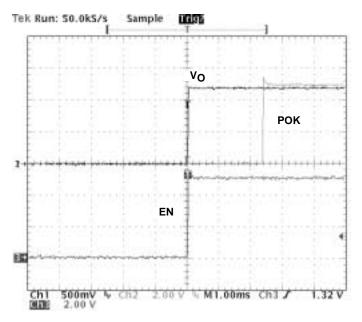

Figure 1. Power Okay Timing During Power Up

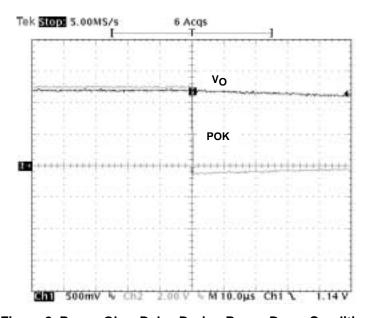

Figure 2. Power Okay Delay Timing and Output Voltage Supervisory

#### **TYPICAL CHARACTERISTICS**

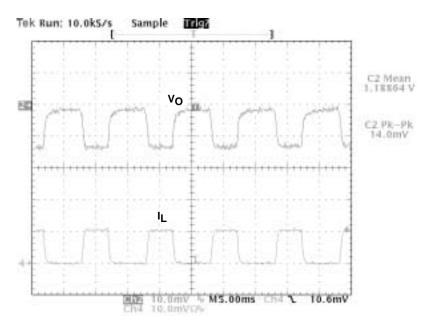

Figure 3. Load Regulation, 50-mA Dynamic Load Step (V<sub>I</sub> = 3 V)

Figure 4. Load Regulation, 150-mA Dynamic Load Step (V<sub>I</sub> = 3 V)

#### **TYPICAL CHARACTERISTICS**

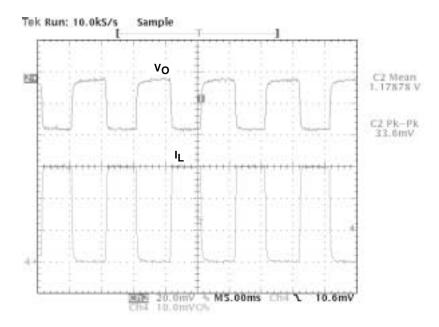

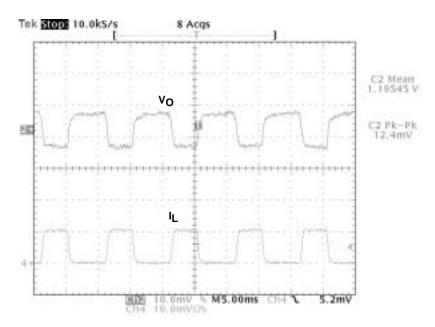

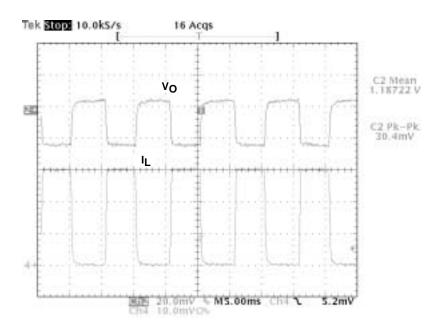

Figure 5. Load Regulation, 50-mA Dynamic Load Step (V<sub>I</sub> = 5 V)

Figure 6. Load Regulation, 150-mA Dynamic Load Step (V<sub>I</sub> = 5 V)

#### **TYPICAL CHARACTERISTICS**

Figure 7. Power Okay Delay During Power Up Condition

Figure 8. Power Okay Delay During Power Down Condition

#### THERMAL INFORMATION

The TPPM0125 is designed to provide a continuous load current of 150 mA when the maximum power dissipation of the package is not exceeded in the application. To determine the maximum power dissipation of the package, use the junction-to-ambient thermal resistance of the device. The basic equation is as follows:

Maximum power dissipation (W)

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / R_{\theta JA}$$

(maximum power dissipation limit)

Where:

$T_{J(MAX)}$  is the maximum junction temperature of the die (less than 150°C, minimum thermal shutdown)  $T_A$  is the operating ambient temperature

$R_{\theta JA}$  is the thermal resistance and is layout dependent

The recommended minimum footprint offers a  $R_{\theta JA}$  of 235°C/W.

To determine the actual power dissipation of the regulator, use the following equation:

$$P_D = (V_I - V_O) I_O + V_I I_{(GND)} \text{ (Watts)}$$

Power dissipation resulting from quiescent current is negligible. When the power dissipation is excessive, the thermal protection circuit is triggered.

#### **APPLICATION INFORMATION**

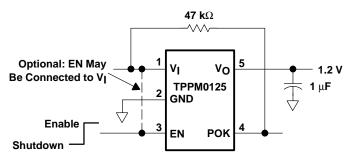

Figure 9. Typical Application Schematic

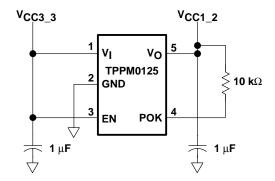

Figure 10. Typical Application For Processor VID Code Power Sequencing Schematic

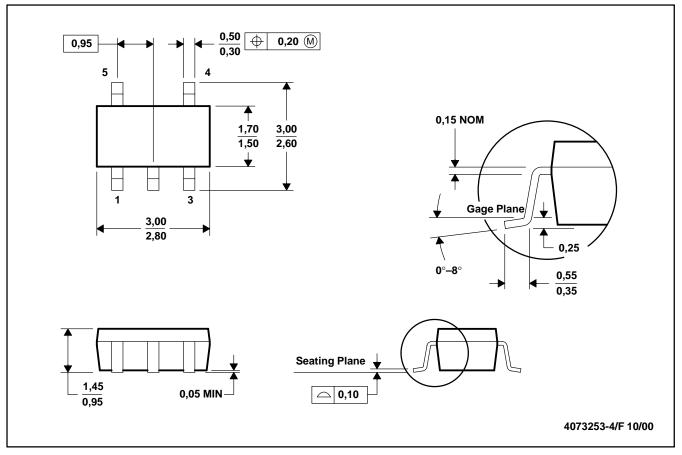

#### **MECHANICAL DATA**

#### DBV (R-PDSO-G5)

#### **PLASTIC SMALL-OUTLINE**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-178

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265