SLOS270B - MARCH 2001 - REVISED JANUARY 2002

**Operational Amplifier**

- Rail-To-Rail Input/Output

- Wide Bandwidth . . . 3 MHz

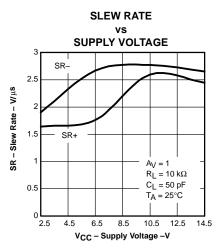

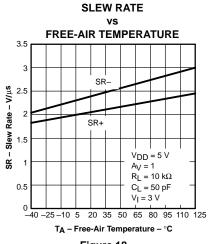

- High Slew Rate . . . 2.4 V/μs

- Supply Voltage Range . . . 2.7 V to 16 V

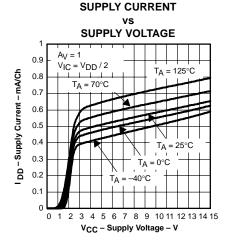

- Supply Current . . . 550 μA/Channel

- Low Power Shutdown Mode

I<sub>DD</sub>(SHDN) . . . 25 μA/Channel

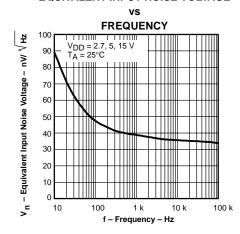

- Input Noise Voltage . . . 39 nV/√Hz

- Input Bias Current . . . 1 pA

- Specified Temperature Range -40°C to 125°C . . . Industrial Grade

- Ultrasmall Packaging

- 5 or 6 Pin SOT-23 (TLV2370/1)

- 8 or 10 Pin MSOP (TLV2372/3)

The CMOS inputs enable use in high-impedance sensor interfaces, with the lower voltage operation making an ideal alternative for the TLC227x in battery-powered applications. The rail-to-rail input stage further increases its versatility. The TLV237x is the seventh member of a rapidly growing number of RRIO products available from TI, and it is the first to allow operation up to 16-V rails with good ac performance.

All members are available in PDIP and SOIC with the singles in the small SOT-23 package, duals in the MSOP, and quads in the TSSOP package.

The 2.7-V operation makes the TLV237x compatible with Li-lon powered systems and the operating supply voltage range of many micro-power microcontrollers available today including TI's MSP430.

#### SELECTION OF SIGNAL AMPLIFIER PRODUCTS<sup>†</sup>

| DEVICE  | V <sub>DD</sub> (V) | V <sub>IO</sub><br>(μV) | lq/Ch<br>(μA) | I <sub>IB</sub> (pA) | GBW<br>(MHz) | SR<br>(V/μs) | SHUTDOWN | RAIL-<br>TO-<br>RAIL | SINGLES/DUALS/QUADS |

|---------|---------------------|-------------------------|---------------|----------------------|--------------|--------------|----------|----------------------|---------------------|

| TLV237x | 2.7–16              | 500                     | 550           | 1                    | 3            | 2.4          | Yes      | I/O                  | S/D/Q               |

| TLC227x | 4–16                | 300                     | 1100          | 1                    | 2.2          | 3.6          | _        | 0                    | D/Q                 |

| TLV27x  | 2.7–16              | 500                     | 550           | 1                    | 3            | 2.4          | _        | 0                    | S/D/Q               |

| TLC27x  | 3–16                | 1100                    | 675           | 1                    | 1.7          | 3.6          | _        | _                    | S/D/Q               |

| TLV246x | 2.7–6               | 150                     | 550           | 1300                 | 6.4          | 1.6          | Yes      | I/O                  | S/D/Q               |

| TLV247x | 2.7–6               | 250                     | 600           | 2                    | 2.8          | 1.5          | Yes      | I/O                  | S/D/Q               |

| TLV244x | 2.7–10              | 300                     | 725           | 1                    | 1.8          | 1.4          | _        | 0                    | D/Q                 |

<sup>†</sup> Typical values measured at 5 V, 25°C

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### **FAMILY PACKAGE TABLE**

| DEVICE  | NUMBER OF |      | PAC  | KAGE TY | PES   |      | SHUTDOWN | UNIVERSAL                           |  |

|---------|-----------|------|------|---------|-------|------|----------|-------------------------------------|--|

| DEVICE  | CHANNELS  | PDIP | SOIC | SOT-23  | TSSOP | MSOP | SHUTDOWN | EVM BOARD                           |  |

| TLV2370 | 1         | 8    | 8    | 6       |       |      | Yes      |                                     |  |

| TLV2371 | 1         | 8    | 8    | 5       |       |      |          |                                     |  |

| TLV2372 | 2         | 8    | 8    | _       | _     | 8    | _        | Refer to the EVM<br>Selection Guide |  |

| TLV2373 | 2         | 14   | 14   | _       | _     | 10   | Yes      | (Lit# SLOU060)                      |  |

| TLV2374 | 4         | 14   | 14   | _       | 14    | _    | _        |                                     |  |

| TLV2375 | 4         | 16   | 16   | _       | 16    | _    | Yes      |                                     |  |

#### TLV2370 and TLV2371 AVAILABLE OPTIONS

| TA             |                        | PACKAGED DEVICES       |                            |              |                        |  |  |  |

|----------------|------------------------|------------------------|----------------------------|--------------|------------------------|--|--|--|

|                | V <sub>IO</sub> MAX AT | SMALL OUTLINE          | SOT-23                     | 3            | PLASTIC DIP            |  |  |  |

|                | 25 0                   | (D) <sup>†</sup>       | (DBV) <sup>‡</sup>         | SYMBOL       | (P)                    |  |  |  |

| -40°C to 125°C | 4.5 mV                 | TLV2370ID<br>TLV2371ID | TLV2370IDBV<br>TLV2371IDBV | VBFI<br>VBGI | TLV2370IP<br>TLV2371IP |  |  |  |

This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLV2370IDR).

#### **TLV2372 AND TLV2373 AVAILABLE OPTIONS**

|                      | V <sub>IO</sub> MAX AT<br>25°C |                        | PACKAGED DEVICES |          |                 |          |               |                |  |  |  |

|----------------------|--------------------------------|------------------------|------------------|----------|-----------------|----------|---------------|----------------|--|--|--|

| TA                   |                                | SMALL                  | MSOP             |          |                 |          | PLASTIC       | PLASTIC        |  |  |  |

|                      |                                | OUTLINE<br>(D)§        | (DGK)§           | SYMBOL   | (DGS)§          | SYMBOL   | DIP<br>(N)    | DIP<br>(P)     |  |  |  |

| -40°C<br>to<br>125°C | 4.5 mV                         | TLV2372ID<br>TLV2373ID | TLV2372IDGK<br>— | APG<br>— | <br>TLV2373IDGS | —<br>API | <br>TLV2373IN | TLV2372IP<br>— |  |  |  |

<sup>§</sup> This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLV2372IDR).

#### TLV2374 and TLV2375 AVAILABLE OPTIONS

|                | V 144 V 4T                     | PACKAGED DEVICES       |                        |                          |  |  |

|----------------|--------------------------------|------------------------|------------------------|--------------------------|--|--|

| TA             | V <sub>IO</sub> MAX AT<br>25°C | SMALL OUTLINE<br>(D)¶  | PLASTIC DIP<br>(N)     | TSSOP<br>(PW)¶           |  |  |

| -40°C to 125°C | 4.5 mV                         | TLV2374ID<br>TLV2375ID | TLV2374IN<br>TLV2375IN | TLV2374IPW<br>TLV2375IPW |  |  |

This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLV2374IDR).

<sup>&</sup>lt;sup>‡</sup> This package is only available taped and reeled. For standard quantities (3,000 pieces per reel), add an R suffix (e.g., TLV2370IDBVR). For smaller quantities (250 pieces per mini-reel), add a T suffix to the part number (e.g., TLV2370IDBVT).

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

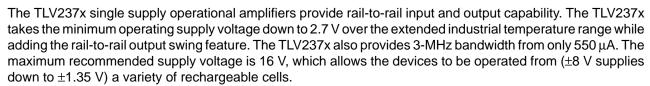

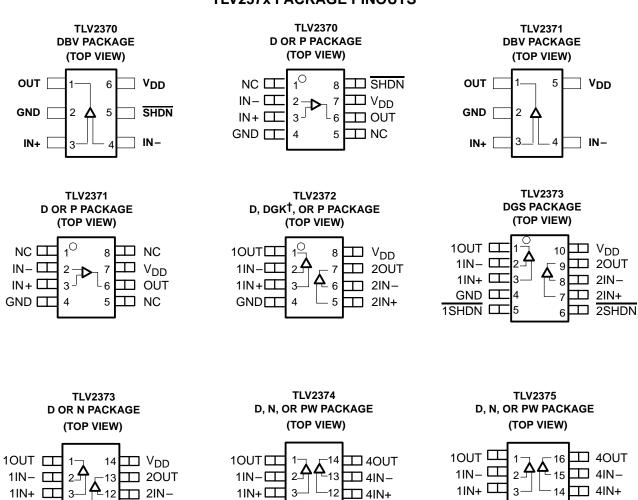

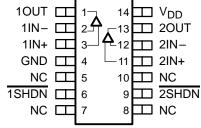

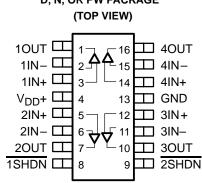

#### **TLV237x PACKAGE PINOUTS**

$V_{DD} \square$

2IN+ □

2IN-□

20UT □

4

5

11 GND

-10 🗀 3IN+

9 ☐ 3IN-

**Ⅲ** 30UT

8

NC - No internal connection

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>DD</sub> (see Note 1)                    |                                  |

|-----------------------------------------------------------------|----------------------------------|

| Differential input voltage, V <sub>ID</sub>                     | ±V <sub>DD</sub>                 |

| Input voltage range, V <sub>I</sub> (see Note 1)                | 0.2 V to V <sub>DD</sub> + 0.2 V |

| Input current range, I <sub>I</sub>                             | ±10 mA                           |

| Output current range, I <sub>O</sub>                            | ±100 mA                          |

| Continuous total power dissipation                              | See Dissipation Rating Table     |

| Operating free-air temperature range, T <sub>A</sub> : I suffix | –40°C to 125°C                   |

| Maximum junction temperature, T <sub>J</sub>                    | 150°C                            |

| Storage temperature range, T <sub>stq</sub>                     | 65°C to 150°C                    |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    | 260°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### NOTE 1: All voltage values, except differential voltages, are with respect to GND.

#### **DISSIPATION RATING TABLE**

| PACKAGE    | θJC<br>(°C/W) | θJA<br>(°C/W) | T <sub>A</sub> ≤ 25°C<br>POWER RATING |

|------------|---------------|---------------|---------------------------------------|

| D (8)      | 38.3          | 176           | 710 mW                                |

| D (14)     | 26.9          | 122.3         | 1022 mW                               |

| D (16)     | 25.7          | 114.7         | 1090 mW                               |

| DBV (5)    | 55            | 324.1         | 385 mW                                |

| DBV (6)    | 55            | 294.3         | 425 mW                                |

| DGK (8)    | 54.23         | 259.96        | 481 mW                                |

| DGS (10)   | 54.1          | 257.71        | 485 mW                                |

| N (14, 16) | 32            | 78            | 1600 mW                               |

| P (8)      | 41            | 104           | 1200 mW                               |

| PW (14)    | 29.3          | 173.6         | 720 mW                                |

| PW (16)    | 28.7          | 161.4         | 774 mW                                |

#### recommended operating conditions

|                                                                        |               | MIN   | MAX      | UNIT |  |

|------------------------------------------------------------------------|---------------|-------|----------|------|--|

| Supply voltage, V <sub>DD</sub>                                        | Single supply | 2.7   | 16       | V    |  |

|                                                                        | Split supply  | ±1.35 | ±8       | V    |  |

| Common-mode input voltage range, V <sub>ICR</sub>                      |               |       | $V_{DD}$ | V    |  |

| Operating free-air temperature, TA                                     | I-suffix      | -40   | 125      | °C   |  |

| Turnon voltage level, V <sub>(ON)</sub> , relative to GND pin voltage  |               |       | 2        | V    |  |

| urnoff voltage level, V <sub>(OFF)</sub> , relative to GND pin voltage |               |       |          | V    |  |

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

### electrical characteristics at specified free-air temperature, $V_{DD}$ = 2.7 V, 5 V, and 15 V (unless otherwise noted)

#### dc performance

|                 | PARAMETER                         | TEST CONDI                                             | TIONS                   | TA         | MIN | TYP | MAX | UNIT  |

|-----------------|-----------------------------------|--------------------------------------------------------|-------------------------|------------|-----|-----|-----|-------|

| V <sub>IO</sub> | Input offset voltage              | ., ., .,                                               |                         | 25°C       |     | 0.5 | 4.5 | mV    |

| ۷IO             | input onset voitage               | $V_{IC} = V_{DD}/2,$<br>$R_S = 50 \Omega$              | $V_O = V_{DD}/2$ ,      | Full range |     |     | 6   | IIIV  |

| ανιο            | Offset voltage drift              | 7.3 00                                                 |                         | 25°C       |     | 2   |     | μV/°C |

|                 |                                   | $V_{IC} = 0$ to $V_{DD}$ ,                             |                         | 25°C       | 52  | 68  |     |       |

|                 |                                   | $R_S = 50 \Omega$                                      | \/DD = 27\/             | Full range | 51  |     |     |       |

|                 |                                   | $V_{IC} = 0 \text{ to } V_{DD} - 1.35V,$               | V <sub>DD</sub> = 2.7 V | 25°C       | 58  | 70  |     |       |

|                 |                                   | $R_S = 50 \Omega$                                      |                         | Full range | 55  |     |     | dB    |

|                 |                                   | $V_{IC} = 0$ to $V_{DD}$ ,                             |                         | 25°C       | 57  | 72  |     |       |

| CMRR            | Common-mode rejection ratio       | $R_S = 50 \Omega$ ,                                    | V <sub>DD</sub> = 5 V   | Full range | 56  |     |     |       |

|                 | Common-mode rejection ratio       | $V_{IC} = 0 \text{ to } V_{DD} - 1.35V,$               | 1 VDD = 3 V             | 25°C       | 69  | 85  |     |       |

|                 |                                   | $R_S = 50 \Omega$ ,                                    |                         | Full range | 64  |     |     |       |

|                 |                                   | $V_{IC} = 0 \text{ to } V_{DD},$<br>$R_S = 50 \Omega,$ | V 45 V                  | 25°C       | 66  | 82  |     |       |

|                 |                                   |                                                        |                         | Full range | 65  |     |     |       |

|                 |                                   | $V_{IC} = 0 \text{ to } V_{DD} - 1.35V,$               | $V_{DD} = 15 V$         | 25°C       | 69  | 84  |     |       |

|                 |                                   | $R_S = 50 \Omega$ ,                                    |                         | Full range | 66  |     |     |       |

|                 |                                   |                                                        | \/ 27\/                 | 25°C       | 98  | 106 |     |       |

|                 |                                   |                                                        | $V_{DD} = 2.7 V$        | Full range | 76  |     |     | dB    |

| ۸. ۳۰           | Large-signal differential voltage | $V_{O(PP)} = V_{DD}/2$                                 | \/ 5\/                  | 25°C       | 100 | 110 |     |       |

| AVD             | amplification                     | $R_L = 10 \text{ k}\Omega$                             | $V_{DD} = 5 V$          | Full range | 86  |     | ·   |       |

|                 |                                   |                                                        | 45.7                    | 25°C       | 81  | 85  |     |       |

|                 |                                   |                                                        | $V_{DD} = 15 V$         | Full range | 79  |     |     |       |

#### input characteristics

|                   | PARAMETER                     | TEST                                           | CONDITIONS            | TA    | MIN | TYP  | MAX  | UNIT      |

|-------------------|-------------------------------|------------------------------------------------|-----------------------|-------|-----|------|------|-----------|

|                   |                               |                                                |                       | 25°C  |     | 1    | 60   |           |

| lιΟ               | Input offset current          |                                                |                       | 70°C  |     |      | 100  | pΑ        |

|                   |                               | $V_{DD} = 15 V$ ,                              | $V_{IC} = V_{DD}/2$ , | 125°C |     |      | 1000 |           |

|                   |                               | $V_{DD} = 15 \text{ V},$<br>$V_{O} = V_{DD}/2$ |                       | 25°C  |     | 1    | 60   |           |

| I <sub>IB</sub>   | Input bias current            |                                                |                       | 70°C  |     |      | 100  | pΑ        |

|                   |                               |                                                |                       | 125°C |     |      | 1000 |           |

| r <sub>i(d)</sub> | Differential input resistance |                                                |                       | 25°C  |     | 1000 |      | $G\Omega$ |

| C <sub>IC</sub>   | Common-mode input capacitance | f = 21 kHz                                     |                       | 25°C  |     | 8    |      | pF        |

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

### electrical characteristics at specified free-air temperature, $V_{DD}$ = 2.7 V, 5 V, and 15 V (unless otherwise noted) (continued)

#### output characteristics

|      | PARAMETER                 | TEST CONDITIONS                                           |                          | TA         | MIN   | TYP   | MAX  | UNIT |

|------|---------------------------|-----------------------------------------------------------|--------------------------|------------|-------|-------|------|------|

|      |                           |                                                           | V 07V                    | 25°C       | 2.55  | 2.58  |      |      |

|      |                           |                                                           | $V_{DD} = 2.7 V$         | Full range | 2.48  |       |      |      |

|      |                           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                    | V EV                     | 25°C       | 4.9   | 4.93  |      |      |

|      |                           | $V_{IC} = V_{DD}/2$ , $I_{OH} = -1 \text{ mA}$            | $V_{DD} = 5 V$           | Full range | 4.85  |       |      |      |

|      |                           |                                                           | V== - 15 V               | 25°C       | 14.92 | 14.96 |      |      |

| \/a  | High lovel output voltage |                                                           | V <sub>DD</sub> = 15 V   | Full range | 14.9  |       |      | V    |

| VOH  | High-level output voltage |                                                           | V <sub>DD</sub> = 2.7 V  | 25°C       | 2     | 2.1   |      | V    |

|      |                           |                                                           | VDD = 2:1 V              | Full range | 1.6   |       |      |      |

|      |                           | $V_{IC} = V_{DD}/2$ , $I_{OH} = -5 \text{ mA}$            | V22 - 5 V                | 25°C       | 4.6   | 4.68  |      |      |

|      |                           | VIC = VDD/2, $IOH = -3 IIIA$                              | $V_{DD} = 5 V$           | Full range | 4.5   |       |      |      |

|      |                           |                                                           | V== - 15 V               | 25°C       | 14.8  | 14.84 |      |      |

|      |                           |                                                           | $V_{DD} = 15 V$          | Full range | 14.74 |       |      |      |

|      |                           |                                                           | V== - 27V                | 25°C       |       | 0.1   | 0.15 |      |

|      |                           |                                                           | $V_{DD} = 2.7 \text{ V}$ | Full range |       |       | 0.22 |      |

|      |                           | $V_{IC} = V_{DD}/2$ , $I_{OL} = 1 \text{ mA}$             | V== - 5 V                | 25°C       |       | 0.05  | 0.1  |      |

|      |                           |                                                           | $V_{DD} = 5 V$           | Full range |       |       | 0.15 |      |

|      |                           |                                                           | V <sub>DD</sub> = 15 V   | 25°C       |       | 0.05  | 0.08 | V    |

| \/a: | Low-level output voltage  |                                                           |                          | Full range |       |       | 0.1  |      |

| VOL  | Low-level output voltage  |                                                           | V <sub>DD</sub> = 2.7 V  | 25°C       |       | 0.47  | 0.6  |      |

|      |                           |                                                           |                          | Full range |       |       | 1.1  |      |

|      |                           | $V_{IC} = V_{DD}/2$ , $I_{OL} = 5 \text{ mA}$             | V <sub>DD</sub> = 5 V    | 25°C       |       | 0.28  | 0.4  |      |

|      |                           | $V_{C} = V_{DD}/2$ , $V_{C} = S_{BB}/2$                   | vDD = 2 v                | Full range |       |       | 0.5  |      |

|      |                           |                                                           | V <sub>DD</sub> = 15 V   | 25°C       |       | 0.16  | 0.22 |      |

|      |                           |                                                           | VDD = 13 V               | Full range |       |       | 0.26 |      |

|      |                           | $V_{DD} = 2.7 \text{ V}, V_{O} = 0.5 \text{ V from rail}$ | Positive rail            | 25°C       |       | 4     |      |      |

|      |                           | VDD = 2.7 V, VO = 0.3 V HOITTAII                          | Negative rail            | 25°C       |       | 5     |      | mA   |

| اما  | Output current            | $V_{DD} = 5 \text{ V},  V_{O} = 0.5 \text{ V from rail}$  | Positive rail            | 25°C       |       | 7     |      |      |

| Ю    | Output current            | vDD = 2  v,  vC = 0.5  v Horn rall                        | Negative rail            | 25°C       |       | 8     |      |      |

|      |                           | V 45V V 05V(m "                                           | Positive rail            | 25°C       |       | 16    |      |      |

|      |                           | $V_{DD} = 15 \text{ V},  V_{O} = 0.5 \text{ V from rail}$ | Negative rail            | 25°C       |       | 15    |      |      |

#### power supply

| PARAMETER                        |                                       | TEST COND                                  | TEST CONDITIONS         |            |     | TYP | MAX  | UNIT |

|----------------------------------|---------------------------------------|--------------------------------------------|-------------------------|------------|-----|-----|------|------|

|                                  |                                       |                                            | V <sub>DD</sub> = 2.7 V | 25°C       |     | 470 | 560  | 560  |

| IDD Supply current (per channel) | \\a\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | V <sub>DD</sub> = 5 V                      | 25°C                    |            | 550 | 660 | l l  |      |

|                                  | Supply current (per channel)          | $V_O = V_{DD}/2,$                          | V 45 V                  | 25°C       |     | 750 | 900  | μΑ   |

|                                  |                                       |                                            | V <sub>DD</sub> = 15 V  | Full range |     |     | 1200 |      |

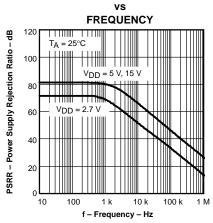

| PSRR                             | Supply voltage rejection ratio        | $V_{DD} = 2.7 \text{ V to } 15 \text{ V},$ | $V_{IC} = V_{DD}/2$ ,   | 25°C       | 70  | 80  |      | dB   |

|                                  | $(\Delta V_{DD} / \Delta V_{IO})$     | No load                                    |                         | Full range | 65  |     |      | uБ   |

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

### electrical characteristics at specified free-air temperature, $V_{DD}$ = 2.7 V, 5 V, and 15 V (unless otherwise noted) (continued)

#### dynamic performance

| PARAMETER      |                         | TEST CONDITIONS                                                                                                                              |                                         | TA         | MIN | TYP  | MAX   | UNIT   |

|----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|-----|------|-------|--------|

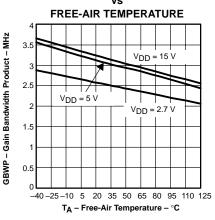

| UGBW U         | Unity gain bandwidth    | $R_1 = 2 k\Omega$                                                                                                                            | V <sub>DD</sub> = 2.7 V                 | 25°C       |     | 2.4  |       | MHz    |

|                |                         | C <sub>L</sub> = 10 pF                                                                                                                       | $V_{DD} = 5 \text{ V to } 15 \text{ V}$ | 25°C       |     | 3    |       | IVITIZ |

|                | Slew rate at unity gain |                                                                                                                                              | V 07V                                   | 25°C       | 1.4 | 2    |       | \//··o |

|                |                         |                                                                                                                                              | V <sub>DD</sub> = 2.7 V                 | Full range | 1   | V/μs |       |        |

| SR             |                         | $V_{O(PP)} = V_{DD}/2,$                                                                                                                      | V <sub>DD</sub> = 5 V                   | 25°C       | 1.6 | 2.4  | \//u0 |        |

|                |                         | $C_L = 50 \text{ pF},$<br>$R_I = 10 \text{ k}\Omega$                                                                                         | vDD = 2 v                               | Full range |     | V/μs |       |        |

|                |                         |                                                                                                                                              | V== - 15 V                              | 25°C       |     |      | V/μs  |        |

|                |                         |                                                                                                                                              | V <sub>DD</sub> = 15 V                  | Full range | 1.4 |      |       |        |

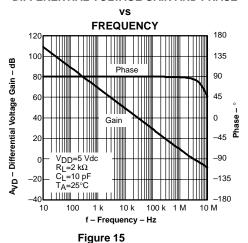

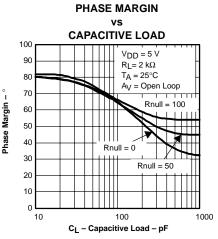

| φm             | Phase margin            | $R_L = 2 k\Omega$ ,                                                                                                                          | C <sub>L</sub> = 100 pF                 | 25°C       |     | 65°  |       |        |

|                | Gain margin             | $R_L = 2 k\Omega$ ,                                                                                                                          | C <sub>L</sub> = 10 pF                  | 25°C       |     | 18   |       | dB     |

| t <sub>S</sub> | Settling time           | $V_{DD} = 2.7 \text{ V},$ $V_{(STEP)PP} = 1 \text{ V},  A_{V} = -1,$ $C_{L} = 10 \text{ pF},  R_{L} = 2 \text{ k}\Omega$                     | 0.1%                                    | 25°C       |     | 2.9  |       | ::     |

|                |                         | $V_{DD} = 5 \text{ V}, 15 \text{ V}, \\ V_{(STEP)PP} = 1 \text{ V},  A_{V} = -1, \\ C_{L} = 47 \text{ pF}, \qquad R_{L} = 2 \text{ k}\Omega$ | 0.1%                                    | 25 0       |     | 2    |       | μѕ     |

#### noise/distortion performance

| PARAMETER      |                                      | TEST CONDITIONS                                                                                                                                                    |                      | TA    | MIN | TYP   | MAX | UNIT                 |  |

|----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-----|-------|-----|----------------------|--|

| T. I.C A.      |                                      | $\begin{array}{c} V_{DD}=2.7 \text{ V,} & A_{V}=1\\ V_{O(PP)}=V_{DD}/2 \text{ V,} & A_{V}=10\\ R_{L}=2 \text{ k}\Omega,  f=10 \text{ kHz} & A_{V}=100 \end{array}$ | A <sub>V</sub> = 1   |       |     | 0.02% |     |                      |  |

|                |                                      |                                                                                                                                                                    | A <sub>V</sub> = 10  | 25°C  |     | 0.05% |     |                      |  |

|                |                                      |                                                                                                                                                                    |                      | 0.18% |     |       |     |                      |  |

| THD + N        | Total harmonic distortion plus noise | $V_{DD} = 5 \text{ V}, 15 \text{ V},$<br>$V_{O(PP)} = V_{DD}/2 \text{ V},$<br>$R_{L} = 2 \text{ k}\Omega, f = 10 \text{ kHz}$                                      | A <sub>V</sub> = 1   |       |     | 0.02% |     |                      |  |

|                |                                      |                                                                                                                                                                    | A <sub>V</sub> = 10  | 25°C  |     | 0.09% |     |                      |  |

|                |                                      |                                                                                                                                                                    | A <sub>V</sub> = 100 |       |     | 0.5%  |     | 7                    |  |

| \              | Fault releast input point voltage    | f = 1 kHz                                                                                                                                                          |                      | 25°C  |     | 39    |     | ->44/ <del>11=</del> |  |

| V <sub>n</sub> | Equivalent input noise voltage       | f = 10 kHz                                                                                                                                                         |                      | 25-0  |     | 35    |     | nV/√Hz               |  |

| In             | Equivalent input noise current       | f = 1 kHz                                                                                                                                                          |                      | 25°C  |     | 0.6   |     | fA/√ <del>Hz</del>   |  |

#### shutdown characteristics

| PARAMETER |                                           | TEST CONDITIONS                             | TA         | MIN | TYP | MAX | UNIT |

|-----------|-------------------------------------------|---------------------------------------------|------------|-----|-----|-----|------|

| IDD(SHDN) |                                           | <u>V<sub>DD</sub> =</u> 2.7 V, 5 V,         | 25°C       |     | 25  | 30  |      |

|           | Supply current in shutdown mode (TLV2370, | SHDN = 0 V                                  | Full range |     |     | 35  | μΑ   |

|           | TLV2373, TLV2375) (per channel)           | <u>V<sub>DD</sub> =</u> 15 V,<br>SHDN = 0 V | 25°C       |     | 40  | 45  | μΑ   |

|           |                                           |                                             | Full range |     |     | 50  |      |

| t(on)     | Amplifier turnon time (see Note 2)        | R <sub>L</sub> = 2 kΩ                       | 25°C       |     | 0.8 | ·   | μs   |

| t(off)    | Amplifier turnoff time (see Note 2)       |                                             | 25°C       |     | 1   | ·   | μs   |

NOTE 2: Disable time and enable time are defined as the interval between application of the logic signal to the SHDN terminal and the point at which the supply current has reached one half of its final value.

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                       |                                              |                              | FIGURE   |

|-----------------------|----------------------------------------------|------------------------------|----------|

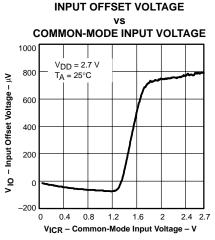

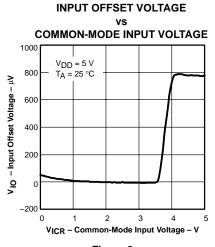

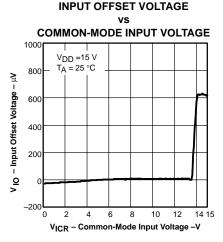

| V <sub>IO</sub>       | Input offset voltage                         | vs Common-mode input voltage | 1, 2, 3  |

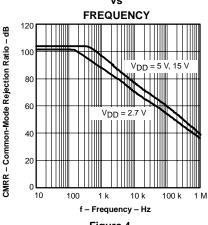

| CMRR                  | Common-mode rejection ratio                  | vs Frequency                 | 4        |

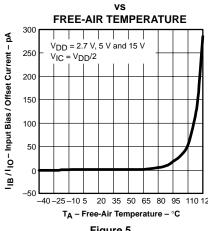

|                       | Input bias and offset current                | vs Free-air temperature      | 5        |

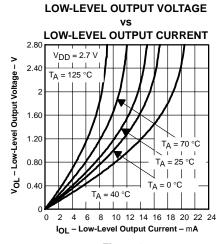

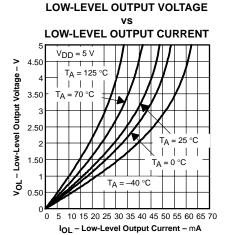

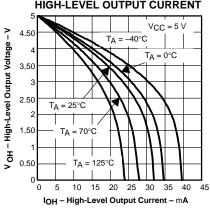

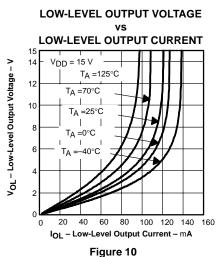

| $V_{OL}$              | Low-level output voltage                     | vs Low-level output current  | 6, 8, 10 |

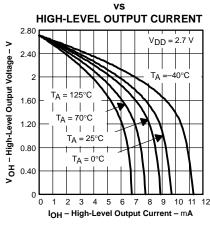

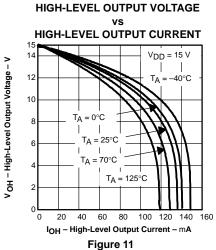

| V <sub>OH</sub>       | High-level output voltage                    | vs High-level output current | 7, 9, 11 |

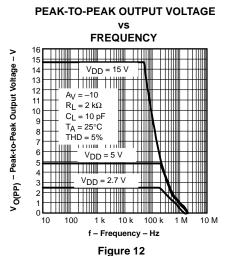

| V <sub>O(PP)</sub>    | Peak-to-peak output voltage                  | vs Frequency                 | 12       |

| I <sub>DD</sub>       | Supply current                               | vs Supply voltage            | 13       |

| PSRR                  | Power supply rejection ratio                 | vs Frequency                 | 14       |

| AVD                   | Differential voltage gain & phase            | vs Frequency                 | 15       |

|                       | Gain-bandwidth product                       | vs Free-air temperature      | 16       |

| SR                    | Clausanta                                    | vs Supply voltage            | 17       |

| SK                    | Slew rate                                    | vs Free-air temperature      | 18       |

| φm                    | Phase margin                                 | vs Capacitive load           | 19       |

| ٧n                    | Equivalent input noise voltage               | vs Frequency                 | 20       |

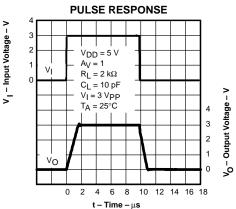

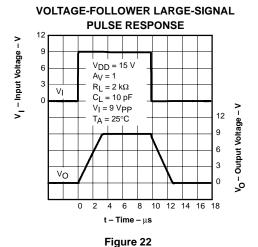

|                       | Voltage-follower large-signal pulse response |                              | 21, 22   |

|                       | Voltage-follower small-signal pulse response |                              | 23       |

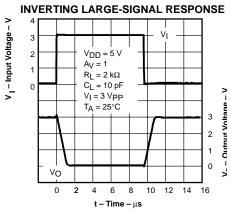

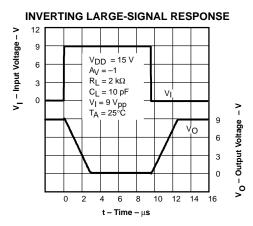

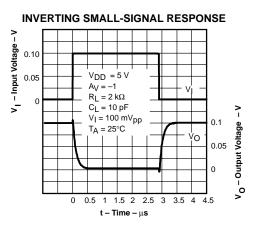

|                       | Inverting large-signal response              |                              | 24, 25   |

|                       | Inverting small-signal response              |                              | 26       |

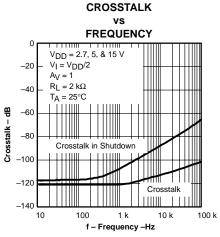

|                       | Crosstalk                                    | vs Frequency                 | 27       |

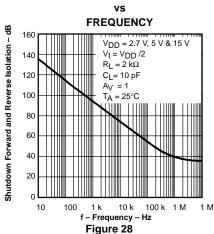

|                       | Shutdown forward & reverse isolation         | vs Frequency                 | 28       |

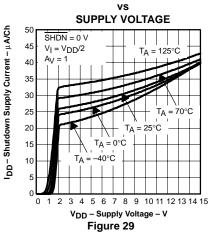

| I <sub>DD(SHDN)</sub> | Shutdown supply current                      | vs Supply voltage            | 29       |

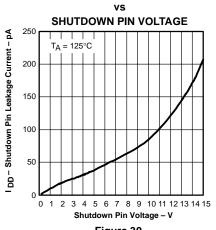

| IDD(SHDN)             | Shutdown pin leakage current                 | vs Shutdown pin voltage      | 30       |

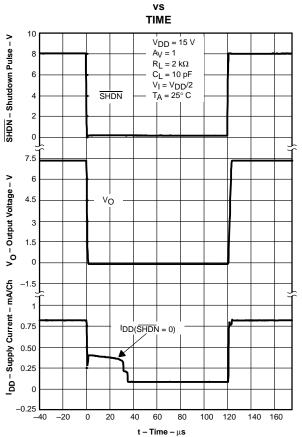

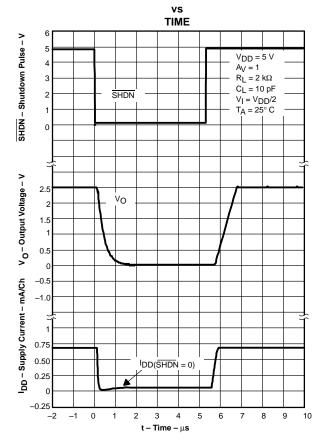

| IDD(SHDN)             | Shutdown supply current/output voltage       | vs Time                      | 31, 32   |

#### TYPICAL CHARACTERISTICS

Figure 2

**INPUT BIAS/OFFSET CURRENT**

Figure 3

#### **COMMON-MODE REJECTION RATIO** vs

Figure 4

Figure 5

Figure 6

#### HIGH-LEVEL OUTPUT VOLTAGE

Figure 7

Figure 8

#### HIGH-LEVEL OUTPUT VOLTAGE HIGH-LEVEL OUTPUT CURRENT

Figure 9

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### TYPICAL CHARACTERISTICS

**3** ... .

Figure 13

**POWER SUPPLY REJECTION RATIO**

Figure 14

#### **DIFFERENTIAL VOLTAGE GAIN AND PHASE**

**GAIN BANDWIDTH PRODUCT**

Figure 16

#### TYPICAL CHARACTERISTICS

Figure 17

Figure 18

Figure 19

#### **EQUIVALENT INPUT NOISE VOLTAGE**

**VOLTAGE-FOLLOWER LARGE-SIGNAL**

Figure 20

Figure 21

**VOLTAGE-FOLLOWER SMALL-SIGNAL**

**PULSE RESPONSE** V<sub>1</sub> - Input Voltage - mV 0.12 0.08 V<sub>DD</sub> = 5 V 0.04  $A_V = 1$ ٧ı  $R_L = 2 k\Omega$  $C_L = 10 pF$ Vi = 100 mVpp V<sub>O</sub> – Output Voltage – mV  $T_A = 25^{\circ}C$ 0.12 0.08 0.04 ۷o 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 t - Time - μs

Figure 23

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### TYPICAL CHARACTERISTICS

t – Time – μs

Figure 24

Figure 25

Figure 26

Figure 27

### SHUTDOWN FORWARD AND REVERSE ISOLATION

SHUTDOWN SUPPLY CURRENT

#### SHUTDOWN PIN LEAKAGE CURRENT

Figure 30

#### TYPICAL CHARACTERISTICS

#### SHUTDOWN SUPPLY CURRENT/OUTPUT VOLTAGE

Figure 31

#### SHUTDOWN SUPPLY CURRENT/OUTPUT VOLTAGE

Figure 32

#### **APPLICATION INFORMATION**

#### rail-to-rail input operation

The TLV237x input stage consists of two differential transistor pairs, NMOS and PMOS, that operate together to achieve rail-to-rail input operation. The transition point between these two pairs can be seen in Figures 1, 2, and 3 for a 2.7-V, 5-V, and 15-V supply. As the common-mode input voltage approaches the positive supply rail, the input pair switches from the PMOS differential pair to the NMOS differential pair. This transition occurs approximately 1.35 V from the positive rail and results in a change in offset voltage due to different device characteristics between the NMOS and PMOS pairs. If the input signal to the device is large enough to swing between both rails, this transition results in a reduction in common-mode rejection ratio (CMRR). If the input signal does not swing between both rails, it is best to bias the signal in the region where only one input pair is active. This is the region in Figures 1–3 where the offset voltage varies slightly across the input range and optimal CMRR can be achieved. This has the greatest impact when operating from a 2.7-V supply voltage.

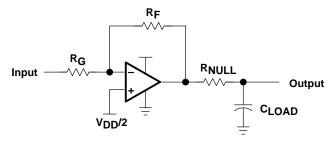

#### driving a capacitive load

When the amplifier is configured in this manner, capacitive loading directly on the output will decrease the device's phase margin leading to high frequency ringing or oscillations. Therefore, for capacitive loads of greater than 10 pF, it is recommended that a resistor be placed in series ( $R_{NULL}$ ) with the output of the amplifier, as shown in Figure 33. A minimum value of 20  $\Omega$  should work well for most applications.

Figure 33. Driving a Capacitive Load

#### offset voltage

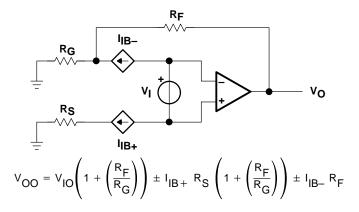

The output offset voltage,  $(V_{OO})$  is the sum of the input offset voltage  $(V_{IO})$  and both input bias currents  $(I_{IB})$  times the corresponding gains. The following schematic and formula can be used to calculate the output offset voltage:

Figure 34. Output Offset Voltage Model

#### APPLICATION INFORMATION

#### general configurations

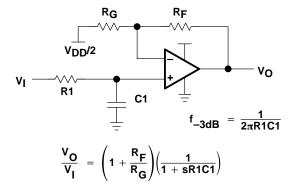

When receiving low-level signals, limiting the bandwidth of the incoming signals into the system is often required. The simplest way to accomplish this is to place an RC filter at the noninverting terminal of the amplifier (see Figure 35).

Figure 35. Single-Pole Low-Pass Filter

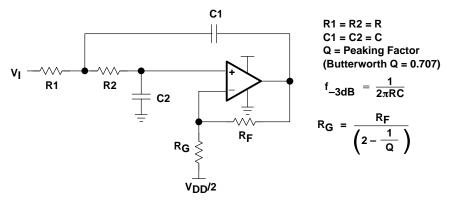

If even more attenuation is needed, a multiple pole filter is required. The Sallen-Key filter can be used for this task. For best results, the amplifier should have a bandwidth that is 8 to 10 times the filter frequency bandwidth. Failure to do this can result in phase shift of the amplifier.

Figure 36. 2-Pole Low-Pass Sallen-Key Filter

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### **APPLICATION INFORMATION**

#### circuit layout considerations

To achieve the levels of high performance of the TLV237x, follow proper printed-circuit board design techniques. A general set of guidelines is given in the following.

- Ground planes—It is highly recommended that a ground plane be used on the board to provide all

components with a low inductive ground connection. However, in the areas of the amplifier inputs and

output, the ground plane can be removed to minimize the stray capacitance.

- Proper power supply decoupling—Use a 6.8-μF tantalum capacitor in parallel with a 0.1-μF ceramic capacitor on each supply terminal. It may be possible to share the tantalum among several amplifiers depending on the application, but a 0.1-μF ceramic capacitor should always be used on the supply terminal of every amplifier. In addition, the 0.1-μF capacitor should be placed as close as possible to the supply terminal. As this distance increases, the inductance in the connecting trace makes the capacitor less effective. The designer should strive for distances of less than 0.1 inches between the device power terminals and the ceramic capacitors.

- Sockets—Sockets can be used but are not recommended. The additional lead inductance in the socket pins

will often lead to stability problems. Surface-mount packages soldered directly to the printed-circuit board

is the best implementation.

- Short trace runs/compact part placements—Optimum high performance is achieved when stray series inductance has been minimized. To realize this, the circuit layout should be made as compact as possible, thereby minimizing the length of all trace runs. Particular attention should be paid to the inverting input of the amplifier. Its length should be kept as short as possible. This helps to minimize stray capacitance at the input of the amplifier.

- Surface-mount passive components—Using surface-mount passive components is recommended for high

performance amplifier circuits for several reasons. First, because of the extremely low lead inductance of

surface-mount components, the problem with stray series inductance is greatly reduced. Second, the small

size of surface-mount components naturally leads to a more compact layout thereby minimizing both stray

inductance and capacitance. If leaded components are used, it is recommended that the lead lengths be

kept as short as possible.

#### shutdown function

Three members of the TLV237x family (TLV2370/3/5) have a shutdown terminal for conserving battery life in portable applications. When the shutdown terminal is tied low, the supply current is reduced to 25  $\mu$ A/channel, the amplifier is disabled, and the outputs are placed in a high impedance mode. To enable the amplifier, the shutdown terminal can either be left floating or pulled high. When the shutdown terminal is left floating, care should be taken to ensure that parasitic leakage current at the shutdown terminal does not inadvertently place the operational amplifier into shutdown.

#### **APPLICATION INFORMATION**

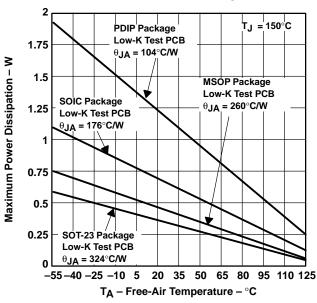

#### general power dissipation considerations

For a given  $\theta_{JA}$ , the maximum power dissipation is shown in Figure 37 and is calculated by the following formula:

$$\mathsf{P}_\mathsf{D} = \left(\frac{\mathsf{T}_\mathsf{MAX}^{-\mathsf{T}}\mathsf{A}}{\theta_\mathsf{JA}}\right)$$

Where:

$P_D$  = Maximum power dissipation of TLV237x IC (watts)

T<sub>MAX</sub> = Absolute maximum junction temperature (150°C)

$T_A$  = Free-ambient air temperature (°C)

$\theta_{JA} = \theta_{JC} + \theta_{CA}$

$\theta_{JC}$  = Thermal coefficient from junction to case

$\theta_{CA}$  = Thermal coefficient from case to ambient air (°C/W)

#### MAXIMUM POWER DISSIPATION vs FREE-AIR TEMPERATURE

NOTE A: Results are with no air flow and using JEDEC Standard Low-K test PCB.

Figure 37. Maximum Power Dissipation vs Free-Air Temperature

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

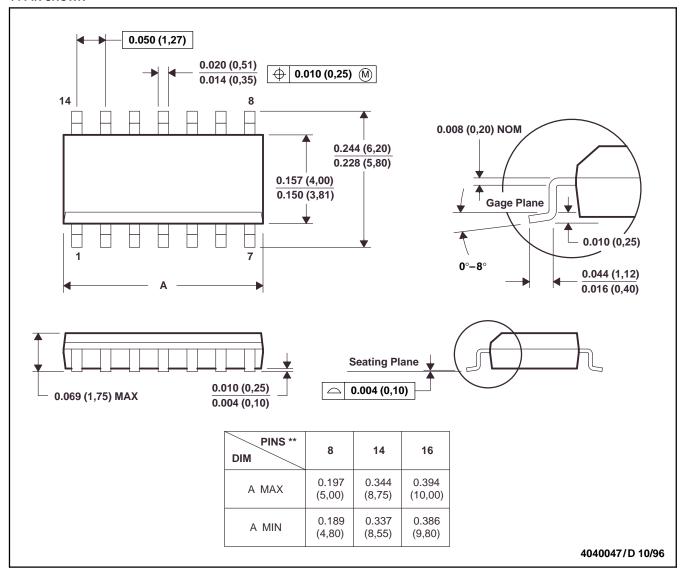

#### **MECHANICAL DATA**

#### D (R-PDSO-G\*\*)

#### 14 PIN SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

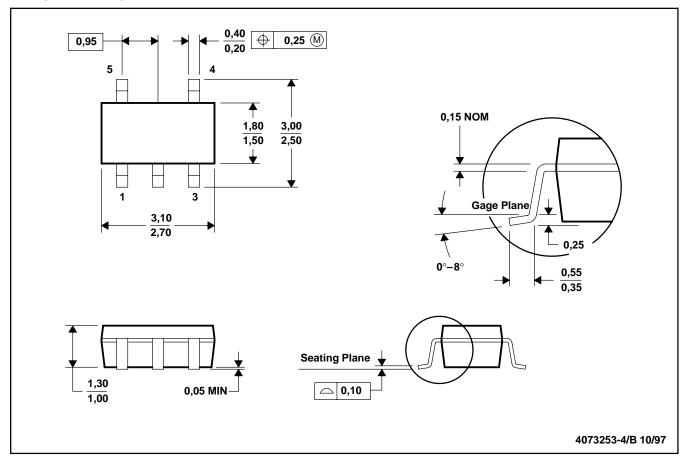

#### **MECHANICAL DATA**

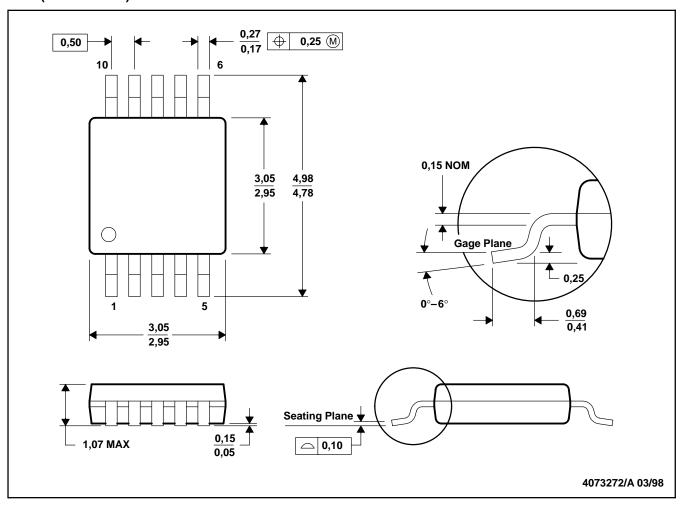

#### DBV (R-PDSO-G5)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusion.

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

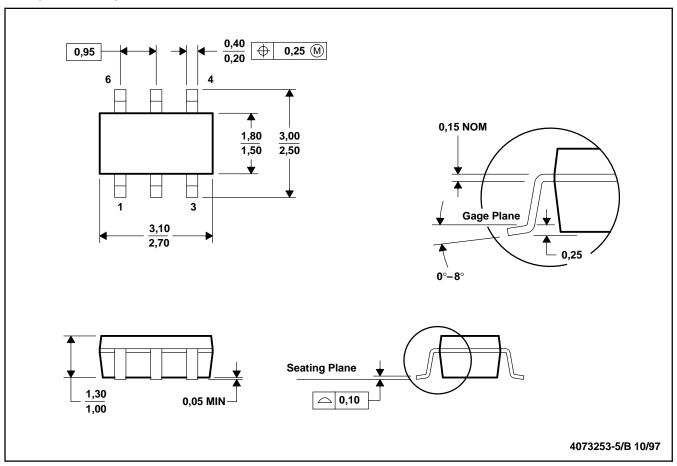

#### **MECHANICAL DATA**

#### DBV (R-PDSO-G6)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusion.

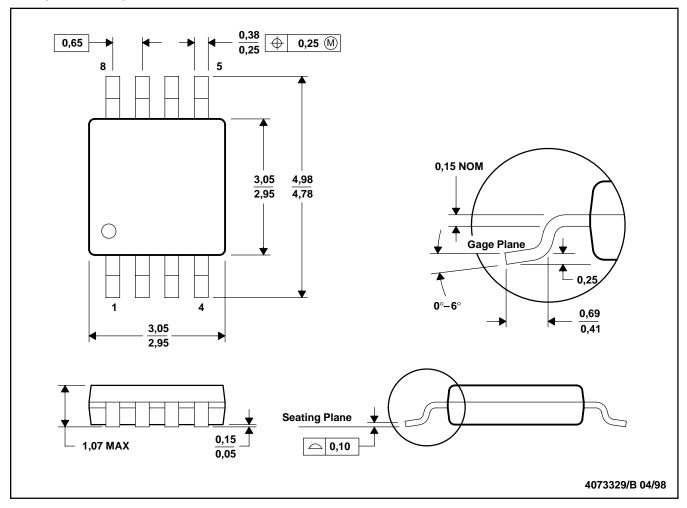

#### **MECHANICAL DATA**

#### DGK (R-PDSO-G8)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-187

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

#### **MECHANICAL DATA**

#### DGS (S-PDSO-G10)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion.

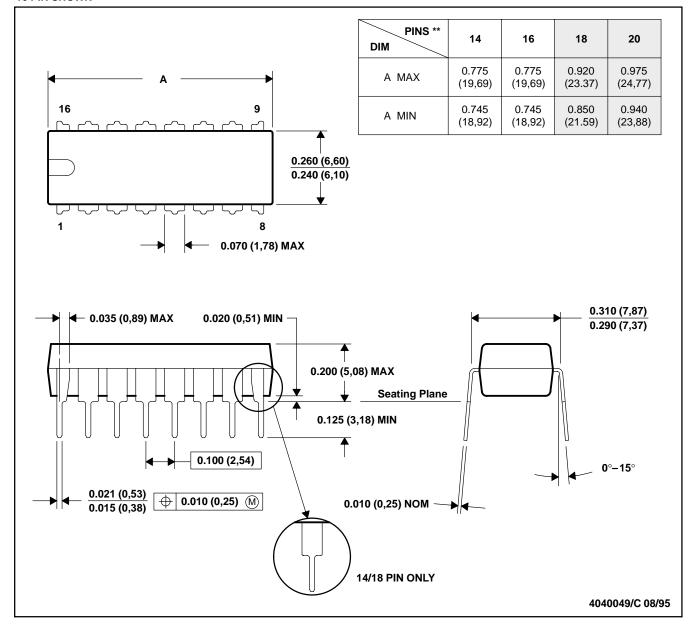

#### MECHANICAL DATA

#### N (R-PDIP-T\*\*)

#### **16 PIN SHOWN**

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20 pin package is shorter then MS-001.)

SLOS270B - MARCH 2001 - REVISED JANUARY 2002

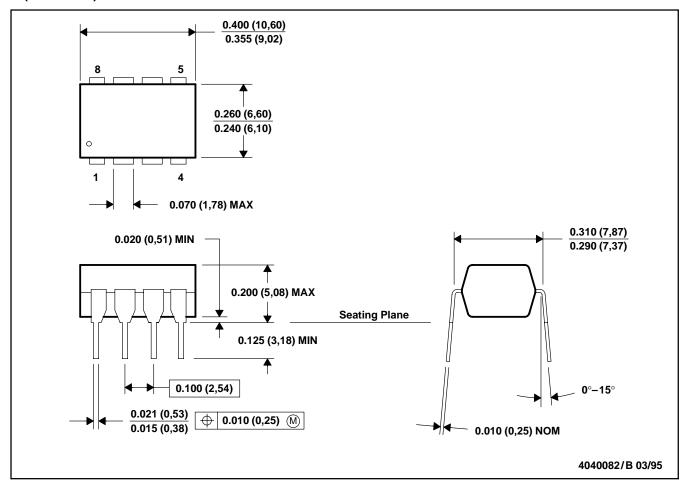

#### **MECHANICAL DATA**

#### P (R-PDIP-T8)

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001

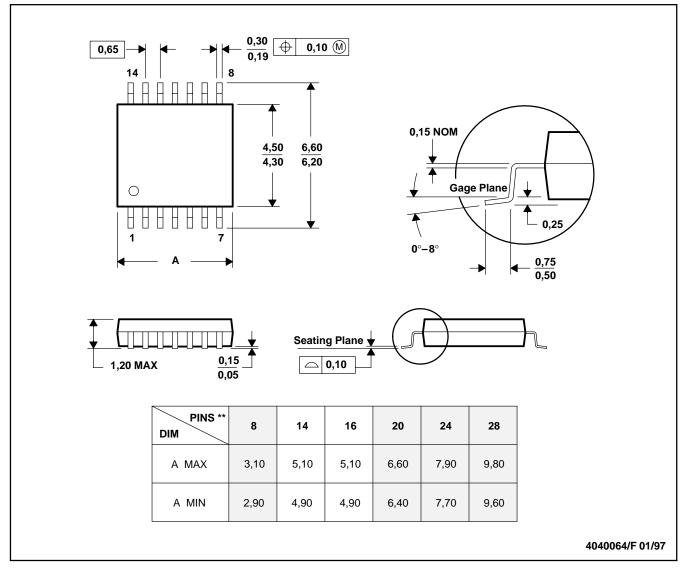

#### **MECHANICAL DATA**

#### PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated