# TIBPAL20L8-5C, TIBPAL20R4-5C, TIBPAL20R6-5C, TIBPAL20R8-5C TIBPAL20L8-7M, TIBPAL20R4-7M, TIBPAL20R6-7M, TIBPAL20R8-7M HIGH-PERFORMANCE IMPACT-X™ PAL® CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

High-Performance Operation:

f<sub>max</sub> (no feedback)

TIBPAL20R' -5C Series . . . 125 MHz Min

TIBPAL20R' -7M Series . . . 100 MHz Min

f<sub>max</sub> (internal feedback)

TIBPAL20R'-5C Series ... 125 MHz Min

TIBPAL20R'-7M Series . . . 100 MHz Min

f<sub>max</sub> (external feedback)

TIBPAL20R' -5C Series . . . 117 MHz Min

TIBPAL20R' -7M Series . . . 74 MHz Min

**Propagation Delay**

TIBPAL20L8-5C Series . . . 5 ns Max

TIBPAL20L8-7M Series . . . 7 ns Max

TIBPAL20R' -5C Series

(CLK-to-Q) . . . 4 ns Max

TIBPAL20R'-7M Series

(CLK-to-Q) . . . 6.5 ns Max

- Functionally Equivalent, but Faster Than, Existing 24-Pin PLDs

- Preload Capability on Output Registers Simplifies Testing

- Power-Up Clear on Registered Devices (All Register Outputs are Set Low, but Voltage Levels at the Output Pins Go High)

- Package Options Include Both Plastic and Ceramic Chip Carriers in Addition to Plastic and Ceramic DIPs

- Security Fuse Prevents Duplication

| DEVICE  | I<br>INPUTS | 3-STATE<br>O OUTPUTS | REGISTERED<br>Q OUTPUTS | I/O<br>PORT<br>S |

|---------|-------------|----------------------|-------------------------|------------------|

| PAL20L8 | 14          | 2                    | 0                       | 6                |

| PAL20R4 | 12          | 0                    | 4 (3-state buffers)     | 4                |

| PAL20R6 | 12          | 0                    | 6 (3-state buffers)     | 2                |

| PAL20R8 | 12          | 0                    | 8 (3-state buffers)     | 0                |

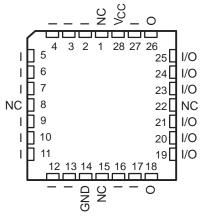

# TIBPAL20L8' C SUFFIX ... JT OR NT PACKAGE M SUFFIX ... JT PACKAGE

TIBPAL20L8'

C SUFFIX ... FN PACKAGE

M SUFFIX ... FK PACKAGE

(TOP VIEW)

NC — No internal connection

Pin assignments in operating mode

#### description

These programmable array logic devices feature high speed and functional equivalency when compared with currently available devices. These IMPACT-X<sup>TM</sup> circuits combine the latest Advanced Low-Power Schottky technology with proven titanium-tungsten fuses to provide reliable, high-performance substitutes for conventional TTL logic. Their easy programmability allows for quick design of custom functions and typically results in a more compact circuit board.

The TIBPAL20' C series is characterized from 0°C to 75°C. The TIBPAL20' M series is characterized for operation over the full military temperature range of –55°C to 125°C.

These devices are covered by U.S. Patent 4,410,987. IMPACT-X is a trademark of Texas Instruments Incorporated. PAL is a registered trademark of Advanced Micro Devices Inc.

# TIBPAL20R4-5C, TIBPAL20R6-5C, TIBPAL20R8-5C TIBPAL20R4-7M, TIBPAL20R6-7M, TIBPAL20R8-7M HIGH-PERFORMANCE *IMPACT-X*™ *PAL*® CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

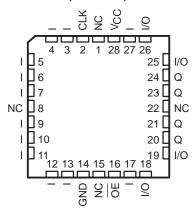

# TIBPAL20R4' C SUFFIX ... JT OR NT PACKAGE M SUFFIX ... JT PACKAGE

TIBPAL20R4'

C SUFFIX ... FN PACKAGE

M SUFFIX ... FK PACKAGE

(TOP VIEW)

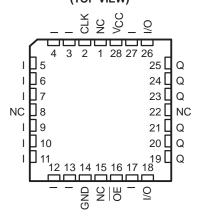

TIBPAL20R6'

C SUFFIX . . . JT OR NT PACKAGE

M SUFFIX . . . JT PACKAGE

#### (TOP VIEW)

TIBPAL20R6'

C SUFFIX . . . FN PACKAGE

M SUFFIX . . . FK PACKAGE

(TOP VIEW)

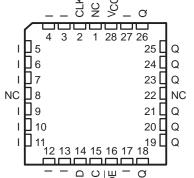

## TIBPAL20R8' C SUFFIX . . . JT OR NT PACKAGE M SUFFIX . . . JT PACKAGE

#### (TOP VIEW)

# TIBPAL20R8' C SUFFIX . . . FN PACKAGE M SUFFIX . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

Pin assignments in operating mode

#### functional block diagrams (positive logic)

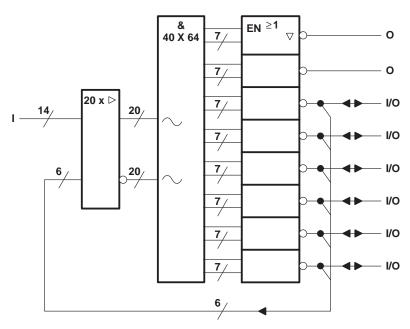

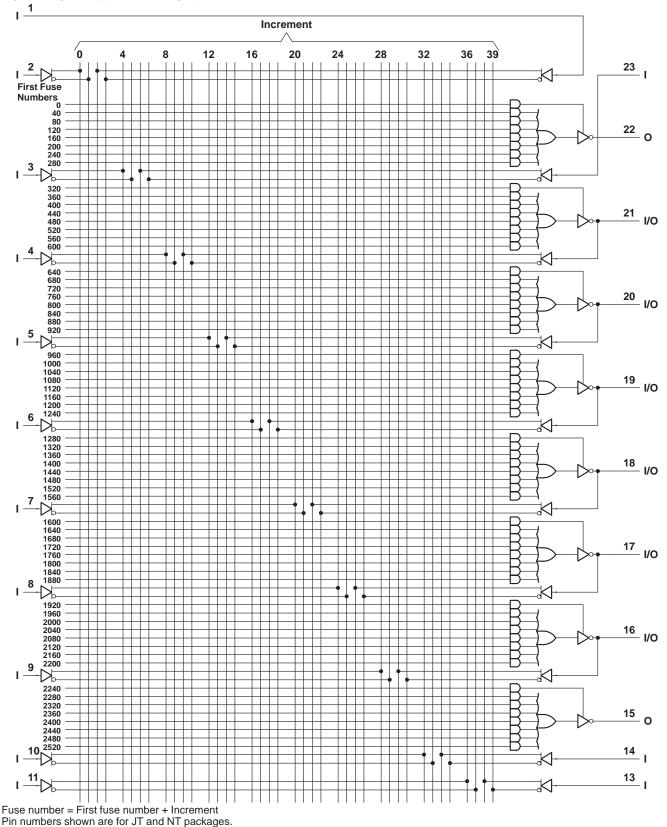

#### TIBPAL20L8'

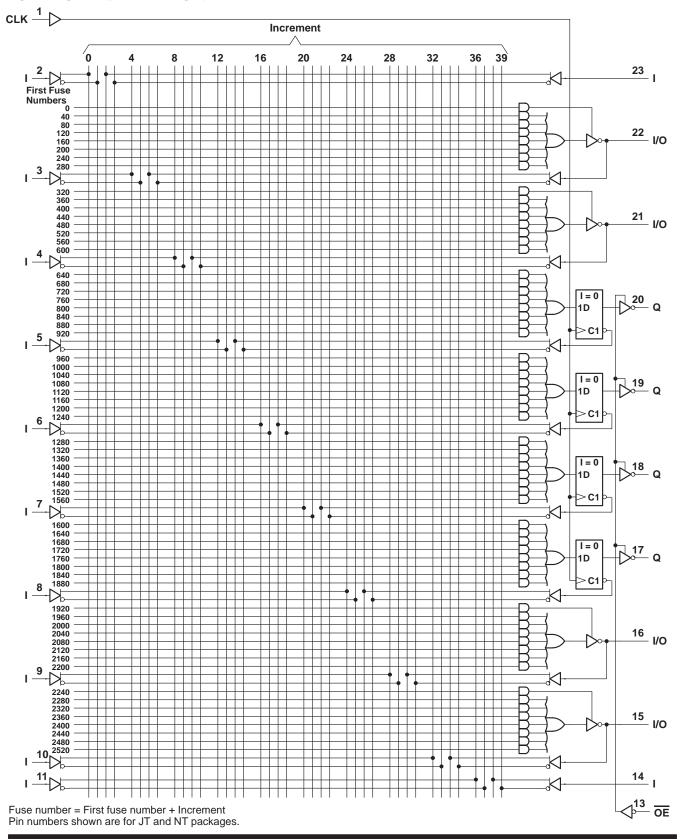

#### TIBPAL20R4'

denotes fused inputs

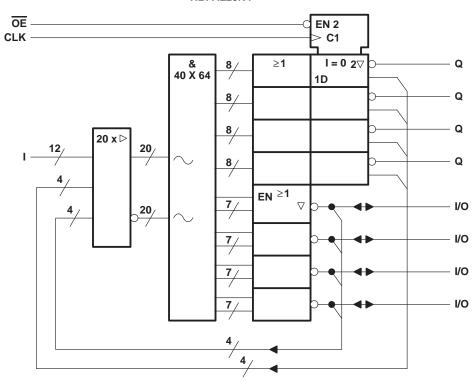

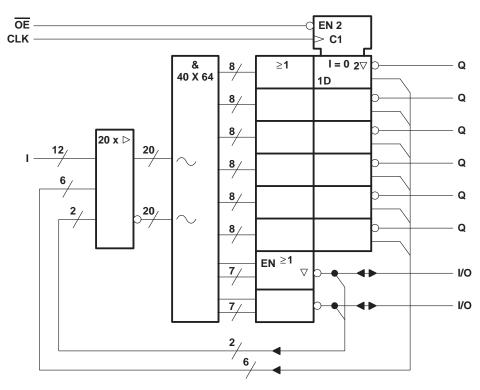

#### functional block diagrams (positive logic)

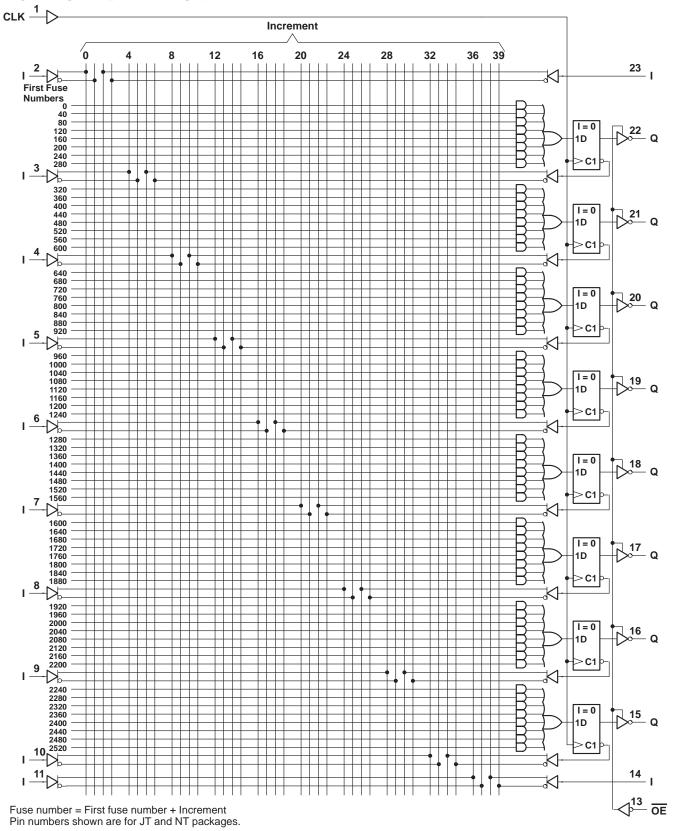

#### TIBPAL20R6'

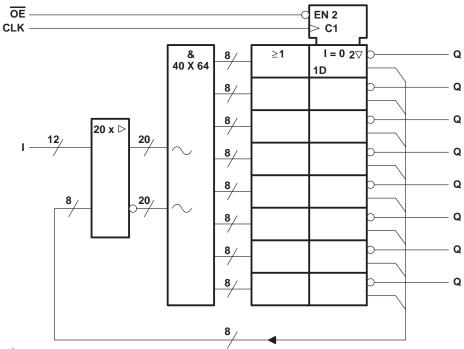

#### TIBPAL20R8'

outputs denotes fused inputs

#### logic diagram (positive logic)

## HIGH-PERFORMANCE *IMPACT-X* TM *PAL*® CIRCUITS SRPS010F – D3353, OCTOBER 1989 – REVISED SEPTEMBER 1992

#### logic diagram (positive logic)

#### logic diagram (positive logic) CLK 1 Increment 0 8 36 39 12 16 20 24 28 32 I 2 N. Numbers 0 40 120 160 200 240 N 320 360 400 440 I = 0 21 Q 1D 480 560 600 640 680 720 I = 0 840 880 920 **⊳**C1 960 1000 1040 1080 I = 0 7.19 Q 1D 1160 1200 ►C1 1240 1280 1320 1360 1400 1440 1480 I = 0 7<mark>18</mark> Q 1D 1520 >C1 I 7 1560 1560 1600 1640 1680 I = 0 17 Q 1720 1760 1D 1800 1840 >C1 I 8 1880 1880 1920 1960 2000 I = 0 716 Q 2040 2080 1D 2120 2160 **⊳**C1 2200 ₩ 2240 2280 2320 2360 <u>15</u> I/O 2400 2440 2480 2520 <u>14</u> I N Fuse number = First fuse number + Increment Pin numbers shown are for JT and NT packages.

#### logic diagram (positive logic)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)    |            | 7 V   |

|-------------------------------------------------|------------|-------|

| Input voltage (see Note 1)                      |            | 5.5 V |

| Voltage applied to disabled output (see Note 1) |            | 5.5 V |

| Operating free-air temperature range            | 0°C to     | 75°C  |

| Storage temperature range                       | -65°C to 1 | 50°C  |

NOTE 1: These ratings apply except for programming pins during a programming cycle or during a preload cycle.

#### recommended operating conditions

|                 |                                       | MIN  | NOM | MAX  | UNIT |

|-----------------|---------------------------------------|------|-----|------|------|

| VCC             | Supply voltage                        | 4.75 | 5   | 5.25 | V    |

| VIH             | High-level input voltage (see Note 2) | 2    |     | 5.5  | V    |

| V <sub>IL</sub> | Low-level input voltage (see Note 2)  |      |     | 0.8  | V    |

| IOH             | High-level output current             |      |     | -3.2 | mA   |

| loL             | Low-level output current              |      |     | 24   | mA   |

| TA              | Operating free-air temperature        | 0    | 25  | 75   | °C   |

NOTE 2: These are absolute voltage levels with respect to the ground pin of the device and include all overshoots due to system and/or tester noise. Testing these parameters should not be attempted without suitable equipment.

#### electrical characteristics over recommended operating free-air temperature range

| PARAMETER         |                            | TEST CONDITIONS            |              | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|-------------------|----------------------------|----------------------------|--------------|-----|------------------|------|------|

| VIK               | $V_{CC} = 4.75 \text{ V},$ | $I_{I} = -18 \text{ mA}$   |              |     | -0.8             | -1.5 | V    |

| Voн               | $V_{CC} = 4.75 \text{ V},$ | $I_{OH} = -3.2 \text{ mA}$ |              | 2.4 | 2.7              |      | V    |

| VOL               | $V_{CC} = 4.75 \text{ V},$ | $I_{OL} = 24 \text{ mA}$   |              |     | 0.3              | 0.5  | V    |

| lozh‡             | $V_{CC} = 5.25 \text{ V},$ | $V_0 = 2.7 \text{ V}$      |              |     |                  | 100  | μΑ   |

| lozL <sup>‡</sup> | $V_{CC} = 5.25 \text{ V},$ | $V_0 = 0.4 V$              |              |     |                  | -100 | μΑ   |

| lį                | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 5.5 V     |              |     |                  | 100  | μΑ   |

| I <sub>IH</sub> ‡ | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 2.7 V     |              |     |                  | 25   | μΑ   |

| I <sub>IL</sub> ‡ | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 0.4 V     |              |     |                  | -250 | μΑ   |

| IOS§              | $V_{CC} = 5.25 \text{ V},$ | V <sub>O</sub> = 0.5 V     |              | -30 | -70              | -130 | mA   |

| lcc               | V <sub>CC</sub> = 5.25 V,  | $V_I = 0$ ,                | Outputs open |     |                  | 210  | mA   |

| Ci                | f = 1 MHz,                 | V <sub>I</sub> = 2 V       |              |     | 8.5              |      | pF   |

| Co                | f = 1 MHz,                 | V <sub>O</sub> = 2 V       |              |     | 10               |      | pF   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        | FROM                                         |          | TO (OUTPUT)                        | TEST TIBPAL20L8-5CFN                       |     | TIBPAL<br>TIBPAL | UNIT |     |    |

|------------------|----------------------------------------------|----------|------------------------------------|--------------------------------------------|-----|------------------|------|-----|----|

|                  | (INPUT)                                      | (OUTPUT) |                                    | CONDITIONS                                 | MIN | MAX              | MIN  | MAX |    |

|                  | I, I/O O, I/O with up to 4 outputs switching | 1.5      | 5                                  | 1.5                                        | 5   |                  |      |     |    |

| <sup>t</sup> pd  | I, I/O                                       | O, I/O   | with more than 4 outputs switching | R1 = 200 $\Omega$ ,<br>R2 = 200 $\Omega$ , | 1.5 | 5                | 1.5  | 5.5 | ns |

| t <sub>en</sub>  | I, I/O                                       |          | O, I/O                             | See Figure 8                               | 2   | 7                | 2    | 7   | ns |

| t <sub>dis</sub> | I, I/O                                       |          | O, I/O                             |                                            | 2   | 7                | 2    | 7   | ns |

<sup>‡</sup> I/O leakage is the worst case of IOZL and I<sub>IL</sub> or IOZH and I<sub>IH</sub>, respectively.

Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second. Vo is set at 0.5 V to avoid test problems caused by test equipment ground degradation.

#### TIBPAL20R4-5C, TIBPAL20R6-5C HIGH-PERFORMANCE *IMPACT-X™ PAL®* CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)    | 7 V            |

|-------------------------------------------------|----------------|

| Input voltage (see Note 1)                      | 5.5 V          |

| Voltage applied to disabled output (see Note 1) | 5.5 V          |

| Operating free-air temperature range            | 0°C to 75°C    |

| Storage temperature range                       | -65°C to 150°C |

NOTE 1: These ratings apply except for programming pins during a programming cycle or during a preload cycle.

#### recommended operating conditions

|                 |                                             |      |   | MIN  | NOM | MAX  | UNIT |

|-----------------|---------------------------------------------|------|---|------|-----|------|------|

| VCC             | Supply voltage                              |      |   | 4.75 | 5   | 5.25 | V    |

| VIH             | High-level input voltage (see Note 2)       |      | 2 |      | 5.5 | V    |      |

| V <sub>IL</sub> | Low-level input voltage (see Note 2)        |      |   |      |     | 0.8  | V    |

| IOH             | High-level output current                   |      |   |      |     | -3.2 | mA   |

| loL             | Low-level output current                    |      |   |      |     | 24   | mA   |

| fclock          | Clock frequency                             |      |   | 0    |     | 125  | MHz  |

|                 | Dulas duration alock                        | High |   | 4    |     |      | ns   |

| t <sub>W</sub>  | Pulse duration, clock                       | Low  |   | 4    |     |      |      |

| t <sub>su</sub> | Setup time, input or feedback before clock↑ |      |   | 4.5  |     |      | ns   |

| th              | Hold time, input or feedback after clock↑   |      |   | 0    |     |      | ns   |

| TA              | Operating free-air temperature              |      |   | 0    | 25  | 75   | °C   |

NOTE 2: These are absolute voltage levels with respect to the ground pin of the device and include all overshoots due to system and/or tester noise. Testing these parameters should not be attempted without suitable equipment.

#### electrical characteristics over recommended operating free-air temperature range

| PARA               | AMETER |                            | TEST CONDITIONS            |              | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|--------------------|--------|----------------------------|----------------------------|--------------|-----|------------------|------|------|

| VIK                |        | V <sub>CC</sub> = 4.75 V,  | $I_{I} = -18 \text{ mA}$   |              |     | -0.8             | -1.5 | V    |

| Vон                |        | $V_{CC} = 4.75 \text{ V},$ | $I_{OH} = -3.2 \text{ mA}$ |              | 2.4 | 2.7              |      | V    |

| VOL                |        | $V_{CC} = 4.75 \text{ V},$ | $I_{OL} = 24 \text{ mA}$   |              |     | 0.3              | 0.5  | V    |

| loz <sub>H</sub> ‡ |        | $V_{CC} = 5.25 \text{ V},$ | V <sub>O</sub> = 2.7 V     |              |     |                  | 100  | μΑ   |

| l <sub>OZL</sub> ‡ |        | $V_{CC} = 5.25 \text{ V},$ | V <sub>O</sub> = 0.4 V     |              |     |                  | -100 | μΑ   |

| II                 |        | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 5.5 V     |              |     |                  | 100  | μΑ   |

| I <sub>IH</sub> ‡  |        | V <sub>CC</sub> = 5.25 V,  | V <sub>I</sub> = 2.7 V     |              |     |                  | 25   | μΑ   |

| I <sub>IL</sub> ‡  |        | V <sub>CC</sub> = 5.25 V,  | V <sub>I</sub> = 0.4 V     |              |     |                  | -250 | μΑ   |

| IOS§               |        | V <sub>CC</sub> = 5.25 V,  | V <sub>O</sub> = 0.5 V     |              | -30 | -70              | -130 | mA   |

| Icc                |        | V <sub>CC</sub> = 5.25 V,  | $V_{I} = 0$ ,              | Outputs open |     |                  | 210  | mA   |

| Ci                 | I      | f = 1 MHz,                 | V <sub>I</sub> = 2 V       |              |     | 8.5              |      | pF   |

|                    | CLK/OE | 1 – 1 1011 12,             | V   - 2 V                  |              |     | 7.5              |      | Pi   |

| C                  | I/O    | f = 1 MHz,                 | V <sub>O</sub> = 2 V       |              |     | 10               |      | pF   |

| Co                 | Q      | i = i ivii1Z,              | v () = 2 v                 |              |     | 7                | PF   |      |

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        | FROM TO (OUTPUT)                               |                    | TEST<br>CONDITIONS  | TIBPAL20R4-5CFN<br>TIBPAL20R6-5CFN |                  |     | TIBPAL20R4-5CJT<br>TIBPAL20R4-5CNT<br>TIBPAL20R6-5CJT<br>TIBPAL20R6-5CNT |                  |     | UNIT |

|------------------|------------------------------------------------|--------------------|---------------------|------------------------------------|------------------|-----|--------------------------------------------------------------------------|------------------|-----|------|

|                  |                                                |                    |                     | MIN                                | TYP <sup>†</sup> | MAX | MIN                                                                      | TYP <sup>†</sup> | MAX |      |

|                  | withou                                         | t feedback         |                     | 125                                |                  |     | 125                                                                      |                  |     |      |

| $f_{max}\P$      | with internal feedback (counter configuration) |                    |                     | 125                                |                  |     | 125                                                                      |                  |     | MHz  |

|                  | with exter                                     |                    | 117                 |                                    |                  | 111 |                                                                          |                  |     |      |

| <sup>t</sup> pd  | CLK↑                                           | Q                  |                     | 1.5                                |                  | 4   | 1.5                                                                      |                  | 4.5 | ns   |

| <sup>t</sup> pd  | CLK↑                                           | Internal feedback  | R1 = 200 $\Omega$ , |                                    |                  | 3.5 |                                                                          |                  | 3.5 | ns   |

| <sup>t</sup> pd  | I, I/O                                         | I/O                | $R2 = 200 \Omega$ , | 1.5                                |                  | 5   | 1.5                                                                      |                  | 5   | ns   |

| t <sub>en</sub>  | ŌE↓                                            | Q                  | See Figure 8        | 1.5                                |                  | 6   | 1.5                                                                      |                  | 6   | ns   |

| <sup>t</sup> dis | ŌE↑                                            | Q                  |                     | 1                                  |                  | 6.5 | 1                                                                        |                  | 7   | ns   |

| t <sub>en</sub>  | I, I/O                                         | I/O                |                     | 2                                  |                  | 7   | 2                                                                        |                  | 7   | ns   |

| <sup>t</sup> dis | I, I/O                                         | I/O                |                     | 2                                  |                  | 7   | 2                                                                        |                  | 7   | ns   |

| t <sub>r</sub>   |                                                |                    |                     |                                    | 1.5              |     |                                                                          | 1.5              |     | ns   |

| t <sub>f</sub>   |                                                |                    |                     |                                    | 1.5              |     |                                                                          | 1.5              |     | ns   |

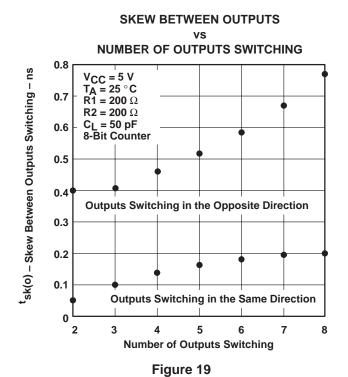

| tsk(o)#          | Skew between                                   | registered outputs |                     |                                    | 0.5              |     |                                                                          | 0.5              |     | ns   |

$<sup>^{\</sup>dagger}$  All typical values are at VCC = 5 V, TA = 25°C.

<sup>‡</sup> I/O leakage is the worst case of IOZL and I<sub>IL</sub> or IOZH and I<sub>IH</sub>, respectively.

<sup>§</sup> Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second. V<sub>O</sub> is set at 0.5 V to avoid test problems caused by test equipment ground degradation.

$<sup>\</sup>P$  See 'fmax Specification' near the end of this data sheet.

$<sup>^{\#}</sup>t_{Sk(0)}$  is the skew time between registered outputs.

#### TIBPAL20R8-5C HIGH-PERFORMANCE *IMPACT-X™ PAL®* CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)    | 7 V            |

|-------------------------------------------------|----------------|

| Input voltage (see Note 1)                      | 5.5 V          |

| Voltage applied to disabled output (see Note 1) | 5.5 V          |

| Operating free-air temperature range            | 0°C to 75°C    |

| Storage temperature range                       | -65°C to 150°C |

NOTE 1: These ratings apply except for programming pins during a programming cycle or during a preload cycle.

#### recommended operating conditions

|                 |                                             |      | MIN  | NOM | MAX  | UNIT |

|-----------------|---------------------------------------------|------|------|-----|------|------|

| VCC             | Supply voltage                              |      | 4.75 | 5   | 5.25 | V    |

| VIH             | High-level input voltage (see Note 2)       |      |      |     | 5.5  | V    |

| V <sub>IL</sub> | Low-level input voltage (see Note 2)        |      |      |     | 0.8  | V    |

| IOH             | High-level output current                   |      |      |     | -3.2 | mA   |

| loL             | Low-level output current                    |      |      |     | 24   | mA   |

| fclock          | Clock frequency                             |      | 0    |     | 125  | MHz  |

|                 | Pulse duration, clock                       | High | 4    |     |      | ns   |

| t <sub>W</sub>  | ruise duration, clock                       | Low  | 4    |     |      |      |

| t <sub>su</sub> | Setup time, input or feedback before clock↑ |      | 4.5  |     |      | ns   |

| th              | Hold time, input or feedback after clock↑   |      | 0    |     |      | ns   |

| T <sub>A</sub>  | Operating free-air temperature              |      | 0    | 25  | 75   | °C   |

NOTE 2: These are absolute voltage levels with respect to the ground pin of the device and include all overshoots due to system and/or tester noise. Testing these parameters should not be attempted without suitable equipment.

12

#### electrical characteristics over recommended operating free-air temperature range

| PARAMETER        | TEST CONDITIONS            |                                  | TIBPAL20R8-5CFN |                  |      | TIBPAL20R8-5CJT<br>TIBPAL20R8-5CNT |                  |      | UNIT |

|------------------|----------------------------|----------------------------------|-----------------|------------------|------|------------------------------------|------------------|------|------|

| 7110111121211    | .13                        |                                  | MIN             | TYP <sup>†</sup> | MAX  | MIN                                | TYP <sup>†</sup> | MAX  | 0    |

| VIK              | $V_{CC} = 4.75 V$ ,        | $I_{I} = -18 \text{ mA}$         |                 | -0.8             | -1.5 |                                    | -0.8             | -1.5 | V    |

| VOH              | $V_{CC} = 4.75 V$ ,        | $I_{OH} = -3.2 \text{ mA}$       | 2.4             | 2.7              |      | 2.4                                | 2.7              |      | V    |

| V <sub>OL</sub>  | $V_{CC} = 4.75 V$ ,        | $I_{OL}$ = 24 mA                 |                 | 0.3              | 0.5  |                                    | 0.3              | 0.5  | V    |

| lozh             | $V_{CC} = 5.25 \text{ V},$ | $V_0 = 2.7 \text{ V}$            |                 |                  | 100  |                                    |                  | 100  | μΑ   |

| lozL             | $V_{CC} = 5.25 \text{ V},$ | $V_0 = 0.4 V$                    |                 |                  | -100 |                                    |                  | -100 | μΑ   |

| IĮ               | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 5.5 V           |                 |                  | 100  |                                    |                  | 100  | μΑ   |

| lн               | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 2.7 V           |                 |                  | 25   |                                    |                  | 25   | μΑ   |

| I <sub>IL</sub>  | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 0.4 V           |                 |                  | -250 |                                    |                  | -250 | μΑ   |

| los <sup>‡</sup> | $V_{CC} = 5.25 \text{ V},$ | V <sub>O</sub> = 0.5 V           | -30             | -70              | -130 | -30                                | -70              | -130 | mA   |

| Icc              | $V_{CC} = 5.25 \text{ V},$ | V <sub>I</sub> = 0, Outputs open |                 |                  | 210  |                                    |                  | 210  | mA   |

|                  | £ 4 MIL-                   | W- 0.W                           |                 | 8.5              |      |                                    | 6.5              |      | nE   |

| CLK/OE           | f = 1 MHz,                 | V <sub>I</sub> = 2 V             |                 | 7.5              |      |                                    | 5.5              |      | pF   |

| Co               | f = 1 MHz,                 | V <sub>O</sub> = 2 V             |                 | 10               |      |                                    | 8                |      | pF   |

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER          | FROM TO                                        |                   | TEST                               | TIBPAL20R8-5CFN                     |     | TIBPAL20R8-5CJT<br>TIBPAL20R8-5CNT |     |     | UNIT             |     |    |

|--------------------|------------------------------------------------|-------------------|------------------------------------|-------------------------------------|-----|------------------------------------|-----|-----|------------------|-----|----|

|                    | (INPUT)                                        | (OUTPUT)          |                                    | CONDITIONS                          | MIN | TYP <sup>†</sup>                   | MAX | MIN | TYP <sup>†</sup> | MAX |    |

|                    | without feedback                               |                   |                                    | 125                                 |     |                                    | 125 |     |                  | MHz |    |

| f <sub>max</sub> § | with internal feedback (counter configuration) |                   |                                    | 125                                 |     |                                    | 125 |     |                  |     |    |

|                    | with external feedback                         |                   |                                    | 117                                 |     |                                    | 111 |     |                  |     |    |

| <sup>t</sup> pd    | CLK↑                                           | Q                 | with up to 4 outputs switching     | R1 = 200 Ω,                         | 1.5 |                                    | 4   | 1.5 |                  | 4   | ns |

|                    | CLK↑                                           | Q                 | with more than 4 outputs switching | R2 = $200 \Omega$ ,<br>See Figure 8 | 1.5 |                                    | 4   | 1.5 |                  | 4.5 |    |

| $t_{pd}$ ¶         | CLK↑                                           | Internal feedback |                                    |                                     |     |                                    | 3.5 |     |                  | 3.5 | ns |

| t <sub>en</sub>    | OE↓                                            | Q                 |                                    |                                     | 1.5 |                                    | 6   | 1.5 |                  | 6   | ns |

| <sup>t</sup> dis   | ŌE↑                                            | Q                 |                                    |                                     | 1   |                                    | 6.5 | 1   |                  | 7   | ns |

| t <sub>r</sub>     |                                                |                   |                                    |                                     |     | 1.5                                | ·   |     | 1.5              | ·   | ns |

| t <sub>f</sub>     |                                                |                   |                                    |                                     |     | 1.5                                |     |     | 1.5              |     | ns |

| tsk(o)#            | Skew between outputs                           |                   |                                    |                                     |     | 0.5                                |     |     | 0.5              |     | ns |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>&</sup>lt;sup>‡</sup> Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second. V<sub>O</sub> is set at 0.5 V to avoid test problems caused by test equipment ground degradation.

<sup>§</sup> See 'f<sub>max</sub> Specification' near the end of this data sheet.

This parameter is calculated from the measured f<sub>max</sub> with internal feedback in a counter configuration (see Figure 4 for illustration).

$<sup>^{\#}</sup>$  t<sub>Sk(0)</sub> is the skew time between registered outputs.

## TIBPAL20L8-7M, TIBPAL20R4-7M, TIBPAL20R6-7M, TIBPAL20R8-7M HIGH-PERFORMANCE *IMPACT-X*™ *PAL*® CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)    |          | . 7 V |

|-------------------------------------------------|----------|-------|

| Input voltage (see Note 1)                      |          | 5.5 V |

| Voltage applied to disabled output (see Note 1) |          | 5.5 V |

| Operating free-air temperature range            | −55°C to | 125°C |

| Storage temperature range                       | −65°C to | 150°C |

NOTE 1: These ratings apply except for programming pins during a programming cycle or during a preload cycle.

#### recommended operating conditions

|                      |                                             |      | MIN | NOM | MAX | UNIT |

|----------------------|---------------------------------------------|------|-----|-----|-----|------|

| VCC                  | Supply voltage                              |      |     | 5   | 5.5 | V    |

| VIH                  | High-level input voltage (see Note 2)       |      | 2   |     | 5.5 | V    |

| V <sub>IL</sub>      | Low-level input voltage (see Note 2)        |      |     |     | 0.8 | V    |

| ГОН                  | High-level output current                   |      |     |     | -2  | mA   |

| lOL                  | Low-level output current                    |      |     |     | 12  | mA   |

| f <sub>clock</sub> † | Clock frequency                             |      | 0   |     | 100 | MHz  |

| t <sub>w</sub> †     | Pulse duration, clock                       | High | 5   |     |     | ns   |

|                      |                                             | Low  | 5   |     |     | 113  |

| t <sub>su</sub> †    | Setup time, input or feedback before clock↑ |      |     |     |     | ns   |

| t <sub>h</sub> †     | Hold time, input or feedback after clock↑   |      |     |     |     | ns   |

| T <sub>A</sub>       | Operating free-air temperature              |      |     | 25  | 125 | °C   |

$^\dagger \, f_{clock}, \, t_W, \, t_{su}, \, \text{and} \, \, t_h \, \, \text{do not apply to TIBPAL16L8'}$

NOTE 2: These are absolute voltage levels with respect to the ground pin of the device and include all overshoots due to system and/or tester noise. Testing these parameters should not be attempted without suitable equipment.

## TIBPAL20L8-7M, TIBPAL20R4-7M, TIBPAL20R6-7M, TIBPAL20R8-7M HIGH-PERFORMANCE *IMPACT-X™ PAL®* CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

#### electrical characteristics over recommended operating free-air temperature range

| PARAMETER      |              |                           | TEST CONDITIONS                      |              | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|----------------|--------------|---------------------------|--------------------------------------|--------------|-----|------------------|------|------|

| VIK            |              | $V_{CC} = 4.5 \text{ V},$ | $I_{I} = -18 \text{ mA}$             |              |     | -0.8             | -1.5 | V    |

| Vон            |              | $V_{CC} = 4.5 \text{ V},$ | $I_{OH} = -2 \text{ mA}$             |              | 2.4 | 2.7              |      | V    |

| VOL            |              | $V_{CC} = 4.5 \text{ V},$ | $I_{OL} = 12 \text{ mA}$             |              |     | 0.25             | 0.5  | V    |

| lozh           | 0, Q outputs | V <sub>CC</sub> = 5.5 V,  | V- 27V                               |              |     |                  | 20   |      |

| I OZH          | I/O ports    | VCC = 5.5 V,              | $V_0 = 2.7 V$                        |              |     |                  | 100  | μΑ   |

| lozL           | 0, Q outputs | V <sub>CC</sub> = 5.5 V,  | V <sub>O</sub> = 0.4 V               | Vo = 0.4 V   |     |                  | -20  | μА   |

| .OZL           | I/O ports    | VCC = 0.0 V,              | VO = 0.4 V                           |              |     | -250             | μΛ   |      |

| II             |              | $V_{CC} = 5.5 V$ ,        | V <sub>I</sub> = 5.5 V               |              |     |                  | 1    | mA   |

| Ιн             | I/O ports    | V <sub>CC</sub> = 5.5 V,  | V <sub>I</sub> = 2.7 V               |              |     |                  | 100  | μΑ   |

| יור            | All others   | VCC = 0.0 V,              |                                      |              |     |                  | 25   |      |

| Iլլ            |              | $V_{CC} = 5.5 V$ ,        | V <sub>I</sub> = 0.4 V               |              |     |                  | -250 | μΑ   |

| los‡           |              | $V_{CC} = 5.5 V$ ,        | V <sub>O</sub> = 0.5 V               |              | -30 | -70              | -130 | mA   |

| Icc            |              | V <sub>CC</sub> = 5.5 V,  | $V_I = GND, \overline{OE} = V_{IH},$ | Outputs open |     |                  | 220  | mA   |

| C <sub>i</sub> |              | V <sub>I</sub> = 2 V      | V1 – 2 V                             |              | 8.5 |                  | pF   |      |

|                | CLK/OE       | 1 – 1 1711 12,            | v   - 2 v                            |              |     | 7.5              | ·    | ۲۰   |

| Co             |              | f = 1 MHz,                | V <sub>O</sub> = 2 V                 |              |     | 10               |      | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER          | FROM<br>(INPUT)                                                 | TO<br>(OUTPUT) | TEST CONDITION      | MIN | MAX | UNIT |

|--------------------|-----------------------------------------------------------------|----------------|---------------------|-----|-----|------|

|                    | without fo                                                      | eedback        |                     | 100 |     |      |

| f <sub>max</sub> § | f <sub>max</sub> § with internal feedbac (counter configuration |                |                     | 100 |     | MHz  |

|                    | with externa                                                    | al feedback    | R1 = 390 $\Omega$ , | 74  |     |      |

| <sup>t</sup> pd    | I, I/O                                                          | O, I/O         | $R2 = 750 \Omega$ , | 1   | 7   | ns   |

| t <sub>pd</sub>    | CLK                                                             | Q              | See Figure 8        | 1   | 7   | ns   |

| t <sub>en</sub>    | OE↓                                                             | Q              |                     | 1   | 8   | ns   |

| <sup>t</sup> dis   | OE↑                                                             | Q              |                     | 1   | 10  | ns   |

| t <sub>en</sub>    | I, I/O                                                          | O, I/O         |                     | 1   | 9   | ns   |

| <sup>t</sup> dis   | I, I/O                                                          | O, I/O         |                     | 1   | 10  | ns   |

$<sup>\</sup>S$  See 'f<sub>max</sub> Specification' near the end of this data sheet. f<sub>max</sub> does not apply for TIBPAL20L8'. f<sub>max</sub> with external feedback is not production tested and is calculated from the equation found in the f<sub>max</sub> specifications section.

<sup>&</sup>lt;sup>‡</sup> Not more than one output should be shorted at a time, and the duration of the short circuit should not exceed one second. V<sub>O</sub> is set at 0.5 V to avoid test problems caused by test equipment ground degradation.

# TIBPAL20L8-5C, TIBPAL20R4-5C, TIBPAL20R6-5C, TIBPAL20R8-5C TIBPAL20L8-7M, TIBPAL20R4-7M, TIBPAL20R6-7M, TIBPAL20R8-7M HIGH-PERFORMANCE *IMPACT-X™ PAL®* CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

#### programming information

Texas Instruments programmable logic devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and firmware are available upon request. Information on programmers capable of programming Texas Instruments programmable logic is also available, upon request, from the nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 997-5666.

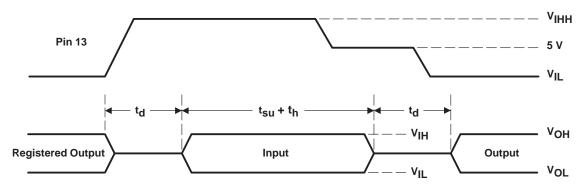

#### asynchronous preload procedure for registered outputs (see Figure 1 and Note 3)

The output registers can be preloaded to any desired state during device testing. This permits any state to be tested without having to step through the entire state-machine sequence. Each register is preloaded individually by following the steps given below.

- Step 1. With  $V_{CC}$  at 5 volts and Pin 1 at  $V_{II}$ , raise Pin 13 to  $V_{IHH}$ .

- Step 2. Apply either V<sub>II</sub> or V<sub>IH</sub> to the output corresponding to the register to be preloaded.

- Step 3. Lower Pin 13 to 5 V.

- Step 4. Remove output voltage, then lower Pin 13 to  $V_{IL}$ . Preload can be verified by observing the voltage level at the output pin.

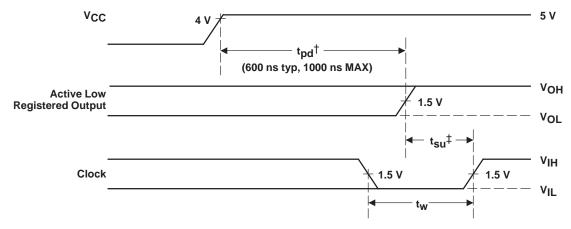

Figure 1. Asynchronous Preload Waveforms

NOTE 3:  $t_d = t_{SU} = t_h = 100 \text{ ns to } 1000 \text{ ns}, V_{IHH} = 10.25 \text{ V to } 10.75 \text{ V}$

# TIBPAL20L8-5C, TIBPAL20R4-5C, TIBPAL20R6-5C, TIBPAL20R8-5C TIBPAL20L8-7M, TIBPAL20R4-7M, TIBPAL20R6-7M, TIBPAL20R8-7M HIGH-PERFORMANCE IMPACT-X™ PAL® CIRCUITS

SRPS010F - D3353, OCTOBER 1989 - REVISED SEPTEMBER 1992

#### power-up reset, see Figure 2

Following power up, all registers are reset to zero. This feature provides extra flexibility to the system designer and is especially valuable in simplifying state-machine initialization. To ensure a valid power-up reset, it is important that the rise of  $V_{CC}$  be monotonic. Following power-up reset, a low-to-high clock transition must not occur until all applicable input and feedback setup times are met.

<sup>†</sup> This is the power-up reset time and applies to registered outputs only. The values shown are from characterization data.

Figure 2. Power-Up Reset Waveforms

<sup>&</sup>lt;sup>‡</sup>This is the setup time for input or feedback.

#### fmax SPECIFICATIONS

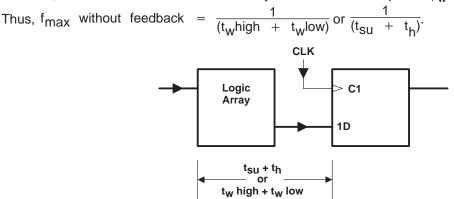

#### f<sub>max</sub> without feedback, see Figure 3

In this mode, data is presented at the input to the flip-flop and clocked through to the Q output with no feedback. Under this condition, the clock period is limited by the sum of the data setup time and the data hold time  $(t_{su} + t_h)$ . However, the minimum fmax is determined by the minimum clock period  $(t_w \text{ high } + t_w \text{ low})$ .

Figure 3. f<sub>max</sub> Without Feedback

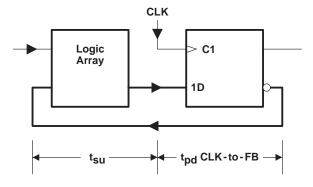

#### f<sub>max</sub> with internal feedback, see Figure 4

This configuration is most popular in counters and on-chip state-machine designs. The flip-flop inputs are defined by the device inputs and flip-flop outputs. Under this condition, the period is limited by the internal delay from the flip-flop outputs through the internal feedback and logic array to the inputs of the next flip-flop.

Thus,

$$f_{max}$$

with internal feedback =  $\frac{1}{(t_{su} + t_{pd} CLK - to - FB)}$ .

Where tpd CLK-to-FB is the deduced value of the delay from CLK to the input of the logic array.

Figure 4. f<sub>max</sub> With Internal Feedback

#### fmax SPECIFICATIONS

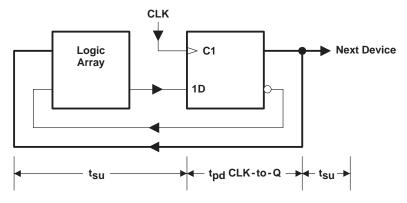

#### f<sub>max</sub> with external feedback, see Figure 5

This configuration is a typical state-machine design with feedback signals sent off-chip. This external feedback could go back to the device inputs or to a second device in a multi-chip state machine. The slowest path defining the period is the sum of the clock-to-output time and the input setup time for the external signals  $(t_{su} + t_{pd} CLK-to-Q)$ .

Thus,  $f_{max}$  with external feedback =  $\frac{1}{(t_{su} + t_{pd} CLK - to - Q)}$

Figure 5. f<sub>max</sub> With External Feedback

#### THERMAL INFORMATION

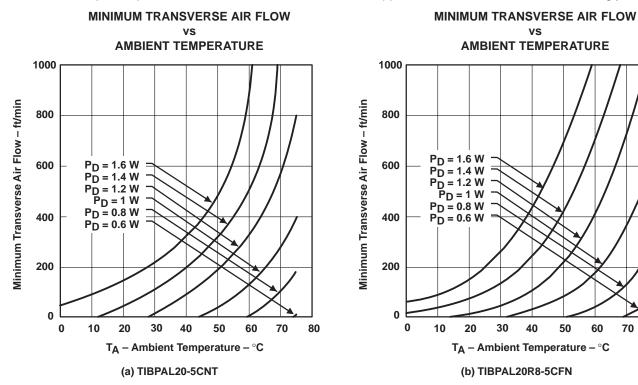

#### thermal management of the TIBPAL20R8-5C

Thermal management of the TIBPAL20R8-5CNT and TIBPAL20R8-5CFN is necessary when operating at certain conditions of frequency, output loading, and outputs switching simultaneously. The device and system application will determine the appropriate level of management.

Determining the level of thermal management is based on factors such as power dissipation (PD), ambient temperature  $(T_A)$ , and transverse airflow (FPM). Figures 6 (a) and 6 (b) show the relationship between ambient temperature and transverse airflow at given power dissipation levels. The required transverse airflow can be determined at a particular ambient temperature and device power dissipation level in order to ensure the device specifications.

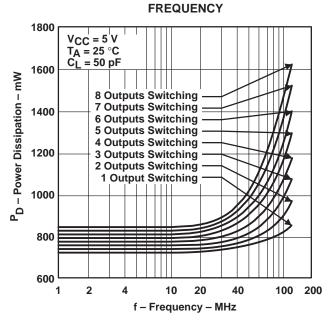

Figure 7 illustrates how power dissipation varies as a function of frequency and the number of outputs switching simultaneously. It should be noted that all outputs are fully loaded ( $C_1 = 50 \text{ pF}$ ). Since the condition of eight fully loaded outputs represents the worst-case condition, each application must be evaluated accordingly.

Figure 6

50

60

70

80

#### THERMAL INFORMATION

## POWER DISSIPATION vs

Figure 7

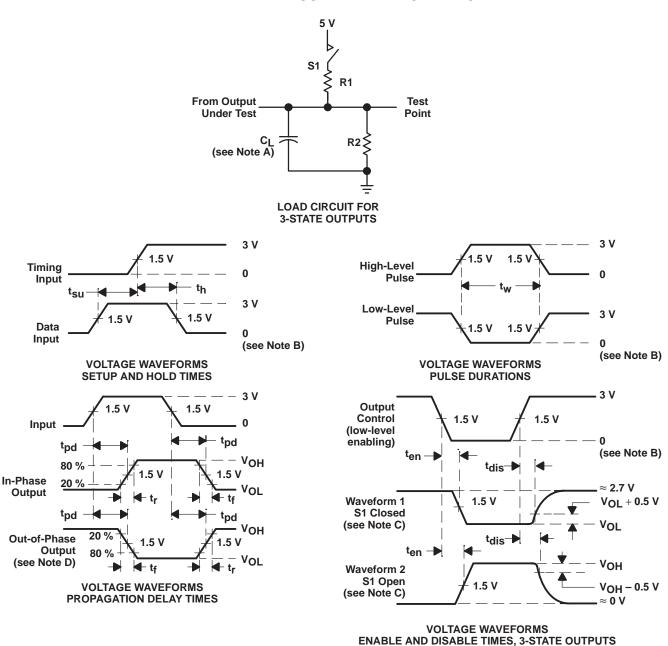

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $C_L$  includes probe and jig capacitance and is 50 pF for  $t_{pd}$  and  $t_{en}$ , 5 pF for  $t_{dis}$ .

- B. All input pulses have the following characteristics: For C suffix, PRR  $\leq$  1 MHz,  $t_r = t_f = 2$  ns, duty cycle = 50%; For M suffix, PRR  $\leq$  10 MHz,  $t_r = t_f \leq$  2 ns, duty cycle = 50%

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

- E. Equivalent loads may be used for testing.

Figure 8. Load Circuit and Voltage Waveforms

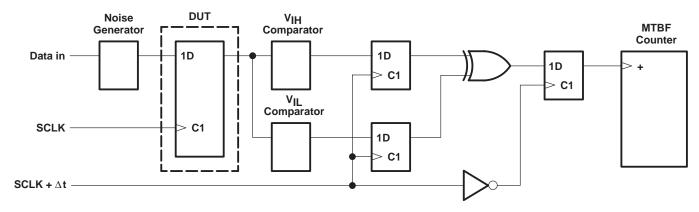

#### metastable characteristics of TIBPAL20R4-5C, TIBPAL20R6-5C, and TIBPAL20R8-5C

At some point a system designer is faced with the problem of synchronizing two digital signals operating at two different frequencies. This problem is typically overcome by synchronizing one of the signals to the local clock through use of a flip-flop. However, this solution presents an awkward dilemma since the setup and hold time specifications associated with the flip-flop are sure to be violated. The metastable characteristics of the flip-flop can influence overall system reliability.

Whenever the setup and hold times of a flip-flop are violated, its output response becomes uncertain and is said to be in the metastable state if the output hangs up in the region between  $V_{IL}$  and  $V_{IH}$ . This metastable condition lasts until the flip-flop falls into one of its two stable states, which takes longer than the specified maximum propagation delay time (CLK to Q max).

From a system engineering standpoint, a designer cannot use the specified data sheet maximum for propagation delay time when using the flip-flop as a data synchronizer – how long to wait after the specified data sheet maximum must be known before using the data in order to guarantee reliable system operation.

The circuit shown in Figure 9 can be used to evaluate MTBF (Mean Time Between Failure) and  $\Delta t$  for a selected flip-flop. Whenever the Q output of the DUT is between 0.8 V and 2 V, the comparators are in opposite states. When the Q output of the DUT is higher than 2 V or lower than 0.8 V, the comparators are at the same logic level. The outputs of the two comparators are sampled a selected time ( $\Delta t$ ) after SCLK. The exclusive OR gate detects the occurrence of a failure and increments the failure counter.

Figure 9. Metastable Evaluation Test Circuit

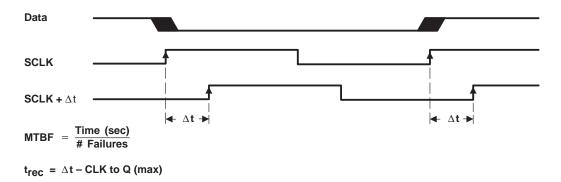

In order to maximize the possibility of forcing the DUT into a metastable state, the input data signal is applied so that it always violates the setup and hold time. This condition is illustrated in the timing diagram in Figure 10. Any other relationship of SCLK to data will provide less chance for the device to enter into the metastable state.

Figure 10. Timing Diagram

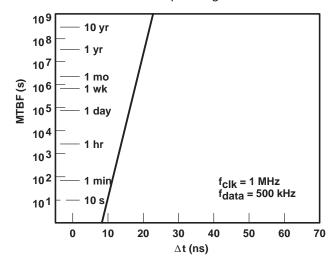

By using the described test circuit, MTBF can be determined for several different values of  $\Delta t$  (see Figure 9). Plotting this information on semilog scale demonstrates the metastable characteristics of the selected flip-flop. Figure 11 shows the results for the TIBPAL20'-5C operating at 1 MHz.

Figure 11. Metastable Characteristics

From the data taken in the above experiment, an equation can be derived for the metastable characteristics at other clock frequencies.

The metastable equation:

$$\frac{1}{MTBF} = f_{SCLK} \times f_{data} \times C1 e^{(-C2 \times \Delta t)}$$

The constants C1 and C2 describe the metastable characteristics of the device. From the experimental data, these constants can be solved for:  $C1 = 4.37 \times 10^{-3}$  and C2 = 2.01

Therefore

$$\frac{1}{\text{MTBF}} = f_{\text{SCLK}} \times f_{\text{data}} \times 4.37 \times 10^{-3} \text{ e}^{(-2.01 \times \Delta t)}$$

#### definition of variables

DUT (Device Under Test): The DUT is a 5-ns registered PLD programmed with the equation Q := D.

MTBF (Mean Time Between Failures): The average time (s) between metastable occurrences that cause a violation of the device specifications.

fSCLK (system clock frequency): Actual clock frequency for the DUT.

f<sub>data</sub> (data frequency): Actual data frequency for a specified input to the DUT.

C1: Calculated constant that defines the magnitude of the curve.

C2: Calculated constant that defines the slope of the curve.

$t_{rec}$  (metastability recovery time): Minimum time required to guarantee recovery from metastability, at a given MTBF failure rate.  $t_{rec} = \Delta t - t_{od}$  (CLK to Q, max)

Δt: The time difference (ns) from when the synchronizing flip-flop is clocked to when its output is sampled.

The test described above has shown the metastable characteristics of the TIBPAL20R4/R6/R8-5C series. For additional information on metastable characteristics of Texas Instruments logic circuits, please refer to TI Applications publication SDAA004, "Metastable Characteristics, Design Considerations for ALS, AS, and LS Circuits."

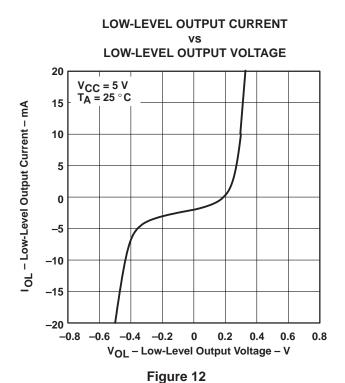

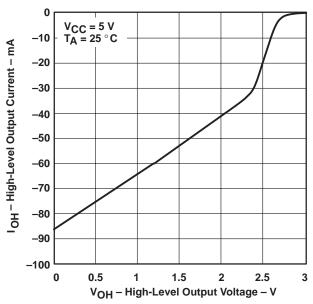

#### TYPICAL CHARACTERISTICS

HIGH-LEVEL OUTPUT CURRENT vs

HIGH-LEVEL OUTPUT VOLTAGE

Figure 13

Figure 14

#### TYPICAL CHARACTERISTICS

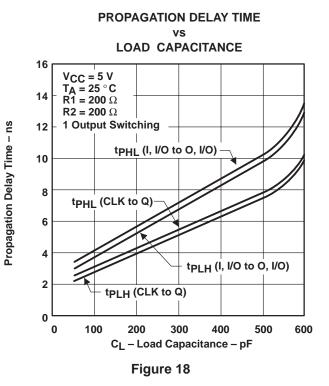

Propagation Delay Time - ns

#### **POWER DISSIPATION FREQUENCY 8-BIT COUNTER MODE** 1100 $V_{CC} = 5 V$ P<sub>D</sub> - Power Dissipation - mW $T_A = 80 \, ^{\circ} C$ 1000 $T_A = 25 \, ^{\circ} C$ 900 $T_A = 0 \circ C$ $T_A = 0 \circ C$ $T_A = 80 \, ^{\circ}C$ 800 700 2 20 200 10 40 100 f - Frequency - MHz Figure 15

#### TYPICAL CHARACTERISTICS

Propagation Delay Time - ns

**PROPAGATION DELAY TIME** vs NUMBER OF OUTPUTS SWITCHING  $V_{CC} = 5 V$  $T_{A} = 25 \,^{\circ}C$  $C_L = 50 pF$ 5  $R1 = 200 \Omega$  $R2 = 200 \Omega$ 3 2  $\Delta = t_{PHL} (I, I/O to O, I/O)$ ▲ = tplH (I, I/O to O, I/O) 1 o = tpHL (CLK to Q) • = tpLH (CLK to Q) 0 8 **Number of Outputs Switching**

Figure 20

# TI North **Offices**

ALABAMA: Huntsville: (205) 837-7530 ARIZONA: Phoenix: (602) 995-1007 CALIFORNIA: Irvine: (714) 660-1200 San Diego: (619) 278-9600 Santa Clara: (408) 980-9000 Woodland Hills: (818) 704-8100 COLORADO: Aurora: (303) 368-8000 CONNECTICUT: Wallingford: (203) 269-0074 FLORIDA: Altamonte Springs: (407) 260-2116 Fort Lauderdale: (305) 973-8502 Tampa: (813) 885-7588

GEORGIA: Norcross: (404) 662-7967 ILLINOIS: Arlington Heights: (708) 640-3000

INDIANA: Carmel: (317) 573-6400 Fort Wayne: (219) 489-4697 KANSAS: Overland Park: (913) 451-4511 MARYLAND: Columbia: (410) 964-2003 MASSACHUSETTS: Waltham: (617) 895-9100 MICHIGAN: Farmington Hills: (313) 553-1581 MINNESOTA: Eden Prairie: (612) 828-9300 MISSOURI: St. Louis: (314) 821-8400 NEW JERSEY: Iselin: (908) 750-1050 NEW MEXICO: Albuquerque: (505) 345-2555

NEW YORK: East Syracuse: (315) 463-9291 Fishkill: (914) 897-2900 Melville: (516) 454-6600 Pittsford: (716) 385-6770

NORTH CAROLINA: Charlotte: (704) 527-0930 Raleigh: (919) 876-2725

OHIO: Beachwood: (216) 765-7258 Beavercreek: (513) 427-6200 OREGON: Beaverton: (503) 643-6758 PENNSYLVANIA: Blue Bell: (215) 825-9500 PUERTO RICO: Hato Rey: (809) 753-8700

TEXAS: Austin: (512) 250-6769

Dallas: (214) 917-1264

Houston: (713) 778-6592

Midland: (915) 561-7137

UTAH: Salt Lake Clty: (801) 466-8972 WISCONSIN: Waukesha: (414) 798-1001 CANADA: Nepean: (613) 726-1970 Richmond Hill: (416) 884-9181 St. Laurent: (514) 335-8392

### TI Regional **Technology Centers**

CALIFORNIA: Irvine: (714) 660-8140 Santa Clara: (408) 748-2222 GEORGIA: Norcross: (404) 662-7945 ILLINOIS: Arlington Heights: (708) 640-2909 INDIANA: Indianapolis: (317) 573-6400 MASSACHUSETTS: Waltham: (617) 895-9196 MEXICO: Mexico City: 491-70834 MINNESOTA: Minneapolis: (612) 828-9300 TEXAS: Dallas: (214) 917-3881 CANADA: Nepean: (613) 726-1970

#### Customer **Response Center**

**TOLL FREE:** (800) 336-5236 OUTSIDE USA: (214) 995-6611

(8:00 a.m. - 5:00 p.m. CST)

### **TI Authorized** American Sales North American **Distributors**

Alliance Electronics, Inc. (military product only) Almac/Arrow

Anthem Electronics

Arrow/Schweber

Future Electronics (Canada)

GRS Electronics Co., Inc. Hall-Mark Flectronics Hall-mark Electronics

Marshall Industries

Newark Electronics

Rochester Electronics, Inc.

(obsolete product only (508) 462-9332)

Wyle Laboratories

Zeus Components

### **TI Distributors**

**ALABAMA:** Arrow/Schweber (205) 837-6955; Hall-Mark (205) 837-8700; Marshall (205) 881-9235.

(205) 837-8700; Marshall (205) 881-9235.

ARIZONA: Anthem (602) 966-6600; Arrow/Schweber (602) 437-0750; Hall-Mark (602) 431-0030; Marshall (602) 496-0290; Wylle (602) 437-2088.

CALIFORNIA: Los Angeles/Orange County: Anthem (818) 775-1333, (714) 768-4444; Arrow/Schweber (818) 380-9686, (714) 838-5422; Hall-Mark (818) 773-4500, (714) 727-6000; Marshall (818) 878-7000, (714) 458-5301; Wyle (818) 880-9900, (714) 863-9953; Zeus (714) 921-9000, (818) 889-3838:

(619) 669-3636, Sacramento: Anthem (916) 624-9744; Hall-Mark (916) 624-9781; Marshall (916) 635-9700; Wyle (916) 638-5282; San Diego: Anthem (619) 453-9005; Arrow/Schweber (619) 565-4800; Hall-Mark (619) 268-1201; Marshall (619) 578-9600; Wyle (619) 565-9171; Zeus (619) 277-9681.

San Francisco Bay Area: Anthem (408) 453-1200; Arrow/Schweber (408) 441-9700, (510) 490-9477; Hall-Mark (408) 432-4000; Marshall (408) 942-4600; Wyle (408) 727-2500; Zeus (408) 629-4789.

**COLORADO:** Anthem (303) 790-4500; Arrow/Schweber (303) 799-0258; Hall-Mark (303) 790-1662; Marshall (303) 451-8383; Wyle (303) 457-9953.

CONNECTICUT: Anthem (203) 575-1575; Arrow/Schweber (203) 265-7741; Hall-Mark (203) 271-2844; Marshall (203) 265-3822.

**FLORIDA: Fort Lauderdale:** Arrow/Schweber (305) 429-8200; Halll-Mark (305) 971-9280; Marshall (305)

**Orlando:** Arrow/Schweber (407) 333-9300; Hall-Mark (407) 830-5855; Marshall (407) 767-8585; Zeus (407) 788-9100. Tampa: Hall-Mark (813) 541-7440; Marshall (813) 573-1399.

**GEORGIA:** Arrow/Schweber (404) 497-1300; Hall-Mark (404) 623-4400; Marshall (404) 923-5750.

ILLINOIS: Anthem (708) 884-0200; Arrow/Schweber (708) 250-0500; Hall-Mark (312) 860-3800; Marshall (708) 490-0155; Newark (312)784-5100.

INDIANA: Arrow/Schweber (317) 299-2071; Hall-Mark (317) 872-8875; Marshall (317) 297-0483. IOWA: Arrow/Schweber (319) 395-7230.

KANSAS: Arrow/Schweber (913) 541-9542; Hall-Mark (913) 888-4747; Marshall (913) 492-3121.

MARYLAND: Anthem (301) 995-6640; Arrow/Schweber (301) 596-7800; Hall-Mark (301) 988-9800; Marshall (301) 622-1118; Zeus (301) 997-1118.

MASSACHUSETTS: Anthem (508) 657-5170; Arrow/Schweber (508) 658-0900; Hall-Mark (508) 667-0902; Marshall (508) 658-0810; Wyle (617) 272-7300; Zeus (617) 246-8200.

MICHIGAN: Detroit: Arrow/Schweber (313) 462-2290; Hall-Mark (313) 416-5800; Marshall (313) 525-5850; Newark (313) 967-0600.

MINNESOTA: Anthem (612) 944-5454; Arrow/Schweber (612) 941-5280; Hall-Mark (612) 881-2600; Marshall (612) 559-2211.

MISSOURI: Arrow/Schweber (314) 567-6888; Hall-Mark (314) 291-5350; Marshall (314) 291-4650.

NEW JERSEY: Anthem (201) 227-7960; Arrow/Schweber (201) 227-7860, (609) 596-8000; Hall-Mark (201) 515-3000, (609) 235-1900; Marshall (201) 882-0320, (609) 234-9100. NEW MEXICO: Alliance (505) 292-3360.

NEW YORK: Long Island: Anthem (516) 864-6600; NEW YORK: Long Island: Anthem (516) 864-6600; Arrow/Schweber (516) 231-1000; Hall-Mark (516) 737-0600; Marshall (516) 273-2424; Zeus (914) 937-7400. Rochester: Arrow/Schweber (716) 427-0300; Hall-Mark (716) 425-3300; Marshall (716) 235-7620.

Syracuse: Marshall (607) 785-2345.

NORTH CAROLINA: Arrow/Schweber (919) 876-3132; Hall-Mark (919) 872-0712; Marshall (919) 878-9882.

OHIO: Cleveland: Arrow/Schweber (216) 248-3990; Hall-Mark (216) 349-4632; Marshall (216) 248-1788.

Columbus: Hall-Mark (614) 888-3313.

Dayton: Arrow/Schweber (513) 435-5563; Marshall (513) 898-4480; Zeus (513) 293-6162.

OKLAHOMA: Arrow/Schweber (918) 252-7537; Hall-Mark

**OREGON:** Almac/Arrow (503) 629-8090; Anthem (503) 643-1114; Marshall (503) 644-5050; Wyle (503) 643-7900.

PENNSYLVANIA: Anthem (215) 443-5150;

Arrow/Schweber (215) 928-1800; GRS (215) 922-7037;

(609) 964-8560; Marshall (412) 788-0441.

TEXAS: Austin: Arrow/Schweber (512) 835-4180;

Hall-Mark (512) 258-8848; Marshall (512) 837-1991; Wyle (512) 345-8853;

**Dallas:** Anthem (214) 238-7100; Arrow/Schweber (214) 380-6464; Hall-Mark (214) 553-4300; Marshall (214) 233-5200; Wyle (214) 235-9953; Zeus (214) 783-7010; Houston: Arrow/Schweber (713) 530-4700; Hall-Mark (713) 781-6100; Marshall (713) 467-1666; Wyle (713) 879-9953.

UTAH: Anthem (801) 973-8555; Arrow/Schweber (801) 973-6913; Marshall (801) 973-2288; Wyle (801) 974-9953. WASHINGTON: Almac/Arrow (206) 643-9992, Anthem (206) 483-1700; Marshall (206) 486-5747; Wyle (206) 881-1150.

**WISCONSIN:** Arrow/Schweber (414) 792-0150; Hall-Mark (414) 797-7844; Marshall (414) 797-8400.

CANADA: Calgary: Future (403) 235-5325;

Edmonton: Future (403) 438-2858

**Montreal:** Arrow/Schweber (514) 421-7411; Future (514) 694-7710; Marshall (514) 694-8142

Ottawa: Arrow/Schweber (613) 226-6903; Future (613) 820-8313

Quebec: Future (418) 897-6666. **Toronto:** Arrow/Schweber (416) 670-7769; Future (416) 612-9200; Marshall (416) 458-8046.

Vancouver: Arrow/Schweber (604) 421-2333; Future (604) 294-1166.

#### **TI Die Processors**

Chip Supply (407) 298-7100 Elmo Semiconductor (818) 768-7400 Minco Technology Labs (512) 834-2022

D0892

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated