# Ambassador™ T8100A, T8102, and T8105 H.100/H.110 Interface and Time-Slot Interchangers

#### Introduction

This advisory describes a flaw in some devices that the initial factory test program did not detect. The flaw exists in some version 2 and version 3 T8100A, T8102, and T8105 devices in both the SQFP and BGA package types. An enhanced factory test program has been in place since January 2000, and all devices shipped after this date are good devices.

#### **Problem: Data Memory Error**

An error in the CAM data memories may cause the corruption of stream data bits and/or bytes. The problem may also occur in the microprocessor read path. Stream data may have an occasional '0' that should be a '1'. An entire bad byte may also occur. The problem going away with lower VDD is a prime indicator of this problem. Not all devices are bad.

#### Workaround

There is no workaround for this flaw.

#### **Corrective Action**

Version 2 and version 3 devices that have the second line of markings ending with W01, W02, W03, W04, W05, W06, W07, W08, and W09 may be returned through Lucent's return material authorization (RMA) process for replacement or credit. Devices that have the second line of markings ending with W10, W11, and W12 are known good devices and do not have to be returned. To return devices, contact your sales person for an RMA number. Enter the RMA number within the following return address:

Lucent Technologies Christa Bromfield RMA #\_\_\_\_\_ 555 Union Blvd., Rm. 31L-30R BU Allentown, PA 18103

#### **Explanation of Version Markings**

The three versions can be identified by markings on the device and apply to the T8100A, T8102, and T8105.

#### Version 1

If there are only seven digits on the last line of the device code marking, and there is not an S following the 4-digit date code, the device is version 1 and applies to both the SQFP and BGA package types.

#### Version 2

- If there are seven digits on the last line of the device code followed by a space and the letters V2, the device is version 2; or

- 2. If there is an S following the 4-digit date code on line 2, the device is version 2. This marking applies to both SQFP and BGA package types.

#### **Version 3**

- 1. For the BGA package type, if the first line ends in BAL3, the device is version 3; or

- 2. For the SQFP package type, if the first line ends in SC3, the device is version 3.

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103 N. AMERICA:

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495

CHINA: Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai 200233 P. R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652

Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 EUROPE:

Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot),

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information. Ambassador is a trademark of Lucent Technologies Inc.

Copyright © 2000 Lucent Technologies Inc. All Rights Reserved

JAPAN:

microelectronics group

# Exceptions and Clarifications for *Ambassador*<sup>™</sup> T8100A, T8102, and T8105 H.100/H.110 Interface and Time-Slot Interchangers

#### **Device Exceptions**

Users of the *Ambassador* T8100A, T8102, and T8105 devices should be aware of the following device operation exceptions and the associated solutions:

When a compatibility clock is programmed as a slave, and the board generates A or B clocks, the watchdog will indicate an error on the A or B clocks it generates. The error will be reported even though the generated clocks are good.

**Workaround**: Use the master board to accurately monitor the clocks.

When a compatibility clock is programmed as a slave, and the clock selector is set to A or B clocks with slide phase alignment, the slave board does not lock and the generated frame continues sliding.

Workaround: None.

Product Status: Device redesign required.

3. Models of the Ambassador T8100A, T8102, and T8105 devices exhibit intermittent corrupted timeslot data. H.100 stream 0 time slot 1 (for outgoing data) and H.100 stream 1 time slot 127 (for incoming data at 8.192 MHz, time slot 63 for 4.096 MHz, and time slot 31 for 2.048 MHz) are the most likely stream/time slots to be corrupted. However, intermittent time-slot corruption may occur in other stream/time slots.

The time-slot corruption problem occurs when a T810x device is used in slave-timing mode, as described in Section 2.5 of the Data Sheet. In a typical slave timing application, a T810x device is set to phase align to an incoming bitclock/frame reference pair (i.e., slave to CT\_C8\_A/FRAME\_A, CT\_C8\_B/FRAME\_B, C4/FR\_COMP, etc.). Both SNAP and SLIDE alignment modes are affected. Devices that don't require phase alignment to these clocks (i.e., the primary bus master) should not exhibit stream data corruption.

Root Cause: The analog PLL has an error which introduces an unexpected 6 ns—7 ns of skew. This skew causes the phase alignment circuit to fail intermittently, whether in the SNAP or SLIDE mode. An intermittent SLIDE produces an internal frame signal that does not align and phase lock with an incoming frame reference. An intermittent SNAP forces a reset of the internal counters and results in corrupted stream data.

**Workaround**: There is no workaround. The solution is a fix to the silicon. Samples are scheduled for release in August 1999.

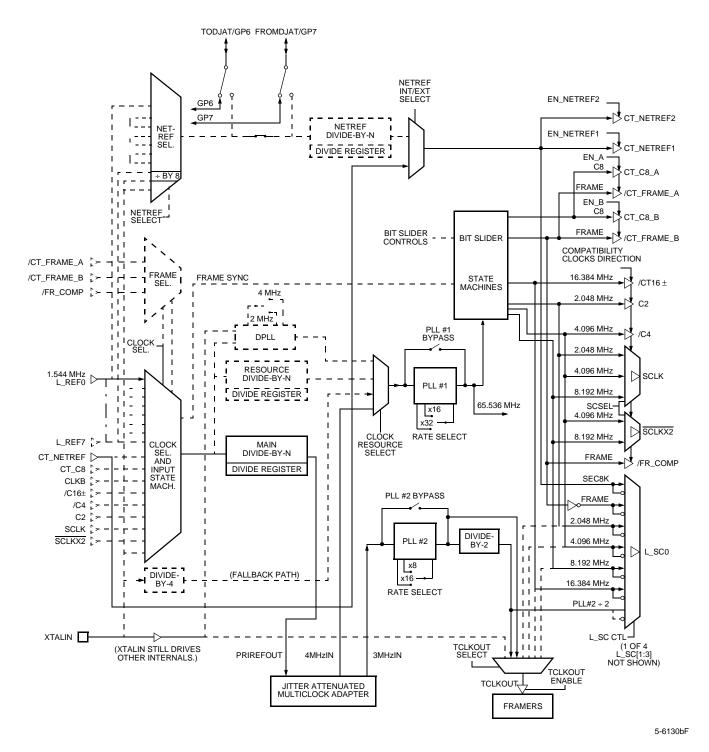

4. Version 2 models of the Ambassador T8100A, T8102, and T8105 devices can exhibit intermittent corrupted time slot data in one specific configuration. The problem occurs when a master T810x device is given an 8 kHz signal as the timing reference and multiplies it up to 2.048 MHz or 4.096 MHz in the digital PLL (DPLL). The DPLL introduces sufficient jitter on the A or B master output clocks that slave devices falsely interpret as a loss of sync and either snap or slide align to this false sync indication. This, in turn, causes corruption of time slot data. Any master timing reference that does not make use of the DPLL does not exhibit the problem.

**Workaround**: Do not use an 8 kHz signal as the A or B master timing reference, since this requires use of the DPLL. Instead, supply a jitter-free timing reference at any of the other allowable frequencies (2.048, 4.096, 8.192 or 16.384 MHz).

**Product Status**: The solution is a fix to the silicon.

#### **Device Clarifications**

The three device clarifications listed in this space have been incorporated into DS00-028CTI.

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103 N. AMERICA:

**1-800-372-2447**, FAX 610-712-4106 (In CANADA: **1-800-553-2448**, FAX 610-712-4106)

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA: Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai

200233 P. R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information. Ambassador is a trademark of Lucent Technologies Inc.

**Lucent Technologies**

microelectronics group

# Ambassador<sup>™</sup> T8100A, T8102, and T8105 H.100/H.110 Interfaces and Time-Slot Interchangers

#### 1 Product Overview

#### 1.1 Features

- Complete solution for interfacing board-level circuitry to the H.100 telephony bus

- H.100 compliant interface; all mandatory signals

- Programmable connections to any of the 4096 time slots on the H.100 bus

- Up to 16 local serial inputs and 16 local serial outputs, programmable for 2.048 Mbits/s,

4.096 Mbits/s, and 8.192 Mbits/s operation per CHI specifications

- Programmable switching between local time slots, up to 1024 connections

- Subrate switching of nibbles, dibits, or bits

- Backward compatible to T8100 through software

- Programmable switching between local time slots and H.100 bus, up to 512 (T8102, T8105 only) connections

- Choice of frame integrity or minimum latency switching on a per-time-slot basis

- Frame integrity to ensure proper switching of wideband data

- Minimum latency switching to reduce delay in voice channels

- On-chip phase-locked loop (PLL) for H.100, MVIP\*, or SC-Bus clock operation in master or slave clock modes

- Serial TDM bus rate and format conversion between most standard buses

- Optional 8-bit parallel input and/or 8-bit parallel output for local TDM interfaces

- High-performance microprocessor interface

- Provides access to device configuration registers and to time-slot data

- Supports both Motorola<sup>†</sup> nonmultiplexed and Intel<sup>‡</sup> multiplexed/nonmultiplexed modes

- Two independently programmable groups of up to 12 framing signals each

- Devices available in 0.25 micron technology

- 3.3 V supply with 5 V tolerant inputs and TTL-compatible outputs

- Boundary-scan testing support

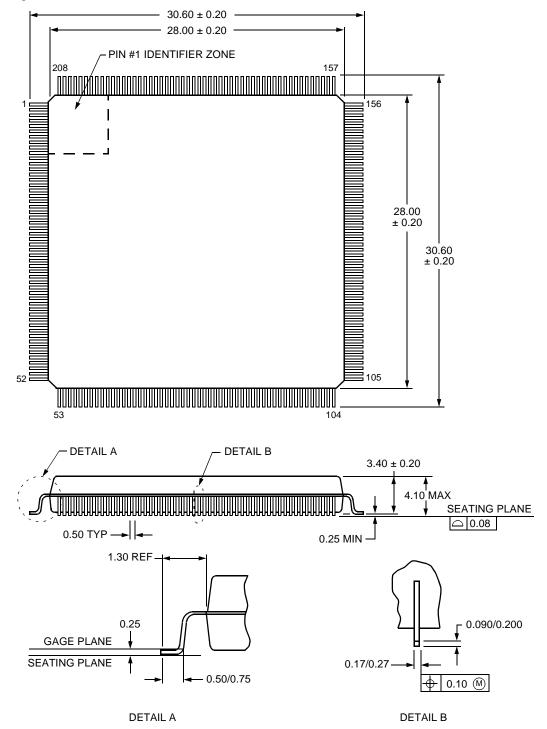

- 208-pin, plastic SQFP package

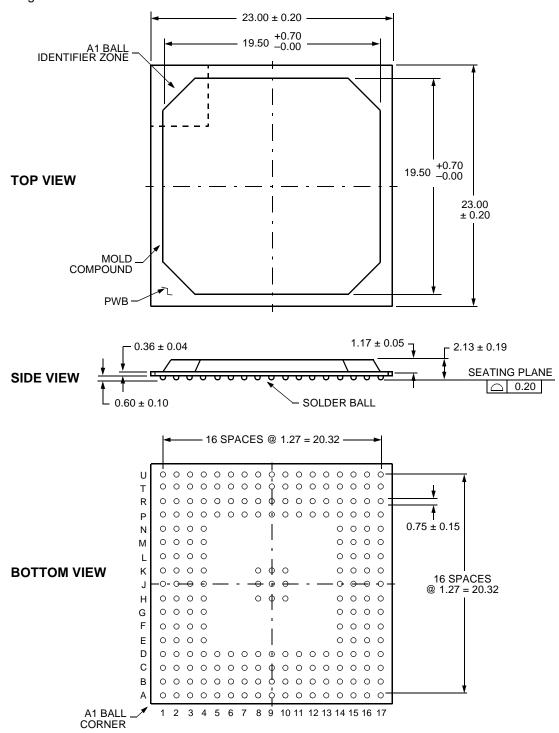

- 217-ball BGA package (industrial temperature range)

#### 1.2 Description

These products in the *Ambassador* T8100 family provide a complete time-slot switch and an interface for the H.100/H.110 time-division multiplexed (TDM) buses. The T8100 family includes devices with hierarchical switching as well as a capacity of up to 512 local to H.100 connections. The hierarchical switching allows up to 1024 local connections without using H.100 bus bandwidth. The family also includes the T8102 device for a low-cost solution in nonhierarchical systems.

All three TSI chips are backward compatible with the bus standards *MVIP*-90 and *Dialogic*'s SC-Bus, as well as supporting the newer standards, H-*MVIP* and ECTF H.100. Other features include a built-in PLL for H.100, *MVIP*, or SC-Bus clock operation in master or slave clock modes and two independently programmable groups of up to 12 framing signals each. Packaged in both a 208-pin SQFP and a 217-ball BGA, the T8100 TSI devices provide an economic solution for the computer telephony market.

- \* MVIP is a registered trademark of GO-MVIP, Inc.

- † Motorola is a registered trademark of Motorola, Inc.

- ‡ Intel is a registered trademark of Intel Corporation.

- § *Dialogic* is a registered trademark of Dialogic Corporation.

## **Table of Contents**

| Contents Page 1                                 | age | Contents P                                      | Page |  |

|-------------------------------------------------|-----|-------------------------------------------------|------|--|

| 1 Product Overview                              | 1   | 2.5.2 Dividers and Rate Multipliers             | 45   |  |

| 1.1 Features                                    | 1   | 2.5.3 State Machines                            | 45   |  |

| 1.2 Description                                 | 1   | 2.5.4 Frame Sync                                | 45   |  |

| 1.3 Pin Information                             | 6   | 2.5.5 Bit Sliding (Frame Locking)               | 45   |  |

| 1.4 Ambassador TSI Architecture                 | 12  | 2.5.6 MTIE                                      |      |  |

| 1.5 Selecting Between T8105, T8102, T8100A,     |     | 2.5.6.1 MTIE Compliance                         | 46   |  |

| and T8100                                       | 12  | 2.5.6.2 Relationship of the Bit Slider to MTIE. | 46   |  |

| 1.6 Enhanced Local Stream Addressing            | 12  | 2.5.6.3 Using the Bit Slider                    |      |  |

| 1.7 Full H.100 Stream Address Support           | 12  | 2.5.7 Clock Fallback                            | 47   |  |

| 1.8 Onboard PLLs and Clock Monitors             | 12  | 2.5.8 Clock Control Register Definitions        | 49   |  |

| 1.9 Phase Alignment of Referenced and           |     | 2.5.8.1 Basic Fallback Mode                     | 54   |  |

| Generated Frames                                | 12  | 2.5.8.2 CKMD, CKND, CKRD: Clocks, Main,         |      |  |

| 1.10 Interfaces                                 | 13  | NETREF, Resource Dividers                       |      |  |

| 1.10.1 Microprocessors                          | 13  | 0x07, 0x08, 0x09                                | 55   |  |

| 1.10.2 Framing Groups                           | 13  | 2.5.9 LREF Pairing                              |      |  |

| 1.10.3 General-Purpose Register and I/O         | 13  | 2.5.9.1 LREF Port Configuration                 | 57   |  |

| 1.11 Applications                               | 13  | 2.5.9.2 Operation                               | 58   |  |

| 1.12 Application Overview                       |     | 2.5.9.3 Example of LREF Pairing on a T8100      | A 58 |  |

| 2 Architecture and Functional Description       |     | 2.5.9.4 Advantages of LREF Pairing              |      |  |

| 2.1 Register/Memory Maps                        | 15  | 2.6 Interface Section                           |      |  |

| 2.1.1 Main Registers                            |     | 2.6.1 Microprocessor Interface                  | 58   |  |

| 2.1.2 Master Control and Status Register        |     | 2.6.2 General-Purpose Register                  | 58   |  |

| 2.1.3 Address Mode Register                     |     | 2.6.3 Framing Groups                            |      |  |

| 2.1.4 Control Register Memory Space             |     | 2.6.3.1 Frame Group Timing                      |      |  |

| 2.2 Local Bus Section                           |     | 2.7 Error Registers                             |      |  |

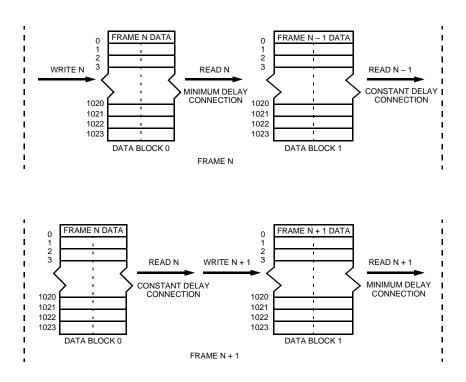

| 2.2.1 Constant Frame Delay and Minimum          |     | 2.8 The JTAG Test Access Port                   |      |  |

| Delay Connections                               | 24  | 2.8.1 Overview of the JTAG Architecture         | 64   |  |

| 2.2.2 Serial and Parallel                       |     | 2.8.2 Overview of the JTAG Instructions         | 64   |  |

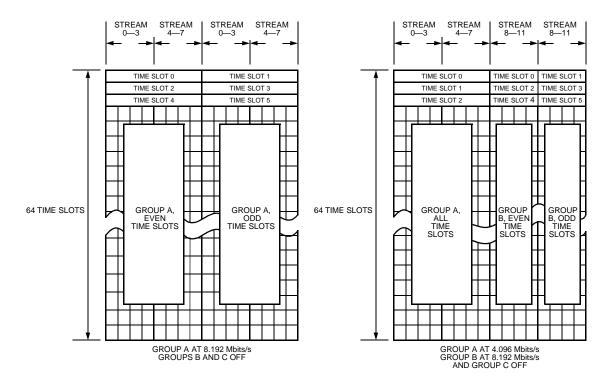

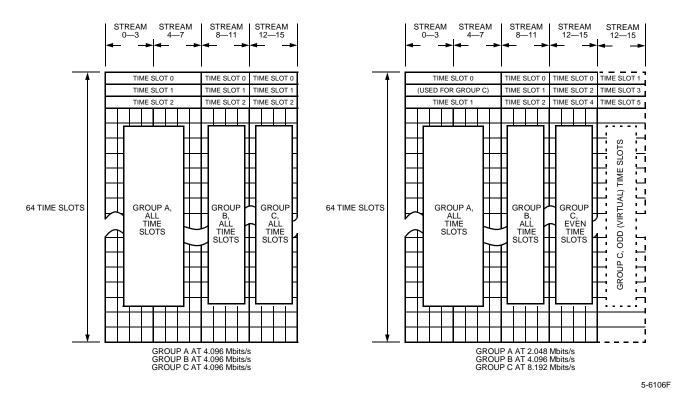

| 2.2.3 Data Rates and Time-Slot Allocation       | 25  | 2.8.3 Elements of JTAG Logic                    | 65   |  |

| 2.2.4 LBS: Local Stream Control, 0x0C           | 28  | 2.9 Testing and Diagnostics                     |      |  |

| 2.2.5 State Counter Operation                   | 29  | 2.9.1 Testing Operations                        |      |  |

| 2.2.6 Software to Reset the Local Connection    |     | 2.9.2 Diagnostics                               |      |  |

| Memory                                          | 29  | 3 Using the TSI Devices                         | 69   |  |

| 2.3 H-Bus Section                               | 30  | 3.1 Resets                                      |      |  |

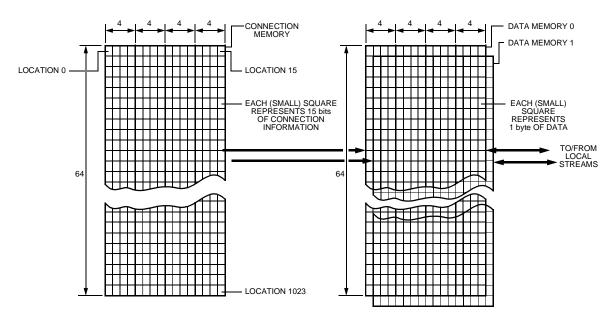

| 2.3.1 Memory Architecture                       | 30  | 3.1.1 Hardware Reset                            | 69   |  |

| 2.3.2 CAM Operation and Commands                | 32  | 3.1.2 Software Reset                            | 69   |  |

| 2.3.3 H-Bus Access                              | 36  | 3.1.3 Power-On Reset                            | 69   |  |

| 2.3.4 L-Bus Access                              | 37  | 3.2 Device Settings                             | 70   |  |

| 2.3.5 H-Bus Rate Selection and Connection       |     | 3.2.1 Architecture                              | 70   |  |

| Address Format                                  | 37  | 3.3 Basic Connections                           | 71   |  |

| 2.4 Subrate Switching for the <i>Ambassador</i> |     | 3.3.1 LPUE Control Pins                         | 71   |  |

| Family                                          | 39  | 3.3.2 H.100/H.110 Data Pin Series               |      |  |

| 2.4.1 Description, Operation, and Application   | 39  | Termination                                     | 71   |  |

| 2.4.2 Definitions                               | 39  | 3.3.3 H.110 Hot Swap                            | 71   |  |

| 2.4.3 Subrate Switching on H.100/H.110          | 39  | 3.3.4 Physical Connections for H.100            | 72   |  |

| 2.4.4 Using the Existing Architecture           | 40  | 3.3.5 Physical Connections for H.110            |      |  |

| 2.4.5 Limitations                               |     | 3.3.6 PC Board BGA Considerations               |      |  |

| 2.4.6 Minimum vs. Constant Delay                | 43  | 3.4 Using the LAR, AMR, and IDR for             |      |  |

| 2.4.7 Example of a Practical Application        | 43  | Connections                                     | 73   |  |

| 2.5 Clocking Section                            |     | 3.4.1 Setting Up Local Connections (T8100A,     |      |  |

| 2.5.1 Clock and NETREF Selection                | 45  | T8105 Only)                                     | 73   |  |

## Table of Contents (continued)

| Figures Pag                                | је                          |

|--------------------------------------------|-----------------------------|

| Figure 1. 208 SQFP—Top View                | . 6                         |

|                                            |                             |

| Figure 3. Block Diagram of the TSI Devices | 14                          |

| •                                          |                             |

|                                            |                             |

| ·                                          |                             |

|                                            |                             |

|                                            | 26                          |

|                                            |                             |

|                                            | 29                          |

|                                            |                             |

|                                            |                             |

|                                            | 33                          |

|                                            |                             |

|                                            |                             |

| <b>5</b> 1                                 |                             |

| S S                                        |                             |

|                                            | 42                          |

|                                            |                             |

|                                            | 43                          |

| ·                                          |                             |

| 0                                          |                             |

|                                            | 47                          |

|                                            |                             |

|                                            |                             |

|                                            |                             |

| · ·                                        |                             |

| • ,                                        | _                           |

|                                            | 74                          |

| 9 9 7                                      |                             |

|                                            | 76                          |

|                                            |                             |

|                                            |                             |

|                                            |                             |

|                                            |                             |

| o o                                        |                             |

|                                            |                             |

| ·                                          |                             |

| 9                                          | 91                          |

|                                            |                             |

|                                            | 91                          |

| '                                          | •                           |

| · ·                                        | 92                          |

|                                            | -                           |

| ·                                          | 92                          |

| •                                          | _                           |

|                                            | 93                          |

| ·                                          | -                           |

| ·                                          | 93                          |

|                                            | -                           |

|                                            |                             |

|                                            | Figure 1. 208 SQFP—Top View |

## Table of Contents (continued)

| Figures                                                                        | Page  | Tables                                                      | Page  |

|--------------------------------------------------------------------------------|-------|-------------------------------------------------------------|-------|

| Figure 35. E1, CT Bus Master, Compatibility Clock Master, Clock Source = 2.048 |       | Table 16. CKS: Clocks, Secondary (Fallback) Selection, 0x04 |       |

| from Trunk                                                                     | 98    | Table 17. CK32: Clocks, Locals 3 and 2, 0x05                | 18    |

| Figure 36. T1, CT Bus Master, Compatibility                                    |       | Table 18. CK10: Clocks, Locals 1 and 0, 0x06                | 18    |

| Clock Master, Clock Source = 1.544                                             |       | Table 19. CKMD: Clocks, Main Divider; CKND                  | :     |

| from Trunk                                                                     | 99    | Clocks, NETREF Divider; CKRD: Cl                            | ocks, |

| Figure 37. E1, Slave to CT Bus, Clock Source                                   |       | Resource Divider, 0x07, 0x08, 0x09                          | 19    |

| Is Either a 16 MHz or a 4 MHz or a 2                                           | 2 MHz | Table 20. LBS: Local Stream Control, 0x0C .                 | 19    |

| and Frame, NETREF Source = 2.048                                               | 8 MHz | Table 21. CON: Connection Delay Type, 0x0E                  | 19    |

| from Trunk                                                                     | 100   | Table 22. HSL: H-Bus Stream Control, Low By                 | ∕te,  |

| Figure 38. T1, Slave to CT Bus, Clock Source                                   |       | 0x10                                                        | 19    |

| Is Either a 16 MHz or a 4 MHz or a 2                                           | 2 MHz | Table 23. HSH: H-Bus Stream Control, High B                 | yte,  |

| and Frame, NETREF Source = 1.544                                               | 4 MHz | 0x11                                                        | 19    |

| from Trunk                                                                     | 101   | Table 24. GPD, General-Purpose Direction Co                 | ntrol |

| Figure 39. Constant Delay Connections,                                         |       | Register, 0x17                                              | 19    |

| CON[1:0] = 0X                                                                  | 104   | Table 25. GPR: General-Purpose I/O Register                 |       |

| Figure 40. Minimum Delay Connections,                                          |       | 0x18                                                        |       |

| CON[1:0] = 0X                                                                  | 105   | Table 26. FRLA: Frame Group A, Start Addres                 | 3S    |

| Figure 41. Mixed Minimum/Constant Delay                                        |       | Low, 0x20                                                   |       |

| Connections, CON[1:0 = 10]                                                     | 106   | Table 27. FRHA: Frame Group A, High Addres                  |       |

| Figure 42. Extended Linear (Mixed Minimum/Co                                   |       | Control, 0x21                                               |       |

| Delay, CON[1:0] = 11                                                           |       | Table 28. FRLB: Frame Group B, Start Addres                 |       |

|                                                                                |       | Low, 0x22                                                   |       |

|                                                                                |       | Table 29. FRHB: Frame Group B, High Addres                  |       |

| Tables                                                                         | Page  | and Control, 0x23                                           |       |

|                                                                                |       | Table 30. FRPL: Frame Group B, Programme                    |       |

| Table 1. Pin Descriptions: Clocking and Framing                                |       | Output, Low, 0x24                                           |       |

| Pins                                                                           |       | Table 31. FRPH: Frame Group B, Programme                    |       |

| Table 2. Pin Descriptions: Local Streams Pins                                  |       | Output, High, 0x25                                          |       |

| Table 3. Pin Descriptions: H-Bus Pins                                          |       | Table 32. CLKERR1: Clock Error Register, Err                |       |

| Table 4. Pin Descriptions: Microprocessor Interfa                              |       | Indicator, 0x28                                             |       |

| Pins                                                                           |       | Table 33. CLKERR2: Clock Error Register, Cu                 |       |

| Table 5. Pin Descriptions: JTAG Pins                                           |       | Status, 0x29                                                |       |

| Table 6. Pin Descriptions: Power Pins                                          |       | Table 34. SYSERR: System Error Register,                    |       |

| Table 7. Pin Descriptions: Other Pins                                          |       | 0x2A                                                        | 21    |

| Table 8. Addresses of Programming Registers                                    |       | Table 35. CKW: Clock Error/Watchdog Maskir                  |       |

| Table 9. Master Control and Status Register                                    |       | Register, 0x2B                                              |       |

| Table 10. Address Mode Register                                                |       | Table 36. CLKERR3: Clock Error Register, Cur                |       |

| Table 11. Control Register Memory Space                                        | 17    | Status, 0x2C                                                |       |

| Table 12. CKM: Clocks, Main Clock Selection,                                   |       | Table 37. DIAG1: Diagnostics Register 1, 0x30               |       |

| 0x00                                                                           | 18    | Table 38. DIAG2: Diagnostics Register 2, 0x3                |       |

| Table 13. CKN: Clocks, NETREF Selections,                                      |       | Table 39. DIAG3: Diagnostics Register 3, 0x32               |       |

| 0x01                                                                           |       | Table 40. DEV_ID: Device Identification Regis               |       |

| Table 14. CKP: Clocks, Programmable Outputs,                                   |       | 0xFE                                                        |       |

| 0x02                                                                           | 18    | Table 41. GMODE: Global Mode Register, 0x                   |       |

| Table 15. CKR: Clocks, Resource Selection,                                     |       | Table 42. LBS: Local Stream Control, 0x0C .                 |       |

| 0v03                                                                           | 10    | rabio 72. LDO. Local Officialli Control, 0x00 .             | 20    |

## Table of Contents (continued)

| Tables      |                                             | Page | Tables                                                                                     | Page |

|-------------|---------------------------------------------|------|--------------------------------------------------------------------------------------------|------|

| Table 43.   | HSL: H-Bus Stream Control, Low Byte         |      | Table 63. DIAG1: Diagnostics Register 1, 0x30                                              |      |

| Table 44    | 0x10Control High Buts                       |      | Table 64. DIAG2: Diagnostics Register 2, 0x31                                              |      |

| Table 44.   | HSL: H-Bus Stream Control, High Byte 0x11   |      | Table 65. DIAG3: Diagnostics Register 3, 0x32                                              |      |

| Table 45    | Permitted Tag Extensions                    |      | Table 66. Device Identification Register, 0xFE Table 67. GMODE: Global Mode Register, 0xFF |      |

|             | CKM: Clocks, Main Clock Selection,          | 40   | Table 68. LPUE Control Pins                                                                |      |

| Table 40.   | 0x00                                        | 40   | Table 69. Time-Slot Bit Decoding                                                           |      |

| Table 47    | CKN: Clocks, NETREF Selections,             | 49   | Table 70. IDR: Indirect Data Register, Local                                               | 7 3  |

| Table 47.   | 0x01                                        | 50   | Connections Only                                                                           | 7/   |

| Tahla 18    | CKP: Clocks, Programmable Outputs,          | 50   | Table 71. IDR: Indirect Data Register, H-Bus                                               | 7 4  |

| i abie 40.  | 0x02                                        | 51   | Connections Only                                                                           | 75   |

| Tahla 10    | CKR: Clocks, Resource Selection,            | 5 1  | Table 72. Crystal Specifications                                                           |      |

| Table 45.   | 0x03                                        | 52   | Table 73. Use of an Oscillator as an Alternative                                           |      |

| Table 50    | CKS: Clocks, Secondary (Fallback)           | 52   | Using a Crystal                                                                            |      |

| Table 50.   | Selection, 0x04                             | 53   | Table 74. Electrical Drive Specifications—CT_C8                                            |      |

| Table 51    | CK32 and CK10: Clocks, Locals 3, 2, 1       |      | and /CT_FRAME                                                                              |      |

| Table 01.   | and 0, 0x05 and 0x06                        |      | Table 75. dc Electrical Characteristics, All                                               |      |

| Table 52    | CON Register 0x0E                           |      | Other Pins                                                                                 | 84   |

|             | LREF Pairs                                  |      | Table 76. ac Electrical Characteristics, Timing,                                           |      |

|             | CKM (0x00) CKSEL Values to Select           |      | H-Bus (H.100 Spec., Rev. 1.0)                                                              | 87   |

| 1 4510 0 11 | LREF Pairs                                  | 57   | Table 77. ac Electrical Characteristics, Skew                                              |      |

| Table 55.   | FRHA, Frame Group A High Address            |      | Timing, H-Bus (H.100 Spec., Rev. 1.0)                                                      | 88   |

|             | and Control, 0x21                           | 59   | Table 78. Reset and Power On                                                               |      |

| Table 56.   | FRHB, Frame Group B High Address            |      | Table 79. ac Electrical Characteristics, Local                                             |      |

|             | and Control, 0x23                           | 59   | Streams, and Frames                                                                        | 89   |

| Table 57.   | FRPH: Frame Group B, Programmed             |      | Table 80. L_SC[3:0] and Frame Group Rise and                                               |      |

|             | Output, High, 0x25                          | 61   | Fall Time                                                                                  | 89   |

| Table 58.   | CLKERR1 and CLKERR2: Error Indicat          |      | Table 81. Microprocessor Access Timing                                                     |      |

|             | and Current Status, 0x28 and 0x29           |      | Table 82. Clock Register Programming Profile for                                           |      |

| Table 59.   | <b>CLKERR3: Error Indicator and Current</b> |      | the Four Previous Examples                                                                 |      |

|             | Status, 0x2C                                | 63   | Table 83. Table of Special Cases (Exceptions)                                              | 105  |

| Table 60.   | SYSERR: System Error Register,              |      | ,                                                                                          |      |

|             | 0x2A                                        | 63   |                                                                                            |      |

| Table 61.   | JTAG Instruction Set                        | 64   |                                                                                            |      |

| Table 62.   | JTAG Scan Register                          | 65   |                                                                                            |      |

#### 1.3 Pin Information

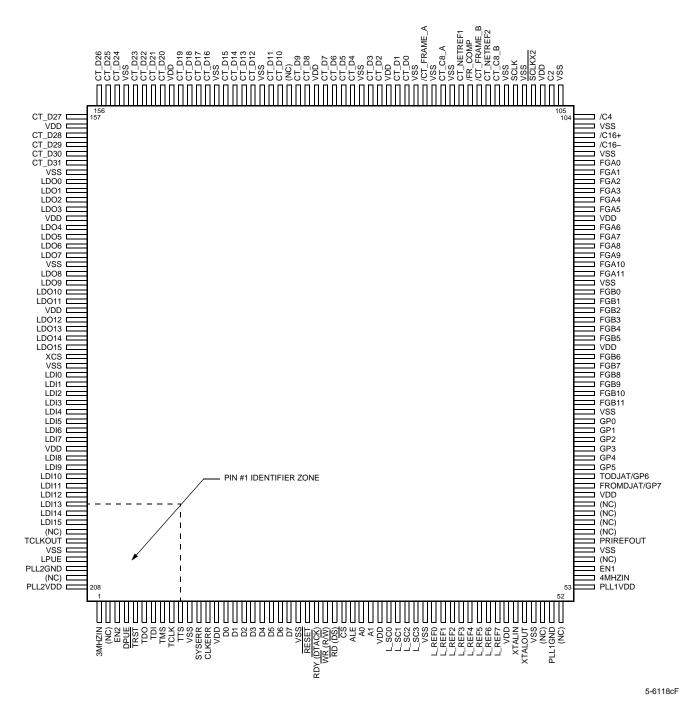

Figure 1. 208 SQFP—Top View

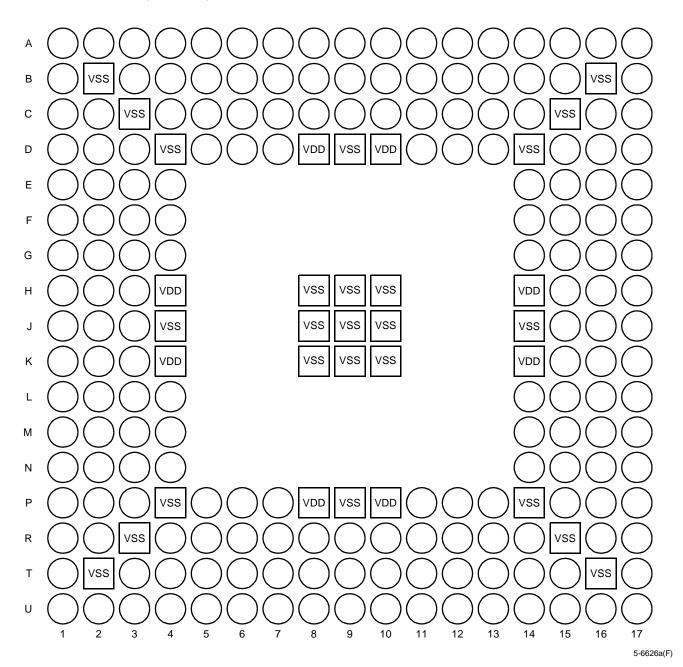

Figure 2. 217 PBGA—Top View

Table 1. Pin Descriptions: Clocking and Framing Pins

| Symbol              | Pin        | Ball                                                 | Туре | Name/Description                                                                                                                                 |  |

|---------------------|------------|------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L_REF[7:0]          | 45—38      | P3, N4, R1, P2, N3, M4,<br>P1, N2                    | I    | <b>Local Frame Reference Inputs.</b> 50 kΩ internal pull-up.                                                                                     |  |

| /C16+<br>/C16-      | 102<br>101 | R14<br>P13                                           | I/O  | <b>H-MVIP 16.384 MHz Clock Signals.</b> Differential 24 mA drive, Schmitt in, 50 k $\Omega$ internal pull-up.                                    |  |

| /C4                 | 104        | U16                                                  | I/O  | <b>MVIP 4.096 MHz Clock.</b> 8 mA drive, Schmitt in, 50 kΩ internal pull-up.                                                                     |  |

| C2                  | 106        | T17                                                  | I/O  | $\it MVIP$ 2.048 MHz Clock. 8 mA drive, Schmitt in, 50 kΩ internal pull-up.                                                                      |  |

| SCLK                | 110        | R17                                                  | I/O  | SC-Bus 2/4/8 MHz Clock. 24 mA drive, Schmitt in, 50 k $\Omega$ internal pull-up.                                                                 |  |

| SCLKX2              | 108        | P15                                                  | I/O  | SC-Bus Inverted 4/8 MHz Clock (Active-Low). 24 mA drive, Schmitt in, 50 k $\Omega$ internal pull-up.                                             |  |

| L_SC[3:0]           | 36—33      | M3, N1, M2, M1                                       | 0    | <b>Local Selected Clocks.</b> 1.024 MHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz, frame (8 kHz), or secondary (NETREF). 8 mA drive, 3-state. |  |

| FGA[5:0]            | 94—99      | R12, T13, U14, P12,<br>R13, T14                      | 0    | Frame Group A. 8 mA drive, 3-state.                                                                                                              |  |

| FGA[11:6]           | 87—92      | T11, P11, R11, U12,<br>T12, U13                      |      |                                                                                                                                                  |  |

| FGB[5:0]            | 80—85      | U9, R9, U10, T10, R10,<br>U11                        | 0    | Frame Group B. 8 mA drive, 3-state.                                                                                                              |  |

| FGB[11:6]           | 73—78      | U6, T7, R8, U7, T8, U8                               |      |                                                                                                                                                  |  |

| PRIREFOUT           | 58         | P5                                                   | 0    | Output from Primary Clock Selector/Divider. 8 mA drive.                                                                                          |  |

| PLL1V <sub>DD</sub> | 53         | U1                                                   | _    | PLL #1 VCO Power. This pin must be connected to power, even if PLL #1 is not used.                                                               |  |

| PLL1GND             | 51         | No ball for this<br>signal, internally<br>connected. |      | PLL #1 VCO Ground. This pin must be connected to ground, even if PLL #1 is not used.                                                             |  |

| EN1                 | 55         | Т3                                                   | _    | <b>PLL #1 Enable.</b> Requires cap to Vss to form power-on reset, or may be driven with RESET line. 50 kΩ internal pull-up.                      |  |

| 4MHZIN              | 54         | U2                                                   | I    | <b>PLL #1 Rate Multiplier.</b> Can be 2.048 MHz or 4.096 MHz. 50 k $\Omega$ internal pull-up.                                                    |  |

| PLL2VDD             | 208        | A2                                                   | ı    | PLL #2 VCO Power. This pin must be connected to power, even if PLL #2 is not used.                                                               |  |

| PLL2GND             | 206        | No ball for this signal, internally connected.       |      | PLL #2 VCO Ground. This pin must be connected to ground, even if PLL #2 is not used.                                                             |  |

| EN2                 | 3          | C2                                                   |      | PLL #2 Enable. Requires cap to Vss to form power-on reset, or may be driven with RESET line. 50 k $\Omega$ internal pull-up.                     |  |

| 3MHZIN              | 1          | A1                                                   | I    | PLL #2 Rate Multiplier. Input, 50 kΩ internal pull-up.                                                                                           |  |

| XTALIN              | 47         | R2                                                   | Ī    | 16.384 MHz Crystal Connection or External Clock Input.                                                                                           |  |

| XTALOUT             | 48         | T1                                                   | 0    | 16.384 MHz Crystal, Feedback Connection.                                                                                                         |  |

| TCLKOUT             | 203        | C4                                                   | 0    | Selected output to drive framers. 8 mA drive, 3-state.                                                                                           |  |

| CLKERR              | 13         | E1                                                   | 0    | Clock Error. Logical OR of CLKERR register flags (only). 8 mA drive, 3-state.                                                                    |  |

| SYSERR              | 12         | F3                                                   | 0    | <b>System Error.</b> Logical OR of all CLKERR and SYSERR register flags. 8 mA drive, 3-state.                                                    |  |

**Table 2. Pin Descriptions: Local Streams Pins**

| Symbol     | Pin     | Ball                           | Туре | Name/Description                       |

|------------|---------|--------------------------------|------|----------------------------------------|

| LDI[15:8]  | 201—194 | A3, B4, C5, D6, A4, B5, C6, A5 | I    | Local Data Input Streams. 50 kΩ inter- |

| LDI[7:0]   | 192—185 | B6, A6, C7, D7, B7, A7, C8, B8 |      | nal pull-up.                           |

| LDO[15:12] | 182—179 | C9, A9, B9, A10                | 0    | Local Data Output Streams. 8 mA        |

| LDO[11:8]  | 177—174 | B10, A11, C10, B11             |      | drive, 3-state.                        |

| LDO[7:4]   | 172—169 | D11, C11, B12, A13             |      |                                        |

| LDO[3:0]   | 167—164 | B13, A14, C13, D12             |      |                                        |

Table 3. Pin Descriptions: H-Bus Pins

| Symbol      | Pin     | Ball               | Туре | Name/Description                                    |

|-------------|---------|--------------------|------|-----------------------------------------------------|

| CT_D[31:28] | 162—159 | A15, D13, C14, B15 | I/O  | H-Bus, Data Lines. Variable rate 2 Mbits/s,         |

| CT_D[27:24] | 157—154 | A17, C16, D15, E14 |      | 4 Mbits/s, 8 Mbits/s. 5 V tolerant, PCI compliant,  |

| CT_D[23:20] | 152—149 | C17, D16, E15, F14 |      | 50 k $\Omega$ internal pull-up.                     |

| CT_D[19:16] | 147—144 | D17, E16, F15, E17 |      |                                                     |

| CT_D[15:12] | 142—139 | F16, F17, G15, G14 |      |                                                     |

| CT_D[11:10] | 137—136 | G16, G17           |      |                                                     |

| CT_D[9:8]   | 134—133 | H15, H16           |      |                                                     |

| CT_D[7:4]   | 131—128 | H17, J15, J17, J16 |      |                                                     |

| CT_D[3:2]   | 126—125 | K17, K16           |      |                                                     |

| CT_D[1:0]   | 123—122 | L17, K15           |      |                                                     |

| /CT_FRAME_A | 120     | L14                | I/O  | H-Bus, 8 kHz, Frame. 5 V tolerant, PCI compliant,   |

|             |         |                    |      | 24 mA drive, Schmitt in. No pull-up.                |

| /CT_FRAME_B | 114     | P17                | I/O  | H-Bus, Alternate 8 kHz Frame. 5 V tolerant, PCI     |

|             |         |                    |      | compliant, 24 mA drive. Schmitt in. No pull-up.     |

| /FR_COMP    | 115     | M15                | I/O  | H-Bus, Compatibility Frame Signal. 24 mA drive,     |

| _           |         |                    |      | Schmitt in, 50 kΩ internal pull-up.                 |

| CT NETREF1  | 116     | N17                | I/O  | H-Bus, Network Reference 1. 8 kHz, 2.048 MHz,       |

|             |         |                    |      | or 1.544 MHz. PCI driver. Not internally pulled up. |

| CT_NETREF2  | 113     | N15                | I/O  | H-Bus, Network Reference 2. 8 kHz, 2.048 MHz,       |

| _           |         |                    |      | or 1.544 MHz. PCI driver. Not internally pulled up. |

| CT_C8_A     | 118     | M16                | I/O  | H-Bus, Main Clock. 5 V tolerant, PCI compliant,     |

|             |         |                    |      | 24 mA drive, Schmitt in. No pull-up.                |

| CT C8 B     | 112     | M14                | I/O  | H-Bus, Alternate Main Clock. 5 V tolerant, PCI      |

|             |         |                    |      | compliant, 24 mA drive, Schmitt in. No pull-up.     |

| LPUE        | 205     | В3                 | ı    | Local Pull-Up Enable. A low disables all pull-ups   |

|             |         |                    |      | other than the CT_Dxx lines and the legacy clocks   |

|             |         |                    |      | C2, /C4, /C16+, /C16-, SCLK, SCLKX2, and            |

|             |         |                    |      | /FR_COMP. 50 kΩ internal pull-up. See Section       |

|             |         |                    |      | 3.3.5 Physical Connections for H.110.               |

| DPUE        | 4       | D3                 | I    | Data Pull-Up Enable. High enables pull-ups on       |

|             |         |                    |      | CT_Dxx only for H.100, low disables for H.110.      |

|             |         |                    |      | 50 kΩ internal pull-up.                             |

**Table 4. Pin Descriptions: Microprocessor Interface Pins**

| Symbol      | Pin   | Ball       | Туре | Name/Description                                                                         |

|-------------|-------|------------|------|------------------------------------------------------------------------------------------|

| RESET       | 24    | J1         | I    | Master Reset (Active-Low). See Section 3.1 Resets. 50 kΩ internal pull-                  |

|             |       |            |      | up.                                                                                      |

| A[1:0]      | 31—30 | L4,        | I    | <b>Microprocessor Interface, Address Lines.</b> Internal 20 k $\Omega$ pull-down.        |

|             |       | L2         |      |                                                                                          |

| D[7:0]      | 22—15 | ,          | I/O  | <b>Microprocessor Interface, Data Lines.</b> 8 mA drive, 50 k $\Omega$ internal pull-up. |

|             |       | H2,        |      |                                                                                          |

|             |       | G1,        |      |                                                                                          |

|             |       | H3,        |      |                                                                                          |

|             |       | G2,<br>F1, |      |                                                                                          |

|             |       | Г1,<br>G4, |      |                                                                                          |

|             |       | G3         |      |                                                                                          |

| ALE         | 29    | L1         | I    | Address Latch Enable. Internal 20 kΩ pull-down.                                          |

| CS          | 28    | K3         | I    | Chip Select (Active-Low). 50 kΩ internal pull-up.                                        |

| RD (DS)     | 27    | K2         | I    | Read Strobe (Intel Mode [Active-Low]), Data Strobe (Motorola [Active-                    |

| , ,         |       |            |      | <b>Low]).</b> 50 k $\Omega$ internal pull-up.                                            |

| WR (R/W)    | 26    | K1         | I    | Write Strobe (Intel [Active-Low]), Read/Write Select (Motorola [Active-                  |

| , ,         |       |            |      | <b>Low]).</b> 50 k $\Omega$ internal pull-up.                                            |

| RDY (DTACK) | 25    | J3         | 0    | Data Ready (Intel), Data Transfer (Motorola [Active-Low]).                               |

|             |       |            |      | 8 mA, open drain (user should add pull-up to this line).                                 |

**Table 5. Pin Descriptions: JTAG Pins**

| Symbol | Pin | Ball | Туре | Name/Description                                 |  |  |

|--------|-----|------|------|--------------------------------------------------|--|--|

| TCLK   | 9   | E3   | I    | JTAG Clock Input.                                |  |  |

| TMS    | 8   | F4   | I    | I JTAG Mode Select. 50 kΩ internal pull-up.      |  |  |

| TDI    | 7   | D2   | I    | I JTAG Data Input. 50 kΩ internal pull-up.       |  |  |

| TDO    | 6   | C1   | 0    | JTAG Data Output. 8 mA drive, 3-state.           |  |  |

| TRST   | 5   | E4   | I    | JTAG Reset (Active-Low). 50 kΩ internal pull-up. |  |  |

**Table 6. Pin Descriptions: Power Pins**

| Symbol | Pin                 | Ball                 | Туре | Name/Description                                    |

|--------|---------------------|----------------------|------|-----------------------------------------------------|

| Vss    | 11, 23, 37, 49, 57, | B2, B16, C3, C15,    | _    | Chip Ground.                                        |

|        | 72, 86, 100, 103,   | D4, D9, D14, H8,     |      |                                                     |

|        | 105, 109, 111, 117, | H9, H10, J4, J8, J9, |      |                                                     |

|        | 119, 121, 127, 138, | J10, J14, K8, K9,    |      |                                                     |

|        | 143, 153, 163, 173, | K10, L15, N14, P4,   |      |                                                     |

|        | 184, 204            | P9, P14, P16, R3,    |      |                                                     |

|        |                     | R15, T2, T15, T16,   |      |                                                     |

|        |                     | U15, U17             |      |                                                     |

| Vdd    | 14, 32, 46, 63, 79, | A16, D8, D10, F2,    | _    | 3.3 V Supply Voltage. Decouple every VDD pin        |

|        | 93, 107, 124, 132,  | H4, H14, K4, K14,    |      | with a 0.1 μF ceramic capacitor to Vss. 1000 pF or  |

|        | 148, 158, 168, 178, | L16, P8, P10, T9     |      | 0.01 μF capacitors may be used in addition to the   |

|        | 193                 |                      |      | 0.1 μF capacitor to provide additional decoupling.  |

|        |                     |                      |      | Place the capacitor as close to the VDD pin as pos- |

|        |                     |                      |      | sible.                                              |

**Table 7. Pin Descriptions: Other Pins**

| Symbol       | Pin                                                   | Ball                                                                           | Туре | Name/Description                                                                                                                        |

|--------------|-------------------------------------------------------|--------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| GP[5:0]      | 66—71                                                 | T5, R6, U5, T6,<br>R7, P7                                                      | I/O  | General-Purpose Bidirectional Register. 8 mA drive, Schmitt in, 50 k $\Omega$ internal pull-up.                                         |

| TODJAT/GP6   | 65                                                    | U4                                                                             | I/O  | Output from Selector to Drive DJAT (for NETREF) or GP Register Bit 6. 8 mA drive, Schmitt in, 50 kΩ internal pull-up.                   |

| FROMDJAT/GP7 | 64                                                    | R5                                                                             | I/O  | Smoothed Input to NETREF Divider and Drivers or GP Register Bit 7. 8 mA drive, input, Schmitt in, $50 \text{ k}\Omega$ internal pullup. |

| XCS          | 183                                                   | A8                                                                             | 0    | <b>Serial Output from Connection Memory.</b> 8 mA drive, 3-state.                                                                       |

| TTS          | 10                                                    | D1                                                                             | I    | <b>Test Type Select.</b> 0 = JTAG, 1 = forced output test, internal pull-down.                                                          |

| (NC)         | 2, 50, 52,<br>56, 59, 60,<br>61, 62, 135,<br>202, 207 | A12, B1, B14, B17,<br>C12, D5, E2, J2,<br>L3, M17, N16, P6,<br>R4, R16, T4, U3 | _    | Reserved, No Connection.                                                                                                                |

#### 1.4 Ambassador TSI Architecture

The *Ambassador* programmable TSIs have been designed to meet today's switching requirements. The T8100A and T8105 TSIs have a hierarchical switching capability. They can switch between the local input bus and the local output bus. They also switch between the H.100/H.110 bus and local bus. The T8102 TSI switches between the H.100/H.110 bus and the local bus.

All three TSIs have circuitry for subrate switching and can interface to other computer telephony standards such as MVIP, SC-Bus, and MC-1\*.

## 1.5 Selecting Between T8105, T8102, T8100A, and T8100

| Features                   | T8100 | T8100A | T8102 | T8105 |

|----------------------------|-------|--------|-------|-------|

| Subrate switching          | _     | V      | V     | √     |

| Local-to-local connections | 1,024 | 1,024  | _     | 1,024 |

| Local-to-H.100 connections | 256   | 256    | 512   | 512   |

| CT_NETREFs                 | 1     | 2      | 2     | 2     |

#### 1.6 Enhanced Local Stream Addressing

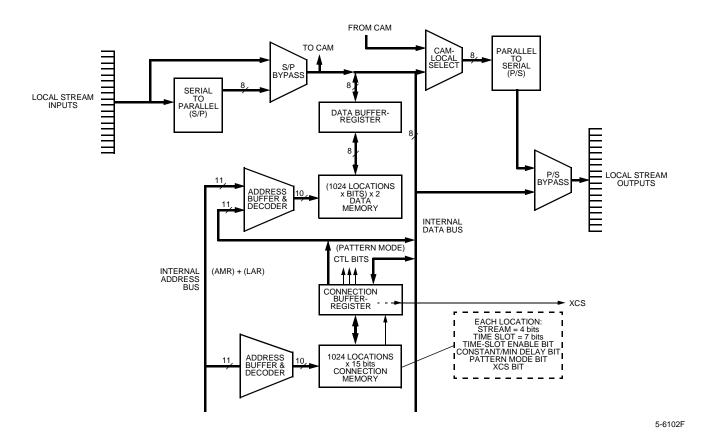

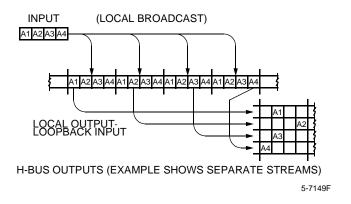

Local stream addressing has 1024 locations. Separate connection and data memories (T8100A, T8105 only) maintain all necessary information for local stream interconnections. The streams may operate at maximum rate on eight physical inputs and eight physical outputs. Choices for slower input or output rates allow enabling of additional physical inputs or outputs for a maximum of 16 pins each. Data rates are 2.048 Mbits/s, 4.096 Mbits/s, or 8.192 Mbits/s.

In addition to the enhanced serial streaming, the local memories may be used for 8-line-serial-in/1-byte-parallel-out, 1-byte-parallel-in/8-line-serial-out, or 1-byte-parallel-in/1-byte-parallel-out options. All three data rates are supported in the parallel modes. The addresses for the local memories (T8100A, T8105 only) have been simplified so that stream and time-slot designations are automatically translated to the appropriate memory address, regardless of rate or serial/parallel modes.

## \* MC-1 is a multichassis communication standard based on MVIP. The devices support this standard.

#### 1.7 Full H.100 Stream Address Support

The devices provide access to the full 4096 H.100 bus slots (32 streams x 128 slots) or any standard subset (H-MVIP has a maximum 24 streams x 128 time slots, for example). The number of stored time-slot addresses is limited to 512 (T8102, T8105 only) at any one time, but these may be updated on the fly. In addition, accesses to and from the H.100 bus can be directed through the 1024 local stream/time slots, giving a total space of 5120 time slots. Data rates are programmable on each of the 32 physical streams, selected in groups of four. The rates are 2.048 Mbits/s, 4.096 Mbits/s, or 8.192 Mbits/s.

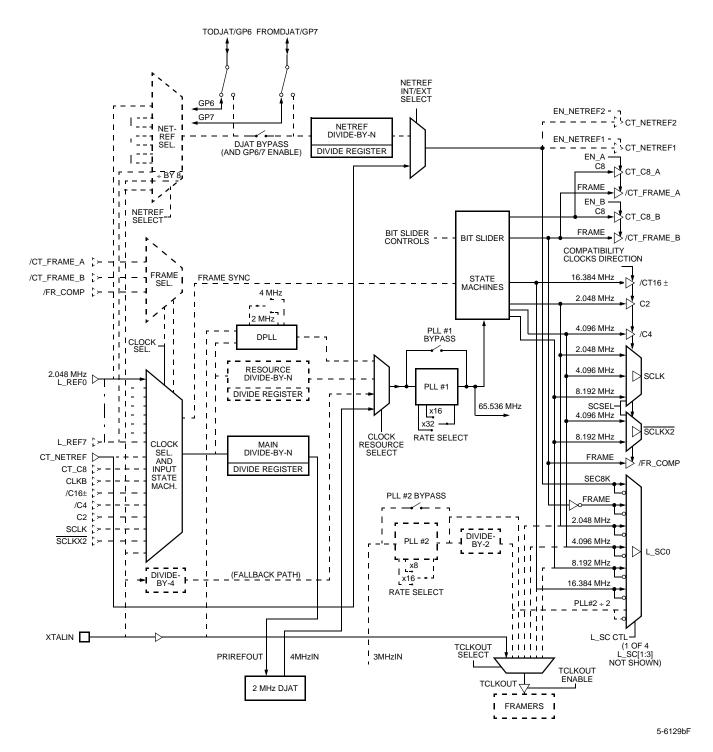

#### 1.8 Onboard PLLs and Clock Monitors

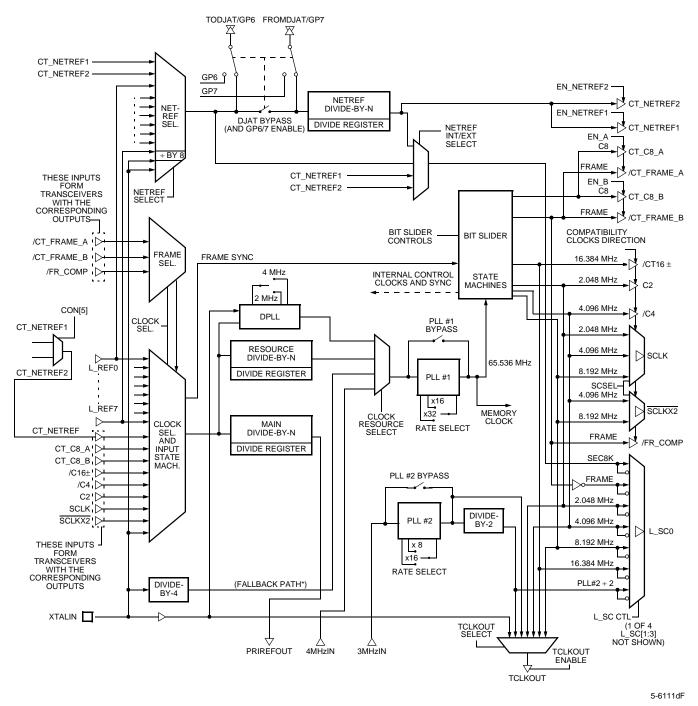

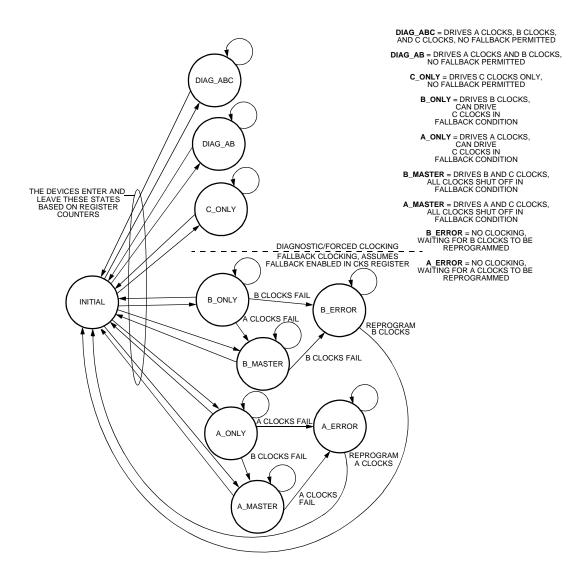

The devices use rate multipliers and state machines to generate onboard frequencies for supporting the H.100, H-MVIP, MVIP, MC-1, and SC-Buses. Pins are provided for coupling the internal clock circuitry with commonly available clock adapters and jitter attenuators. If external resources are not available, an internal digital phase-locked loop (DPLL) can be used to generate all the bus frequencies and remain synchronized to an 8 kHz reference. One of several clock input reference sources may be selected, and separate inputactive detection logic can identify the loss of the individual input references. The entire clocking structure operates from a 16.384 MHz crystal or external input.

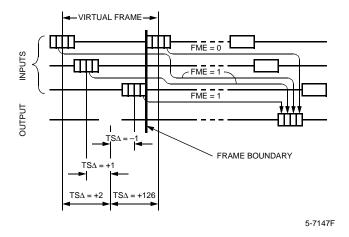

## 1.9 Phase Alignment of Referenced and Generated Frames

If this resource is selected, special control logic will create bit-sliding in the data streams when the reference frame and generated frame are out of phase. The bit-sliding refers to removing a fraction of a bit time per frame until the frames are in phase.

#### 1.10 Interfaces

#### 1.10.1 Microprocessors

The devices provide the user a choice of either *Motor-ola* or *Intel* interfacing through an 8-bit data bus, a 2-bit address bus, and multifunction control pins. All access to the devices' memory blocks and registers use indirect addressing.

#### 1.10.2 Framing Groups

Two groups of programmable framing signals are available. Each group is composed of 12 sequenced lines operating in one of four modes. The devices support 1-bit, 2-bit, 1-byte, and 2-byte pulse widths. Starting position of the pulse sequences are also programmable.

#### 1.10.3 General-Purpose Register and I/O

A general-purpose, 8-bit, input/output port is provided as either byte-wide I/O or bit addressed I/O.

#### 1.11 Applications

- Computer-telephony systems

- Enhanced service platforms

- WAN access devices

- PBXs

- Wireless base stations

#### 1.12 Application Overview

The integration of computers and telecommunications has enabled a wide range of new communications applications and has fueled an enormous growth in communications markets. A key element in the development of computer-based communications equipment has been the addition of an auxiliary telecom bus to existing computer systems. Most manufacturers of high-capacity, computer-based telecommunications equipment have incorporated some such telecom bus in their systems. Typically, these buses and bus interfaces are designed to transport and switch N x 64 kbits/s low-latency telecom traffic between boards within the computer, independent of the computer's I/O and memory buses. At least a half dozen of these PC-based telecom buses emerged in the early 1990s for use within equipment based on ISA/EISA and MCA computers.

With the advent of the H.100 bus specification by the Enterprise Computer Telephony Forum, the computer-telephony industry has agreed on a single telecom bus for use with PCI and compact PCI computers. H.100 facilitates interoperation of components, thus providing maximum flexibility to equipment manufacturers, value-added resellers, system integrators, and others building computer-based telecommunications applications.

## 2 Architecture and Functional Description

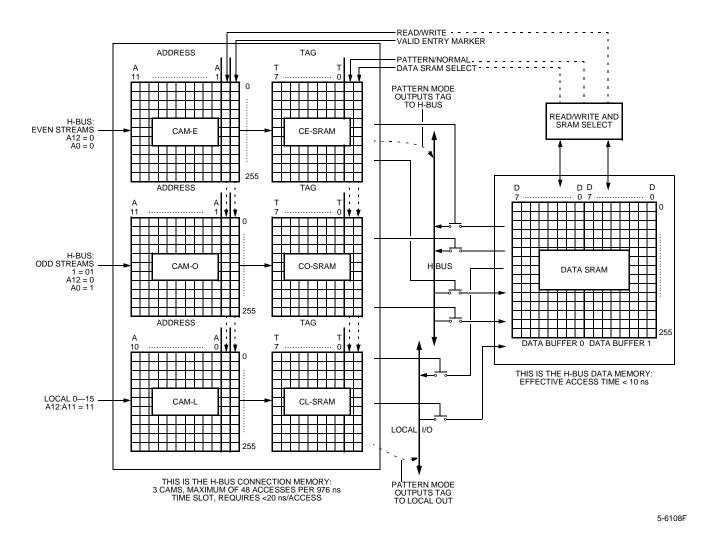

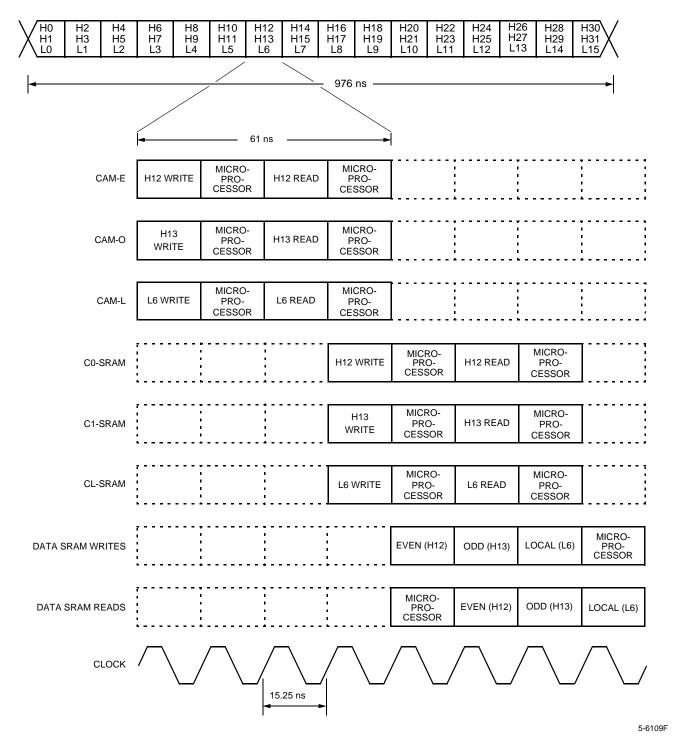

The devices are H.100-compliant and provide a complete interface between the H.100 bus and a wide variety of telephony interface components, processors, and other circuits. The bus interface provides all signals needed for the H.100 bus, the H-MVIP and MVIP-90 buses, or the SC-Bus. Local interfaces include 16 serial inputs and 16 serial outputs based on the Lucent Technologies Microelectronics Group concentration highway interface (CHI). The T8100A and the T8105 include two built-in time-slot interchangers. The first provides a local switching domain with up to 1024 programmable connections between time slots on the local CHI inputs and outputs. The second provides programmable connections between any time slot on the H.100 bus and any time slot in the local switching domain. The T8105 has 512 programmable connections while the T8100A has 256. The T8102 has only 1 TSI for switching up to 512 programmable connections on the H.100 bus and any time slot in the local switching domain. All Ambassador devices are configured via a microprocessor interface. This interface can also read and write time slot and device data. Onboard clock circuitry, including a DPLL, supports all H.100 clock modes including MVIP and SC-Bus compatibility clocks. The local CHI interfaces support PCM rates of 2.048 Mbits/s, 4.096 Mbits/s, and 8.192 Mbits/s. Each device has internal circuitry to support either minimum latency or multi-time-slot frame integrity. Frame integrity is a requisite feature for applications that switch wideband data (ISDN H-channels). Minimum latency is advantageous in voice applications.

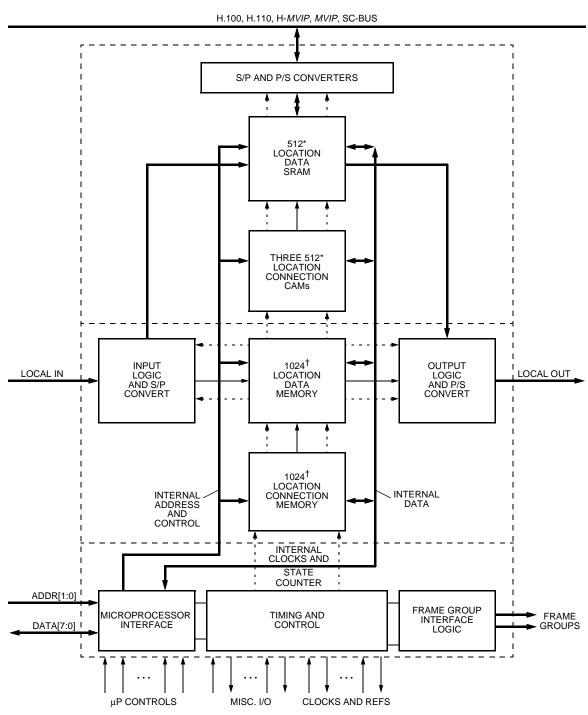

All three TSIs have the following four major sections:

- Local bus—refers to the local streams.

- H-bus—refers to the H.100/H.110/H-*MVIP* and legacy streams.

- Interface—refers to the microprocessor interface, frame groups, and general-purpose I/O (GPIO).

- Timing—the rate multipliers, DPLL, and clocking functions.

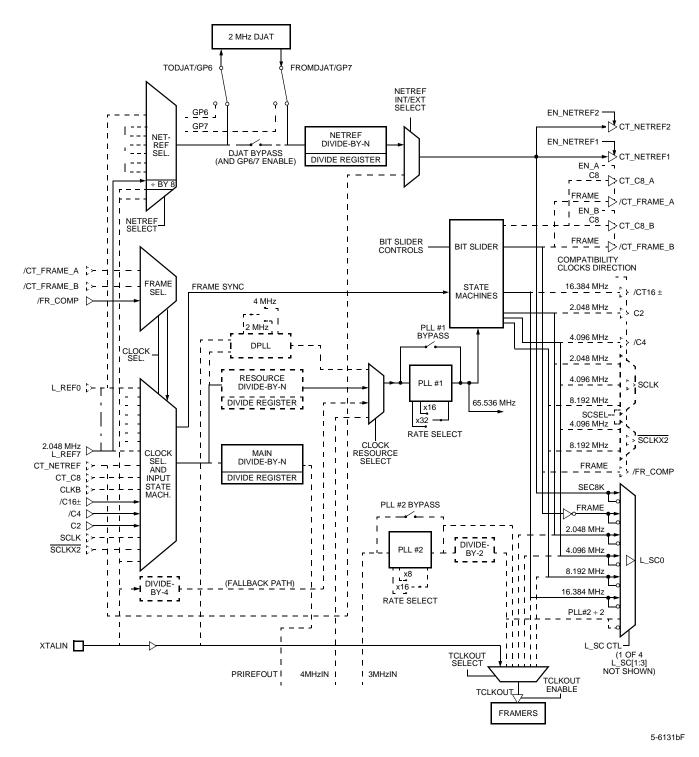

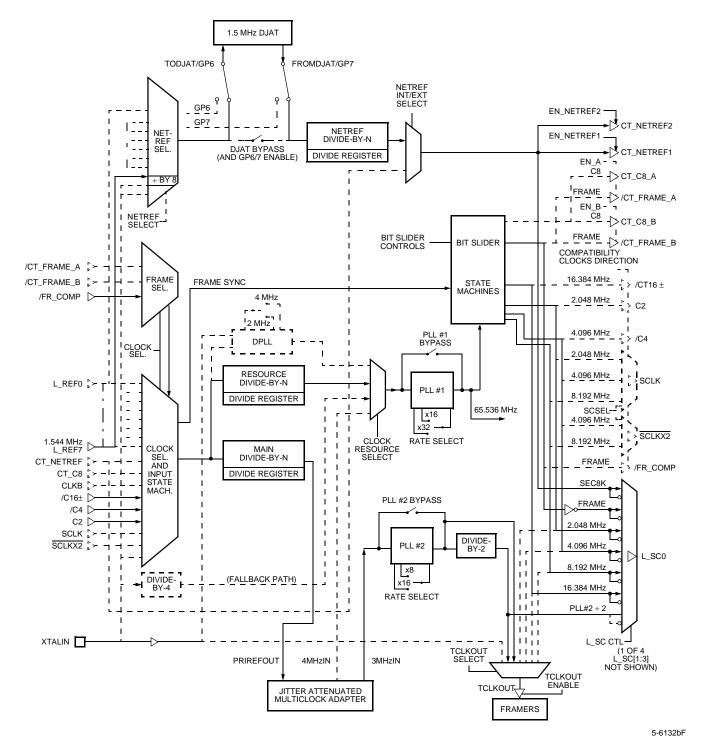

Figure 3 shows a block diagram of the TSI devices. The devices operate on a 3.3 V supply for both the core and I/Os, though the I/Os are TTL compatible and 5 V tolerant.

<sup>\*</sup> For T8100 and T8100A, there are only 256 locations.

Figure 3. Block Diagram of the TSI Devices

<sup>†</sup> T8102 does not have local data memory.

#### 2.1 Register/Memory Maps

In this section, a general overview of the registers and the indirect mapping to different memory spaces is described. More detailed descriptions for using the registers in software can be found in Section 3.4 Using the LAR, AMR, and IDR for Connections.

(Throughout this document, all registers are defined with the MSB on the left and the LSB on the right.)

#### 2.1.1 Main Registers

The address bits are used to map a large memory space.

All registers default to 0 at powerup.

**Table 8. Addresses of Programming Registers**

| A1 | A0 | Symbol | Name/Description                                                           |

|----|----|--------|----------------------------------------------------------------------------|

| 0  | 0  | MCR    | Master Control and Status Register (read/write)                            |

| 0  | 1  | LAR    | Lower Address Register—Lower Indirect Address (time slot) (write only)     |

| 1  | 0  | AMR    | Address Mode Register—Upper Address (stream) and Address Type (write only) |

| 1  | 1  | IDR    | Indirect Data Register (read/write)                                        |

#### 2.1.2 Master Control and Status Register

**Table 9. Master Control and Status Register**

| Symbol | Bit | Name/Description                                                                                                                                                                                                                                                                                                                                                                |

|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MR     | 7   | Master (Software) Reset. A high reinitializes the registers.                                                                                                                                                                                                                                                                                                                    |

| CER    | 6   | Clock Error Reset. A high resets the error bits of the CLKERR registers.                                                                                                                                                                                                                                                                                                        |

| SER    | 5   | <b>System Error Reset</b> . A high resets the error bits of the SYSERR register. (Note that MR, CER, and SER are automatically cleared after the requested reset is complete.)                                                                                                                                                                                                  |

| AP     | 4   | Active Page. This bit identifies which of the double-buffered data memories are active. A zero indicates buffer 0; a one indicates buffer 1. The AP identifies which data buffer is being accessed during a write operation (i.e., input from local streams or input from H-bus).                                                                                               |

| HBE    | 3   | <b>H-Bus Enable</b> . On powerup or software reset, all H-bus pins (including clocks) are disabled. HBE must be set high to reenable the 3-stated buffers.                                                                                                                                                                                                                      |

| LBE    | 2   | Local Bus Enable. Same function as HBE for local data outputs.                                                                                                                                                                                                                                                                                                                  |

| LCE    | 1   | <b>Local Clock Enable</b> . Enables all other local functions: clocks, frame groups, etc. (Note that the TCLKOUT is disabled during a Master Reset and is unaffected by HBE, LBE, or LCE, though there are control bits for this signal in the CKP register. See Section 2.5.8 Clock Control Register Definitions for a description of the CKP register.) 3-stated if disabled. |

| СВ     | 0   | <b>CAM Busy</b> . A status bit indicating microprocessor activity in any of the CAM blocks. A high means that one (or more) of the CAMs is being accessed by the microprocessor. In most cases, this bit will read low since there are many internal operational cycles dedicated to the microprocessor, which allow it to finish quickly.                                      |

#### 2.1 Register/Memory Maps (continued)

#### 2.1.3 Address Mode Register

The AMR is defined in Table 10 below where (aaaa) is the stream address and the LAR is the time-slot address of the selected memory space.

Note: All unused AMR values are reserved.

**Table 10. Address Mode Register**

| Bits<br>7—4  | Bits<br>3—0  | Register Function                                                                                                                                                                                       |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000         | 0000         | Control Registers.                                                                                                                                                                                      |

| 0001         | (aaaa)       | Local Bus, Data Memory 1.                                                                                                                                                                               |

| 0010         | (aaaa)       | Local Bus, Data Memory 2.                                                                                                                                                                               |

| 0100         | (aaaa)       | Local Bus, Connection Memory, Time-Slot Field.                                                                                                                                                          |

| 0101         | (aaaa)       | Local Bus, Connection Memory, Stream, and Control Bit Field.                                                                                                                                            |

| 0111         | 0000         | Local Bus, Holding Registers, Reset.                                                                                                                                                                    |

| 1001         | 0000         | CAM, Data Memory 1. Lower 256 Addresses.                                                                                                                                                                |

| 1001         | 0001         | CAM, Data Memory 1. Upper 256 Addresses (T8102, T8105 only).                                                                                                                                            |

| 1010         | 0000         | CAM, Data Memory 2. Lower 256 Addresses.                                                                                                                                                                |

| 1010         | 0001         | CAM, Data Memory 2. Upper 256 Addresses (T8102, T8105 only).                                                                                                                                            |

| 1011         | 0000         | CAM, Connection, Time-Slot Field.                                                                                                                                                                       |

| 1011         | 0001         | CAM, Connection, Stream, and Control Bit Field.                                                                                                                                                         |

| 1011         | 0010         | CAM, Connection, Tag Field.                                                                                                                                                                             |

| 1011         | 0011         | CAM, Connection, Subrate Control, Tag Field MSB.                                                                                                                                                        |

| 1110         | 0000         | CAM, Even, Make Connection (MKCE). Write to Next Free Location.                                                                                                                                         |

| 1110         | 0001         | CAM, Odd, Make Connection (MKCO). Write to Next Free Location.                                                                                                                                          |

| 1110         | 0011         | CAM, Local, Make Connection (MKCL). Write to Next Free Location.                                                                                                                                        |

| 1110         | 0100         | CAM, Even, Break Connection (BKCE).                                                                                                                                                                     |

| 1110         | 0101         | CAM, Odd, Break Connection (BKCO).                                                                                                                                                                      |

| 1110         | 0111         | CAM, Local, Break Connection (BKCL).                                                                                                                                                                    |

| 1110         | 1000         | CAM, Even, Clear Location (CLLE). Lower 256 Range. Requires LAR.                                                                                                                                        |

| 1100         | 1000         | CAM, Even, Clear Location (CLLE). <b>Upper</b> 256 Range. Requires LAR (T8102, T8105 only).                                                                                                             |

| 1110<br>1100 | 1001<br>1001 | CAM, Odd, Clear Location (CLLO). <b>Lower</b> 256 Range. Requires LAR. CAM, Odd, Clear Location (CLLO). <b>Upper</b> 256 Range. Requires LAR (T8102, T8105 only).                                       |

| 1110         | 1011         | CAM, Local, Clear Location (CLLL). Lower 256 Range. Requires LAR.                                                                                                                                       |

| 1100         | 1011         | CAM, Local, Clear Location (CLLL). <b>Upper</b> 256 Range. Requires LAR (T8102, T8105 only).                                                                                                            |

| 1110<br>1100 | 1100<br>1100 | CAM, Even, Read Location (RDCE). <b>Lower</b> 256 Range. Requires LAR, IDR Holds Results. CAM, Even, Read Location (RDCE). <b>Upper</b> 256 Range. Requires LAR, IDR Holds Results (T8102, T8105 only). |

| 1110         | 1101         | CAM, Odd, Read Location (RDCO). Lower 256 Range. Requires LAR, IDR Holds Results.                                                                                                                       |

| 1100         | 1101         | CAM, Odd, Read Location (RDCO). <b>Upper</b> 256 Range. Requires LAR, IDR Holds Results (T8102, T8105 only).                                                                                            |

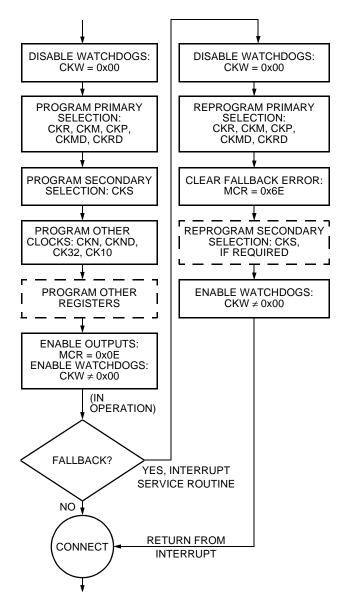

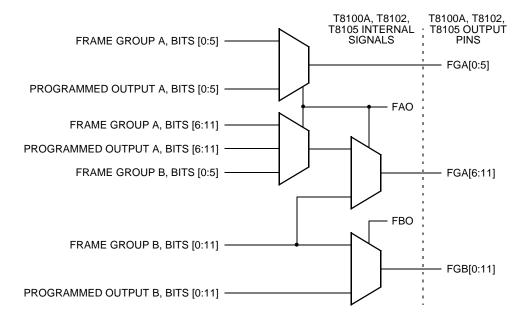

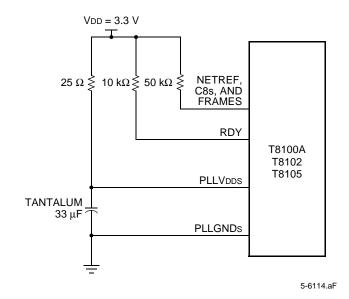

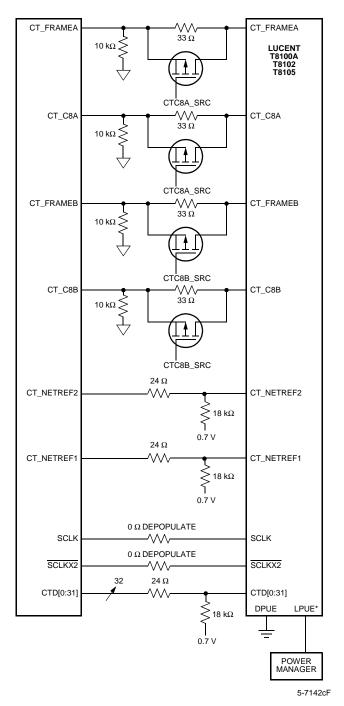

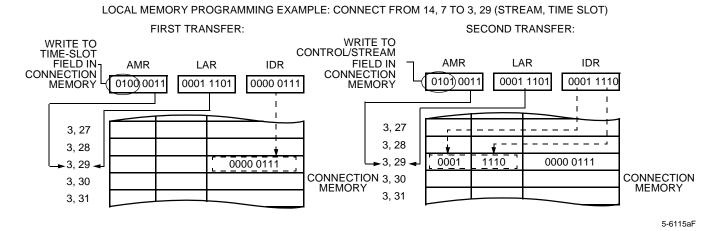

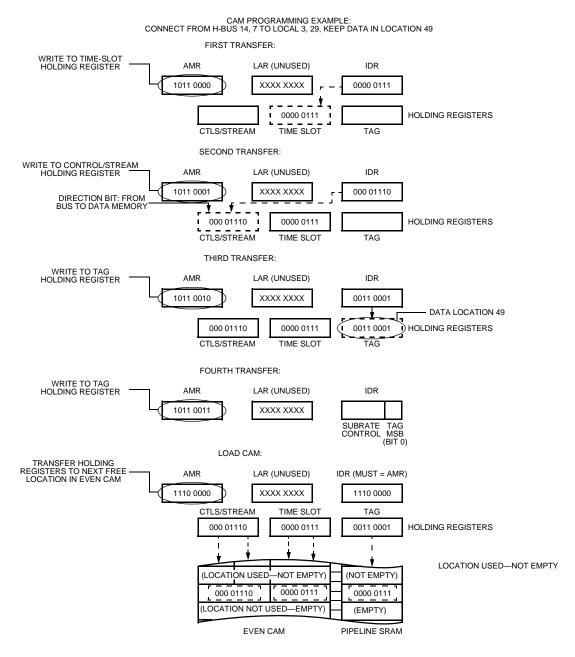

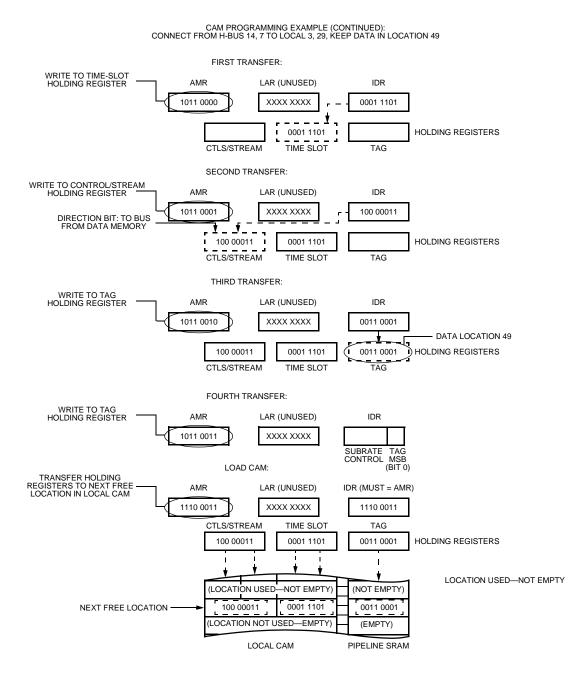

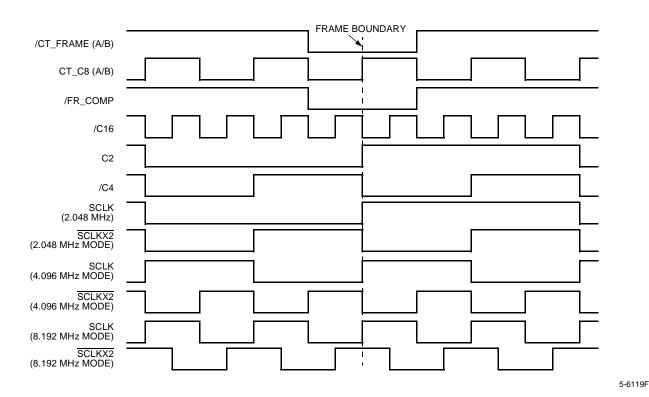

| 1110         | 1111         | CAM, Local, Read Location (RDCL). Lower 256 Range. Requires LAR, IDR Holds Results.                                                                                                                     |