## Extremely Efficient Class-D Stereo Operation

## Drives L and R Channels, Plus Stereo Headphones

- 10-W BTL Output Into 4  $\Omega$  From 12 V

- 32-W Peak Music Power

- Fully Specified for 12-V Operation

- Low Shutdown Current

- Class-AB Headphone Amplifier

- Thermally-Enhanced PowerPAD™ Surface-Mount Packaging

- Thermal and Under-Voltage Protection

## description

The TPA032D04 is a monolithic power IC stereo audio amplifier that operates in extremely efficient Class-D operation, using the high switching speed of power DMOS transistors to replicate the analog input signal through high-frequency switching of the output stage. This allows the TPA032D04 to be configured as a bridge-tied load (BTL) amplifier capable of delivering up to 10 W of continuous average power into a 4- $\Omega$  load at 0.5% THD+N from a 12-V power supply in the high-fidelity audio frequency range (20 Hz to 20 kHz). A BTL configuration eliminates the need for external

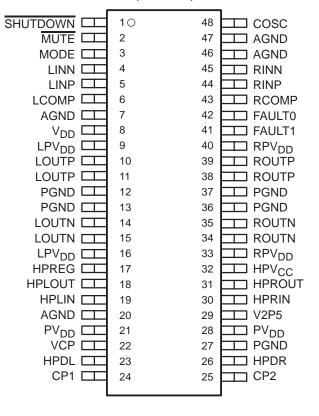

#### DCA PACKAGE (TOP VIEW)

coupling capacitors on the output. Included is a Class-AB headphone amplifier with interface logic to select between the two modes of operation. Only one amplifier is active at any given time, and the other is in power-saving sleep mode. Also, a chip-level shutdown control is provided to limit total supply current to  $20\,\mu\text{A}$ , making the device ideal for battery-powered applications.

The output stage is compatible with a range of power supplies from 8 V to 14 V. Protection circuitry is included to increase device reliability: thermal and under-voltage shutdown, with a status feedback terminal for use when any error condition is encountered.

The high switching frequency of the TPA032D04 allows the output filter to consist of three small capacitors and two small inductors per channel. The high switching frequency also allows for good THD+N performance.

The TPA032D04 is offered in the thermally enhanced 48-pin PowerPAD™ TSSOP surface-mount package (designator DCA).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

INSTRUMENTS

POST OFFICE BOX 656300. DALLAS, TEXAS 75265

lemplate

Release Date: 7-11-94

NOTE A: LPVDD, RPVDD, and PVDD are externally connected. AGND and PGND are externally connected.

## **Terminal Functions**

| TERMIN            | IAL              |                                                                                                                                                                                                                                                                                |

|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.              | DESCRIPTION                                                                                                                                                                                                                                                                    |

| AGND              | 7, 20,<br>46, 47 | Analog ground for headphone and Class-D analog sections                                                                                                                                                                                                                        |

| cosc              | 48               | Connect a capacitor from analog ground to this terminal to set the frequency of the ramp reference signal.                                                                                                                                                                     |

| CP1               | 24               | First diode node for charge pump                                                                                                                                                                                                                                               |

| CP2               | 25               | First inverter switching node for charge pump                                                                                                                                                                                                                                  |

| FAULT0            | 42               | Logic level fault0 output signal. Lower order bit of the two fault signals with open drain output.                                                                                                                                                                             |

| FAULT1            | 41               | Logic level fault1 output signal. Higher order bit of the two fault signals with open drain output.                                                                                                                                                                            |

| HPDL              | 23               | Depop control for left headphone                                                                                                                                                                                                                                               |

| HPDR              | 26               | Depop control for right headphone                                                                                                                                                                                                                                              |

| HPLIN             | 19               | Headphone amplifier left input                                                                                                                                                                                                                                                 |

| HPLOUT            | 18               | Headphone amplifier left output                                                                                                                                                                                                                                                |

| HPREG             | 17               | 5-V regulator output. This terminal requires a 1-μF capacitor to ground for stability reasons.                                                                                                                                                                                 |

| HPRIN             | 30               | Headphone amplifier right input                                                                                                                                                                                                                                                |

| HPROUT            | 31               | Headphone amplifier right output                                                                                                                                                                                                                                               |

| HPVCC             | 32               | 5V supply to headphone amplifier and logic. This terminal is typically connected to HPREG.                                                                                                                                                                                     |

| LCOMP             | 6                | Compensation capacitor terminal for left-channel Class-D amplifier                                                                                                                                                                                                             |

| LINN              | 4                | Class-D left-channel negative input                                                                                                                                                                                                                                            |

| LINP              | 5                | Class-D left-channel positive input                                                                                                                                                                                                                                            |

| LOUTN             | 14, 15           | Class-D amplifier left-channel negative output of H-bridge                                                                                                                                                                                                                     |

| LOUTP             | 10, 11           | Class-D amplifier left-channel positive output of H-bridge                                                                                                                                                                                                                     |

| LPV <sub>DD</sub> | 9, 16            | Class-D amplifier left-channel power supply                                                                                                                                                                                                                                    |

| MODE              | 3                | TTL logic-level mode input signal. When MODE is held low, the main Class-D amplifier is active. When MODE is held > high, the head phone amplifier is active.                                                                                                                  |

| MUTE              | 2                | Active-low TTL logic-level mute input signal. When MUTE is held low, the selected amplifier is muted. When MUTE is held > high, the device operates normally. When the Class-D amplifier is muted, the low-side output transistors are turned on, shorting the load to ground. |

| PGND              | 12, 13           | Power ground for left-channel H-bridge only                                                                                                                                                                                                                                    |

| PGND              | 27               | Power ground for charge pump only                                                                                                                                                                                                                                              |

| PGND              | 36, 37           | Power ground for right-channel H-bridge only                                                                                                                                                                                                                                   |

| $PV_{DD}$         | 21, 28           | V <sub>DD</sub> supply for charge-pump, headphone regulator, and gate drive circuitry                                                                                                                                                                                          |

| RCOMP             | 43               | Compensation capacitor terminal for right-channel Class-D amplifier                                                                                                                                                                                                            |

| RINN              | 45               | Class-D right-channel negative input                                                                                                                                                                                                                                           |

| RINP              | 44               | Class-D right-channel positive input                                                                                                                                                                                                                                           |

| RPV <sub>DD</sub> | 33, 40           | Class-D amplifier right-channel power supply                                                                                                                                                                                                                                   |

| ROUTN             | 34, 35           | Class-D amplifier right-channel negative output of H-bridge                                                                                                                                                                                                                    |

| ROUTP             | 38, 39           | Class-D amplifier right-channel positive output of H-bridge                                                                                                                                                                                                                    |

| SHUTDOWN          | 1                | Active-low TTL logic-level shutdown input signal. When SHUTDOWN is held low, the device goes into shutdown mode. When SHUTDOWN is held high, the device operates normally.                                                                                                     |

| V2P5              | 29               | 2.5V internal reference bypass. This terminal requires a capacitor to ground.                                                                                                                                                                                                  |

| VCP               | 22               | Connect a capacitor from this terminal to power ground to provide storage for the charge pump output voltage.                                                                                                                                                                  |

| V <sub>DD</sub>   | 8                | V <sub>DD</sub> bias supply for analog circuitry. This terminal needs to be well filtered to prevent degrading the device performance.                                                                                                                                         |

## **Class-D amplifier faults**

Table 1. Class-D Amplifier Fault Table

| FAULT 0 | FAULT 1 | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |

|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | 1       | No fault. The device is operating normally.                                                                                                                                                                                                                                                                                     |

| 0       | 1       | Charge pump under-voltage lock-out (VCP-UV) fault. All low-side transistors are turned on, shorting the load to ground. Once the charge pump voltage is restored, normal operation resumes, but FAULT1 is still active. This is not a latched fault, however. FAULT1 is cleared by cycling MUTE, SHUTDOWN, or the power supply. |

| 0       | 0       | Thermal fault. All the low-side transistors are turned on, shorting the load to ground. Once the junction temperature drops 20°C, normal operation resumes (not a latched fault). But the FAULTx terminals are still set and are cleared by cycling MUTE, SHUTDOWN, or the power supply.                                        |

## headphone amplifier faults

The thermal fault remains active when the device is in head phone mode. This fault operation has exactly the same as it does for the Class-D amplifier (see Table 1).

If  $HPV_{CC}$  drops below approximately 4.5 V, the head phone is disabled. Once  $HPV_{CC}$  exceeds approximately 4.5 V, the head phone amplifier is re-enabled. No fault is reported to the user.

#### **AVAILABLE OPTIONS**

|                | PACKAGED DEVICES |

|----------------|------------------|

| T <sub>A</sub> | TSSOP†<br>(DCA)  |

|                | (DOA)            |

| -40°C to 125°C | TPA032D04DCA     |

<sup>&</sup>lt;sup>†</sup>The DCA package is available in left-ended tape and reel. To order a taped and reeled part, add the suffix R to the part number (e.g., TPA032D04DCAR).

## absolute maximum ratings over operating free-air temperature range, $T_C = 25^{\circ}C$ (unless otherwise noted)<sup>†</sup>

| 14 V                         |

|------------------------------|

| 5.5 V                        |

|                              |

| 1 mA                         |

| 7 V                          |

| PV <sub>DD</sub> + 20 V      |

| 3.5 A                        |

| 7 A                          |

| 150 mA                       |

| See Dissipation Rating Table |

| 40°C to 150°C                |

| 40°C to 125°C                |

| 65°C to 260°C                |

| 260°C                        |

|                              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Pulse duration = 10 ms, duty cycle  $\leq$  2%

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C <sup>‡</sup> | DERATING FACTOR             | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|------------------------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING                       | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| DCA     | 5.6 W                              | 44.8 mW/°C                  | 3.6 W                 | 2.9 W                 |

<sup>&</sup>lt;sup>‡</sup> Please see the Texas Instruments document, *PowerPAD Thermally Enhanced Package Application Report* (literature number SLMA002), for more information on the PowerPAD™ package. The thermal data was measured on a PCB layout based on the information in the section entitled *Texas Instruments Recommended Board for PowerPAD* on page 33 of the before mentioned document.

## recommended operating conditions

|                                                                                            | MIN  | NOM | MAX                     | UNIT             |

|--------------------------------------------------------------------------------------------|------|-----|-------------------------|------------------|

| Supply voltage, V <sub>DD</sub> , PV <sub>DD</sub> , LPV <sub>DD</sub> , RPV <sub>DD</sub> | 8    |     | 14                      | V                |

| Headphone supply voltage, HPV <sub>CC</sub>                                                | 4.5  |     | 5.5                     | V                |

| High-level input voltage, VIH (MUTE, MODE, SHUTDOWN)                                       | 2    |     | V <sub>DD</sub> + 0.3 V | V                |

| Low-level input voltage, V <sub>IL</sub> (MUTE, MODE, SHUTDOWN)                            | -0.3 |     | 0.8                     | V                |

| Audio inputs, LINN, LINP, RINN, RINP, HPLIN, HPRIN, differential input voltage             |      |     | 1                       | V <sub>RMS</sub> |

| PWM frequency                                                                              | 100  | 250 | 500                     | kHZ              |

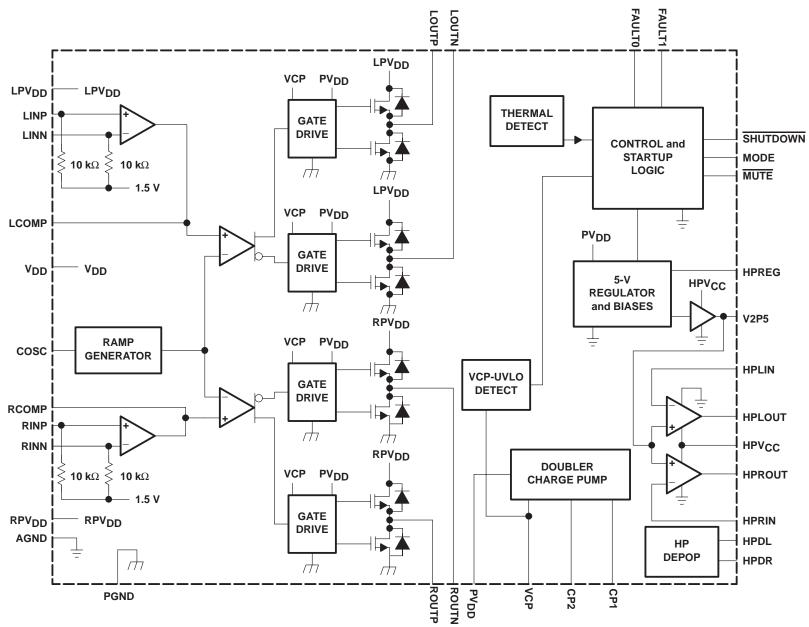

# electrical characteristics Class-D amplifier, V<sub>DD</sub> = PV<sub>DD</sub> = LPV<sub>DD</sub> = RPV<sub>DD</sub> = 12 V, R<sub>L</sub> = 4 $\Omega$ to 8 $\Omega$ , T<sub>A</sub> = 25°C, See Figure 1 (unless otherwise noted)

|                        | PARAMETER                                                              | TEST CONDITIONS                                               | MIN | TYP | MAX | UNIT |

|------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

|                        | Power supply rejection ratio                                           | $V_{DD} = PV_{DD} = xPV_{DD} = 11 \text{ V to } 13 \text{ V}$ |     | -40 |     | dB   |

| I <sub>DD</sub>        | Supply current                                                         | No output filter connected                                    |     | 25  | 35  | mA   |

| I <sub>DD</sub> (Mute) | Supply current, mute mode                                              | MUTE = 0 V                                                    |     | 10  | 18  | mA   |

| I <sub>DD</sub> (S/D)  | Supply current, shutdown mode                                          | SHUTDOWN = 0 V                                                |     | 20  | 30  | μΑ   |

| IIIII                  | High-level input current (MUTE, MODE, SHUTDOWN)                        | V <sub>IH</sub> = 5.25 V                                      |     |     | 10  | μΑ   |

| I <sub>IL</sub>        | Low-level input current (MUTE, MODE, SHUTDOWN)                         | V <sub>IL</sub> = -0.3 V                                      |     |     | 10  | μА   |

| rDS(on)                | Static drain-to-source on-state resistance (high-side + low-side FETs) | I <sub>DD</sub> = 0.5 A                                       |     | 720 | 800 | mΩ   |

| rDS(on)                | Matching, high-side to high-side, low-side to low-side, same channel   |                                                               | 95% | 98% |     | ·    |

# operating characteristics, Class-D amplifier, $V_{DD}$ = $PV_{DD}$ = $LPV_{DD}$ = $RPV_{DD}$ = 12 V, $R_L$ = 4 $\Omega$ , $T_A$ = 25°C, See Figure 1 (unless otherwise noted)

|                | PARAMETER                                               | TEST CONDITIONS                                                                 | MIN | TYP | MAX   | UNIT |

|----------------|---------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-------|------|

| PO             | Output power                                            | f = 1 kHz,<br>THD = 0.5%, per channel,<br>Device soldered on PCB,<br>See Note 2 |     | 10  |       | W    |

|                | Efficiency                                              | P <sub>O</sub> = 10 W,<br>f = 1 kHz                                             |     | 77% |       |      |

| Ay             | Gain                                                    |                                                                                 |     | 25  |       | dB   |

|                | Left/right channel gain matching                        |                                                                                 | 92% | 95% |       |      |

|                | Noise floor                                             |                                                                                 |     | -60 |       | dB   |

|                | Dynamic range                                           |                                                                                 |     | 80  |       | dB   |

|                | Crosstalk                                               | f = 1 kHz                                                                       |     | -50 |       | dB   |

|                | Frequency response bandwidth, post output filter, -3 dB |                                                                                 | 20  |     | 20000 | Hz   |

| ВОМ            | Maximum output power bandwidth                          |                                                                                 |     |     | 20    | kHz  |

| Z <sub>l</sub> | Input impedance                                         |                                                                                 |     | 10  |       | kΩ   |

NOTE 2: Output power is thermally limited,  $T_A = 23^{\circ}C$

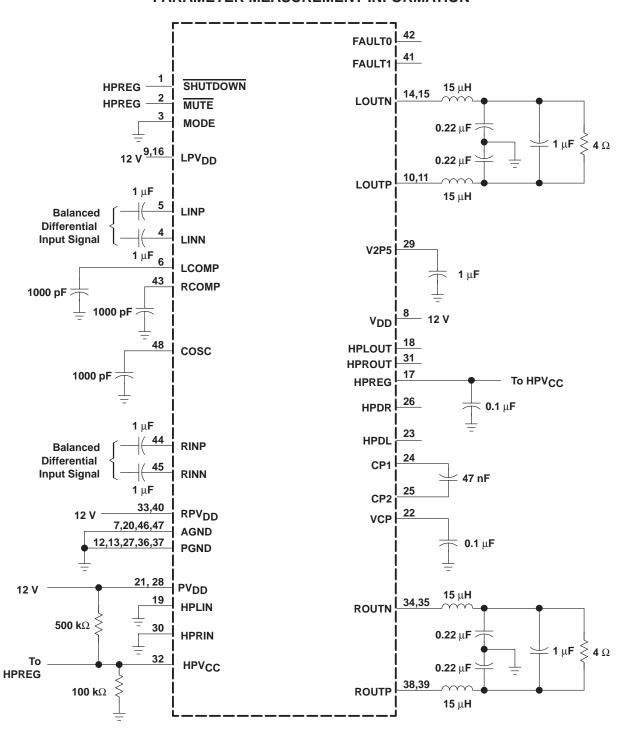

## operating characteristics, Class-D amplifier, $V_{DD}$ = $PV_{DD}$ = $LPV_{DD}$ = $RPV_{DD}$ = 12 V, $R_L$ = 8 $\Omega$ , $T_A$ = 25°C, See Figure 2 (unless otherwise noted)

|                | PARAMETER                                               | TEST CONDITIONS                                                   | MIN | TYP             | MAX    | UNIT |

|----------------|---------------------------------------------------------|-------------------------------------------------------------------|-----|-----------------|--------|------|

| PO             | Output power,                                           | THD = 0.5%, per channel,<br>Device soldered on PCB,<br>See Note 2 |     | 7.5             |        | W    |

|                | Efficiency                                              | P <sub>O</sub> = 7.5 W,<br>f = 1 kHz                              |     | 85%             |        |      |

| Ay             | Gain                                                    |                                                                   |     | 25              |        | dB   |

|                | Left/right channel gain matching                        |                                                                   | 92% | 95%             |        |      |

|                | Noise floor                                             |                                                                   |     | -60             |        | dB   |

|                | Dynamic range                                           |                                                                   |     | 80              |        | dB   |

|                | Crosstalk                                               | f = 1 kHz                                                         |     | <del>-</del> 50 |        | dB   |

|                | Frequency response bandwidth, post output filter, -3 dB |                                                                   | 20  |                 | 20 000 | Hz   |

| Вом            | Maximum output power bandwidth                          |                                                                   |     |                 | 20     | kHz  |

| Z <sub>l</sub> | Input impedance                                         |                                                                   |     | 10              |        | kΩ   |

NOTE 2: Output power is thermally limited,  $T_A = 85^{\circ}C$

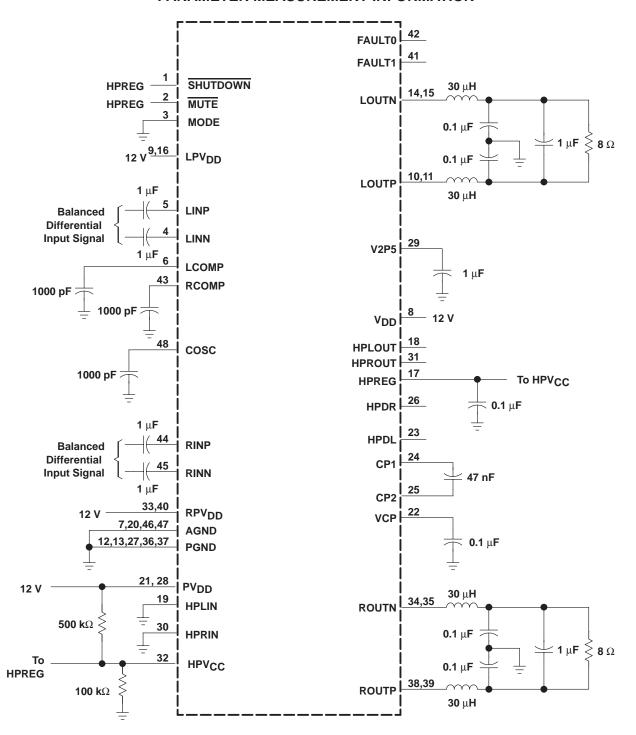

## electrical characteristics, headphone amplifier, HPV $_{CC}$ = 5 V, R $_{L}$ = 32 $\Omega$ , T $_{A}$ = 25°C, See Figure 3 (unless otherwise noted)

|                       | PARAMETER                     | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------|-----------------|-----|-----|-----|------|

|                       | Power supply rejection ratio  |                 |     | -60 |     | dB   |

|                       | Uncompensated gain range      |                 | -1  |     | -10 | V/V  |

| I <sub>DD</sub>       | Supply current                |                 |     | 9   | 12  | mA   |

| IDD(MUTE)             | Supply current, mute mode     |                 |     | 9   | 12  | mA   |

| I <sub>DD</sub> (S/D) | Supply current, shutdown mode |                 |     | 20  | 30  | μΑ   |

# operating characteristics, headphone amplifier, HPV $_{CC}$ = 5V, R $_{L}$ = 32 $\Omega$ , gain set at -10V/V, T $_{A}$ = 25°C, See Figure 3 (unless otherwise noted)

|     | PARAMETER                                               | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|-----|---------------------------------------------------------|--------------------------|-----|-----|-----|------|

| PO  | Output power                                            | THD = 0.5%,<br>f = 1 kHz |     | 50  |     | mW   |

|     | Crosstalk                                               | f = 1 kHz                |     | -60 |     | dB   |

|     | Frequency response bandwidth, post output filter, -3 dB |                          | 20  |     | 20  | kHz  |

| ВОМ | Maximum output power bandwidth                          |                          |     |     | 20  | kHz  |

| ZI  | Input impedance                                         |                          |     | >1  |     | МΩ   |

## operating characteristics, HPREG 5-V regulator, $T_A$ = 25°C (unless otherwise noted)

|     | PARAMETER                    | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |

|-----|------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VO  | Output voltage               | $V_{DD} = PV_{DD} = LPV_{DD} = RPV_{DD} = 8 V \text{ to } 14 V,$<br>$I_{O} = 0 \text{ to } 90 \text{ mA}$ | 4.5 |     | 5.5 | V    |

| los | Short-circuit output current | $V_{DD} = PV_{DD} = LPV_{DD} = RPV_{DD} = 8 V \text{ to } 14 V^{\dagger}$                                 | 90  |     |     | mA   |

<sup>†</sup> Pulse width must be limited to prevent exceeding the maximum operating virtual junction temperature of 150°C.

#### thermal shutdown

| PARAMETER                    | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------|-----------------|-----|-----|-----|------|

| Thermal shutdown temperature |                 |     | 165 |     | °C   |

| Thermal shutdown hysteresis  |                 |     | 30  |     | °C   |

## PARAMETER MEASUREMENT INFORMATION

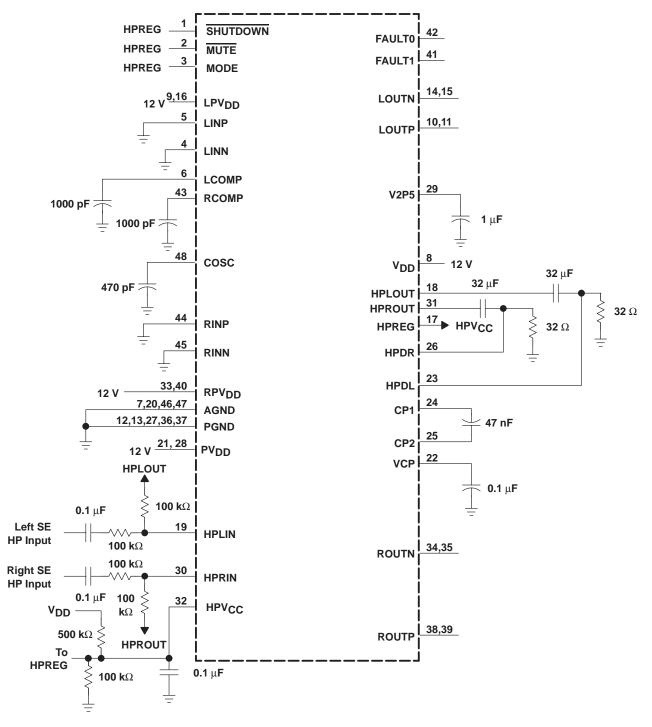

Figure 1. 12-V, 4- $\Omega$  Test Circuit

## PARAMETER MEASUREMENT INFORMATION

Figure 2. 12-V, 8- $\Omega$  Test Circuit

## PARAMETER MEASUREMENT INFORMATION

Figure 3. Headphone Test Circuit

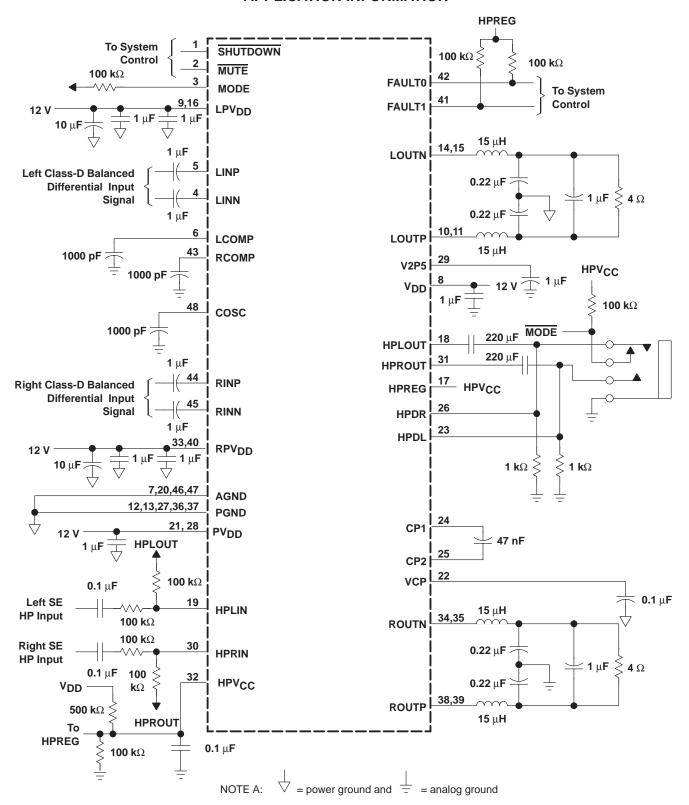

Figure 4. TPA032D04 Typical Configuration Application Circuit

## input capacitor, CI

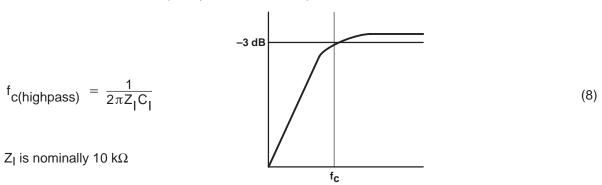

In the typical application an input capacitor,  $C_I$ , is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case,  $C_I$  and  $Z_I$ , the TPA032D04's input resistance forms a high-pass filter with the corner frequency determined in equation 8.

The value of  $C_l$  is important to consider as it directly affects the bass (low frequency) performance of the circuit. Consider the example where the specification calls for a flat bass response down to 40 Hz. Equation 8 is reconfigured as equation 9.

$$C_{I} = \frac{1}{2\pi Z_{I} f_{C}}$$

(9)

In this example,  $C_I$  is 0.40  $\mu$ F so one would likely choose a value in the range of 0.47  $\mu$ F to 1  $\mu$ F. A low-leakage tantalum or ceramic capacitor is the best choice for the input capacitors. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input, as the dc level there is held at 1.5 V, which is likely higher than the source dc level. Please note that it is important to confirm the capacitor polarity in the application.

#### differential input

The TPA032D04 has differential inputs to minimize distortion at the input to the IC. Since these inputs nominally sit at 1.5 V, dc-blocking capacitors are required on each of the four input terminals. If the signal source is single-ended, optimal performance is achieved by treating the signal ground as a signal. In other words, reference the signal ground at the signal source, and run a trace to the dc-blocking capacitor, which should be located physically close to the TPA032D04. If this is not feasible, it is still necessary to locally ground the unused input terminal through a dc-blocking capacitor.

## power supply decoupling, CS

The TPA032D04 is a high-performance Class-D CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F placed as close as possible to the device's various  $V_{DD}$  leads, works best. For filtering lower-frequency noise signals, a larger aluminum electrolytic capacitor of  $10\,\mu$ F or greater placed near the audio power amplifier is recommended.

The TPA032D04 has several different power supply terminals. This was done to isolate the noise resulting from high-current switching from the sensitive analog circuitry inside the IC.

### **APPLICATION INFORMATION**

#### mute and shutdown modes

The TPA032D04 employs both a mute and a shutdown mode of operation designed to reduce supply current,  $I_{DD}$ , to the absolute minimum level during periods of nonuse for battery-power conservation. The <u>SHUTDOWN</u> input terminal should be held high during normal operation when the amplifier is in use. Pulling <u>SHUTDOWN</u> low causes the outputs to mute and the amplifier to enter a low-current state,  $I_{DD}$  = 20  $\mu$ A. Mute mode alone reduces  $I_{DD}$  to 10 mA.

## using low-ESR capacitors

Low-ESR capacitors are recommended throughout this applications section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance the more the real capacitor behaves like an ideal capacitor.

## output filter components

The output inductors are key elements in the performance of the class-D audio amplifier system. It is important that these inductors have a high enough current rating and a relatively constant inductance over frequency and temperature. The current rating should be higher than the expected maximum current to avoid magnetically saturating the inductor. When saturation occurs, the inductor loses its functionality and looks like a short circuit to the PWM signal, which increases the harmonic distortion considerably.

A shielded inductor may be required if the class-D amplifier is placed in an EMI sensitive system; however, the switching frequency is low for EMI considerations and should not be an issue in most systems. The dc series resistance of the inductor should be low to minimize losses due to power dissipation in the inductor, which reduces the efficiency of the circuit.

Capacitors are important in attenuating the switching frequency and high frequency noise, and in supplying some of the current to the load. It is best to use capacitors with low equivalent-series-resistance (ESR). A low ESR means that less power is dissipated in the capacitor as it shunts the high-frequency signals. Placing these capacitors in parallel also parallels their ESR, effectively reducing the overall ESR value. The voltage rating is also important, and, as a rule of thumb, should be 2 to 3 times the maximum rms voltage expected to allow for high peak voltages and transient spikes. These output filter capacitors should be stable over temperature since large currents flow through them.

## efficiency of class-D vs linear operation

Amplifier efficiency is defined as the ratio of output power delivered to the load to power drawn from the supply. In the efficiency equation below,  $P_{I}$  is power across the load and  $P_{SUP}$  is the supply power.

$$\text{Efficiency} = \eta = \frac{P_L}{P_{SUP}}$$

A high-efficiency amplifier has a number of advantages over one with lower efficiency. One of these advantages is a lower power requirement for a given output, which translates into less waste heat that must be removed from the device, smaller power supply required, and increased battery life.

Audio power amplifier systems have traditionally used linear amplifiers, which are well known for being inefficient. Class-D amplifiers were developed as a means to increase the efficiency of audio power amplifier systems.

A linear amplifier is designed to act as a variable resistor network between the power supply and the load. The transistors operate in their linear region and voltage that is dropped across the transistors (in their role as variable resistors) is lost as heat, particularly in the output transistors.

The output transistors of a class-D amplifier switch from full OFF to full ON (saturated) and then back again, spending very little time in the linear region in between. As a result, very little power is lost to heat because the transistors are not operated in their linear region. If the transistors have a low on-resistance, little voltage is dropped across them, further reducing losses. The ideal class-D amplifier is 100% efficient, which assumes that both the on-resistance (r<sub>DS(on)</sub>) and the switching times of the output transistors are zero.

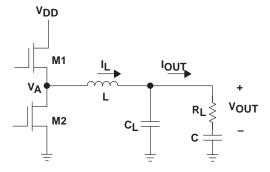

#### the ideal class-D amplifier

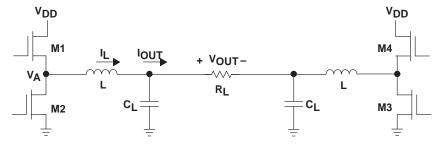

To illustrate how the output transistors of a class-D amplifier operate, a half-bridge application is examined first (see Figure 5).

Figure 5. Half-Bridge Class-D Output Stage

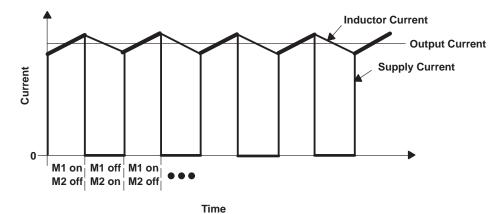

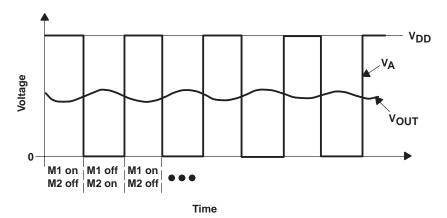

Figures 6 and 7 show the currents and voltages of the half-bridge circuit. When transistor M1 is on and M2 is off, the inductor current is approximately equal to the supply current. When M2 switches on and M1 switches off, the supply current drops to zero, but the inductor keeps the inductor current from dropping. The additional inductor current is flowing through M2 from ground. This means that  $V_A$  (the voltage at the drain of M2, as shown in Figure 5) transitions between the supply voltage and slightly below ground. The inductor and capacitor form a low-pass filter, which makes the output current equal to the average of the inductor current. The low-pass filter averages  $V_A$ , which makes  $V_{OUT}$  equal to the supply voltage multiplied by the duty cycle.

## the ideal class-D amplifier (continued)

Control logic is used to adjust the output power, and both transistors are never on at the same time. If the output voltage is rising, M1 is on for a longer period of time than M2.

Figure 6. Class-D Currents

Figure 7. Class-D Voltages

### the ideal class-D amplifier (continued)

Given these plots, the efficiency of the class-D device can be calculated and compared to an ideal linear amplifier device. In the derivation below, a sine wave of peak voltage (V<sub>P</sub>) is the output from an ideal class-D and linear amplifier and the efficiency is calculated.

$$\text{CLASS-D} \qquad \qquad \text{LINEAR} \\ V_{L(rms)} = \frac{V_P}{\sqrt{2}} \qquad \qquad V_{L(rms)} = \frac{V_P}{\sqrt{2}} \\ \text{Average } \left(I_{DD}\right) = \frac{I_{L(rms)} \times V_{L(rms)}}{V_{DD}} \qquad \qquad P_L = \frac{V_{L(rms)}^2}{R_L} = \frac{V_P^2}{2 R_L} \\ P_L = V_L \times I_L \qquad \qquad \text{Average } \left(I_{DD}\right) = \frac{2}{\pi} \times \frac{V_P}{R_L} \\ P_{SUP} = V_{DD} \times \text{Average} \left(I_{DD}\right) \qquad \qquad P_{SUP} = V_{DD} \times \text{Average} \left(I_{DD}\right) = \frac{V_{DD} \ V_P}{R_L} \times \frac{2}{\pi} \\ P_{SUP} = \frac{V_{DD} \times I_{L(rms)} \times V_{L(rms)}}{V_{DD}} \qquad \qquad \text{Efficiency } = \eta = \frac{P_L}{P_{SUP}} \\ \text{Efficiency } = \eta = \frac{P_L}{P_{SUP}} \qquad \qquad \text{Efficiency } = \eta = V_{DD} \times \frac{\frac{V_P^2}{2R_L}}{\frac{2}{\pi} \times \frac{V_P}{R_L}} \\ \text{Efficiency } = \eta = 1 \qquad \qquad \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \eta = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Efficiency } = \frac{\pi}{4} \times \frac{V_P}{V_{DD}} \\ \text{Effic$$

In the ideal efficiency equations, assume that  $V_P = V_{DD}$ , which is the maximum sine wave magnitude without clipping. Then, the highest efficiency that a linear amplifier can have without clipping is 78.5%. A class-D amplifier, however, can ideally have an efficiency of 100% at all power levels.

The derivation above applies to an H-bridge as well as a half-bridge. An H-bridge requires approximately twice the supply current but only requires half the supply voltage to achieve the same output power—factors that cancel in the efficiency calculation. The H-bridge circuit is shown in Figure 8.

Figure 8. H-Bridge Class-D Output Stage

### losses in a real-world class-D amplifier

Losses make class-D amplifiers nonideal, and reduce the efficiency below 100%. These losses are due to the output transistors having a nonzero  $r_{DS(on)}$ , and rise and fall times that are greater than zero.

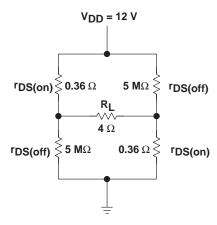

The loss due to a nonzero  $r_{DS(on)}$  is called conduction loss, and is the power lost in the output transistors at nonswitching times, when the transistor is on (saturated). Any  $r_{DS(on)}$  above 0  $\Omega$  causes conduction loss. Figure 9 shows an H-bridge output circuit simplified for conduction loss analysis and can be used to determine new efficiencies with conduction losses included.

Figure 9. Output Transistor Simplification for Conduction Loss Calculation

The power supplied,  $P_{SUP}$ , is determined to be the power output to the load plus the power lost in the transistors, assuming that there are always two transistors on.

Efficiency =

$$\eta = \frac{P_L}{P_{SUP}}$$

Efficiency =  $\eta = \frac{I^2R_L}{I^2 2r_{DS(on)} + I^2R_L}$

Efficiency =  $\eta = \frac{R_L}{2r_{DS(on)} + R_L}$

Efficiency =  $\eta = 95\%$  (at all output levels  $r_{DS(on)} = 0.1 \ \Omega$ ,  $R_L = 4 \ \Omega$ )

Efficiency =  $\eta = 85\%$  (at all output levels  $r_{DS(on)} = 0.36 \ \Omega$ ,  $R_L = 4 \ \Omega$ )

## losses in a real-world class-D amplifier (continued)

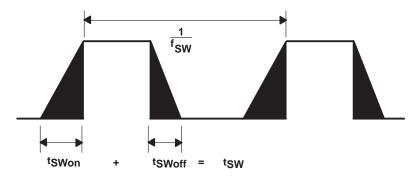

Losses due to rise and fall times are called switching losses. A diagram of the output, showing switching losses, is shown in Figure 10.

Figure 10. Output Switching Losses

Rise and fall times are greater than zero for several reasons. One is that the output transistors cannot switch instantaneously because (assuming a MOSFET) the channel from drain to source requires a specific period of time to form. Another is that transistor gate-source capacitance and parasitic resistance in traces form RC time constants that also increase rise and fall times.

Switching losses are constant at all output power levels, which means that switching losses can be ignored at high power levels in most cases. At low power levels, however, switching losses must be taken into account when calculating efficiency. Switching losses are dominated by conduction losses at the high output powers, but should be considered at low powers. The switching losses are automatically taken into account if you consider the quiescent current with the output filter and load.

## class-D effect on power supply

Efficiency calculations are an important factor for proper power supply design in amplifier systems. Table 2 shows Class-D efficiency at a range of output power levels (per channel) with a 1-kHz sine wave input. The maximum power supply draw from a stereo 10-W per channel audio system with 4- $\Omega$  loads and a 12-V supply is almost 26 W. A similar linear amplifier such as the TPA032D04 has a maximum draw of greater than 50 W under the same circumstances.

Table 2. Efficiency vs Output Power in 12-V 4- $\Omega$  H-Bridge Systems

| Output Power (W) | Efficiency (%) | Peak Voltage (V) | Internal Dissipation (W) |

|------------------|----------------|------------------|--------------------------|

| 0.5              | 41.7           | 2                | 0.7                      |

| 2                | 66.7           | 4                | 1.0                      |

| 5                | 75.1           | 6.32             | 1.66                     |

| 8                | 78             | 8                | 2.26                     |

| 10               | 77.9           | 8.94†            | 2.84                     |

<sup>†</sup> High peak voltages cause the THD to increase

## class-D effect on power supply (continued)

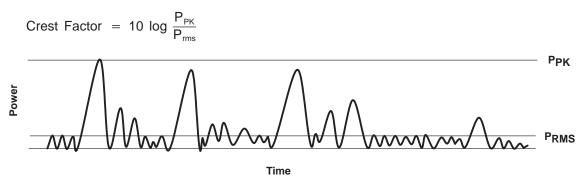

There is a minor power supply savings with a class-D amplifier versus a linear amplifier when amplifying sine waves. The difference is much larger when the amplifier is used strictly for music. This is because music has much lower RMS output power levels, given the same peak output power (see Figure 11); and although linear devices are relatively efficient at high RMS output levels, they are very inefficient at mid-to-low RMS power levels. The standard method of comparing the peak power to RMS power for a given signal is crest factor, whose equation is shown below. The lower RMS power for a set peak power results in a higher crest factor

Figure 11. Audio Signal Showing Peak and RMS Power

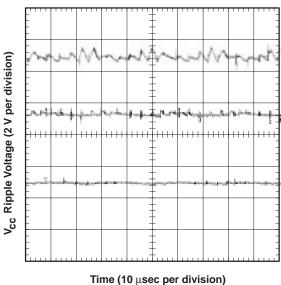

## class-D EVM power supply decoupling data

The decoupling capacitance required will depend upon the application. Pads and through-holes have been provided on the EVM for the addition of bulk capacitance (see the schematic). A plot showing the impact of various levels of bulk capacitance on the voltage ripple on the power supply line is shown in Figure 12. This ripple is maximum at higher frequency. The figure shows worst-case voltage ripple for a 20-kHz, 10-W output into a 4- $\Omega$  load. In all cases, two 10- $\mu$ F and one 1- $\mu$ F ceramic chip capacitors were decoupling the power supply signal from the EVM. The 1- $\mu$ F unit was placed immediately adjacent to the IC power pins, and the 10- $\mu$ F units were placed adjacent to each other a little farther out.

The upper trace shows the ripple when only these capacitors are used. The middle trace shows the impact of an additional 330- $\mu$ F aluminum electrolytic capacitor rated at 25 V, 90 m $\Omega$ , and for 755 mA at 100 kHz. In the bottom trace, the 330- $\mu$ F capacitor was replaced by a 390- $\mu$ F aluminum electrolytic capacitor rated at 35 V, 65 m $\Omega$ , and for 1.2 A of 100 kHz ripple current.

The results indicate that for sensitive circuits where minimum voltage ripple is required, a larger bulk capacitance with low ESR should be used. For systems that are contained and EMI is controlled, less capacitance may be used. The difference in the level of distortion in the output signal was very small between each level of decoupling, with the 20- $\mu$ F bulk capacitance providing the least distortion. This is attributed to the low ESR of the capacitor, which is only a few milliohms at the switching frequency of 250 kHz. The distortion is made lower still by the parallel combination. Distortion of the output signal when only one 10- $\mu$ F capacitor is used is the same as for 20  $\mu$ F. The difference is more noticeable on the power supply line, though the distortion is increased only slightly more than with the 20- $\mu$ F capacitor.

## RIPPLE VOLTAGE

Figure 12. Power Supply Decoupling

#### crest factor and thermal considerations

A typical music CD requires 12 dB to 15 dB of dynamic headroom to pass the loudest portions without distortion as compared with the average power output. From the TPA032D04 data sheet, one can see that when the TPA032D04 is operating from a 12-V supply into a 4- $\Omega$  speaker that 20-W peaks are available. Converting watts to dB:

$$P_{dB} = 10 Log \left(\frac{P_W}{P_{ref}}\right) = 10 Log \left(\frac{20}{1}\right) = 6 dB$$

(17)

Subtracting the crest factor restriction to obtain the average listening level without distortion yields:

$$6.0 \text{ dB} - 18 \text{ dB} = -12 \text{ dB}$$

(15 dB crest factor)

$6.0 \text{ dB} - 15 \text{ dB} = -9 \text{ dB}$  (15 dB crest factor)

$6.0 \text{ dB} - 12 \text{ dB} = -6 \text{ dB}$  (12 dB crest factor)

$6.0 \text{ dB} - 9 \text{ dB} = -3 \text{ dB}$  (9 dB crest factor)

$6.0 \text{ dB} - 6 \text{ dB} = -0 \text{ dB}$  (6 dB crest factor)

$6.0 \text{ dB} - 3 \text{ dB} = 3 \text{ dB}$  (3 dB crest factor)

Converting dB back into watts:

This is valuable information to consider when attempting to estimate the heat dissipation requirements for the amplifier system. Comparing the absolute worst case, which is 10 W of continuous power output with a 3 dB crest factor, against 12 dB and 15 dB applications drastically affects maximum ambient temperature ratings for the system. Using the power dissipation curves for a 12-V,  $4-\Omega$  system, the internal dissipation in the TPA032D04 and maximum ambient temperatures are shown in Table 3.

## crest factor and thermal considerations (continued)

Table 3. TPA032D04 Power Rating, 12-V, 4-Ω, Stereo

| PEAK OUTPUT POWER<br>(W) | AVERAGE OUTPUT POWER | POWER DISSIPATION<br>(W/Channel) | MAXIMUM AMBIENT<br>TEMPERATURE |

|--------------------------|----------------------|----------------------------------|--------------------------------|

| 20                       | 10 W (3 dB)          | 2.84                             | 23°C                           |

| 20                       | 5 W (6 dB)           | 1.66                             | 75°C                           |

| 20                       | 2.5 W (9 dB)         | 1.12                             | 100°C                          |

| 20                       | 1.25 W (12 dB)       | 0.87                             | 111°C                          |

| 20                       | 630 mW (15 dB)       | 0.7                              | 118°C                          |

| 20                       | 315 mW (18 dB)       | 0.6                              | 123°C                          |

The maximum ambient temperature depends on the heatsinking ability of the PCB system. Using the 0 CFM data from the dissipation rating table, the derating factor for the DCA package with 6.9 in<sup>2</sup> of copper area on a multilayer PCB is 44.8 mW/°C. Converting this to  $\Theta_{JA}$ :

$$\Theta_{\text{JA}} = \frac{1}{\text{Derating}}$$

$$= \frac{1}{0.0448}$$

$$= 22.3^{\circ}\text{C/W}$$

(19)

To calculate maximum ambient temperatures, first consider that the numbers from the dissipation graphs are per channel so the dissipated heat needs to be doubled for two channel operation. Given  $\Theta_{JA}$ , the maximum allowable junction temperature, and the total internal dissipation, the maximum ambient temperature can be calculated with the following equation. The maximum recommended junction temperature for the TPA032D04 is 150 °C. The internal dissipation figures are taken from the Efficiency vs Output Power graphs.

$$T_A \text{ Max} = T_J \text{ Max} - \Theta_{JA} P_D$$

(20)

= 150 - 22.3(0.7 × 2) = 118°C (15 dB crest factor)

= 150 - 22.3(2.84 × 2) = 23°C (3dB crest factor)

#### NOTE:

Internal dissipation of 1.4 W is estimated for a 10-W system with a 15 dB crest factor per channel.

The TPA032D04 is designed with thermal protection that turns the device off when the junction temperature surpasses 150°C to prevent damage to the IC. Table 3 was calculated for maximum listening volume without distortion. When the output level is reduced the numbers in the table change significantly. Also, using  $8-\Omega$  speakers dramatically increases the thermal performance by increasing amplifier efficiency.

### THERMAL INFORMATION

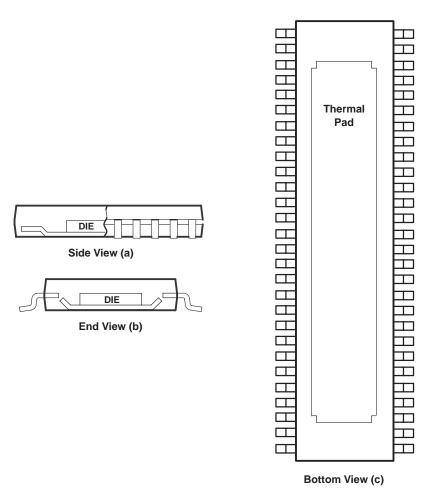

The thermally enhanced DCA package is based on the 56-pin TSSOP, but includes a thermal pad (see Figure 13) to provide an effective thermal contact between the IC and the PWB.

Traditionally, surface-mount and power have been mutually exclusive terms. A variety of scaled-down TO-220-type packages have leads formed as gull wings to make them applicable for surface-mount applications. These packages, however, have only two shortcomings: they do not address the very low profile requirements (<2 mm) of many of today's advanced systems, and they do not offer a terminal-count high enough to accommodate increasing integration. On the other hand, traditional low-power surface-mount packages require power-dissipation derating that severely limits the usable range of many high-performance analog circuits.

The PowerPAD package (thermally enhanced TSSOP) combines fine-pitch surface-mount technology with thermal performance comparable to much larger power packages.

The PowerPAD package is designed to optimize the heat transfer to the PWB. Because of the very small size and limited mass of a TSSOP package, thermal enhancement is achieved by improving the thermal conduction paths that remove heat from the component. The thermal pad is formed using a patented lead-frame design and manufacturing technique to provide a direct connection to the heat-generating IC. When this pad is soldered or otherwise thermally coupled to an external heat dissipator, high power dissipation in the ultrathin, fine-pitch, surface-mount package can be reliably achieved.

Figure 13. Views of Thermally Enhanced DCA Package

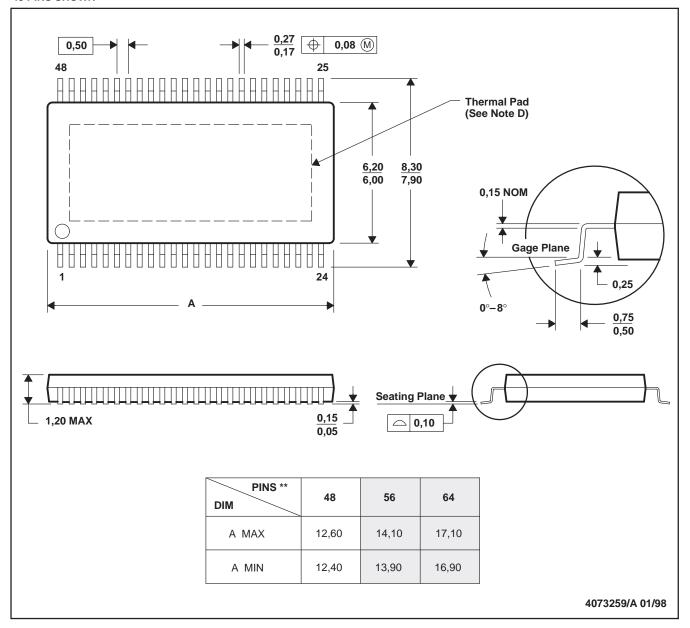

#### **MECHANICAL DATA**

## DCA (R-PDSO-G\*\*)

## PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

## **48 PINS SHOWN**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated