# HIGH EFFICIENCY CLASS-G ADSL LINE DRIVER

#### **FEATURES**

- Low Total Power Consumption Increases ADSL Line Card Density (20 dBm on Line)

- 600 mW w/Active Termination (Full Bias)

- 530 mW w/Active Termination (Low Bias)

- Low MTPR of -74 dBc (All Bias Conditions)

- High Output Current of 500 mA (typ)

- Wide Supply Voltage Range of ±5 V to ±15 V [V<sub>CC(H)</sub>] and ±3.3 V to ±15 V [V<sub>CC(L)</sub>]

- Wide Output Voltage Swing of 43 Vpp Into 100-Ω Differential Load [V<sub>CC(H)</sub> = ±12 V]

- Multiple Bias Modes Allow Low Quiescent Power Consumption for Short Line Lengths

- 160-mW/ch Full Bias Mode

- 135-mW/ch Mid Bias Mode

- 110-mW/ch Low Bias Mode

- 75-mW/ch Terminate Only Mode

- 13-mW/ch Shutdown Mode

- Low Noise for Increased Receiver Sensitivity

- 3.3 pA/√Hz Noninverting Current Noise

- 9.5 pA/√Hz Inverting Current Noise

- 3.5 nV/√Hz Voltage Noise

#### **APPLICATIONS**

Ideal for Active Termination Full Rate ADSL DMT applications (20-dBm Line Power)

#### DESCRIPTION

The THS6132 is a Class-G current feedback differential line driver ideal for full rate ADSL DMT systems. Its extremely low power consumption of 600 mW or lower is ideal for ADSL systems that must achieve high densities in ADSL central office rack applications. The unique patent pending architecture of the THS6132 allows the quiescent current to be much lower than existing line drivers while still achieving very high linearity. In addition, the multiple bias settings of the amplifiers allow for even lower power consumption for line lengths where the full performance of the amplifier is not required. The output voltage swing has been vastly improved over first generation Glass-G amplifiers and allows the use of lower power supply voltages that help conserve power. For maximum flexibility, the THS6132 can be configured in classical Class-AB mode requiring only as few as one power supply.

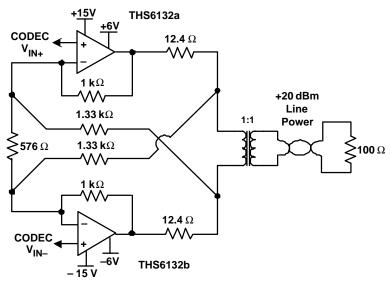

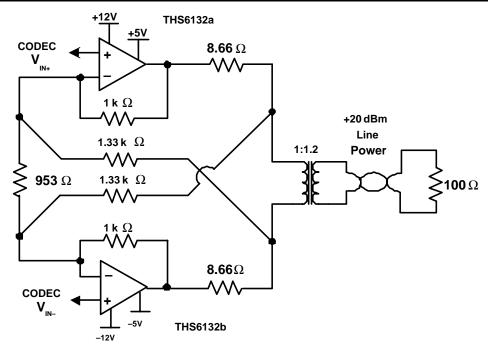

# Typical ADSL CO Line Driver Circuit Utilizing Active Impedance Supporting A 6.3 Crest Factor

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage.

#### ORDERING INFORMATION

| PRODUCT     | PACKAGE                                   | PACKAGE<br>CODE | SYMBOL    | TA            | ORDER NUMBER | TRANSPORT<br>MEDIA |

|-------------|-------------------------------------------|-----------------|-----------|---------------|--------------|--------------------|

| TUCC420\/ED | TOED SO Downer DA DIM                     | VED 22          | TI ICC422 |               | THS6132VFP   | Tube               |

| THS6132VFP  | TQFP-32 PowerPAD™                         | VFP-32          | THS6132   | -40°C to 85°C | THS6132VFPR  | Tape and reel      |

| THS6132RGW  | Leadless 25-pin 5,mm x<br>5, mm PowerPAD™ | RGW-25          | 6132      | -40 C 10 65 C | THS6132RGWR  | Tape and reel      |

## PACKAGE DISSIPATION RATINGS

| PACKAGE | ΘЈА      | ΘJC      | $T_A \le 25^{\circ}C$ POWER RATING(1) | T <sub>A</sub> = 70°C<br>POWER RATING <sup>(1)</sup> | T <sub>A</sub> = 85°C<br>POWER RATING <sup>(1)</sup> |

|---------|----------|----------|---------------------------------------|------------------------------------------------------|------------------------------------------------------|

| VFP-32  | 29.4°C/W | 0.96°C/W | 3.57 W                                | 2.04 W                                               | 1.53 W                                               |

| RGW-25  | 31°C/W   | 1.7°C/W  | 3.39 W                                | 1.94 W                                               | 1.45 W                                               |

<sup>(1)</sup> Power rating is determined with a junction temperature of 130°C. This is the point where distortion starts to substantially increase. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                  |                                                                                      | THS6132       |

|------------------|--------------------------------------------------------------------------------------|---------------|

| Supply voltage   | e, V <sub>CC(H)</sub> and V <sub>CC(L)</sub> (2)                                     | ±16.5 V       |

| Input voltage, \ | /।                                                                                   | ±VCC(L)       |

| Output current   | , I <sub>O</sub> (3)                                                                 | 900 mA        |

| Differential inp | ut voltage, V <sub>IO</sub>                                                          | ±2 V          |

| Maximum junc     | tion temperature, T <sub>J</sub> (see Dissipation Rating Table for more information) | 150°C         |

| Operating free   | -air temperature, T <sub>A</sub>                                                     | -40°C to 85°C |

| Storage tempe    | rature, T <sub>Stg</sub>                                                             | 65°C to 150°C |

| Lead temperat    | ure, 1,6 mm (1/16–inch) from case for 10 seconds                                     | 300°C         |

|                  | НВМ                                                                                  | 1 kV          |

| ESD ratings      | CDM                                                                                  | 500 V         |

|                  | ММ                                                                                   | 200 V         |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> V<sub>CC(H)</sub> must always be greater than or equal to V<sub>CC(L)</sub> for proper operation. Class-AB mode operation occurs when V<sub>CC(H)</sub> is equal to VCC(L) and is considered acceptable operation for the THS6132 even though it is not fully specified in this mode of operation.

<sup>(3)</sup> The THS6132 incorporates a PowerPAD on the underside of the chip. This acts as a heatsink and must be connected to a thermally dissipating plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature that could permanently damage the device. See TI Technical Brief SLMA002 for more information about utilizing the PowerPAD thermally enhanced package.

## **RECOMMENDED OPERATING CONDITIONS**

|                       |                            | MIN             | NOM | MAX                 | UNIT |

|-----------------------|----------------------------|-----------------|-----|---------------------|------|

| Committee and         | +VCC(H) to -VCC(H)         | $\pm V_{CC(L)}$ | ±15 | ±16                 | V    |

| Supply voltage        | +VCC(L) to -VCC(L)         | ±3.3            | ±5  | ±V <sub>CC(H)</sub> | V    |

| Operating free-air to | emperature, T <sub>A</sub> | -40             |     | 85                  | °C   |

## **ELECTRICAL CHARACTERISTICS**

overrecommended operating free-air temperature range,  $T_A = 25^{\circ}C$ ,  $V_{CC(H)} = \pm 15$  V,  $V_{CC(L)} = \pm 5$  V RF = 1.5 k $\Omega$ , Gain = +10, Full Bias Mode, R<sub>L</sub> = 50  $\Omega$  (unless otherwise noted)

| NOISE | E/DISTORTION PER                                                  |                                  | TES                                                             | T CONDITIONS                            | MIN   | TYP   | MAX    | UNIT   |

|-------|-------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------|-----------------------------------------|-------|-------|--------|--------|

|       | Multitone power ratio                                             |                                  | Gain =+11, 163kHz<br>+20 dBm Line Powe<br>active termination, s | to 1.1MHz DMT,<br>r, 1:1.1 transformer, |       | -74   | WAA    | dBc    |

|       | Receive band spill-o                                              | ver                              | Gain =+11, 25 kHz to<br>applied                                 | o 138 kHz with MTPR signal              |       | -95   |        | dBc    |

|       | Harmonic distortion (Differential                                 |                                  | 2 <sup>nd</sup> harmonic                                        | Differential load = $100 \Omega$        |       | -84   |        | dBc    |

| HD    |                                                                   | ,                                | Znanamonic                                                      | Differential load = $25 \Omega$         |       | -69   |        | ubc    |

| טח    | Configuration, $f = 1 \text{ MHz}$ ,<br>VO(PP) = 2 V, Gain = +10) |                                  | 3 <sup>rd</sup> harmonic                                        | Differential load = $100 \Omega$        |       | -92   |        | dBc    |

|       | VO(PP) = 2 V, Guin                                                | - 110)                           | 314 narmonic                                                    | Differential load = $25 \Omega$         |       | -73   |        | aBc    |

| ٧n    | Input voltage noise                                               |                                  | f = 10 kHz                                                      |                                         |       | 3.5   |        | nV/√Hz |

|       | Input current noise +Input                                        |                                  | f = 10 kHz                                                      |                                         | 3.3   |       | pA/√Hz |        |

| In    | input current noise                                               | -Input                           | 1 = 10 KHZ                                                      |                                         |       | 9.5   |        | pA/√⊓∠ |

|       | Crosstalk                                                         |                                  | f = 1  MHz,<br>$R_L = 100 \Omega,$                              | $V_{O(PP)} = 2 V,$<br>Gain = +2         |       | -52   |        | dBc    |

| OUTP  | UT CHARACTERIS                                                    | TICS                             |                                                                 |                                         | •     |       |        |        |

|       |                                                                   |                                  | V 140V                                                          | R <sub>L</sub> = 100 Ω                  | ±10.4 | ±10.8 |        |        |

| \/ -  | Cincela and adams                                                 | turalta na acciana               | $V_{CC(H)} = \pm 12 \text{ V}$                                  | R <sub>L</sub> = 30 Ω                   | ±9.9  | ±10.4 |        | V      |

| ٧O    | Single-ended outpu                                                | t voitage swing                  | V 145 V                                                         | R <sub>L</sub> = 100 Ω                  | ±13.3 | ±13.8 |        | V      |

|       |                                                                   |                                  | $V_{CC(H)} = \pm 15 \text{ V}$                                  | R <sub>L</sub> = 50 Ω                   | ±13   | ±13.6 |        | V      |

|       | Output voltage trans                                              | ition from V <sub>CC(L)</sub> to | R <sub>I</sub> = 50 Ω                                           | VCC(L) = ±5 V                           |       | ±3.1  |        | V      |

|       | VCC(H) (Point when                                                | $e \ ICC(L) = ICC(H)$            | KC = 20.75                                                      | $V_{CC(L)} = \pm 6 \text{ V}$           |       | ±3.9  |        | V      |

| I.    | Output current (1)                                                | <u> </u>                         | B: -10.0                                                        | V <sub>CC(H)</sub> = ±12 V              |       | ±500  |        | mA     |

| lo    | Output current (1)                                                |                                  | R <sub>L</sub> = 10 Ω                                           | VCC(H) = ±15 V                          | ±400  | ±500  |        | IIIA   |

| I(SC) | Short-circuit current                                             | (1)                              | R <sub>L</sub> = 1 Ω                                            | VCC(H) = ±15 V                          |       | ±750  |        | mA     |

|       | Output resistance                                                 |                                  | Open-loop                                                       |                                         |       | 5     |        | Ω      |

|       | Output resistance—                                                | terminate mode                   | f = 1 MHz,                                                      | Gain = +10                              |       | 0.35  |        | Ω      |

|       | Output resistance—                                                | shutdown mode                    | f = 1 MHz,                                                      | Open-loop                               |       | 5.5   |        | kΩ     |

<sup>(1)</sup> A heatsink is required to keep the junction temperature below absolute maximum rating when an output is heavily loaded or shorted. See Absolute Maximum Ratings section for more information.

ELECTRICAL CHARACTERISTICS (continued) over recommended operating free-air temperature range, T<sub>A</sub> = 25°C, V<sub>CC(H)</sub> =  $\pm$ 15 V, V<sub>CC(L)</sub> =  $\pm$ 5 V R<sub>F</sub> = 1.5 k $\Omega$ , Gain = +10, Full Bias Mode, R<sub>L</sub> = 50  $\Omega$  (unless otherwise noted)

| POWER  | R SUPPLY                                                                                                                         |                                                                   |                                                       |                             |      |         |       |    |

|--------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|-----------------------------|------|---------|-------|----|

|        | PARAMETER                                                                                                                        | TES"                                                              | TCONDITIONS                                           | MIN                         | TYP  | MAX     | UNIT  |    |

| V      | Operating rooms                                                                                                                  | ±V <sub>CC(H)</sub>                                               |                                                       | ±VCC(L)                     | ±15  | ±16.5   | ٧     |    |

| VCC(x) | Operatingrange                                                                                                                   | ±V <sub>CC(L)</sub>                                               |                                                       | ±3                          | ±5   | ±VCC(H) | ٧     |    |

|        |                                                                                                                                  | $V_{CC(L)} = \pm 5 \text{ V};$                                    | $T_A = 25^{\circ}C$                                   | 5.7                         | 6.4  | 7.5     | mA    |    |

|        |                                                                                                                                  | $(V_{CC(H)} = \pm 15 \text{ V})$                                  | T <sub>A</sub> = full range                           |                             |      | 8.1     | ША    |    |

|        | Quiescent current (each driver) Full-bias mode                                                                                   | $V_{CC(L)} = \pm 6 \text{ V};$                                    | T <sub>A</sub> = 25°C                                 |                             | 6.7  |         | mA    |    |

|        | (Bias-1 = 1, Bias-2 = 1,<br>Bias-3 = X)<br>(Icc trimmed with $V_{CC(H)} = \pm 15 \text{ V}$ ,<br>$V_{CC(L)} = \pm 5 \text{ V}$ ) | $(V_{CC(H)} = \pm 15 \text{ V})$                                  | T <sub>A</sub> = full range                           |                             |      |         | ША    |    |

|        |                                                                                                                                  | Bias-3 = X)<br>(Icc trimmed with $V_{CC(H)} = \pm 15 \text{ V}$ , | $V_{CC(H)} = \pm 12 \text{ V};$                       | T <sub>A</sub> = 25°C       |      | 3.1     |       | mA |

|        |                                                                                                                                  |                                                                   | $(V_{CC(L)} = \pm 5 \text{ V})$                       | T <sub>A</sub> = full range |      |         |       | ША |

|        |                                                                                                                                  | $V_{CC(H)} = \pm 15 \text{ V};$                                   | $T_A = 25^{\circ}C$                                   | 2.9                         | 3.25 | 3.75    | mA    |    |

| 1      |                                                                                                                                  | $(V_{CC(L)} = \pm 5 \text{ V})$                                   | T <sub>A</sub> = full range                           |                             |      | 4.25    | ША    |    |

| Icc    |                                                                                                                                  | Mid; Bias-1 = 1, Bias                                             | 5.0                                                   | 5.6                         | 6.8  | mA      |       |    |

|        | Quiescent current (each driver) Variable bias modes,                                                                             | Low; Bias-1 = 1, Bias-2 = 0, Bias-3 = 0                           |                                                       | 4.25                        | 4.8  |         | 6.0   |    |

|        | $V_{CC(L)} = \pm 5 \text{ V}$                                                                                                    | Terminate; Bias-1 =                                               | Ferminate; Bias-1 = 0, Bias-2 = 1, Bias-3 = $X^{(1)}$ |                             | 3.8  |         | 4.5   |    |

|        |                                                                                                                                  | Shutdown; Bias-1 =                                                | 0, Bias-2 = 0, Bias-3 = X(1)                          |                             | 1    | 1.3     |       |    |

|        |                                                                                                                                  | Mid; Bias-1 = 1, Bias                                             | s–2 = 0, Bias–3 = 1                                   | 2.4                         | 2.7  | 3.0     |       |    |

|        | Quiescent current (each driver) Variable bias modes,                                                                             | Low; Bias-1 = 1, Bia                                              | ıs–2 = 0, Bias–3 = 0                                  | 1.9                         | 2.15 | 2.4     | mA    |    |

|        | $V_{CC(H)} = \pm 15 \text{ V}$                                                                                                   | Terminate; Bias-1 =                                               | 0, Bias-2 = 1, Bias-3 = X(1)                          | 1.1                         | 1.3  | 1.5     | ША    |    |

|        |                                                                                                                                  | Shutdown; Bias-1 =                                                | 0, Bias-2 = 0, Bias-3 = $X(1)$                        |                             | 0.1  | 0.5     |       |    |

|        |                                                                                                                                  | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                            | T <sub>A</sub> = 25°C                                 | -70                         | -82  |         | _     |    |

| PSRR   | Power supply rejection ratio                                                                                                     | $V_{CC(L)} = \pm 5V$                                              | T <sub>A</sub> = full range                           | -68                         | •    | ·       | ם אום |    |

| PORK   | $(\Delta V_{CC(x)} = \pm 1 \text{ V})$                                                                                           | V0040 - ±15V                                                      | T <sub>A</sub> = 25°C                                 | -70                         | -82  |         | dB    |    |

|        |                                                                                                                                  | $V_{CC(H)} = \pm 15V$                                             | T <sub>A</sub> = full range                           | -68                         |      |         |       |    |

<sup>(1)</sup> X is used to denote a logic state of either 1 or 0.

ELECTRICAL CHARACTERISTICS (continued) overrecommended operating free-air temperature range,  $T_A = 25^{\circ}C$ ,  $V_{CC(H)} = \pm 15$  V,  $V_{CC(L)} = \pm 5$  V  $R_F = 1.5$  k $\Omega$ , Gain = +10, Full Bias Mode,  $R_L$ =  $50 \Omega$  (unless otherwise noted)

| DYNA | DYNAMIC PERFORMANCE                       |                                       |                               |     |     |     |        |  |

|------|-------------------------------------------|---------------------------------------|-------------------------------|-----|-----|-----|--------|--|

|      | PARAMETER                                 | TES                                   | T CONDITIONS                  | MIN | TYP | MAX | UNIT   |  |

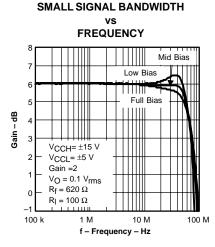

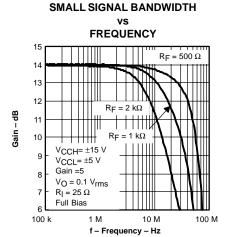

|      |                                           |                                       | Gain = +1, RF = 750 $\Omega$  |     | 80  |     |        |  |

|      |                                           | D. 100.0                              | Gain = +2, RF = 620 $\Omega$  |     | 70  |     | MHz    |  |

|      |                                           | $R_L = 100 \Omega$                    | Gain = +5, RF = $500 \Omega$  |     | 60  |     | IVITZ  |  |

| DW   | Single-endedsmall-signalbandwidth         |                                       | Gain = +10, RF = 1 k $\Omega$ |     | 20  |     |        |  |

| BW   | $(-3 \text{ dB}), V_0 = 0.1 \text{ Vrms}$ |                                       | Gain = +1, RF = 750 $\Omega$  |     | 60  |     |        |  |

|      |                                           | D. 25.0                               | Gain = +2, RF = 620 $\Omega$  |     | 55  |     | MHz    |  |

|      |                                           | $R_L = 25 \Omega$                     | Gain = +5, RF = $500 \Omega$  |     | 50  |     | IVITIZ |  |

|      |                                           |                                       | Gain = +10, RF = 1 k $\Omega$ |     | 17  |     |        |  |

| SR   | Single-endedslew-rate(1)                  | V <sub>O</sub> = 20 V <sub>PP</sub> , | Gain=+10                      |     | 300 |     | V/μs   |  |

<sup>(1)</sup> Slew-rate is defined from the 25% to the 75% output levels

| DC PE           | RFORMANCE                                                                                                             |                                                |                             |     |     |     |       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------|-----|-----|-----|-------|

|                 | PARAMETER                                                                                                             | TEST C                                         | ONDITIONS                   | MIN | TYP | MAX | UNIT  |

|                 | land offertualte as                                                                                                   |                                                | T <sub>A</sub> = 25°C       |     | 1   | 15  |       |

|                 | PARAMETER  Input offset voltage  Differential offset voltage  Offset drift  -Input bias current  + Input bias current | T                                              | T <sub>A</sub> = full range |     |     | 20  | \/    |

| Vos             | Differential offendaments                                                                                             | V <sub>CC(L)</sub> = ± 5 V, ±6 V               | T <sub>A</sub> = 25°C       |     | 0.3 | 6   | mV    |

|                 | Dillerentiaronset voltage                                                                                             | ( )                                            | T <sub>A</sub> = full range |     |     | 8   |       |

|                 | Offset drift                                                                                                          |                                                | T <sub>A</sub> = full range |     | 40  |     | μV/°C |

|                 | lamenthing assument                                                                                                   |                                                | T <sub>A</sub> = 25°C       |     | 1   | 15  |       |

|                 | Offset drift  -Input bias current                                                                                     |                                                | T <sub>A</sub> = full range |     |     | 20  |       |

| I <sub>IB</sub> | . In addition and                                                                                                     | $V_{CC(L)} = \pm 5 \text{ V}, \pm 6 \text{ V}$ | T <sub>A</sub> = 25°C       |     | 1.5 | 15  | μΑ    |

|                 | + input bias current                                                                                                  |                                                | T <sub>A</sub> = full range |     |     | 20  |       |

| Z <sub>OL</sub> | Open loop transimpedance                                                                                              | $R_L = 1 k\Omega$                              | ·                           |     | 2   |     | МΩ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating free-air temperature range,  $T_A = 25^{\circ}C$ ,  $V_{CC(H)} = \pm 15$  V,  $V_{CC(L)} = \pm 5$  V RF = 1.5 k $\Omega$ , Gain = +10, Full Bias Mode,  $R_L = 50~\Omega$  (unless otherwise noted)

| INPUT          | CHARACTERISTICS                    |                                                |                             |      |      |     |      |  |

|----------------|------------------------------------|------------------------------------------------|-----------------------------|------|------|-----|------|--|

|                | PARAMETER                          | TEST C                                         | ONDITIONS                   | MIN  | TYP  | MAX | UNIT |  |

|                |                                    | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\         | T <sub>A</sub> = 25°C       | ±2.7 | ±3.0 |     |      |  |

| $V_{ICR}$      | Input common-mode voltage range(1) | $V_{CC(L)} = \pm 5 \text{ V}$                  | T <sub>A</sub> = full range | ±2.6 |      |     | V    |  |

|                |                                    | $V_{CC(L)} = \pm 6 \text{ V}$                  | T <sub>A</sub> = 25°C       |      | ±4.0 |     |      |  |

|                | REF pin input voltage range        | $V_{CC-(L)} = \pm 5 V$ $V_{CC(L)} = \pm 6 V$   |                             |      | ±2.5 |     | V    |  |

|                | REF piir input voitage range       |                                                |                             | ±3.5 |      |     | 7 V  |  |

| CMDD           | Common-mode rejection ratio        | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\         | T <sub>A</sub> = 25°C       | 60   | 67   |     | dB   |  |

| CMRR           | Common-moderejectionratio          | $V_{CC(L)} = \pm 5 \text{ V}, \pm 6 \text{ V}$ | T <sub>A</sub> = full range | 57   |      |     | uБ   |  |

| Б              | Input resistance                   | + Input                                        |                             |      | 800  |     | kΩ   |  |

| R <sub>I</sub> | inputresistance                    | - Input                                        |                             |      | 45   |     | Ω    |  |

| CI             | Differential Input capacitance     |                                                |                             |      | 1.2  |     | pF   |  |

<sup>(1)</sup> To conserve as much power as possible, the input stage of the THS6132 is powered from the  $V_{CC(L)}$  supplies and is limited by the  $V_{CC(L)}$  supply voltage. For Class-AB operation, connect the  $V_{CC(L)}$  supplies to  $V_{CC(H)}$ .

| LOGIC CONTROL CHARACTERISTICS |                                                   |                                   |         |      |                       |      |

|-------------------------------|---------------------------------------------------|-----------------------------------|---------|------|-----------------------|------|

|                               | PARAMETER                                         | TEST CONDITIONS                   | MIN     | TYP  | MAX                   | UNIT |

| VIH                           | Bias pin voltage for logic 1                      | Relative to DGND pin voltage      | 2.0     |      |                       | V    |

| ٧ <sub>IL</sub>               | Bias pin voltage for logic 0                      | Relative to DGND pin voltage      |         |      | 0.8                   | V    |

| lн                            | Bias pin current for logic 1                      | V <sub>IH</sub> = 5 V, DGND = 0 V |         | -0.1 | -0.2                  | μΑ   |

| ΊL                            | Bias pin current for logic 0                      | V <sub>IL</sub> = 0 V, DGND = 0 V |         | -0.1 | -0.2                  | μΑ   |

|                               | Transition time—logic 0 to logic 1 <sup>(1)</sup> |                                   |         | 0.1  |                       | μs   |

|                               | Transition time—logic 1 to logic 0 <sup>(1)</sup> |                                   |         | 0.2  |                       | μs   |

|                               | DGND useable range                                |                                   | -VCC(H) |      | +VCC(H) <sup>-5</sup> | V    |

<sup>(1)</sup> Transition time is defined as the time from when the logic signal is applied to the time when the supply current has reached half its final value.

| LOGIC                                     | LOGIC TABLE |      |                |                                                                                              |  |  |  |  |  |

|-------------------------------------------|-------------|------|----------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| BIAS-1 BIAS-2 BIAS-3 FUNCTION DESCRIPTION |             |      |                |                                                                                              |  |  |  |  |  |

| 1                                         | 1           | χ(1) | Full bias mode | Amplifiers ON with lowest distortion possible                                                |  |  |  |  |  |

| 1                                         | 0           | 1    | Mid bias mode  | Amplifiers ON with power savings with a reduction in distortion performance                  |  |  |  |  |  |

| 1                                         | 0           | 0    | Low bias mode  | Amplifiers ON with enhanced power savings and a reduction of distortion performance          |  |  |  |  |  |

| 0                                         | 1           | χ(1) | Terminate mode | Lowest power state with +Vin pins internally connect to REF pin and output has low impedance |  |  |  |  |  |

| 0                                         | 0           | χ(1) | Shutdownmode   | Amplifiers OFF and output has high impedance                                                 |  |  |  |  |  |

<sup>(1)</sup> X is used to denote a logic state of either 1 or 0.

NOTE: The default state for all logic pins is a logic one (1).

Figure 1. ±12 V Active Termination ADSL CO Line Driver Circuit (Synthesis Factor = 4; CF = 5.6)

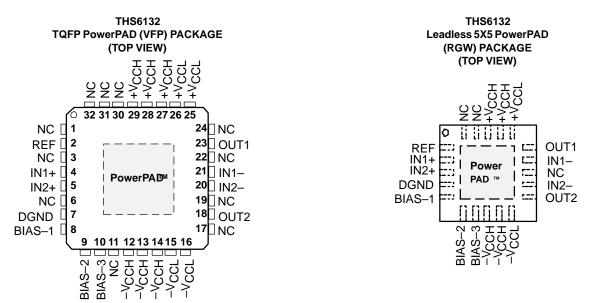

#### **PIN ASSIGNMENTS**

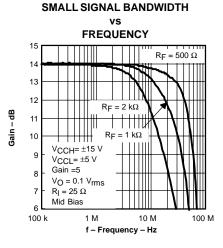

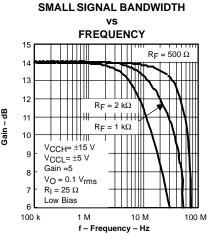

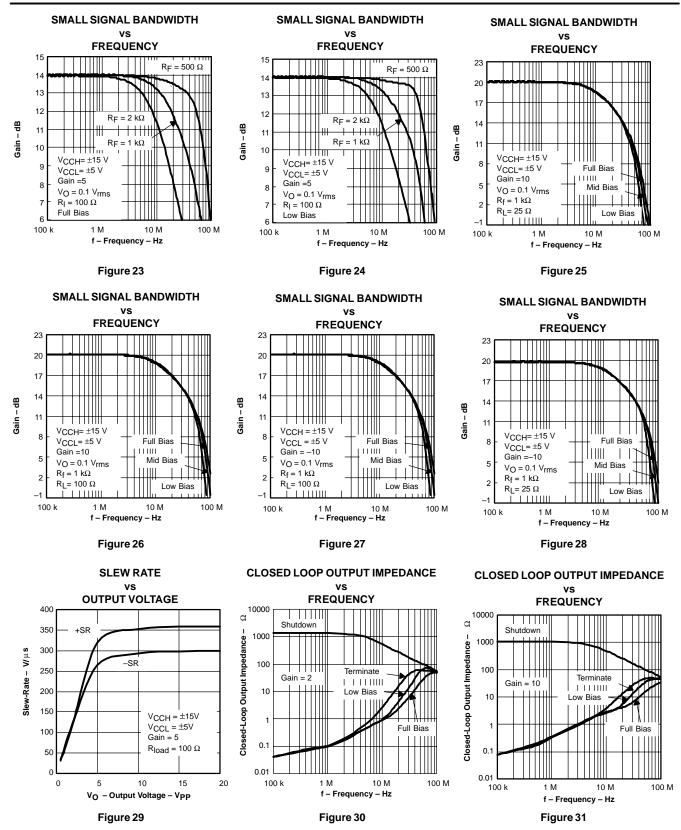

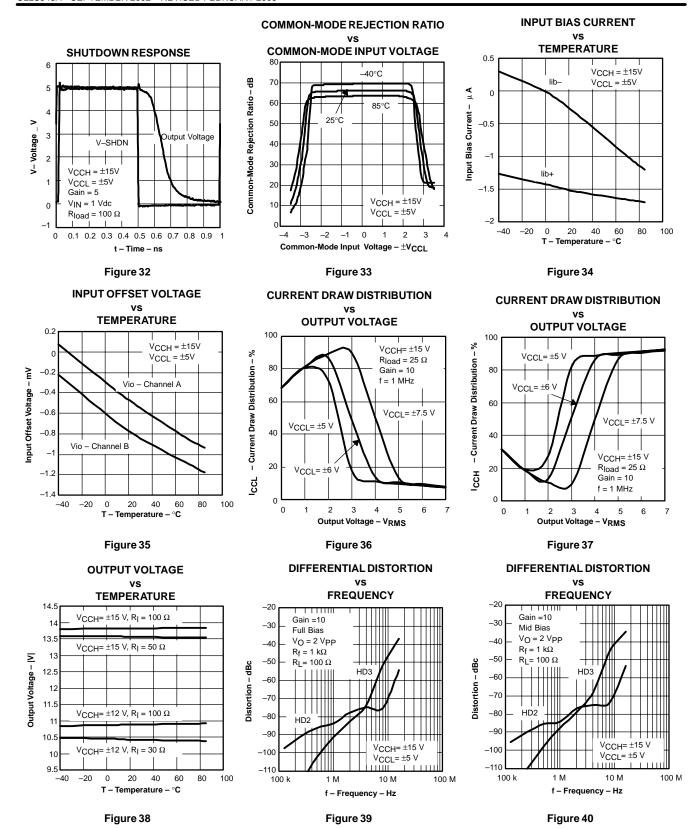

## TYPICAL CHARACTERISTICS

**Table of Graphs**

|                                 |                                | FIGURE     |

|---------------------------------|--------------------------------|------------|

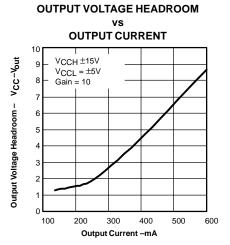

| Output voltage headroom         | vs Output current              | 2          |

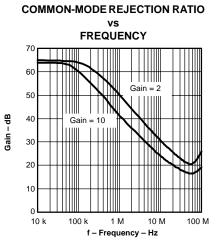

| Common-mode rejection ratio     | vs Frequency                   | 3          |

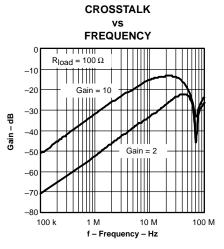

| Crosstalk                       | vs Frequency                   | 4          |

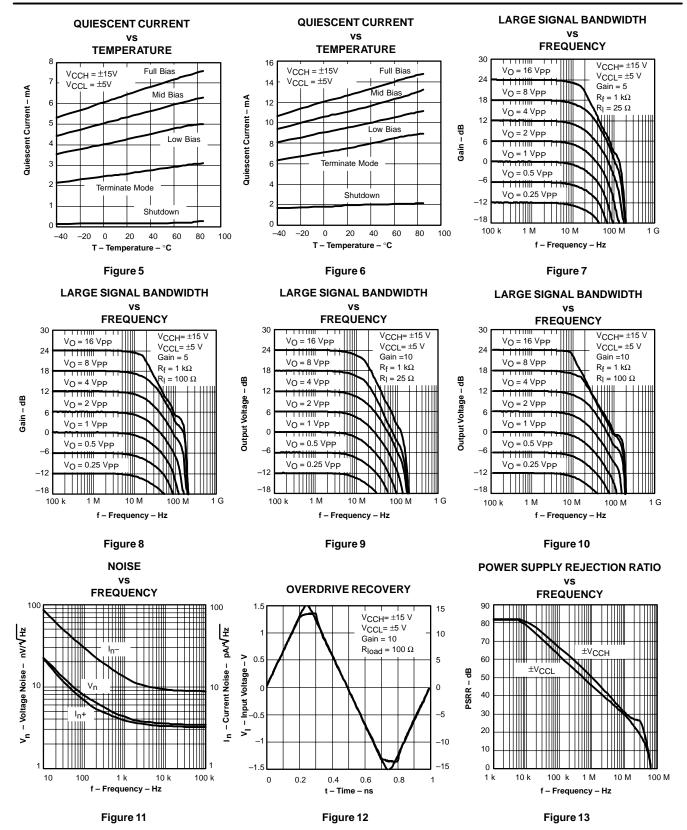

| Quiescent current               | vs Temperature                 | 5, 6       |

| Large signal bandwidth          | vs Frequency                   | 7 – 10     |

| Noise                           | vs Frequency                   | 11         |

| Overdrive recovery              |                                | 12         |

| Power supply rejection ratio    | vs Frequency                   | 13         |

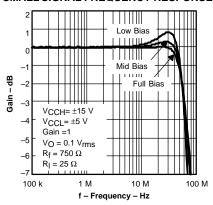

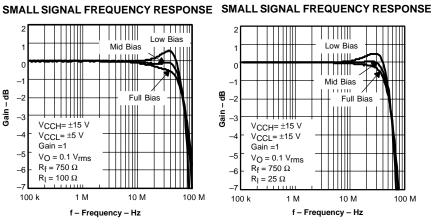

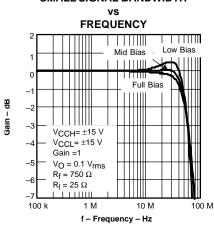

| Small signal frequency response |                                | 14, 15, 16 |

| Small signal bandwidth          | vs Frequency                   | 17 – 28    |

| Slew rate                       | vs Output voltage              | 29         |

| Closed-loop output impedance    | vs Frequency                   | 30, 31     |

| Shutdownresponse                |                                | 32         |

| Common-mode rejection ratio     | vs Common-mode input voltage   | 33         |

| Input bias current              | vs Temperature                 | 34         |

| Input offset voltage            | vs Temperature                 | 35         |

| Current draw distribution       | vs Output voltage              | 36, 37     |

| Output voltage                  | vs Temperature                 | 38         |

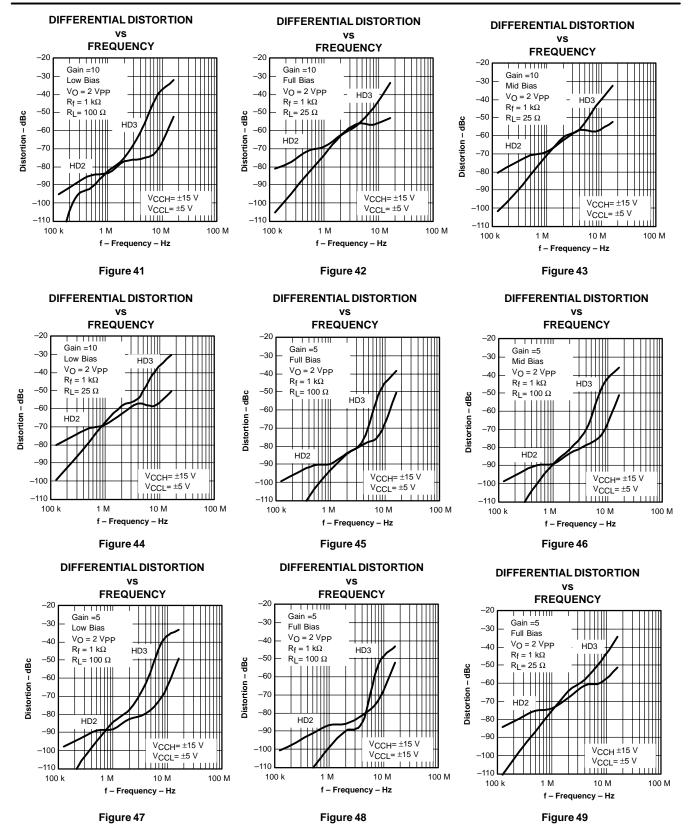

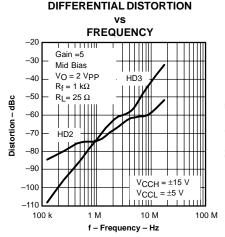

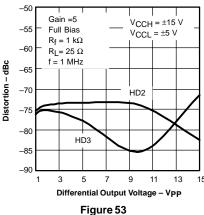

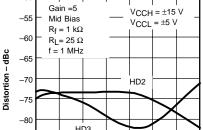

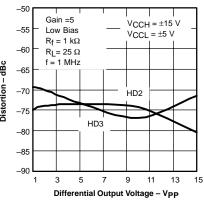

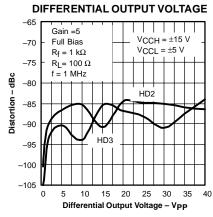

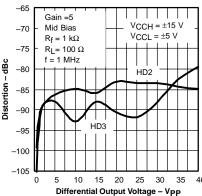

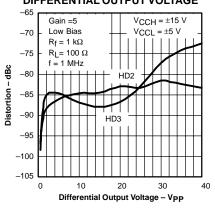

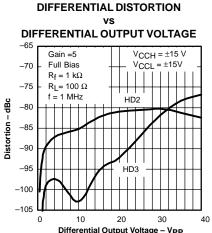

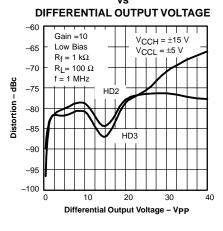

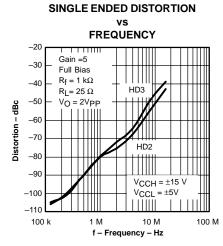

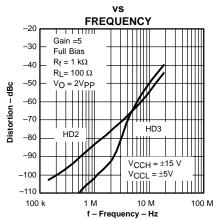

| Differential distortion         | vs Frequency                   | 39 – 52    |

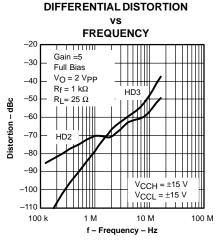

| Differential distortion         | vs Differential output voltage | 53 – 63    |

| Single ended distortion         | vs Frequency                   | 64, 65     |

Figure 2

Figure 3

Figure 4

#### **SMALL SIGNAL FREQUENCY RESPONSE**

Figure 14

Low Bias Mid Bias Full Bias Gain VCCH= ±15 V V<sub>CCL</sub>= ±5 V Gain =1  $V_O = 0.1 V_{rms}$  $R_f = 750 \Omega$ R<sub>I</sub> = 100 Ω 100 k 10 M 100 M f - Frequency - Hz

Figure 15

Figure 16 **SMALL SIGNAL BANDWIDTH**

**SMALL SIGNAL BANDWIDTH**

Figure 17

Figure 18

**FREQUENCY** Mid Bias Low Bias Full Bias 명 V<sub>CCH</sub>= ±15 V V<sub>CCL</sub>= ±15 V Gain =2  $V_O = 0.1 V_{rms}$  $R_f = 620 \Omega$  $R_{\parallel} = 25 \Omega$ 100 k 10 M 100 M f - Frequency - Hz

Figure 19

Figure 20

Figure 21

Figure 22

**FREQUENCY** -20Gain =5 -30 Low Bias V<sub>O</sub> = 2 V<sub>PP</sub> HD3 -40  $R_f = 1 k\Omega$ -50 R<sub>L</sub>= 25 Ω Distortion – dBc -60 -70 HD2 -80 -90 V<sub>CCH</sub> = ±15 V -100 V<sub>CCL</sub> = ±5 V -110 100 k 10 M 100 M f - Frequency - Hz

**DIFFERENTIAL DISTORTION**

Figure 50

Figure 51

**DIFFERENTIAL DISTORTION**

vs

**DIFFERENTIAL OUTPUT VOLTAGE**

-50

-85

\_90

Figure 52

#### **DIFFERENTIAL DISTORTION** vs **DIFFERENTIAL OUTPUT VOLTAGE**

Distortion -Differential Output Voltage - Vpp

**DIFFERENTIAL DISTORTION** vs

#### **DIFFERENTIAL OUTPUT VOLTAGE**

# **DIFFERENTIAL DISTORTION**

**DIFFERENTIAL DISTORTION DIFFERENTIAL OUTPUT VOLTAGE**

Figure 54

**DIFFERENTIAL DISTORTION** VS **DIFFERENTIAL OUTPUT VOLTAGE**

Figure 55

Figure 56

Figure 57

Figure 58

**DIFFERENTIAL DISTORTION**

Differential Output Voltage - Vpp

**DIFFERENTIAL OUTPUT VOLTAGE** -50 Gain =10 V<sub>CCL</sub> = ±15 V V<sub>CCL</sub> = ±5V Full Bias -55  $R_f = 1 k\Omega$ -60 R<sub>L</sub>= 25 Ω f = 1 MHz HD2 -65 Distortion -70 -75 -80 HD3 -85 -90 11 13 15 Differential Output Voltage - Vpp

**DIFFERENTIAL DISTORTION**

**DIFFERENTIAL OUTPUT VOLTAGE** -60 Gain =10  $V_{CCH} = \pm 15 \text{ V}$ Full Bias -65  $V_{CCL} = \pm 5V$  $R_f = 1 k\Omega$  $R_L$ = 100  $\Omega$ -70 f = 1 MHz – dBc -75 Distortion HD2 -80 -85 -90 -95 -100 20 10 30 0 40 Differential Output Voltage - Vpp

**DIFFERENTIAL DISTORTION** vs

Figure 59

**DIFFERENTIAL OUTPUT VOLTAGE** -60 Gain =10 V<sub>CCH</sub> = ±15 V Mid Bias -65  $V_{CCL} = \pm 5V$  $R_f = 1 k\Omega$ -70  $R_L$ = 100  $\Omega$ f = 1 MHz-75 HD2 Distortion -80 -85 -90 HD3 -95 -100 **L** 10 20 40 Differential Output Voltage - Vpp

Figure 62

**DIFFERENTIAL DISTORTION** VS

Figure 60

Figure 63

Figure 61

Figure 64

#### SINGLE ENDED DISTORTION

Figure 65

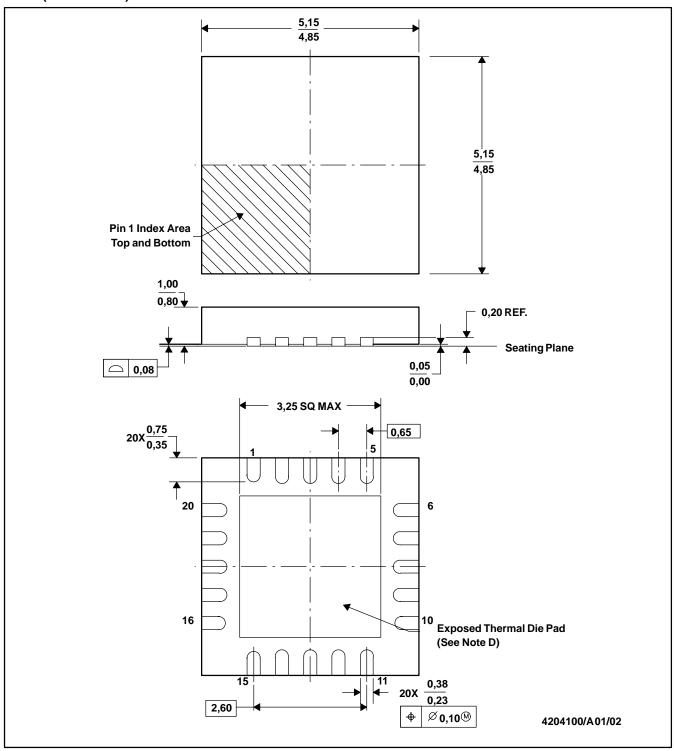

## **MECHANICAL DATA**

# RGW (S-PQFP-N20)

# **PLASTIC QUAD FLATPACK**

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads, (QFN) package configuration.

- D. The package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane.

- E. Falls within JEDEC M0-220.

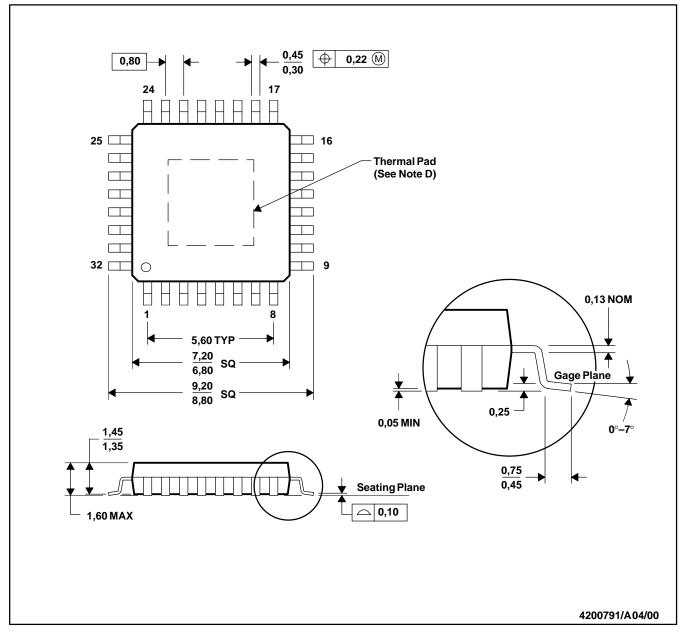

## **MECHANICAL DATA**

# VFP (S-PQFP-G32)

## **PowerPAD™ PLASTIC QUAD FLATPACK**

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MS-026

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated