## SOT-3 Device STM-1/STS-3/STS-3c Overhead Terminator TXC-03003B

**DATA SHEET**

### FEATURES I

- Transport (Section) and Line Overhead byte processing

- · Independent Path Overhead byte processing

- Transmit and receive pointer generation with respect to external clock and frame signals

- Line interface: byte-parallel data, clock and frame signals

- Terminal interface: byte-parallel data, clock, C1J1, SPE, parity bit and path overhead indication signals

- SDH/SONET alarm detection

- Alarm Indication Port (AIP) for path-protected ring applications

- VTAIS and Path AIS generation on alarms

- · Downstream fault indications inserted in E1 byte

- Performance monitoring: B1, B2 and B3 coding violations, FEBE and pointer justification counts

- · Microprocessor access:

- Pin selectable for Intel or Motorola interface

- Hardware/software interrupt capability

- Receive and transmit section and line overhead bytes available from on-chip RAM and via a serial I/O port

- Source timing mode: transmit side provides downstream device timing (optional V1 pulse)

- Data communication mode: for STM-1 VC-4/ STS-3c use

- Single +5 V, ±5 % power supply

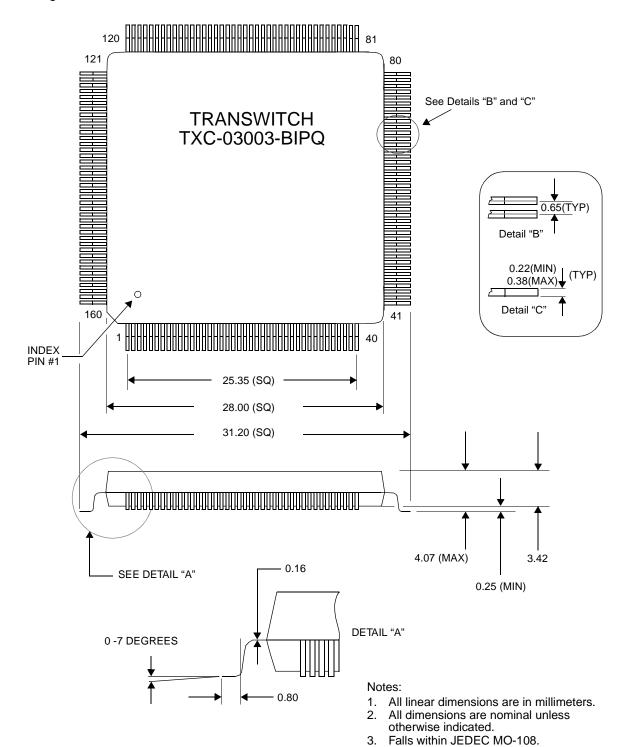

- 160-pin 28 x 28 mm plastic quad flat package

### **DESCRIPTION**

The SOT-3 SDH/SONET overhead terminator is a programmable device that performs section, line and path overhead processing for STM-1/STS-3/STS-3c signals. The SOT-3 device performs pointer generation (with internal pointer justification) with respect to external clock timing in both the transmit and receive directions. It automatically adjusts pointers to account for differences between the input clock and frame, and the reference clock and frame. All overhead bytes are provided in the SOT-3 memory map with access via a microprocessor port and a serial I/O port.

The SOT-3 device generates path AIS and sends downstream AIS information via the E1 bytes. It also provides a serial Alarm Indication Port for use in path-protected ring architectures. In the transmit direction, section and line overhead bytes may be multiplexed into the signal from either the memory map or from the external serial interface.

### **APPLICATIONS**

- Supports Telecom Bus and dual ring mode applications

- Add/drop multiplexer

- · Digital cross-connect

- · High speed data communication

U.S. Patents No. 4,967,405; 5,040,170; 5,141,529; 5,257,261, 5,265,096 and 5,331,641 U.S. and/or foreign patents issued or pending Copyright © 1998 TranSwitch Corporation TXC and TranSwitch are registered trademarks of TranSwitch Corporation

Document Number: TXC-03003B-MB Ed. 2, November 1998

## **TABLE OF CONTENTS**

| Section                                                    | Page |

|------------------------------------------------------------|------|

| List of Figures                                            | 3    |

| Block Diagram                                              | 5    |

| Block Diagram Description                                  | 5    |

| Pin Diagram                                                | 9    |

| Pin Descriptions                                           | 10   |

| Absolute Maximum Ratings and Environmental Limitations     | 21   |

| Thermal Characteristics                                    | 21   |

| Power Requirements                                         | 21   |

| Input, Output and Input/Output Parameters                  |      |

| Timing Characteristics                                     |      |

| Operation                                                  | 40   |

| Receive Transport Overhead Byte Processing                 | 40   |

| Receive Path Overhead Byte Processing                      | . 40 |

| Receive Retiming                                           |      |

| VTAIS and Path AIS Insertion at Receive Terminal Interface | . 41 |

| E1 Byte AIS Indication                                     | 44   |

| Pointer Tracking Interpretation                            | . 45 |

| Transmit Terminal Interface Operating Modes                | 47   |

| Bus Parity                                                 | . 48 |

| Transmit Retiming                                          | 48   |

| Transmit Transport (Section) Overhead Byte Processing      | 48   |

| Transmit Path Overhead Byte Processing                     | . 49 |

| Throughput Delay                                           | . 51 |

| Alarm Indication Port Serial Data Interface                | . 52 |

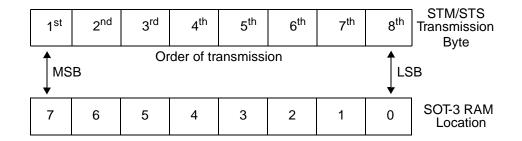

| Random Access Memory (RAM)                                 | . 53 |

| Performance Counters                                       | . 53 |

| Alarms And Interrupts                                      | . 54 |

| Memory Map For RAM Locations                               | 55   |

| Memory Map Descriptions                                    | 60   |

| Descriptions of Overhead in RAM                            | . 60 |

| Control Register Descriptions                              | . 82 |

| Status Register Descriptions                               | 103  |

| Interrupt Mask Register Descriptions                       | 109  |

| Performance Counter and K1-K2 Byte Register Descriptions   | 109  |

| Package Information                                        | 112  |

| Ordering Information                                       | 113  |

| Related Products                                           | 113  |

| Standards Documentation Sources                            | 114  |

| List of Data Sheet Changes                                 | 116  |

| Documentation Update Registration Form *                   | 121  |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

| Figure | <u>e</u>                                                                           | <b>Page</b> |

|--------|------------------------------------------------------------------------------------|-------------|

| 1      | SOT-3 TXC-03003B Block Diagram                                                     | 5           |

| 2      | SOT-3 TXC-03003B Pin Diagram                                                       | 9           |

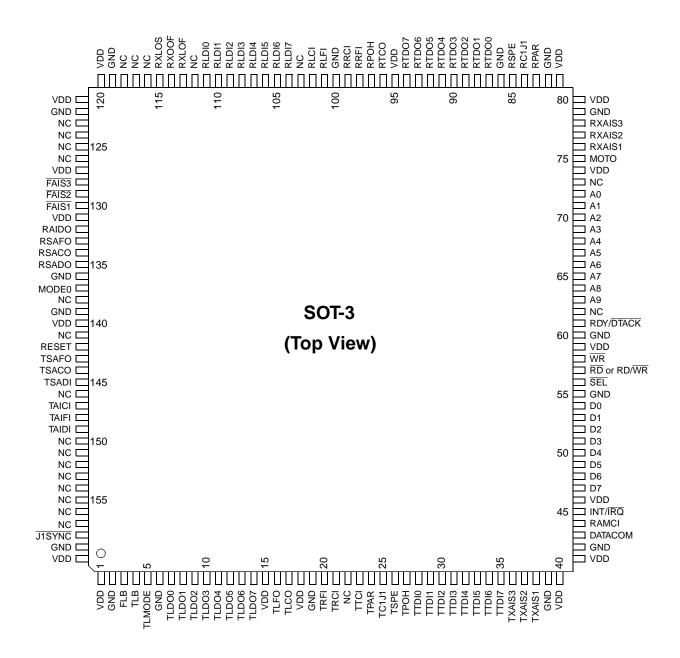

| 3      | Line Side Receive Timing                                                           | 25          |

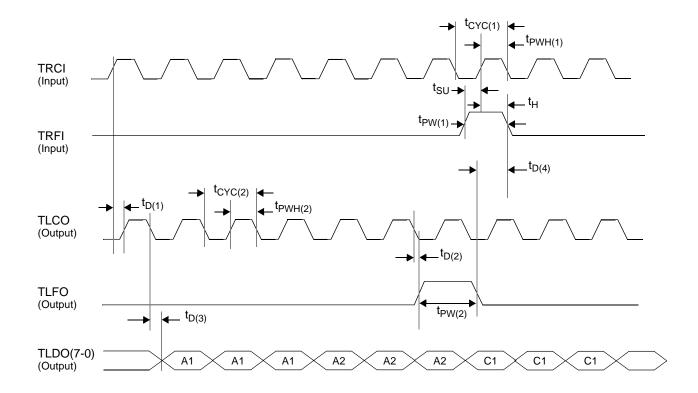

| 4      | Line Side Transmit Timing with TLMODE (Pin 5) Tied High                            | 26          |

| 5      | Line Side Transmit Timing with TLMODE (Pin 5) Tied Low                             | 27          |

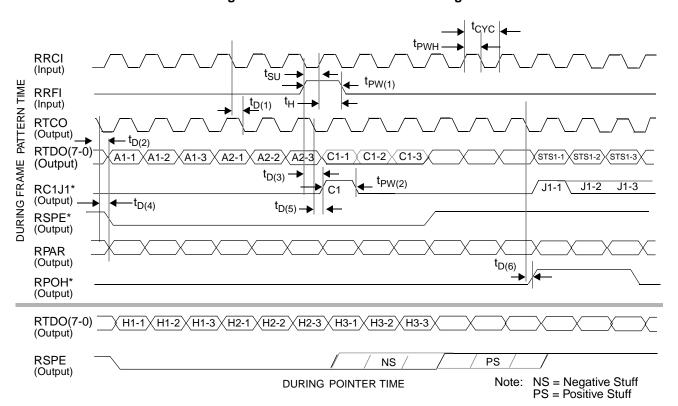

| 6      | Terminal Side Receive Timing                                                       | 28          |

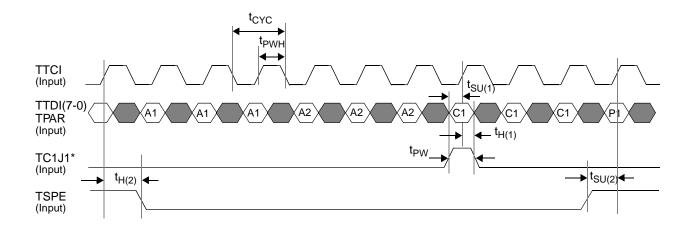

| 7      | Terminal Side Transmit Timing in Normal Mode                                       | 29          |

| 8      | Terminal Side Transmit Timing in Data Communication Mode                           | 30          |

| 9      | Terminal Side Transmit Timing in Source Timing Mode                                | 31          |

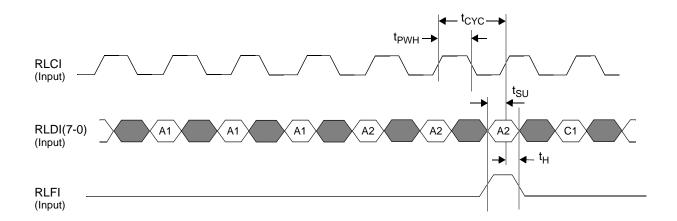

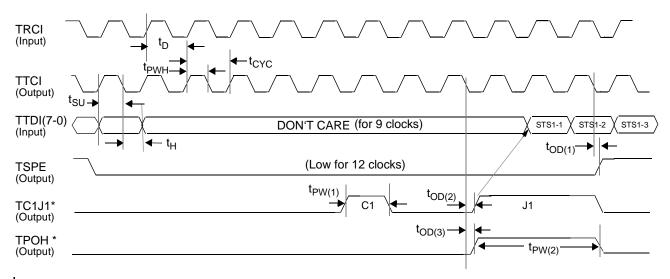

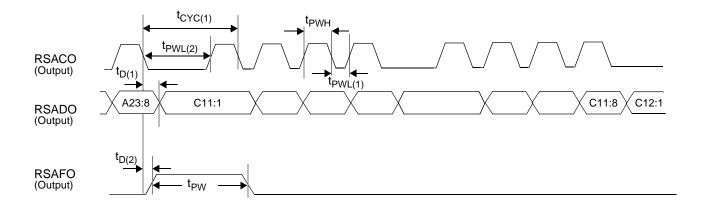

| 10     | TOH Serial Access Port Receive Timing                                              | 32          |

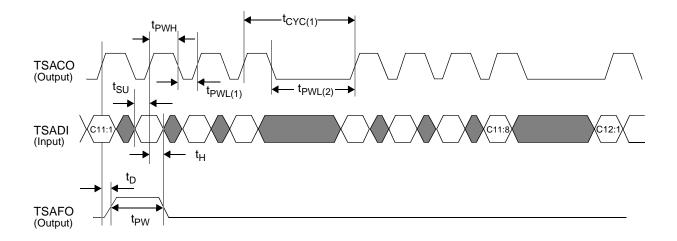

| 11     | TOH Serial Access Port Transmit Timing                                             | 33          |

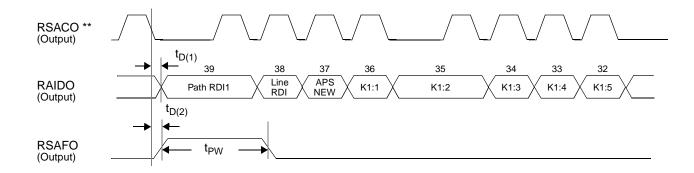

| 12     | Alarm Indication Port Receive Timing                                               | 34          |

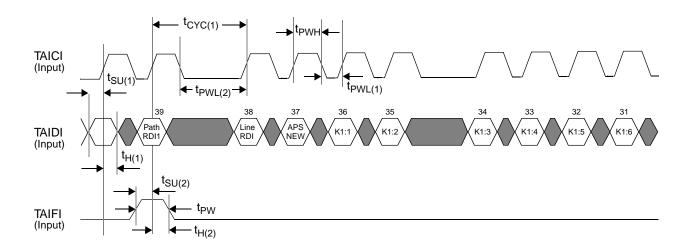

| 13     | Alarm Indication Port Transmit Timing                                              | 35          |

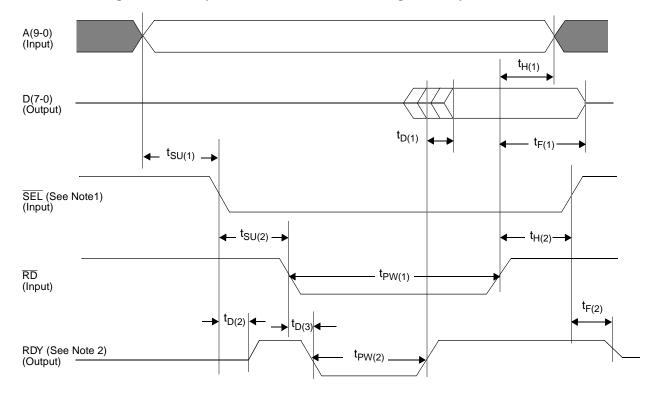

| 14     | Microprocessor Interface Bus Timing: Read Cycle - Intel Mode                       | 36          |

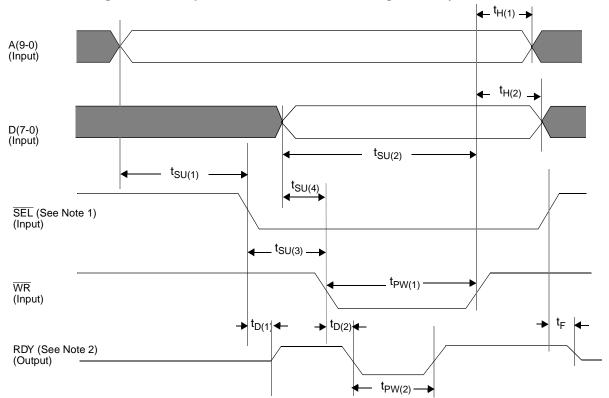

| 15     | Microprocessor Interface Bus Timing: Write Cycle - Intel Mode                      | 37          |

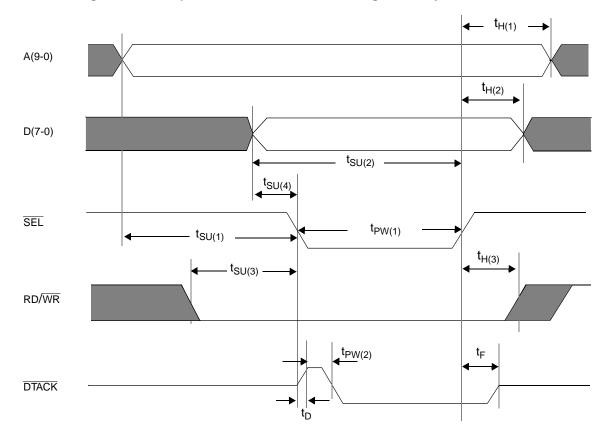

| 16     | Microprocessor Interface Bus Timing: Read Cycle - Motorola Mode                    | 38          |

| 17     | Microprocessor Interface Bus Timing: Write Cycle - Motorola Mode                   | 39          |

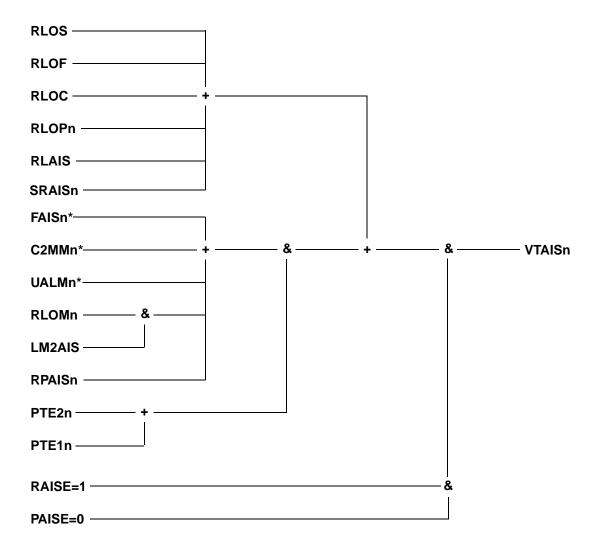

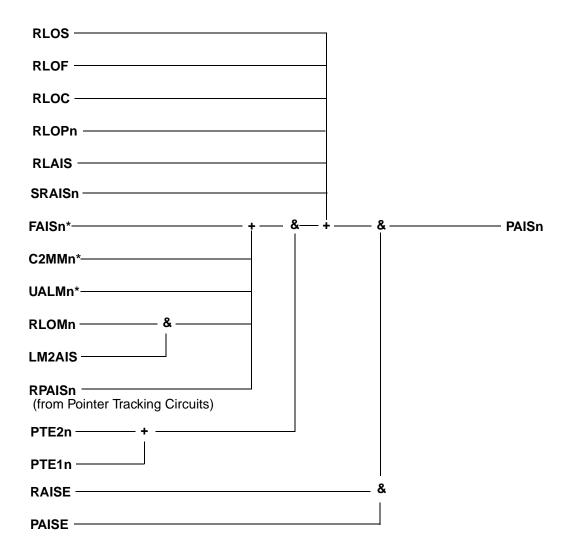

| 18     | Logic Diagram for Generation of VTAISn                                             | 42          |

| 19     | Logic Diagram for Generation of PAISn                                              | 43          |

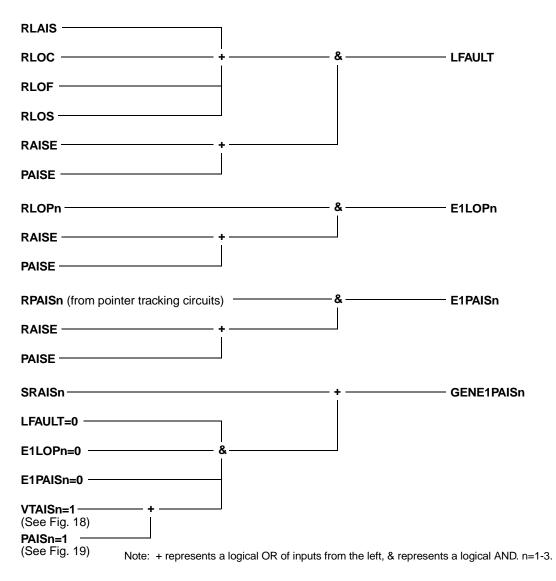

| 20     | Format of E1n Byte AIS Indication and Logic Diagram for its Content                | 44          |

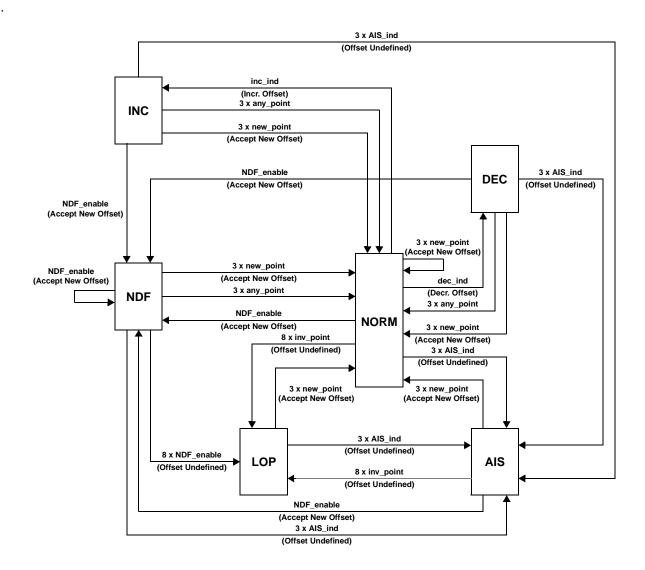

| 21     | STS Pointer Tracking State Machine                                                 | 46          |

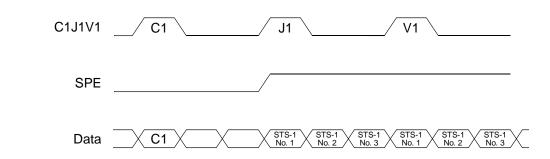

| 22     | Transmit Terminal Interface C1J1V1 Signal Format                                   | 47          |

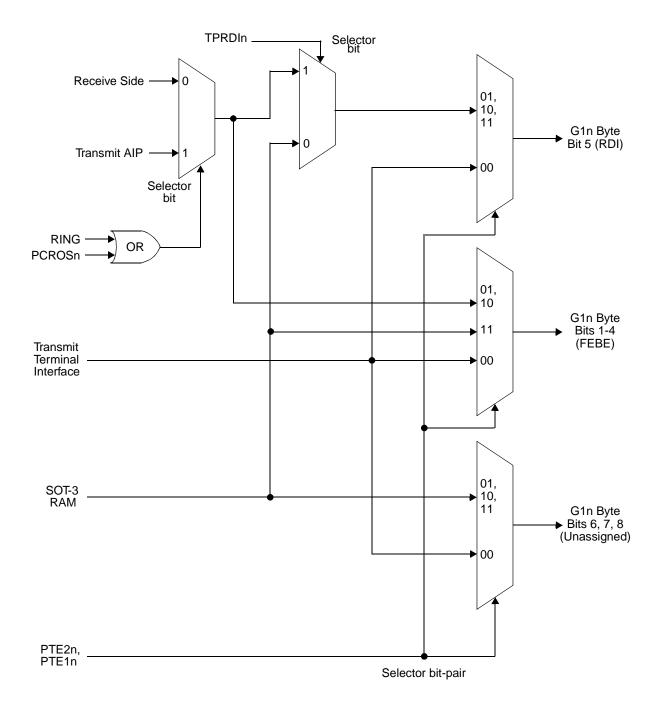

| 23     | G1 Byte Multiplex for Transmit Line Output                                         | 50          |

| 24     | Sourcing of Line Side Transmit Path Overhead Bytes                                 | 51          |

| 25     | Format of Serial Data Stream on Receive Alarm Indication Port Data Out (RAIDO) Pin | 52          |

| 26     | SOT-3 TXC-03003B 160-Pin Plastic Quad Flat Package                                 | 112         |

This page has been intentionally left blank.

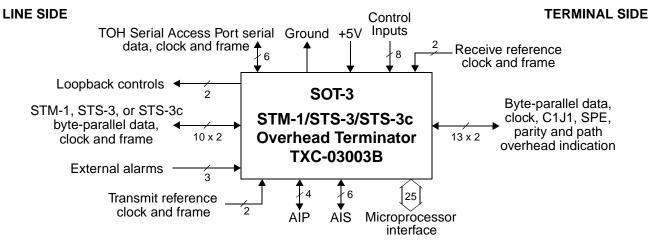

### **BLOCK DIAGRAM**

Figure 1. SOT-3 TXC-03003B Block Diagram

### **BLOCK DIAGRAM DESCRIPTION**

A simplified block diagram of the SOT-3 device is shown in Figure 1. Each functional group of blocks in this diagram is described briefly in the following subsections. Supplemental detail is provided in the Operation section, which has the same order of presentation as this section, i.e., receive direction, transmit direction (including the bidirectional topics of parity and throughput delay) and auxiliary functions. The Pin Descriptions section provides information on the pins associated with each function, in the same order, with controls grouped at the end. Timing diagrams are provided in Figures 3 through 17.

### RECEIVE DIRECTION

#### **Receive Line Interface Block**

The Receive Line Interface block terminates the receive line signals, which are derived from the line signal in an external STM-1/STS-3 155 Mbit/s framer device, such as the TranSwitch SYN155 Synchronizer VLSI device (TXC-02301B). The external framer device performs the functions of scrambling/descrambling, B1 byte BIP-8 generation and checking, and serial to byte conversion of the data stream. Byte-parallel data (RLDI(7-0)) and a framing pulse (RLFI) are clocked into the SOT-3 device from the framer on rising edges of a 19.44 MHz

clock (RLCI), as shown in Figure 3. Pin RLDI7 carries the most significant bit (MSB) of the data byte, which corresponds to bit 1 in a SDH/SONET serial bit stream. In addition, the SOT-3 device provides external alarm input pins for Receive Out Of Frame (RXOOF), Receive Loss Of Frame (RXLOF) and Receive Loss Of Signal (RXLOS) alarms. These external receive alarm indications are stored as status bits in the SOT-3 RAM block, from which they may be read via the Microprocessor Interface block by a read cycle of an external microprocessor. The SOT-3 device provides two output pins (FLB and TLB), driven by corresponding control bits in RAM, which can be used to invoke Facility Loopback and Terminal Loopback in the external framer device.

### Receive Overhead Demultiplexer Block

The Receive Overhead Demultiplexer block writes the 81 STM-1 Section Overhead bytes or the 81 STS-3/STS-3c Transport Overhead bytes to the RAM block, where they are available for microprocessor access. The bytes are also provided at the output of the Transport Overhead Byte (TOH) Serial Access Port block for external processing. The Receive Overhead Demultiplexer block also performs the TOH processing of the B2 byte BIP-8 parity, line FEBE checking, K1 and K2 byte checking for an inconsistent APS and for a new APS indication, and detection of line RDI and line AIS prior to pointer tracking. A pointer tracking state machine interprets the incoming pointer bytes H1 and H2 to determine the location of the J1 Path Overhead (POH) byte. Pointer tracking is performed according to the latest ETSI and ANSI standards, with loss of pointer and AIS alarms reported for the STM-1 AU-4/STS-3c or for the three STS-3:STS-1 signals. Three sets of three eight-bit counters are provided to count pointer increments, decrements and New Data Flag (NDF) occurrences.

After pointer tracking, the Receive Overhead Demultiplexer block writes the Path Overhead bytes into RAM locations, and performs B3 BIP-8 parity checking and counts the number of detected bit or block errors. An H4 multiframe detector is provided with an optional V1 pulse generator. Control bits also permit the H4 byte to pass through the receiver transparently. A circuit is provided for C2 Mismatch and Unequipped detection, with alarm indications. The G1 byte is checked for an RDI status, and the number of FEBE errors is counted.

### **Receive Retiming Block**

The Receive Retiming block provides pointer justification for the STM-1 VC-4/STS-3c signal or for each of the three STS-1 signals. The VC-4 or STS-1 signals, which consist of the POH bytes and payload, are justified to two external reference signals, which are a framing pulse (RRFI) and a clock (RRCI). The VC-4 consists of 2349 bytes (261 columns times 9 rows). Each of the three STS-1 signals in the STS-3 signal consists of 783 bytes (87 columns times 9 rows).

### **Receive Terminal Output Block**

The Receive Terminal Output block provides a receive output interface for byte-parallel data (RTDO(7-0)), a 19.44 MHz clock signal (RTCO), a composite C1J1 signal (RC1J1) with an optional V1 signal, an SPE signal (RSPE) that identifies the POH byte and payload byte times, a path overhead indicator signal (RPOH), and an odd or even parity indication bit (RPAR), as shown in Figure 6. Parity is calculated over the data (RTDO(7-0)), the C1J1 (RC1J1) and the SPE (RSPE) signals only. The RTDO7 bit is the MSB and represents bit 1 in a SDH/SONET serial bit stream. The C1J1 signal is used in conjunction with the SPE signal to determine the location of the various bytes in the SDH/SONET signal. A high pulse on the RC1J1 pin indicates a C1 pulse when the RSPE pin is low, and a J1 (or V1) pulse when RSPE is high, as illustrated in Figure 22. The C1 pulse identifies the location of the first C1 byte in the SDH/SONET frame. A single J1 pulse, one clock cycle wide, identifies the starting location of the J1 byte in the Path Overhead bytes in the VC-4 format. Three J1 pulses are provided for the STS-3 format, each identifying the starting location of the J1 byte in one of the three STS-1 signals.

The optional V1 pulse is used to determine the starting location of the V1 bytes in asynchronous mapping formats such as VT1.5. For STM-1 VC-4 operation, an optional single V1 pulse, one clock cycle wide, will occur once every four frames following the J1 pulse. For STS-3 operation, three V1 pulses may be present every four frames. Each V1 pulse will occur on the third clock cycle after the corresponding J1 pulse, when the SPE signal is high. For example, in a VC-4 signal carrying TUG-3 signals, the J1 pulse identifies the J1 byte location (defined as the starting point for the VC-4) in the POH bytes. In the next column (first clock cycle), all the rows

are assigned as fixed stuff. Similarly, in the next column (second clock cycle), all the rows are assigned as fixed stuff. The next column (third clock cycle), which carries a Null Pointer Indication, defines the start of the TUG-3 designated as "A". This column is where the V1 pulse occurs every four frames. However, the actual V1 byte occurs six clock cycles after the V1 pulse.

Receive side Alarm Indication Signals are provided at the terminal side outputs, as shown in Figures 18-20.

### TRANSMIT DIRECTION

### **Transmit Terminal Input Block**

In the transmit direction, the Transmit Terminal Input block, when operating in the normal mode, provides an input interface for byte-parallel data (TTDI(7-0)), a 19.44 MHz clock signal (TTCI), a composite C1J1 signal (TC1J1) with an optional V1 input signal, an SPE signal (TSPE) that identifies the POH byte and payload byte times, and an odd or even parity indication (TPAR). Internal parity is calculated over the data, C1J1 and SPE signals, or for the data byte only, with the sense (odd or even) of the calculation determined by the value of a bit in a control register. The result of this parity calculation is compared with the input signal present on the parity pin (TPAR). Other than providing an error indication, the SOT-3 device takes no action when a parity error is detected. The TTDI7 bit is the MSB and represents bit 1, the first bit transmitted in a SDH/SONET serial bit stream. The TC1J1 signal is used in conjunction with the TSPE signal to determine the location of the various parts of the SDH/SONET signal (see Figures 7 and 22).

In the data communication (datacom) and source timing modes, the 19.44 MHz clock signal (TTCI), the composite C1J1 signal (TC1J1), and the SPE signal (TSPE), become output signals. In the data communication mode, which is intended for STM-1 VC-4/STS-3c operation, the TSPE output signal, with the MODE0 pin high, is active for the payload byte times only (260 bytes per row). The TSPE signal is low during the Transport Overhead byte times and the single Path Overhead byte time. With the MODE0 pin low, the TSPE is high for the 258 payload times only, and low for the nine TOH byte times as well as the POH byte time and the two byte time slots immediately following. In addition, a Path Overhead byte indication signal (TPOH) is provided for identifying the POH byte times (see Figure 8). In the source timing mode, the TSPE output signal is active for the Path Overhead and payload byte times (261 bytes per row). The TSPE signal is low during the Transport Overhead byte times. An internal H4 multiframe generator provides an optional V1 pulse for the C1J1 (TC1J1) output signal (see Figures 9 and 22). The V1 pulse is synchronous with the transmitted H4 byte for the STM-1 VC-4 format, or there may be up to three V1 pulses, one for each of the three STS-1 signals. The optional V1 pulse is used to determine the starting location of the V1 byte in asynchronous mapping formats such as VT1.5 for multiple VT add/drop devices.

#### **Transmit Retiming Block**

The Transmit Retiming block provides pointer justification for the STM-1 VC-4/STS-3c signal or for each of the three STS3:STS-1 signals. The VC-4 or STS-1 signals, which consist of the POH bytes and payload, are justified to two external reference signals, a framing pulse (TRFI) and a clock (TRCI). The VC-4 consists of 2349 bytes (261 columns times 9 rows). Each of the three STS-1 signals in the STS-3 signal consists of 783 bytes (87 columns times 9 rows).

#### **Transmit Overhead Multiplexer Block**

The Transmit Overhead Multiplexer block performs the multiplexing of the Transport Overhead (TOH) and Path Overhead (POH) bytes into the SDH/SONET signal. The TOH bytes are inserted from RAM locations, which may be written either by the external microprocessor or from the TOH Serial Access Port. Control bits select the source of these bytes, as shown in Figures 24 and 25. Path overhead bytes may accompany the payload bytes, or they may be multiplexed into the transmitted signals from microprocessor-written RAM locations. The Transmit Overhead Multiplexer block also controls the state of the Path RDI alarm (bit 5 in the G1 byte) and Line RDI (bits 6-8 of the K2 byte), and the generation of Path and Line AIS and FEBE signals.

### **Transmit Line Output Block**

The Transmit Line Output block provides transmit line signals for an external STM-1/STS-3 155 Mbit/s framer device, such as the TranSwitch SYN155 Synchronizer VLSI Device (TXC-02301B). The interface consists of a byte-parallel data output signal (TLDO(7-0)), a clock signal (TLCO), and a framing pulse (TLFO). The signals are derived from the reference clock (TRCI) and reference framing pulse (TRFI) input signals. The framing pulse may be active high or low, depending upon the state of the TLMODE pin. Data and the framing pulse are clocked out on falling edges of the clock TLCO when TLMODE is high, and on rising edges when TLMODE is low, as shown in Figures 4 and 5. TLDO7 is the MSB and represents bit 1, the first bit transmitted in a SDH/SONET serial bit stream.

#### **AUXILIARY FUNCTIONS**

### **Transport Overhead Byte Serial Access Port Block**

The Transport Overhead Byte (TOH) Serial Access Port block provides serial receive and transmit interfaces for the 81 Line Overhead and Section Overhead bytes in the SDH/SONET format, as shown in Figures 10 and 11. The receive interface consists of serial data (RSADO), a clock signal (RSACO), and a framing pulse (RSAFO). Data is clocked out on falling edges of RSACO. The framing pulse RSAFO identifies the location of bit 1 (MSB) of the first C1 byte. The transmit interface consists of a serial data input signal (TSADI), an output clock signal (TSACO), and framing pulse (TSAFO). Data is clocked in on rising edges of TSACO. The framing signal TSAFO identifies the starting location of bit 1 in the C1 byte.

### **Alarm Indication Port Block**

The SOT-3 device supports a ring architecture using the Alarm Indication Port (AIP) block. The Alarm Indication Port receive output consists of serial data (RAIDO) and the receive clock and framing outputs of the TOH Serial Access Port block (RSACO and RSAFO), as shown in Figure 12. Alarm information to be used by the mate SOT-3 device in a ring architecture is clocked out on falling edges of the clock. Only the first 40 of the 81 RSACO clock cycles are used by the AIP. The serial data format consists of the corresponding 40 bits, numbered 39 through 0. Bit 39 is the MSB and is the first bit transmitted at the interface. The format conveys line and path FEBE information, line and path RDI alarm information, APS information, and the debounced K1 and K2 bytes, as shown in Figure 25.

The receive interface output signals, data (RAIDO), clock (RSACO) and framing (RSAFO), are connected to the transmit interface of the Alarm Indication Port of the mate SOT-3 device. The transmit interface consists of a serial data input signal (TAIDI), clock input signal (TAICI), and input framing signal (TAIFI). Data and the framing pulse are clocked in on rising edges of the clock, as shown in Figure 13.

### Microprocessor Interface and RAM Blocks

The Microprocessor Interface block provides support of either an Intel-compatible or a Motorola-compatible formatted microprocessor bus interface, selectable by the MOTO control input pin. The memory of the SOT-3 device has 1024 8-bit register locations (addresses 000H through 3FFH). A memory map and a description of each location are provided in later sections of this Data Sheet.

The microprocessor interface consists of a 10-bit address input bus, an 8-bit bidirectional data bus, and various control and status pins, plus a RAM clock (RAMCI) input for operating the RAM. Read and write cycle timing for the Intel and Motorola interfaces is shown in Figures 14 -17. In addition, interrupt capability is provided by both a hardware interrupt (INT/IRQ) pin and a software interrupt status register in memory. Each of the alarms in the SOT-3 device has one unlatched and one latched status bit in RAM associated with it, and a mask bit for disabling the software interrupt. The mask bit must be set to zero to disable the interrupt for the associated alarm. The latched status bits are located in latched registers, which latch on a positive alarm level and clear automatically when they are read, although the latched bits are maintained in the set condition for alarms which persist through the read cycle.

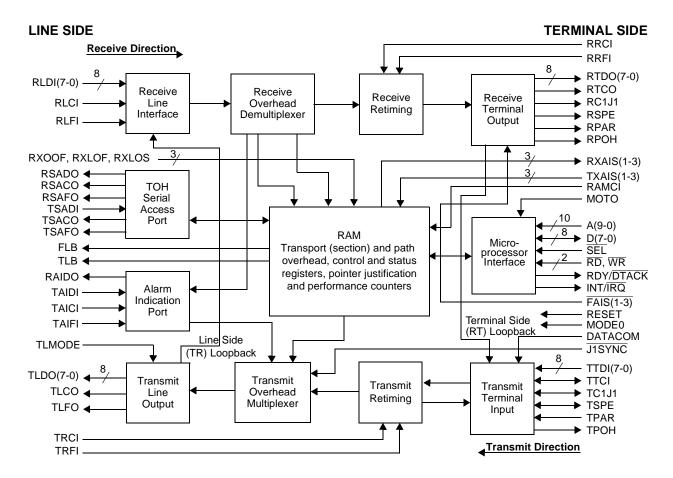

### **PIN DIAGRAM**

Figure 2. SOT-3 TXC-03003B Pin Diagram

# **PIN DESCRIPTIONS**

# POWER SUPPLY, GROUND AND NO CONNECT

| Symbol | Pin No.                                                              | I/O/P * | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                    |

|--------|----------------------------------------------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | 1,15,18,40,41,46,59,<br>74,80,81,95,120,121,<br>127,131,140,160      | Р       |      | <b>VDD:</b> + 5 volt power supply, $\pm$ 5%. Nominal high level for signals.                                                                                                                                                                                                                                                                                                     |

| GND    | 2,6,19,39,42,55,60,<br>79,82,86,100,119,<br>122,136,139,159          | Р       |      | <b>Ground:</b> Zero volts reference. Nominal low level for signals.                                                                                                                                                                                                                                                                                                              |

| NC     | 22,62,73,103,<br>112,116-118,<br>123-126,<br>138,141,146,<br>150-157 |         |      | No Connect: NC pins are not to be connected, not even to another NC pin, but must be left floating. Connection of these pins may impair performance or cause damage to the device. (NC pins may have internal connections within the device. They may also be assigned functions in future versions of the device such that a connection would prevent backwards compatibility.) |

<sup>\*</sup> Note: I = Input; O = Output; P = Power

## RECEIVE LINE SIDE INTERFACE

| Symbol    | Pin No. | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLFI      | 101     | I     | CMOS   | <b>Receive Line Frame In:</b> An active high framing pulse that occurs at the time of the third A2 byte of the STM-1/STS-3/STS-3c received data signal on RLDI.                                                                                                                                                                                                     |

| RLCI      | 102     | I     | CMOS   | Receive Line Clock In: This input clock has a nominal frequency of 19.44 MHz. Data (RLDI) and the framing signal (RLFI) are clocked in on the rising edges of this clock.                                                                                                                                                                                           |

| RLDI(7-0) | 104-111 | I     | CMOS   | Receive Line Data In: STM-1/STS-3/STS-3c byte-parallel data. The high level corresponds to logic 1. RLDI7 is defined as the most significant bit and the first bit received in the SDH/SONET format.                                                                                                                                                                |

| RXLOF     | 113     | I     | TTL    | Receive Loss Of Frame In: An external active high signal received from the SYN155 device or other line interface circuit that indicates a loss of frame alarm. The status of this alarm is conditionally recorded in status bit RLOF of the SOT-3 RAM.                                                                                                              |

| RXOOF     | 114     | I     | TTL    | Receive Out Of Frame In: An external active high signal received from the SYN155 device or other line interface circuit that indicates an out of frame alarm. The status of this alarm is conditionally recorded in status bit ROOF of the SOT-3 RAM.                                                                                                               |

| RXLOS     | 115     | I     | TTL    | Receive Loss Of Signal In: An external active high signal received from the SYN155 device or other line interface circuit that indicates a loss of signal. This signal is or-gated with the output of the internal SOT-3 circuit that detects loss of data input transitions to provide an alarm indication, which is recorded in status bit RLOS of the SOT-3 RAM. |

<sup>\*</sup> See Input, Output and I/O Parameters section below for Type Definitions.

## **RECEIVE REFERENCE TIMING**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                     |

|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRFI   | 98      | I     | CMOS | Receive Reference Frame In: An optional active high framing pulse reference, one RRCI cycle wide, that occurs every 125 microseconds. It can be used by the SOT-3 device to locate the receive terminal side frame timing. If it is not used, this pin must be set low. When it is not used, the pointer value will be arbitrary. |

| RRCI   | 99      | I     | CMOS | Receive Reference Clock In: A required clock input that has a nominal frequency of 19.44 MHz. Used for receive retiming, and for sourcing the receive terminal side output signals. The rising edge of RRCI is used for clocking in RRFI.                                                                                         |

## RECEIVE TERMINAL SIDE INTERFACE

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|---------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPAR   | 83      | 0     | CMOS2mA | Receive Terminal Parity: Parity status bit that is calculated over the receive terminal side data RTDO(7-0), RSPE, and RC1J1 signals, for each RTCO clock cycle. Setting control bit TPLEV to 1 (0) selects even (odd) parity.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RC1J1  | 84      | 0     | CMOS2mA | Receive Terminal C1, J1 (and optional V1) Indications: A composite synchronization signal which contains active high pulses in the location of the first C1 byte in the transport overhead and in the location(s) of the J1 byte(s) within the payload. The receive SPE indication (RSPE) is low during C1 and high during J1. For STM-1/STS-3c signals, there is one J1 pulse. For STS-3 signals, there are three J1 pulses, one for each STS-1. One or more V1 pulses may be present for asynchronous VT/TU mappings, and may be used in place of the H4 byte multiframe indication to determine the location of the V1 byte(s). Refer to Figure 22. |

| RSPE   | 85      | 0     | CMOS2mA | Receive Terminal SPE Indication: RSPE is active high during STM-1 VC-4/STS-3c and STS-3:STS-1 SPE byte times (payload plus POH bytes, 261 byte times per subframe). This signal is low during the time that corresponds to the STM-1 section overhead and AU-4 pointer bytes and the STS-3 transport overhead bytes (nine byte times per subframe).                                                                                                                                                                                                                                                                                                    |

| Symbol    | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTDO(7-0) | 94-87   | 0     | CMOS2mA | Receive Terminal Data Out: Byte-parallel data output for the STM-1 AU-4/STS-3c and STS-3 frames. Data is clocked out on the falling edge of the Receive Terminal Clock Out (RTCO). Data bytes are present for the A1, A2, three E1s, three H1s and H2s, H4 during VTAIS/TUAIS, and 261 STM-1 VC-4 or STS-3/STS-3c SPE byte times. During other byte times, the data bytes are set equal to zero. The high level corresponds to logic 1. RTDO7 is defined as the most significant bit and is the first bit received. |

| RTCO      | 96      | 0     | CMOS2mA | Receive Terminal Clock Out: Output clock, derived from RRCI, that has a nominal frequency of 19.44 MHz. Its falling edges are used for clocking out the byte-parallel data after retiming, and the RC1J1, RSPE, and RPAR signals.                                                                                                                                                                                                                                                                                   |

| RPOH      | 97      | 0     | CMOS2mA | Receive Terminal Path Overhead Bytes Indication: RPOH is high during STM-1 VC-4/STS-3c and STS-3 path overhead byte times. For STM-1/STS-3c signals, RPOH will be high for one byte per subframe. For STS-3 signals, RPOH will be high for three bytes per subframe, one for each STS-1. RPOH is low at other times.                                                                                                                                                                                                |

## TRANSMIT TERMINAL SIDE INTERFACE

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TTCI   | 23      | I/O   | CMOS2mA | Transmit Terminal Clock In: Transmit STM-1/STS-3 byte rate clock that has a nominal frequency of 19.44 MHz. In normal operation, byte-parallel data TTDI(7-0) and the TPAR, TC1J1 and TSPE input signals are clocked into the SOT-3 device on the rising edges of this clock. In the data communication and source timing modes, this clock becomes an output clock and is used for sourcing data (TTDI) and parity (TPAR) into the SOT-3 device on its falling edges, which are also used for clocking out TC1J1, TSPE and TPOH.                                                                                                                                     |

| TPAR   | 24      | I     | CMOS    | Transmit Terminal Parity Input: Parity input bit in which even (or odd) parity has been calculated over the transmit data byte (TTDI), TSPE, and TC1J1 signals in combination (or over the data byte alone) for each TTCI clock cycle. The SOT-3 device may be set up to compare this input value with a corresponding internally generated value. Even (odd) parity is calculated if control bit TPLEV is set to 1 (0). Parity is calculated for the 3-signal combination (data only) if control bit PDAT is set to 0 (1). If the comparison does not match, the BERR alarm bit is set. The TPAR input is ignored in the data communication and source timing modes. |

| Symbol    | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|---------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TC1J1     | 25      | I/O   | TTL2mA  | Transmit Terminal C1, J1 (and optional V1) Indications: In the normal mode, this is an input synchronization signal which contains active high pulses in the location of the first C1 byte in the transport overhead and in the location(s) of the J1 byte(s) within the payload. The transmit SPE indication (TSPE) must be low during C1 and high during J1. For STM-1/STS-3c signals, there is one J1 pulse. For STS-3 signals, there are three J1 pulses, one for each STS-1. One or more V1 pulses may be present for asynchronous VT/TU mappings, to determine the starting location of the V1 byte(s). In the data communication and source timing modes, this signal becomes an output.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TSPE      | 26      | I/O   | TTL2mA  | Transmit Terminal SPE Indication: In the normal mode, TSPE is an active high input signal that occurs during the STM-1 VC-4/STS-3c or STS-3:STS-1 SPE byte times (261 byte times per row.) It is low during the time that corresponds to the STM-1 section overhead and AU pointer bytes and the STS-3/STS-3c transport overhead bytes (nine byte times per row).  In the source timing and data communication modes, when the MODE0 pin is tied low, this signal becomes an output. In the data communication mode, which is intended for STM-1 VC-4/STS-3c operation, when MODE0 is tied high, the TSPE pin is low for the first 10 byte times per "row" of each STM-1/STS-3c frame, and high for the remaining 260 byte time slots of the row. When MODE0 is tied low, the TSPE signal is low for the first 12 byte time slots per "row" of the STM-1/STS-3c frame, and high for the remaining 258 byte time slots of the row. In the source timing mode of operation, the TSPE signal is low for the first nine byte time slots of each "row" of the frame, and high for the remaining 261 byte time slots of the frame. |

| ТРОН      | 27      | 0     | CMOS2mA | Transmit Terminal Path Overhead Bytes Indication: This signal is high during STM-1 VC-4/STS-3c path overhead byte times in the source timing and data communication modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TTDI(7-0) | 35-28   | I     | CMOS    | Transmit Terminal Data In: Byte-parallel data input for the STM-1 AU-4/STS-3c and STS-3 frames. The E1 bytes carrying an AIS indication are optional. No other TOH bytes are required. The path overhead bytes may accompany the payload. The high level corresponds to logic 1. TTDI7 is defined as the most significant bit and is the first bit transmitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## TRANSMIT REFERENCE TIMING

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|---------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRFI   | 20      | I     | CMOS | Transmit Reference Frame In: An optional reference framing pulse input that the SOT-3 uses to locate the transmit line side frame timing. When used, it is active for one TRCI clock cycle every 125 microseconds. When not used, it must be set to the inactive level of the signal, which is controlled by TLMODE (pin 5), as follows: When TLMODE is low, set TRFI high. When TLMODE is high, set TRFI low When it is not used, the pointer value will be arbitrary. |

| TRCI   | 21      | I     | CMOS | Transmit Reference Clock In: A required clock input that has a nominal frequency of 19.44 MHz. Used for transmit retiming and for sourcing the transmit data (TLDO) and clock out (TLCO) signals. The optional framing pulse (TRFI) is clocked in on the rising (falling) edge of TRCI when TLMODE (pin 5) is high (low).                                                                                                                                               |

## TRANSMIT LINE SIDE INTERFACE

| Symbol    | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                  |

|-----------|---------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLDO(7-0) | 14-7    | 0     | CMOS2mA | Transmit Line Data Out: STM-1/STS-3/STS-3c byte-parallel data. Data is clocked out on the falling edge of the transmit line clock out (TLCO) if TLMODE (pin 5) is high. Otherwise, it is clocked out on the rising edge. The high level corresponds to logic 1. TLDO7 is defined as the most significant bit and is the first bit transmitted. |

| TLFO      | 16      | 0     | CMOS2mA | Transmit Line Frame Out: An active high (low) framing pulse, one TLCO clock cycle wide, that occurs during the third A2 byte time of the transmitted data (TLDO), when TLMODE (pin 5) is set high (low).                                                                                                                                       |

| TLCO      | 17      | 0     | CMOS2mA | Transmit Line Clock Out: When TLMODE (pin 5) is set high (low), the byte-parallel data (TLDO) and the active high (low) framing signal (TLFO) are clocked out on falling (rising) edges of this TLCO clock, which is derived from TRCI after retiming.                                                                                         |

# TRANSPORT OVERHEAD BYTE (TOH) SERIAL ACCESS PORT INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSAFO  | 133     | 0     | TTL4mA | Receive TOH Serial Access Port Frame Out: An active high framing pulse, one RSACO clock cycle wide, that identifies the most significant bit in the C1 byte of the RSADO serial data stream. This framing pulse is also used to identify the location of the first bit in the 40-bit serial format of the Receive Alarm Indication Port Data Out (RAIDO) signal.                                                                                                                                                                           |

| RSACO  | 134     | 0     | TTL4mA | Receive TOH Serial Access Port Clock Out: A gapped clock which has an average rate of 5.184 MHz. The clock is generated by dividing the RLCI input clock by three, and the gap is one clock cycle out of every five cycles. Serial data (RSADO) and a framing signal (RSAFO) are clocked out on the falling edge of this clock (see the timing diagram in Figure 10). The first 40 pulses of this clock in each frame are also used to clock out the Receive Alarm Indication Port Data Out signal (RAIDO) and its framing signal (RSAFO). |

| RSADO  | 135     | 0     | TTL4mA | Receive TOH Serial Access Port Data Out: Serial bit stream that carries the contents of the receive line side Section Overhead bytes plus the AU-4 pointer in an STM-1 signal or the 81 Transport Overhead bytes in an STS-3/STS-3c frame. The high level corresponds to logic 1.                                                                                                                                                                                                                                                          |

| TSAFO  | 143     | 0     | TTL4mA | Transmit TOH Serial Access Port Frame Out: An active high framing pulse, one TSACO clock cycle wide, that identifies the most significant bit (MSB) of the C1 byte in the TSADI serial data stream. Used for identifying the starting location of the 81 overhead bytes to be accepted into the SOT-3.                                                                                                                                                                                                                                     |

| TSACO  | 144     | 0     | TTL4mA | Transmit TOH Serial Access Port Clock Out: A gapped output clock which has an average rate of 5.184 MHz. The clock is generated by dividing the TRCI input clock by three, and the gap is one clock cycle for every five cycles. Serial data (TSADI) and a framing signal (TSAFO) are clocked in on the rising edge of this clock. Refer to the timing diagram in Figure 11.                                                                                                                                                               |

| TSADI  | 145     | I     | TTL    | Transmit TOH Serial Access Port Data In: A serial bit stream that carries the contents of the transmit line side Section Overhead bytes plus the AU-4 pointer in the STM-1 format or the 81 Transport Overhead bytes in an STS-3c/STS-3 frame. The high level corresponds to logic 1.                                                                                                                                                                                                                                                      |

## **ALARM INDICATION PORT INTERFACE**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|---------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAIDO  | 132     | 0     | ΠL   | Receive Alarm Indication Port Data Out: A serial bit stream output that provides the status of receive alarms. It is normally connected to the TAIDI input of the mate SOT-3 device in ring applications. The data format is a serial stream of 40 bits that is transmitted once per frame, as described in Figure 25 (Operation section). The values present on this pin during the remaining 41 clock times of the frame are not defined. The high level corresponds to logic 1.                                                                                                                |

|        |         |       |      | This signal is clocked out on the falling edges of the Receive TOH Serial Access Port Clock Out signal (RSACO). The Receive TOH Serial Access Port Frame Out signal (RSAFO) indicates the position of the most significant bit (bit 39).                                                                                                                                                                                                                                                                                                                                                          |

| TAICI  | 147     | I     | TTL  | Transmit Alarm Indication Port Clock In: Normally connected to the Receive TOH Serial Access Port Clock Out signal (RSACO) of the other SOT-3 device in a ring configuration. This is a gapped clock which has an average rate of 5.184 MHz. Data (TAIDI) and the framing signal (TAIFI) are clocked into the SOT-3 on the rising edges of this clock. TAICI is not monitored for loss of clock.                                                                                                                                                                                                  |

| TAIFI  | 148     | I     | TTL  | Transmit Alarm Indication Port Frame In: Normally connected to the Receive TOH Serial Access Port Frame Out signal (RSAFO) pin of the mate SOT-3 device in a ring configuration. An active high framing pulse, one TAICI clock cycle wide, which identifies the first bit (No. 39) of the Alarm Indication Port data input stream at TAIDI.                                                                                                                                                                                                                                                       |

| TAIDI  | 149     | I     | TTL  | Transmit Alarm Indication Port Data In: Normally connected to the Receive Alarm Indication Port Data Out signal (RAIDO) pin of the mate SOT-3 device when two devices are used together in a ring configuration. The input alarm indications in the serial bit stream (see Figure 25 in the Operation section) are used to generate line and path RDI and FEBE alarm indications, and APS information, in the transmitted STM-1/STS-3 line signal. The alarm indications are clocked into the SOT-3 device on the rising edges of the input clock (TAICI). The high level corresponds to logic 1. |

## **MICROPROCESSOR BUS INTERFACE**

| Symbol            | Pin No. | I/O/P            | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|---------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAMCI             | 44      | I                | CMOS   | RAM Clock Input: Asynchronous clock input used for internal RAM functions. This clock may be connected to the microprocessor clock. Requires clock rate of 16-20 MHz and duty cycle of 45-55%.                                                                                                                                                                                                                                                                    |

| INT/ĪRQ           | 45      | 0                | TTL4mA | Interrupt: Intel mode (INT): A high on this output pin signals an interrupt request to the microprocessor. Motorola mode (IRQ): A low on this output pin signals an interrupt request to the microprocessor.                                                                                                                                                                                                                                                      |

| D(7-0)            | 47-54   | I/O              | TTL8mA | Data Bus: These bidirectional data lines are used for transferring data between the SOT-3 RAM and the microprocessor. The high level corresponds to logic 1. D7 is defined as the most significant bit.                                                                                                                                                                                                                                                           |

| SEL               | 56      | I                | TTLp   | <b>Select:</b> A low enables data transfers between the microprocessor and SOT-3 RAM during a read or write cycle.                                                                                                                                                                                                                                                                                                                                                |

| RD<br>or<br>RD/WR | 57      | I                | TTL    | Read or Read/Write:  Intel mode (RD): An active low signal generated by the microprocessor for reading the SOT-3 RAM.  Motorola mode (RD/WR): An active high signal generated by the microprocessor for reading the SOT-3 RAM.  A low is used to write to SOT-3 RAM locations.                                                                                                                                                                                    |

| WR                | 58      | I                | TTL    | Write: Intel mode: An active low signal generated by the microprocessor for writing to SOT-3 RAM. Motorola mode: Not used, left floating.                                                                                                                                                                                                                                                                                                                         |

| МОТО              | 75      | I                | TTL    | Motorola/Intel Processor Select: A high selects a Motorola microprocessor compatible bus interface. A low selects an Intel microprocessor compatible bus interface.                                                                                                                                                                                                                                                                                               |

| RDY/<br>DTACK     | 61      | O<br>(tri-state) | TTL8mA | Ready or Data Transfer Acknowledge:  Intel mode (RDY): A high is an acknowledgment from the addressed RAM location that the transfer can be completed. A low indicates the SOT-3 cannot complete the transfer cycle, and that microprocessor wait states must be generated.  Motorola mode (DTACK): During a read cycle, a low signal indicates the information on the data bus is valid. During a write cycle, a low signal acknowledges the acceptance of data. |

| A(9-0)            | 63-72   | I                | TTL    | Address Bus: These address line inputs are used by the microprocessor to select a SOT-3 RAM location for a read/write data transfer when the Select lead is low. The high level corresponds to logic 1. A9 is defined as the most significant bit.                                                                                                                                                                                                                |

## **CONTROLS**

| Symbol  | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|---------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLB     | 3       | 0     | TTL4mA | Facility Loopback Control Out: An active high control signal provided by the SOT-3 device, when control bit FLB is set to 1 by the microprocessor, for enabling the facility loopback feature in the SYN155 (TXC-02301B) or other line interface circuit.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TLB     | 4       | 0     | TTL4mA | Terminal Loopback Control Out: An active high control signal provided by the SOT-3 device, when control bit TLB is set to 1 by the microprocessor, for enabling the terminal loopback feature in the SYN155 (TXC-02301B) or other line interface circuit.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TLMODE  | 5       | I     | TTLp   | Transmit Line Interface Invert Control:  A high causes the Transmit Line Frame Out (TLFO) signal to be active high. This framing signal and data (TLDO(7-0)) will be clocked out on falling edges of the transmit line clock (TLCO). The Transmit Reference Frame In (TRFI) must be an active high indication.  A low causes the Transmit Line Frame Out (TLFO) signal to be active low. The framing signal and data (TLDO(7-0)) will be clocked out on rising edges of the transmit line clock (TLCO). The Transmit Reference Frame In (TRFI) must be an active low indication.  See Figures 4 and 5 for timing diagrams of operation with TLMODE (pin 5) set high and low. |

| DATACOM | 43      | I     | TTL    | Data Communication Mode: An active high select for the data communication (datacom) and source timing modes of operation. When high, datacom (source timing) mode is selected when control bit STIME is set to 0 (1). In the transmit direction, the SOT-3 device provides the transmit clock (TTCI), C1J1 and SPE as output signals, together with the POH output, for sourcing terminal data (TTDI) into the SOT-3 device.                                                                                                                                                                                                                                                 |

| FAIS1   | 130     | I     | TTLp   | Generate Receive Path AIS and Transmit an RDI Indication for STM-1 AU-4/STS-3c or STS-3:STS-1 No. 1: An active low input for controlling the generation of path AIS and Transmit RDI (when not in the RING mode) for STM-1 AU-4/STS-3c or STS-3:STS-1 No. 1. When this pin is not used it should held high. It should be noted that activation of this input may cause erratic J1 pulse and pointer movements.                                                                                                                                                                                                                                                               |

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FAIS2  | 129     | I     | TTLp | Generate Receive Path AIS and Transmit an RDI Indication for STS-3:STS-1 No. 2: An active low input for controlling the generation of path AIS and Transmit RDI (when not in the RING mode) for STS-3 STS-1 No. 2. When this pin is not used it should held high. It should be noted that activation of this input may cause erratic J1 pulse and pointer movements.                                                                                                                          |  |  |  |

| FAIS3  | 128     | I     | TTLp | Generate Receive Path AIS and Transmit an RDI Indication for STS-3:STS-1 No. 3: An active low inp for controlling the generation of path AIS and Transm RDI (when not in the RING mode) for STS-3 STS-1 No. 3. When this pin is not used it should held high. It should be noted that activation of this input may cause erration J1 pulse and pointer movements.                                                                                                                             |  |  |  |

| MODE0  | 137     | I     | TTLp | Mode Control: A low is normally applied to this pin, to enable the full set of features and performance characteristics described in this Data Sheet. If this pin is instead tied high or left floating, the device emulates the features and performance characteristics of the predecessor SOT-3 device, Part Number TXC-03003-AIPQ, which are described in its Data Sheet, document number TXC-03003-MB.                                                                                   |  |  |  |

| J1SYNC | 158     | I     | TTLp | J1 Byte Optional Synchronize Pulse: When an active low pulse having a minimum duration of one clock cycle at 19.44 MHz is applied to this pin the starting locations of the three transmit path overhead RAM segment addresses J11, J12 and J13 are reset to 1C0H, 200H and 240H, respectively. The next J1 byte transmitted for a STM-1/STS-3c or for one of the three STS-3:STS-1 signals will start at the appropriate one of these three address locations.                               |  |  |  |

| RESET  | 142     | I     | TTL  | SOT-3 Reset: An active high signal which resets the FIFOs, performance counters and parity counters to preset values. The transmit pointer generation and access ports are also reset. The receive pointer tracking state machine is set to path AIS state. Control bits and RAM locations are not affected.  RESET must be used at power-up, after the power supply and all four input clocks are stable. The signal must be held high for a minimum duration of six 19.44 MHz clock cycles. |  |  |  |

## **AIS INDICATIONS AND CONTROLS**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                               |

|--------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXAIS1 | 76      | 0     | TTL4mA | Receive AIS Indication for STM-1 AU-4/STS-3c or STS-3:STS-1 No. 1: Active high output indication for the alarms that cause a receive VT or path AIS for STM-1 AU-4/STS-3c or STS-3:STS-1 No. 1. See Note 1.                                                                                                                 |

| RXAIS2 | 77      | 0     | TTL4mA | Receive AIS Indication for STS-3:STS-1 No. 2: Active high output indication for the alarms that cause a receive VT or path AIS for STS-3:STS-1 No. 2. See Note 1.                                                                                                                                                           |

| RXAIS3 | 78      | 0     | TTL4mA | Receive AIS Indication for STS-3:STS-1 No. 3: Active high output indication for the alarms that cause a receive VT or path AIS for STS-3:STS-1 No. 3. See Note 1.                                                                                                                                                           |

| TXAIS1 | 38      | I     | TTL    | Transmit AIS Control for STM-1 AU-4/STS-3c or STS-3:STS-1 No. 1: Active high input that generates a line or path AIS for STM-1 AU-4/STS-3c or STS-1 No. 1 of STS-3, conditional on bit 2 and bit 0 at Address 3E0H. When bit 2 (TRPAISE) is 1, a Path AIS is generated. When bit 0 (TRLAISE) is 1, a Line AIS is generated. |

| TXAIS2 | 37      | I     | TTL    | Transmit AIS Control for STS-3:STS-1 No. 2: Active high input that generates path AIS for STS-1 No. 2 of STS-3 (similar to TXAIS1, above). When high, with TRPAISE set to 1, path AIS is generated.                                                                                                                         |

| TXAIS3 | 36      | I     | TTL    | Transmit AIS Control for STS-3:STS-1 No. 3: Active high input that generates AIS for STS-1 No. 3 of STS-3 (similar to TXAIS1, above). When high, with TRPAISE set to 1, path AIS is generated.                                                                                                                              |

Note 1: See Figures 18 and 19 for description of conditions which cause a receive VT or path AIS and activate pin RXAISn, where n=1-3.

## ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS

| Parameter                          | Symbol          | Min  | Max                   | Unit   | Conditions                        |

|------------------------------------|-----------------|------|-----------------------|--------|-----------------------------------|

| Supply voltage                     | V <sub>DD</sub> | -0.3 | +7.0                  | V      | Note 1                            |

| DC input voltage                   | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V      | Note 1                            |

| Storage temperature range          | T <sub>S</sub>  | -55  | 150                   | οС     | Note 1                            |

| Ambient operating temperature      | T <sub>A</sub>  | -40  | 85                    | οС     | 0 ft/min linear airflow           |

| Component Temperature x Time       | TI              |      | 270 x 5               | °C x s | Note 1                            |

| Moisture Exposure Level            | ME              | 5    |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A    |

| Relative Humidity, during assembly | RH              | 30   | 60                    | %      | Note 2                            |

| Relative Humidity, in-circuit      | RH              | 0    | 100                   | %      | non-condensing                    |

| ESD Classification                 | ESD             |      | ±2000                 | V      | per MIL-STD-883D<br>Method 3015.7 |

#### Notes: