# SOT-1 Device SONET STS-1 Overhead Terminator TXC-03001

**DATA SHEET**

Preliminary

#### **FEATURES**

- Provides SONET interface to any type of payload

- Programmable STS-1 or STS-N modes

- Receive bit-serial STS-1 signal in the line side using external reference frame pulse input for STS-N applications

- Transmit bit-serial STS-1 signal from the line side using external reference frame pulse for outgoing phase synchronization

- Programmable: full STS-1 or SPE-only I/O on the terminal side

- Bit-serial or byte-parallel I/O on the terminal side

- Optional AIS communication with peer SOT-1 or SOT-3

- Interfaces to microprocessors with hierarchical scan and optional hardware interrupt on alarms

- SONET alarm processing and performance monitoring

- Meets 1991 ANSI/Bellcore standards:

- T1X1.5/90-025R1

- TA-NWT-000253

#### **DESCRIPTION ≡**

The SOT-1 SONET/STS-1 Overhead Terminator performs section, line and path overhead processing for STS-1 SONET signals. This versatile device can be used anywhere in a SONET network where STS-1 signals are in use, i.e., repeaters and line or path termination points. Interfaces are provided for both section and line orderwire and datacom channels. Further, control bits in the memory map enable the SOT-1 to perform loopback, and serial or parallel I/O. Line side and terminal side clock rates can differ. The receive/transmit pointer is recalculated as necessary to compensate for the differences in these clocks.

All overhead bytes are stored in on-chip RAM. New overhead bytes can be substituted from RAM to either the terminal or line side, depending on the application. The SOT-1 also provides alarm detection and AIS generation, as well as software and hardware interrupt in the event of errors.

### APPLICATIONS =

- SONET W-DCS/B-DCS

- High speed data communication

- Payload extraction, introduction into STS-1

- STS-N multiplexer

- SONET test sets

**TERMINAL** LINE Microprocessor +5V SIDE SIDE Interface Bit-serial/byte-parallel clock, data and frame STS-1 serial SOT-1 clock, data Payload indicators: and frame start of payload, payload present STS-1 serial **SONET STS-1** Bit-serial/byte-parallel clock and 4 clock and data Overhead Terminator data Payload indicators: start of payload, payload present Transmit reference clock and frame Section, line Section, line orderwire, APS datacom data, clocks and frames data and clocks

Patents Pending

Copyright © 1994 TranSwitch Corporation

TXC and TranSwitch are registered trademarks of TranSwitch Corporation

Document Number: TXC-03001-MB Ed. 10, September 1994 PRELIMINARY information documents contain information on products in the sampling, pre-production or early production phases of the product life cycle. Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

# **TABLE OF CONTENTS**

| SECTION                               | <u>PAGE</u>     |

|---------------------------------------|-----------------|

| Block Diagram                         | 3               |

| Block Diagram Description             | 3-4             |

| Pin Diagram                           | 5- <del>4</del> |

| Pin Descriptions                      | 5-10            |

| Absolute Maximum Ratings              | 3-10<br>11      |

| Thermal Characteristics               | 11              |

| Power Requirements                    | 11              |

| Input, Output, and I/O Parameters     | 12-14           |

| Timing Characteristics                | 15-29           |

| Operation                             | 30-54           |

| Register Bit Map                      | 30-34           |

| Register Bit Map Descriptions         | 31-41           |

| Control Register Descriptions         | 31-38           |

| Status Register Descriptions          | 39-41           |

| Alarm Propagation Tables              | 42              |

| Receive Alarm Propagation Table       | 42              |

| Transmit Alarm Propagation Table      | 42              |

| Memory Map                            | 43-50           |

| Interfaces and Operating Modes        | 51-52           |

| Microprocessor Interface              | 53              |

| Orderwire/APS Interface               | 53              |

| Datacom Interfaces                    | 53              |

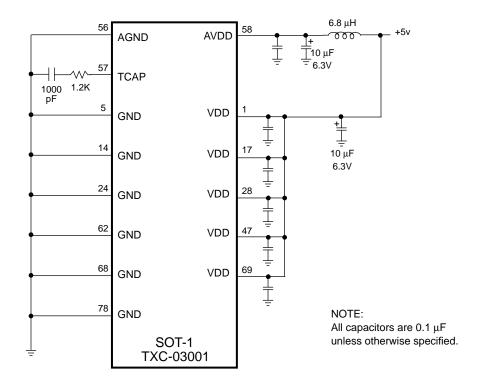

| Power, Ground and External Components | 54              |

| Throughput Delays                     | 54              |

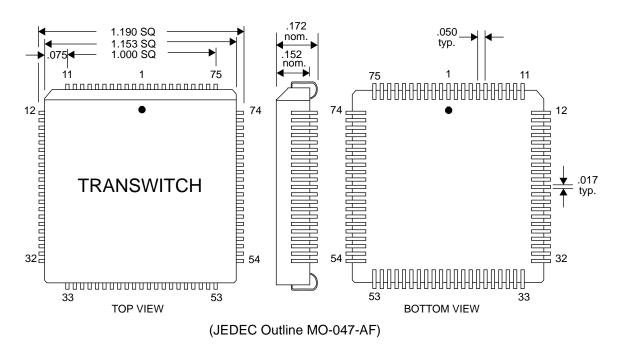

| Packaging                             | 55              |

| Ordering Information                  | 56              |

| Related Products                      | 56              |

| Standards Documentation Sources       | 57              |

| List of Data Sheet Changes            | 58-60           |

|                                       |                 |

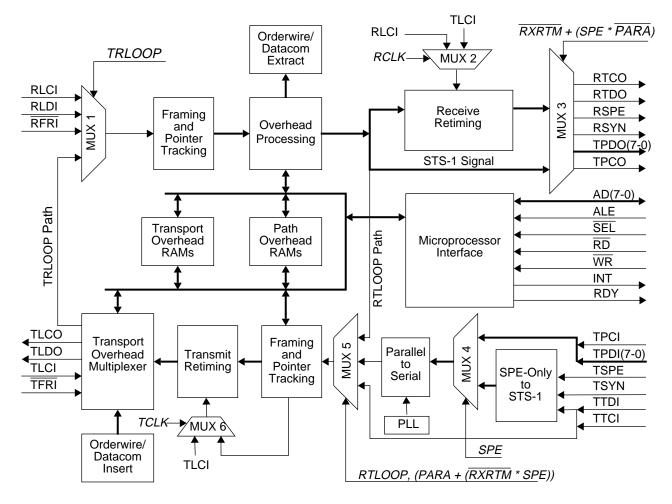

#### **BLOCK DIAGRAM**

Note: Names in italics are internal control bits.

Figure 1. SOT-1 Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

The block diagram of the SOT-1 is shown in Figure 1. The input multiplexer (MUX 1) selects either the line side input, or the looped back signal from transmit line output, as the input to the Framing and Pointer Tracking Block. The Framing and Pointer Tracking Block performs frame synchronization to the incoming STS-1 signal, serial to parallel conversion, and pointer tracking. Incoming STS-1 alarms are also detected. The Overhead Processing Block stores the line, section, and path overhead bytes into RAM locations for access by the microprocessor. It then optionally multiplexes the line, section, and path overhead bytes from the RAM locations written by the microprocessor. Incoming SONET performance monitoring functions as well as debouncing of selected overhead bytes are also performed by the Overhead Processing Block. The Orderwire/Datacom Extract Block extracts and routes the APS and the two orderwire bytes to the orderwire interface, and the section and line data communication bytes to the two datacom interfaces.

The Receive Retiming Block retimes the line input to the reference frequency, and performs pointer recalculation and SPE-only extraction. All transport overhead bytes are demultiplexed and the payload is retimed. The

#### **PRELIMINARY**

reference clock used for retiming is selected by MUX 2 as either the line clock (RLCI) or the reference clock (TLCI). The terminal side output multiplexer (MUX 3) allows selection of either the output of the Overhead Processing Block or the output of the Receive Retiming Block.

In the transmit direction, the SPE-Only to STS-1 Block receives serial SPE-only signals from the terminal, and introduces framing and pointer bytes to produce a parallel STS-1 signal. The Parallel to Serial Block uses the phase-locked loop (PLL) to serialize either the data from the SPE-Only to STS-1 Block or parallel input from the terminal, as selected by MUX 4. The MUX 5 multiplexer selects for input to the Transmit Framing and Pointer Tracking Block either the looped back data from the output of the receive side Overhead Processing Block, or the output of the Parallel to Serial Block, or the serial STS-1 input from the terminal.

The Framing and Pointer Tracking Block performs frame synchronization to the serial STS-1 signal, serial to parallel conversion, and pointer tracking. Incoming STS-1 alarms are also detected. The section, line and path overhead bytes are stored into RAM locations for access by the microprocessor. The path overhead bytes are then optionally multiplexed from the RAM locations written by the microprocessor.

The Transmit Retiming Block performs retiming to the reference frequency and pointer recalculation. The Transport Overhead Multiplexer Block optionally multiplexes the section and line overhead bytes from the RAM written by the microprocessor. The Orderwire/Datacom Insert Block optionally multiplexes the orderwire, APS and datacom bytes from the orderwire interface and the two datacom interfaces into the transmit outgoing Transport Overhead RAM locations.

The Transport Overhead RAMs consist of locations for storing receive incoming transport overhead bytes, receive outgoing transport overhead bytes (written by the microprocessor), transmit incoming transport overhead bytes, and transmit outgoing transport overhead bytes. It also stores B1 and B2 performance monitors, and pointer justification counters. The RAMs also act as temporary storage for datacom and orderwire bytes received from the respective interfaces.

The Path Overhead RAMs consist of locations for storing receive incoming path overhead bytes, receive outgoing path overhead bytes (written by the microprocessor), transmit incoming path overhead bytes, and transmit outgoing path overhead bytes. The RAMs also store B3 and FEBE performance monitors.

The Microprocessor Interface provides access to the control registers, which select various modes of operation and status registers that report various alarm conditions. It also provides access to the Transport and Path Overhead RAMs, and provides both software and hardware interrupt capability based on the status of the chip.

When SPE = 1 in the serial mode (PARA = 0), the terminal output of the SOT-1 contains payload bits but no transport overhead, TOH (see the SOT-1 Memory Map section of this data sheet). The RSPE output provides a gapping signal for the SPE-only mode of operation. Nominally, there are 8 x 3 = 24 bits of TOH and 8 x 87 = 696 bits of payload. For this circumstance, the RSPE provides 24 equally spaced gaps in the output data (720/24 = 30, every 30th bit is gapped). When there is an increment in the pointer, there must be 32 equally spaced gaps, and when there is a decrement, there are 16 equally spaced gaps for the row containing the pointer bytes.

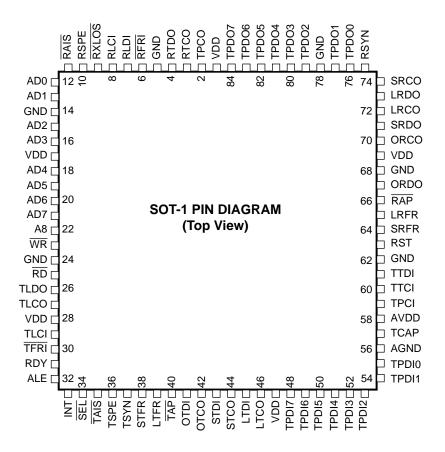

### **PIN DIAGRAM**

Figure 2. SOT-1 Pin Diagram

### **PIN DESCRIPTIONS**

### **Power Supply and Ground**

| Symbol | Pin No.             | I/O/P* | Туре | Name/Function                                |

|--------|---------------------|--------|------|----------------------------------------------|

| VDD    | 1,17,28,47,69       | Р      |      | Power Supply: +5-volt supply voltage, +/- 5% |

| AVDD   | 58                  | Р      |      | Analog Power: +5 volts, +/- 5%               |

| GND    | 5,14,24,62,68<br>78 | Р      |      | Digital Ground                               |

| AGND   | 56                  | Р      |      | Analog Ground                                |

<sup>\*</sup>Note: I = Input; O = Output; P = Power; OD = Open Drain Output

# **Microprocessor Bus Interface**

| Symbol                        | Pin No.                 | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|-------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD(7-4)<br>AD(3-2)<br>AD(1-0) | 21-18<br>16-15<br>13-12 | I/O   | TTL8mA | Address/Data Bus: These signal leads constitute the time-multiplexed address and bidirectional data bus.                                                                                                                                                                                                                                                                                                                                                           |

| A8                            | 22                      | I     | TTL    | Address Bus - Bit 8: Bit 8 of the address bus.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| WR                            | 23                      | I     | TTLp   | <b>Write:</b> An active low signal generated by the microprocessor for writing to the SOT-1.                                                                                                                                                                                                                                                                                                                                                                       |

| RD                            | 25                      | I     | TTLp   | <b>Read:</b> An active low signal generated by the microprocessor for reading the SOT-1.                                                                                                                                                                                                                                                                                                                                                                           |

| RDY                           | 31                      | OD    | OD16mA | Ready: A high is an active acknowledgment from the SOT-1 indicating that the transfer can be completed. The RDY line will go low whenever the address being read or written to corresponds to a RAM location. When status or control registers are accessed, RDY remains high. The RDY lead is an open drain capable of sinking a maximum of 16 mA. The value of the pullup resistor value depends on the number of devices that use the RDY signal in the system. |

| ALE                           | 32                      | I     | TTLp   | Address Latch Enable: An active high input signal provided by the microprocessor to latch the address into a SOT-1 address latch for a bus cycle.                                                                                                                                                                                                                                                                                                                  |

| INT                           | 33                      | 0     | TTL4mA | Interrupt: A high on this pin signals an interrupt request for the microprocessor. The hardware interrupt request is enabled by HINT=1 (bit 5, address 0FA).                                                                                                                                                                                                                                                                                                       |

| SEL                           | 34                      | I     | TTLp   | <b>Select:</b> An active low signal which enables data transfers between the microprocessor and SOT-1 RAM during a read/write bus cycle.                                                                                                                                                                                                                                                                                                                           |

| RST                           | 63                      | I     | TTL    | Reset: Resets all internal counters and sets all alarms except RLOC. RST is a positive pulse with a minimum width of 300 ns. It must be used after power is applied, registers are initialized, and the clocks are stable.                                                                                                                                                                                                                                         |

# **Receive Line Side Interface:**

| Symbol | Pin No. | I/O/P | Туре  | Name/Function                                                                                                                                                               |

|--------|---------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFRI   | 6       | I     | CMOSp | Receive Line Frame In: An optional active low frame pulse that occurs during the C1 byte, bit 7 time. When used, it reduces the OOF exit time from two frames to one frame. |

| RLDI   | 7       | I     | CMOS  | Receive Line Data In: Incoming serial STS-1/STS-N data which is clocked into the SOT-1 on the rising edge of RLCI.                                                          |

<sup>\*</sup>See Input, Output and I/O Parameters section below for Type definitions.

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                 |

|--------|---------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLCI   | 8       | I     | CMOS | Receive Line Clock In: A 51.84 MHz clock that clocks in the serial data and the optional framing pulse. RLCI is used as the time base for framing, pointer tracking, and demultiplexing the transport overhead bytes, and for RAM access in the receive side. |

| RXLOS  | 9       | I     | TTLp | Receive Loss of Signal: An active low external loss of signal indication from a higher multiplexer such as an SM3. SOT-1 combines RXLOS with the internal loss of signal and reports the result to the microprocessor as the RLOS status bit.                 |

### **Transmit Line Side Interface:**

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                         |

|--------|---------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLDO   | 26      | 0     | CMOS4mA | Transmit Line Data Out: Outgoing serial STS-1/STS-N data which is clocked out of the SOT-1 on the falling edge of TLCO.                                                               |

| TLCO   | 27      | 0     | CMOS4mA | Transmit Line Clock Out: An outgoing serial STS-1/STS-N clock. Depending on the operating mode, TLCO is derived from TLCI, TTCI or TPCI.                                              |

| TLCI   | 29      | I     | CMOS    | Transmit Line Clock In: The 51.84 MHz reference clock input.                                                                                                                          |

| TFRI   | 30      | I     | CMOSp   | Transmit Frame Reference In: An optional active low frame pulse, synchronous with TLCI, which determines outgoing A1, A2 epoch. TFRI can be used only if TCLK=1 (bit 6, address 1FA). |

## Orderwire/APS Interface:

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                            |

|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| STFR   | 38      | 0     | TTL4mA | Transmit Section Orderwire Framing Pulse: Transmit frame pulse for section orderwire codec/filter.                                                       |

| LTFR   | 39      | 0     | TTL4mA | <b>Transmit Line Orderwire Framing Pulse:</b> Transmit frame pulse for line orderwire codec/filter.                                                      |

| TAP    | 40      | 0     | TTL4mA | Transmit APS Framing Pulse: An active low signal which occurs one clock cycle before the MSB of the K1 byte is expected in the serial bit stream (OTDI). |

| OTDI   | 41      | I     | TTLp   | Transmit Orderwire Byte and APS Byte Input: The two orderwire bytes and APS bytes are clocked into the SOT-1 on negative transitions of OTCO.            |

| ОТСО   | 42      | 0     | TTL4mA | Transmit Orderwire and APS Clock: A 576 KHz clock, synchronous to TLCO, which is used for sourcing the orderwire and APS bytes into the SOT-1.           |

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                    |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SRFR   | 64      | 0     | TTL4mA | Receive Section Orderwire Framing Pulse: Receive frame pulse for section orderwire codec/filter.                                                 |

| LRFR   | 65      | 0     | TTL4mA | Receive Line Orderwire Framing Pulse: Receive frame pulse for line orderwire codec/filter.                                                       |

| RAP    | 66      | 0     | TTL4mA | Receive APS Framing Pulse: An active low signal which occurs one clock cycle after the LSB of the first K2 byte in the serial bit stream (ORDO). |

| ORDO   | 67      | 0     | TTL4mA | Receive Orderwire Byte and APS Byte Output: The two orderwire bytes and APS bytes are clocked out of the SOT-1 on positive transitions of ORCO.  |

| ORCO   | 70      | 0     | TTL4mA | Receive Orderwire and APS Clock: A 576 KHz clock, derived from RLCI, which is used for clocking the orderwire and APS bytes from the SOT-1.      |

### **Section and Line Data Communication Interface:**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                        |

|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STDI   | 43      | I     | TTLp   | Transmit Section Data Communication Data Input: Serial 192 Kbit/s data (D1 - D3 bytes) is clocked into the SOT-1 on positive transitions of the clock STCO.          |

| STCO   | 44      | 0     | TTL4mA | Transmit Section Data Communication Clock Output: A 192 KHz clock, derived from TLCO, which is used for sourcing the section data communication data into the SOT-1. |

| LTDI   | 45      | I     | TTLp   | Transmit Line Data Communication Data Input:<br>Serial 576 Kbit/s data (D4 - D12 bytes) is clocked into<br>the SOT-1 on positive transitions of the clock LTCO.      |

| LTCO   | 46      | 0     | TTL4mA | Transmit Line Data Communication Clock Output: A 576 KHz clock, derived from TLCO, which is used for sourcing the line data communication data into the SOT-1.       |

| SRDO   | 71      | 0     | TTL4mA | Receive Section Data Communication Data Output: Serial 192 Kbit/s data (D1 - D3 bytes) is clocked out of the SOT-1 on negative transitions of the clock SRCO.        |

| LRCO   | 72      | 0     | TTL4mA | Receive Line Data Communication Clock Output: A 576 KHz clock, derived from RLCI, which is used for clocking out the line data communication data.                   |

| LRDO   | 73      | 0     | TTL4mA | Receive Line Data Communication Data Output:<br>Serial 576 Kbit/s data (D4 - D12 bytes) is clocked out<br>of the SOT-1 on negative transitions of the clock<br>LRCO. |

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                            |

|--------|---------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRCO   | 74      | 0     |      | Receive Section Data Communication Clock Output: A 192 KHz clock, derived from RLCI, which is used for clocking out the section data communication data. |

### **Terminal Side Interface:**

| Symbol                 | Pin No.        | I/O/P | Туре    | Name/Function                                                                                                                                                                                                        |

|------------------------|----------------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTCO                   | 3              | 0     | CMOS4mA | Receive Terminal Clock Output: The 51.84 MHz terminal clock, used for clocking out the serial data RTDO. Depending on operating mode, RTCO can be derived either from RLCI or TLCI.                                  |

| RTDO                   | 4              | 0     | CMOS4mA | Receive Terminal Data Output: Serial 51.84 Mbit/s STS-1 receive data. Data is clocked out of the SOT-1 on negative transitions of the clock RTCO.                                                                    |

| RSPE                   | 10             | 0     | CMOS4mA | Receive Terminal SPE Indication: An active high signal indicating the synchronous payload envelope in the terminal data output, RTDO or TPDO. For SPE-only, the RSPE output is a gapping signal.                     |

| RSYN                   | 75             | 0     | CMOS4mA | Receive Terminal Sync Pulse: RSYN is high during the C1 byte and J1 byte of RTDO or TPDO. In serial SPE-only mode, RSYN is high only during the J1 byte of RTDO.                                                     |

| TPCO                   | 2              | 0     | TTL4mA  | <b>Terminal Parallel Clock Output:</b> The 6.48 MHz clock, derived from RTCO, that clocks out receive terminal byte data TPDO.                                                                                       |

| TPDO(7-2)<br>TPDO(1-0) | 84-79<br>77-76 | 0     | TTL4mA  | Terminal Parallel Data Output: Byte-wide 6.48 Mbyte/s receive terminal data which is clocked out of the SOT-1 on positive transitions of the clock TPCO.                                                             |

| TTCI                   | 60             | I     | CMOS    | Transmit Terminal Serial Clock Input: A 51.84 MHz terminal clock used for clocking in serial data (TTDI), as well as transmit SPE indication (TSPE) and the transmit sync pulse (TSYN).                              |

| TTDI                   | 61             | I     | CMOS    | <b>Transmit Terminal Data Input:</b> Serial 51.84 Mbit/s transmit terminal data which is clocked into the SOT-1 on positive transitions of the clock TTCI.                                                           |

| TSPE                   | 36             | I     | CMOS    | Transmit Terminal SPE Indication: Required input for the SPE-only mode. A high value indicates the location of the SPE bits in the data input, TTDI. A low value identifies the location of a gap in the input data. |

| TSYN                   | 37             | I     | CMOS    | Transmit Terminal Sync Pulse: Required input for the SPE-only mode. TSYN must be high during incoming J1 byte of TTDI in the SPE-only mode.                                                                          |

| Symbol    | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                          |

|-----------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPCI      | 59      | I     | TTL  | Terminal Parallel Clock Input: A 6.48 MHz clock used for clocking in terminal transmit data TPDI.                                                      |

| TPDI(7-0) | 48-55   | I     |      | Terminal Parallel Data Input: Byte-wide 6.48 Mbyte/s transmit terminal data. Data is clocked into the SOT-1 on positive transitions of the clock TPCI. |

## **Alarm Indication Ports:**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                            |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAIS   | 11      | 0     | TTL4mA | Receive Alarm Indication Signal: An active low signal indicating a downstream AIS must be generated under the conditions indicated in the Receive Alarm Propagation Table section below as resulting in action code 'A'. |

| TAIS   | 35      | I     | TTLp   | Transmit Alarm Indication Signal: An active low input causes AIS to be introduced into transmit line, as indicated in the 'TAIS pin is low', column of the Transmit Alarm Propagation Table section below.               |

## Phase-Locked Loop:

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                         |

|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCAP   | 57      | I/O   |      | External Resistor/Capacitor: A 1.2 Kohm, 1/4 watt, 5% carbon composition resistor in series with a 1000 pF capacitor connected to analog ground. The RC network is required when the terminal interface is used in the following modes:  1. Byte-parallel 2. SPE-only |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol          | Min  | Max                   | Unit |

|--------------------------------|-----------------|------|-----------------------|------|

| Supply voltage                 | V <sub>DD</sub> | -0.3 | +7.0                  | V    |

| DC input voltage               | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Continuous power dissipation   | P <sub>C</sub>  |      | 825                   | mW   |

| Ambient operating temperature  | T <sub>A</sub>  | -40  | 85                    | °C   |

| Operating junction temperature | T <sub>J</sub>  |      | 125                   | °C   |

| Storage temperature range      | T <sub>S</sub>  | -55  | 150                   | °C   |

<sup>\*</sup>Note: Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

### THERMAL CHARACTERISTICS

| Parameter                                | Min | Тур | Max | Unit | Test Conditions |

|------------------------------------------|-----|-----|-----|------|-----------------|

| Thermal resistance - junction to ambient |     | 32  | 34  | °C/W |                 |

# **POWER REQUIREMENTS**

| Parameter           | Min  | Тур | Max  | Unit | Test Conditions  |

|---------------------|------|-----|------|------|------------------|

| V <sub>DD</sub>     | 4.75 | 5.0 | 5.25 | V    |                  |

| V <sub>ANALOG</sub> | 4.75 | 5.0 | 5.25 | V    |                  |

| I <sub>DD</sub>     |      | 130 | 150  | mA   |                  |

| I <sub>ANALOG</sub> |      | 5   | 7    | mA   |                  |

| P <sub>DD</sub>     |      | 650 | 788  | mW   | Output switching |

| P <sub>ANALOG</sub> |      | 25  | 37   | mW   |                  |

# INPUT, OUTPUT, AND I/O PARAMETERS

## **Input Parameters For CMOS**

| Parameter             | Min  | Тур | Max  | Unit | Test Conditions              |

|-----------------------|------|-----|------|------|------------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |      |     | 1.65 | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |      |     | 10   | μΑ   | V <sub>DD</sub> = 5.25       |

| Input capacitance     |      | 5.5 |      | pF   |                              |

## **Input Parameters For CMOSp**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                   |

|-----------------------|-----|-----|-----|------|-----------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25      |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25      |

| Input leakage current |     | 0.5 | 1.4 | mA   | $V_{DD} = 5.25$ ; Input = 0 volts |

| Input capacitance     |     | 5.5 |     | pF   |                                   |

Note: Input has a 100K (nominal) internal pull-up resistor.

## **Input Parameters For TTL**

| Parameter             | Min | Тур | Max | Unit | Test Conditions              |

|-----------------------|-----|-----|-----|------|------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |     |     | 10  | μΑ   | V <sub>DD</sub> = 5.25       |

| Input capacitance     |     | 5.5 |     | pF   |                              |

## **Input Parameters For TTLp**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                         |

|-----------------------|-----|-----|-----|------|-----------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25            |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25            |

| Input leakage current |     | 0.5 | 1.4 | mA   | V <sub>DD</sub> = 5.25; Input = 0 volts |

| Input capacitance     |     | 5.5 |     | pF   |                                         |

Note: Input has a 9K (nominal) internal pull-up resistor.

# **Output Parameters For TTL4mA**

| Parameter         | Min                   | Тур | Max  | Unit | Test Conditions                                |

|-------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -2.0 |

| V <sub>OL</sub>   |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0  |

| I <sub>OL</sub>   |                       |     | 4.0  | mA   |                                                |

| I <sub>OH</sub>   |                       |     | -2.0 | mA   |                                                |

| t <sub>RISE</sub> | 2.8                   | 6.5 | 9.2  | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub> | 1.3                   | 2.3 | 3.4  | ns   | C <sub>LOAD</sub> = 15 pF                      |

## **Output Parameters For CMOS4mA**

| Parameter         | Min                   | Тур | Max  | Unit | Test Conditions                                |

|-------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>   |                       |     | 0.4  | V    | $V_{DD} = 4.75; I_{OL} = 4.0$                  |

| I <sub>OL</sub>   |                       |     | 4.0  | mA   |                                                |

| I <sub>OH</sub>   |                       |     | -4.0 | mA   |                                                |

| t <sub>RISE</sub> | 1.4                   | 2.9 | 4.2  | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub> | 1.3                   | 2.3 | 3.4  | ns   | C <sub>LOAD</sub> = 15 pF                      |

## Input/Output Parameters For TTL4mA

| Parameter             | Min                   | Тур | Max  | Unit | Test Conditions                                |

|-----------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>IH</sub>       | 2.0                   |     |      | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                   |

| V <sub>IL</sub>       |                       |     | 0.8  | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                   |

| Input leakage current |                       |     | 10   | μΑ   | V <sub>DD</sub> = 5.25                         |

| Input capacitance     |                       | 5.5 |      | pF   |                                                |

| V <sub>OH</sub>       | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -2.0 |

| V <sub>OL</sub>       |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0  |

| I <sub>OL</sub>       |                       |     | 4.0  | mA   |                                                |

| I <sub>OH</sub>       |                       |     | -2.0 | mA   |                                                |

| t <sub>RISE</sub>     | 2.8                   | 6.5 | 9.2  | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub>     | 1.3                   | 2.3 | 3.4  | ns   | C <sub>LOAD</sub> = 15 pF                      |

# Input/Output Parameters For TTL8mA

| Parameter             | Min                   | Тур | Max  | Unit | Test Conditions                                |

|-----------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>IH</sub>       | 2.0                   |     |      | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                   |

| V <sub>IL</sub>       |                       |     | 0.8  | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                   |

| Input leakage current |                       |     | 10   | μΑ   | V <sub>DD</sub> = 5.25                         |

| Input capacitance     |                       | 5.5 |      | pF   |                                                |

| V <sub>OH</sub>       | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>       |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0  |

| I <sub>OL</sub>       |                       |     | 8.0  | mA   |                                                |

| I <sub>OH</sub>       |                       |     | -4.0 | mA   |                                                |

| t <sub>RISE</sub>     | 2.4                   | 4.9 | 7.0  | ns   | C <sub>LOAD</sub> = 25 pF                      |

| t <sub>FALL</sub>     | 1.1                   | 1.8 | 2.5  | ns   | C <sub>LOAD</sub> = 25 pF                      |

# Output Parameters for OD16mA

| Parameter         | Min | Тур | Max  | Unit | Test Conditions                                |

|-------------------|-----|-----|------|------|------------------------------------------------|

| V <sub>OL</sub>   |     |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 16.0 |

| I <sub>OL</sub>   |     |     | 16.0 | mA   |                                                |

| t <sub>FALL</sub> | 0.8 | 1.0 | 1.5  | ns   | C <sub>LOAD</sub> = 15 pF                      |

### **TIMING CHARACTERISTICS**

Detailed timing diagrams for the SOT-1 are illustrated in Figures 3 through 20, with values of the timing intervals following each figure. All output times are measured with a maximum 15 pF load capacitance. Timing parameters are measured at  $(V_{OH} - V_{OL})/2$  or  $(V_{IH} - V_{IL})/2$ , as applicable.

RLCI

tcyc

tpwh

tsu

the tpwl

the topwl

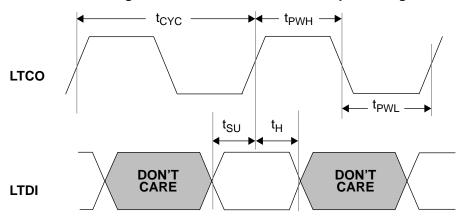

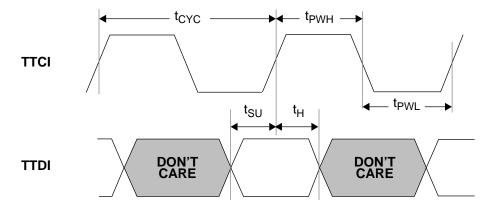

Figure 3. Line Side Input Timing

| Parameter                      | Symbol           | Min   | Тур   | Max   | Unit |

|--------------------------------|------------------|-------|-------|-------|------|

| RLCI clock period              | t <sub>CYC</sub> | 19.25 | 19.29 |       | ns   |

| RLCI high time                 | t <sub>PWH</sub> | 8.68  | 9.65  | 10.61 | ns   |

| RLCI low time                  | t <sub>PWL</sub> | 8.68  | 9.65  | 10.61 | ns   |

| RLDI/RFRI set-up time to RLCI↑ | t <sub>SU</sub>  | 4     |       |       | ns   |

| RLDI/RFRI hold time after RLCI | t <sub>H</sub>   | 2     |       |       | ns   |

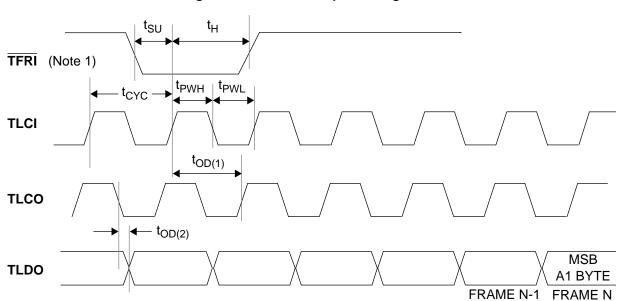

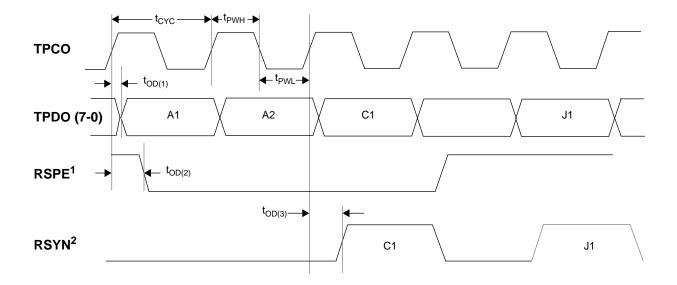

Figure 4. Line Side Output Timing

| Parameter                     | Symbol             | Min    | Тур    | Max    | Unit |

|-------------------------------|--------------------|--------|--------|--------|------|

| TLCI clock period (Note 2)    | t <sub>CYC</sub>   | 19.285 | 19.290 | 19.295 | ns   |

| TLCI high time                | t <sub>PWH</sub>   | 8.68   | 9.65   | 10.61  | ns   |

| TLCI low time                 | t <sub>PWL</sub>   | 8.68   | 9.65   | 10.61  | ns   |

| TFRI set-up time to TLCI↑     | t <sub>SU</sub>    | 4      |        |        | ns   |

| TFRI hold time after TLCI↑    | t <sub>H</sub>     | 2      |        |        | ns   |

| TLCO output delay after TLCI↑ | t <sub>OD(1)</sub> | 6      | 15     | 24     | ns   |

| TLDO output delay after TLCO↓ | t <sub>OD(2)</sub> | -1     | 0      | 3      | ns   |

Note 1.  $\overline{TFRI}$  can only be used if the control bit TCLK = 1.

Note 2. TLCI should not be operated outside of the range of 51.830 to 51.850 MHz: Data errors may occur and a reset of the device may be required after the clock frequency is returned to the normal operating range.

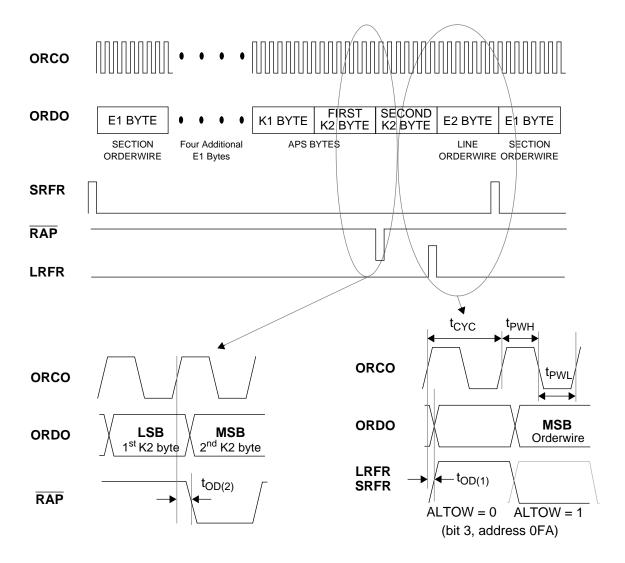

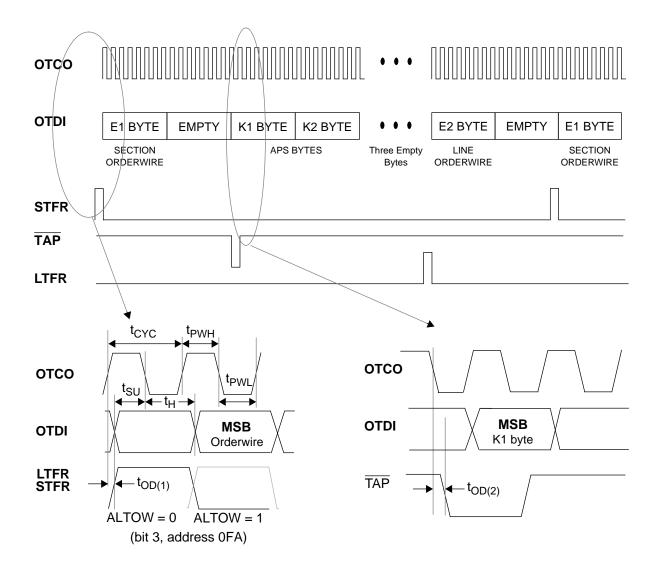

Figure 5. APS and Orderwire Output Timing

| Parameter                           | Symbol             | Min  | Тур  | Max | Unit |

|-------------------------------------|--------------------|------|------|-----|------|

| ORCO clock period                   | t <sub>CYC</sub>   | 1732 | 1736 |     | ns   |

| ORCO high time                      | t <sub>PWH</sub>   | 860  | 868  | 875 | ns   |

| ORCO low time                       | t <sub>PWL</sub>   | 860  | 868  | 875 | ns   |

| SRFR, LRFR output delay after ORCO↑ | t <sub>OD(1)</sub> | 1    |      | 5   | ns   |

| RAP output delay after ORCO↑        | t <sub>OD(2)</sub> | 1    |      | 5   | ns   |

Figure 6. APS and Orderwire Input Timing

| Parameter                           | Symbol             | Min  | Тур  | Max | Unit |

|-------------------------------------|--------------------|------|------|-----|------|

| OTCO clock period                   | t <sub>CYC</sub>   | 1732 | 1736 |     | ns   |

| OTCO high time                      | t <sub>PWH</sub>   | 860  | 868  | 875 | ns   |

| OTCO low time                       | t <sub>PWL</sub>   | 860  | 868  | 875 | ns   |

| OTDI set-up time to OTCO↓           | t <sub>SU</sub>    | 7    |      |     | ns   |

| OTDI hold time after OTCO↓          | t <sub>H</sub>     | 3    |      |     | ns   |

| STFR, LTFR output delay after OTCO↑ | t <sub>OD(1)</sub> | 2    |      | 5   | ns   |

| TAP output delay after OTCO↓        | t <sub>OD(2)</sub> | 2    |      | 5   | ns   |

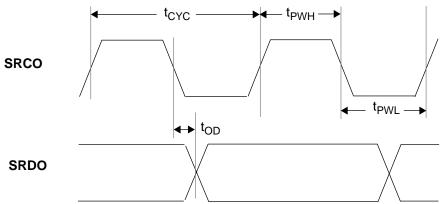

Figure 7. Section Datacom Channel Output Timing

| Parameter                     | Symbol           | Min  | Тур  | Max  | Unit |

|-------------------------------|------------------|------|------|------|------|

| SRCO clock period             | t <sub>CYC</sub> | 5.20 | 5.21 | 5.22 | μs   |

| SRCO high time                | t <sub>PWH</sub> | 2.59 | 2.60 | 2.61 | μs   |

| SRCO low time                 | t <sub>PWL</sub> | 2.59 | 2.60 | 2.61 | μs   |

| SRDO output delay after SRCO↓ | t <sub>OD</sub>  | 2    | 4    | 5    | ns   |

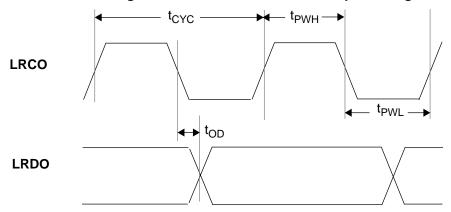

Figure 8. Line Datacom Channel Output Timing

| Parameter                     | Symbol           | Min  | Тур  | Max | Unit |

|-------------------------------|------------------|------|------|-----|------|

| LRCO clock period             | t <sub>CYC</sub> | 1732 | 1736 |     | ns   |

| LRCO high time                | t <sub>PWH</sub> | 860  | 868  | 875 | ns   |

| LRCO low time                 | t <sub>PWL</sub> | 860  | 868  | 875 | ns   |

| LRDO output delay after LRCO↓ | t <sub>OD</sub>  | 2    | 4    | 5   | ns   |

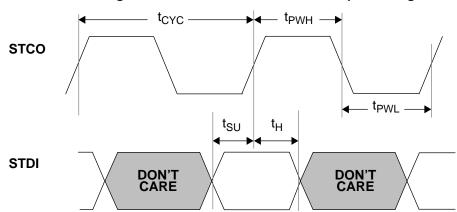

Figure 9. Section Datacom Channel Input Timing

| Parameter                  | Symbol           | Min  | Тур  | Max  | Unit |

|----------------------------|------------------|------|------|------|------|

| STCO clock period          | t <sub>CYC</sub> | 5.20 | 5.21 | 5.22 | μs   |

| STCO high time             | t <sub>PWH</sub> | 2.59 | 2.60 | 2.61 | μs   |

| STCO low time              | t <sub>PWL</sub> | 2.59 | 2.60 | 2.61 | μs   |

| STDI set-up time to STCO↑  | t <sub>SU</sub>  | 7    |      |      | ns   |

| STDI hold time after STCO↑ | t <sub>H</sub>   | 3    |      |      | ns   |

Figure 10. Line Datacom Channel Input Timing

| Parameter                  | Symbol           | Min  | Тур  | Max | Unit |

|----------------------------|------------------|------|------|-----|------|

| LTCO clock period          | t <sub>CYC</sub> | 1732 | 1736 |     | ns   |

| LTCO high time             | t <sub>PWH</sub> | 860  | 868  | 875 | ns   |

| LTCO low time              | t <sub>PWL</sub> | 860  | 868  | 875 | ns   |

| LTDI set-up time to LTCO↑  | t <sub>SU</sub>  | 7    |      |     | ns   |

| LTDI hold time after LTCO↑ | t <sub>H</sub>   | 3    |      |     | ns   |

Figure 11. Terminal Parallel STS-1 Output Timing

| Parameter                     | Symbol             | Min   | Тур   | Max  | Unit |

|-------------------------------|--------------------|-------|-------|------|------|

| TPCO clock period             | t <sub>CYC</sub>   | 154.0 | 154.3 |      | ns   |

| TPCO high time                | t <sub>PWH</sub>   | 72.2  | 77.2  | 82.2 | ns   |

| TPCO low time                 | t <sub>PWL</sub>   | 72.2  | 77.2  | 82.2 | ns   |

| TPDO output delay after TPCO↑ | t <sub>OD(1)</sub> | 7     | 12    | 19   | ns   |

| RSPE output delay after TPCO↑ | t <sub>OD(2)</sub> | 52.9  | 57.9  | 62.9 | ns   |

| RSYN output delay after TPCO↑ | t <sub>OD(3)</sub> | 52.9  | 57.9  | 62.9 | ns   |

Note 1: Pointer movements are indicated by RSPE in subframe #4.

Note 2: J1 can be anywhere in the payload.

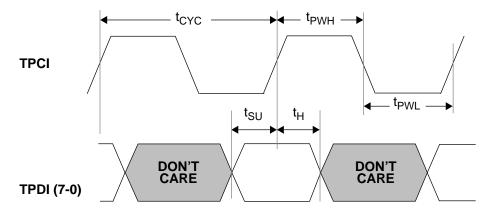

Figure 12. Terminal Parallel STS-1 Input Timing

| Parameter                  | Symbol           | Min   | Тур   | Max   | Unit |

|----------------------------|------------------|-------|-------|-------|------|

| TPCI clock period          | t <sub>CYC</sub> | 154.0 | 154.3 |       | ns   |

| TPCI high time             | t <sub>PWH</sub> | 38.5  | 77.2  | 115.7 | ns   |

| TPCI low time              | t <sub>PWL</sub> | 38.5  | 77.2  | 115.7 | ns   |

| TPDI set-up time to TPCI↑  | t <sub>SU</sub>  | 20    |       |       | ns   |

| TPDI hold time after TPCI↑ | t <sub>H</sub>   | 0     |       |       | ns   |

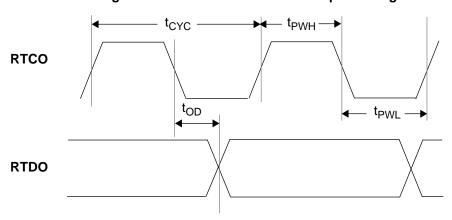

Figure 13. Terminal Serial STS-1 Output Timing

| Parameter                     | Symbol           | Min   | Тур   | Max   | Unit |

|-------------------------------|------------------|-------|-------|-------|------|

| RTCO clock period             | t <sub>CYC</sub> | 19.25 | 19.29 |       | ns   |

| RTCO high time                | t <sub>PWH</sub> | 8.68  | 9.65  | 10.61 | ns   |

| RTCO low time                 | t <sub>PWL</sub> | 8.68  | 9.65  | 10.61 | ns   |

| RTDO output delay after RTCO↓ | t <sub>OD</sub>  | -1    |       | 3     | ns   |

Figure 14. Terminal Serial STS-1 Input Timing

| Parameter                  | Symbol           | Min   | Тур   | Max   | Unit |

|----------------------------|------------------|-------|-------|-------|------|

| TTCI clock period          | t <sub>CYC</sub> | 19.25 | 19.29 |       | ns   |

| TTCI high time             | t <sub>PWH</sub> | 8.68  | 9.65  | 10.61 | ns   |

| TTCI low time              | t <sub>PWL</sub> | 8.68  | 9.65  | 10.61 | ns   |

| TTDI set-up time to TTCI↑  | t <sub>SU</sub>  | 4     |       |       | ns   |

| TTDI hold time after TTCI↑ | t <sub>H</sub>   | 2     |       |       | ns   |

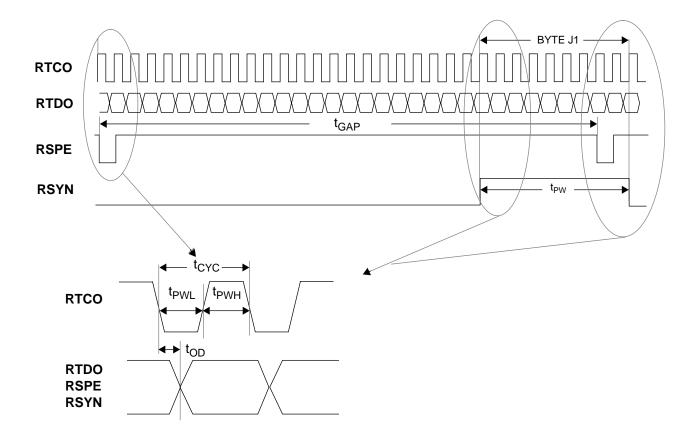

Figure 15. Terminal Serial SPE-Only Output Timing

| Parameter                                | Symbol           | Min                 | Тур                 | Max                 | Unit |

|------------------------------------------|------------------|---------------------|---------------------|---------------------|------|

| RTCO clock period                        | t <sub>CYC</sub> | 19.25               | 19.29               |                     | ns   |

| RTCO high time                           | t <sub>PWH</sub> | 8.68                | 9.65                | 10.61               | ns   |

| RTCO low time                            | t <sub>PWL</sub> | 8.68                | 9.65                | 10.61               | ns   |

| RTDO,RSPE, RSYN output delay after RTCO↓ | t <sub>OD</sub>  | -1                  |                     | 5                   | ns   |

| RSPE gap between pulses                  | t <sub>GAP</sub> | 22 t <sub>CYC</sub> | 30 t <sub>CYC</sub> | 45 t <sub>CYC</sub> |      |

| RSYN pulse width                         | t <sub>PW</sub>  | 8 t <sub>CYC</sub>  |                     | 9 t <sub>CYC</sub>  |      |

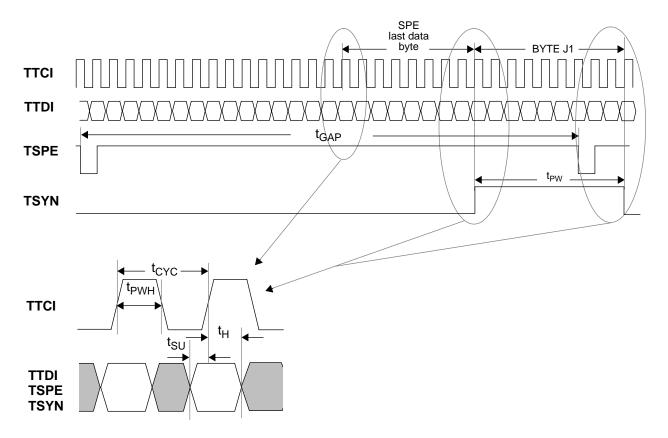

Figure 16. Terminal Serial SPE-Only Input Timing

| Parameter                             | Symbol           | Min                 | Тур                 | Max                 | Unit |

|---------------------------------------|------------------|---------------------|---------------------|---------------------|------|

| TTCI clock period                     | t <sub>CYC</sub> | 19.25               | 19.29               |                     | ns   |

| TTCI high time                        | t <sub>PWH</sub> | 8.68                | 9.65                | 10.61               | ns   |

| TTCI low time                         | t <sub>PWL</sub> | 8.68                | 9.65                | 10.61               | ns   |

| TTDI, TSPE, TSYN set-up time to TTCI↑ | t <sub>SU</sub>  | 4                   |                     |                     | ns   |

| TTDI, TSPE, TSYN hold time after TTCI | t <sub>H</sub>   | 2                   |                     |                     | ns   |

| TSPE gap between pulses               | t <sub>GAP</sub> | 22 t <sub>CYC</sub> | 30 t <sub>CYC</sub> | 45 t <sub>CYC</sub> |      |

| TSYN pulse width                      | t <sub>PW</sub>  |                     | 8 t <sub>CYC</sub>  | 9 t <sub>CYC</sub>  |      |

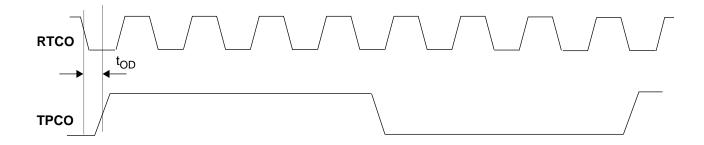

Figure 17. Receive Terminal Clock Output Timing

| Parameter                     | Symbol          | Min | Тур | Max | Unit |

|-------------------------------|-----------------|-----|-----|-----|------|

| TPCO output delay after RTCO↓ | t <sub>OD</sub> | -1  |     | 5   | ns   |

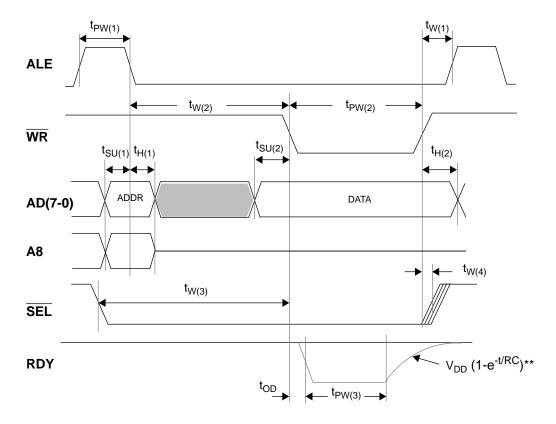

Figure 18. Microprocessor Write Cycle Timing

| Parameter                  | Symbol             | Min | Тур | Max  | Unit |

|----------------------------|--------------------|-----|-----|------|------|

| ALE pulse width            | t <sub>PW(1)</sub> | 20  |     |      | ns   |

| ALE wait after WR↑         | t <sub>W(1)</sub>  | 0   |     |      | ns   |

| WR wait time after ALE↓    | t <sub>W(2)</sub>  | 20  |     |      | ns   |

| WR pulse width             | t <sub>PW(2)</sub> | 20  |     |      | ns   |

| AD set-up time to ALE↓     | t <sub>SU(1)</sub> | 7   |     |      | ns   |

| AD hold time after ALE↓    | t <sub>H(1)</sub>  | 3   |     |      | ns   |

| AD hold time after WR↑     | t <sub>H(2)</sub>  | 3   |     |      | ns   |

| RDY output delay after WR↓ | t <sub>OD</sub>    | 2   |     | 7    | ns   |

| RDY pulse width*           | t <sub>PW(3)</sub> | 0   |     | 2500 | ns   |

| Data set-up to WR↓         | t <sub>SU(2)</sub> | 0   |     |      | ns   |

| WR↓ wait time after SEL↓   | t <sub>W(3)</sub>  | 0   |     |      | ns   |

| SEL↑ wait time after WR↑   | t <sub>W(4)</sub>  | 0   |     |      | ns   |

<sup>\*</sup>RDY goes low when the address being written to corresponds to a RAM location but remains high during status or control register access.

<sup>\*\*</sup>Open drain rise time is dependent upon external pull-up resistor and load capacitance.

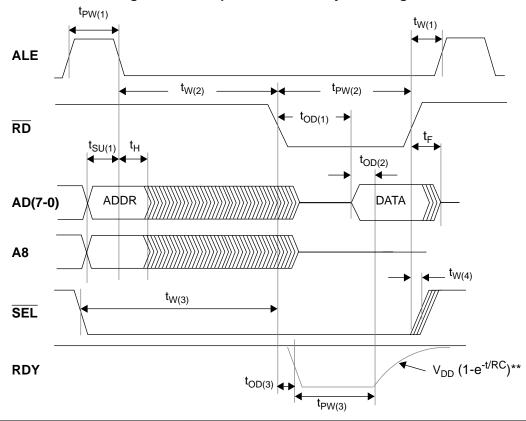

Figure 19. Microprocessor Read Cycle Timing

| Parameter                                        | Symbol             | Min | Тур | Max  | Unit |

|--------------------------------------------------|--------------------|-----|-----|------|------|

| ALE pulse width                                  | t <sub>PW(1)</sub> | 20  |     |      | ns   |

| ALE wait after RD↑                               | t <sub>W(1)</sub>  | 0   |     |      | ns   |

| RD wait time after ALE↓                          | t <sub>W(2)</sub>  | 7   |     |      | ns   |

| RD pulse width                                   | t <sub>PW(2)</sub> | 40  |     |      | ns   |

| AD set-up time to ALE↓                           | t <sub>SU(1)</sub> | 7   |     |      | ns   |

| AD hold time after ALE↓                          | t <sub>H</sub>     | 3   |     |      | ns   |

| AD output delay after $\overline{RD} \downarrow$ | t <sub>OD(1)</sub> | 5   |     | 2500 | ns   |

| RDY <sup>↑</sup> output delay after AD           | t <sub>OD(2)</sub> | 0   | 20  |      | ns   |

| AD float after RD↑                               | t <sub>F</sub>     | 2   |     | 7    | ns   |

| RDY output delay after RD↓                       | t <sub>OD(3)</sub> | 2   |     | 7    | ns   |

| RDY pulse width*                                 | t <sub>PW(3)</sub> | 0   |     | 2500 | ns   |

| RD↓ wait time after SEL↓                         | t <sub>W(3)</sub>  | 0   |     |      | ns   |

| SEL↑ wait time after RD↑                         | t <sub>W(4)</sub>  | 0   |     |      | ns   |

<sup>\*</sup>RDY goes low when the address being read corresponds to a RAM location but remains high during status or control register access.

<sup>\*\*</sup>Open drain rise time is dependent upon external pull-up resistor and load capacitance.

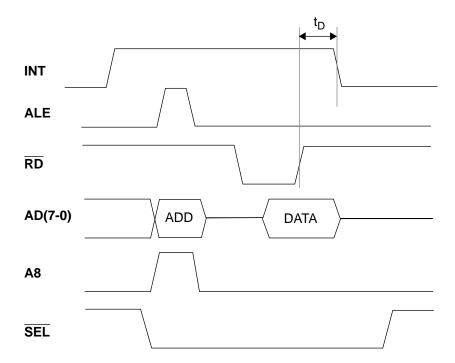

Figure 20. Microprocessor Interrupt Timing

| Parameter           | Symbol         | Min | Тур | Max | Unit |

|---------------------|----------------|-----|-----|-----|------|

| INT delay after RD↑ | t <sub>D</sub> | 2   |     | 7   | ns   |

## **OPERATION**

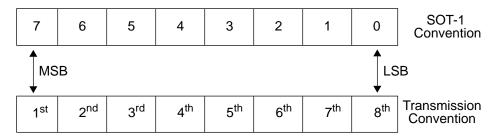

#### Conventions

All address locations are given in Hex (H). The relationship between a transmission byte (e.g., C1) and the corresponding SOT-1 location is the following:

Order of transmission

### **Register Bit Map**

| Address<br>(Hex) | Mode <sup>1</sup> | Bit 7 | Bit 6      | Bit 5      | Bit 4                   | Bit 3       | Bit 2      | Bit 1       | Bit 0    | Comments <sup>2</sup> |

|------------------|-------------------|-------|------------|------------|-------------------------|-------------|------------|-------------|----------|-----------------------|

| 0F0              | R/W               | RLOC  | RNPTR      | RPAIS      | RLAIS                   | RLOP        | RLOF       | ROOF        | RLOS     | SR0                   |

| 0F1              | R/W               | Same  | as 0F0 exc | ept does n | ot reset on             | read; write | ones to re | set individ | ual bits | SR0                   |

| 0F2              | R/W               | INT   | RTNEW      | RPNEW      | RPYE                    | RFERF       | RAPS       |             |          | SR1                   |

| 0F3              | R/W               | Same  | as 0F2 exc | ept does n | ot reset on             | read; write | ones to re | set individ | ual bits | SR1                   |

| 0F4              | R                 |       |            | Same a     | s 0F0 exce <sub>l</sub> | pt unlatche | d values   |             |          | SR0                   |

| 0F5              | R                 |       |            | Same a     | s 0F2 exce <sub>l</sub> | pt unlatche | d values   |             |          | SR1                   |

| 0F8              | R/W               | RRSD  | RRLD       | RRE1       | RRE2                    | RPATH       | RRAPS      | RRPTR       | TRLOOP   | CR0                   |

| 0F9              | R/W               | RRF1  | RRC1       | RRZ1       | RRZ2                    | RRAIS       | LTE        | RRFRM       | RRB1     | CR1                   |

| 0FA              | R/W               | STS1  | PARA       | HINT       | TRFERF                  | ALTOW       | TIEN       | PIEN        | -VE      | CR2                   |

| 1F0              | R/W               | TLOC  | TNPTR      | TPAIS      | TLAIS                   | TLOP        | TLOF       | TOOF        | TLOS     | SR2                   |

| 1F1              | R/W               | Same  | as 1F0 exc | ept does n | ot reset on             | read; write | ones to re | set individ | ual bits | SR2                   |

| 1F4              | R                 |       |            | Same a     | s 1F0 exce <sub>l</sub> | pt unlatche | d values   |             |          | SR2                   |

| 1F8              | R/W               | TRSD  | TRLD       | TRE1       | TRE2                    | TPATH       | TRAPS      | EXAPS       | RTLOOP   | CR3                   |

| 1F9              | R/W               | TRF1  | TRC1       | TRZ1       | TRZ2                    | TRAIS       | PTE        | RXRTM       | RRB2     | CR4                   |

| 1FA              | R/W               | SPE   | TCLK       | RCLK       | Reserved                | TXRTM       | Reserved   | INC         | DEC      | CR5                   |

| 1FB              | R/W               | TRFRM | TRERR      | TAIS       | Unused                  | RE2A        | RA2E       | TE2A        | TA2E     | CR6                   |

- 1. Read/write (R/W); Read only (R).

- 2. SR = Status Register; CR = Control Register

## **REGISTER BIT MAP DESCRIPTIONS**

## **Control Register 0**

| Address | Bit | Name   | Description                                                                                                                           | on                                                                              | Comments                                                          |

|---------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------|

| (Hex)   | ы   | Name   | Bit Equal to 1 (High)                                                                                                                 | Bit Equal to 0 (Low)                                                            | Comments                                                          |

| 0F8     | 7   | RRSD   | Receiver Terminal-Side Section Datacom Bytes Control: Outgoing terminal data has section datacom bytes from the RAM. (D1-D3)          | Outgoing terminal data has section datacom bytes from the receive line.         | See Note 1.                                                       |

| 0F8     | 6   | RRLD   | Receiver Terminal-Side Line<br>Datacom Bytes Control: Out-<br>going terminal data has line<br>datacom bytes from the RAM.<br>(D4-D12) | Outgoing terminal data has line datacom bytes from the receive line.            | See Note 1.                                                       |

| 0F8     | 5   | RRE1   | Receiver Terminal-Side E1 Byte Control: Outgoing terminal data has section orderwire byte from the RAM. RA2E must be low.             | Outgoing terminal data has section orderwire byte from the receive line.        | See Note 1.                                                       |

| 0F8     | 4   | RRE2   | Receiver Terminal-Side E2 Byte Control: Outgoing terminal data has line orderwire byte from the RAM.                                  | Outgoing terminal data has line orderwire byte from the receive line.           | See Note 1.                                                       |

| 0F8     | 3   | RPATH  | Receiver Terminal-Side Path<br>Overhead Control: Outgoing<br>terminal data has path over-<br>head (except H4) bytes from<br>the RAM.  | Outgoing terminal data has path over-head bytes from the receive line.          | Multi-frame indi-<br>cator byte (H4)<br>always passes<br>through. |

| 0F8     | 2   | RRAPS  | Receiver Terminal-Side APS<br>Bytes Control: Outgoing ter-<br>minal data has APS bytes (K1<br>and K2) from the RAM.                   | Outgoing terminal data has APS bytes (K1 and K2) from the receive line.         | See Note 1.                                                       |

| 0F8     | 1   | RRPTR  | Receiver Terminal-Side Pointer Control: Outgoing terminal data has pointer bytes (H1 and H2) from the RAM.                            | Outgoing terminal data has pointer bytes from the receive line or recalculated. | See Notes 1<br>and 2. Only<br>pointer value is<br>introduced.     |

| 0F8     | 0   | TRLOOP | Transmit-Receive Loopback Enable: Line output looped back to receive line input.                                                      | Normal operation.                                                               | RFRI is disabled during loopback.                                 |

- 1. The TOH bytes are inserted into the terminal data only in the pass-through mode.

- 2. This mode does not modify the payload; it simply inserts H1 and H2 bytes from insert RAM locations. It can be used for self test.

| Address | Bit | Name  | Descrip                                                                                                                                                                                                    | tion                                                                  | Comments                                                                                                                                          |

|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| (Hex)   | Бії | Name  | Bit Equal to 1 (High)                                                                                                                                                                                      | Bit Equal to 0 (Low)                                                  | Comments                                                                                                                                          |

| 0F9     | 7   | RRF1  | Receiver Terminal-Side F1 Byte Control: Outgoing terminal data has section user byte (F1) from the RAM.                                                                                                    | Outgoing terminal data has section user byte from the receive line.   | See Note 1.                                                                                                                                       |

| 0F9     | 6   | RRC1  | Receiver Terminal-Side C1 Byte Control: Outgoing terminal data has STS-1 ID byte (C1) from the RAM.                                                                                                        | Outgoing terminal data has STS-1 ID byte (C1) from the receive line.  | See Note 1.                                                                                                                                       |

| 0F9     | 5   | RRZ1  | Receiver Terminal-Side Z1 Byte Control: Outgoing terminal data has growth byte Z1 from the RAM.                                                                                                            | Outgoing terminal data has growth byte Z1 from the receive line.      | See Note 1.                                                                                                                                       |

| 0F9     | 4   | RRZ2  | Receiver Terminal-Side Z2 Byte Control: Outgoing terminal data has growth byte Z2 from the RAM.                                                                                                            | Outgoing terminal data has growth byte Z2 from the receive line.      | See Note 1.                                                                                                                                       |

| 0F9     | 3   | RRAIS | Receiver Terminal-Side AIS Output Control: Enables automatic insertion of AIS into outgoing termi- nal data, as shown in the Receive Alarm Propaga- tion Table section below for action codes 'L' and 'P'. | Disables automatic insertion of AIS into outgoing terminal data.      | See Note 2.                                                                                                                                       |

| 0F9     | 2   | LTE   | Line Terminating Equipment Enable: Line terminating equipment for AIS transmission and introduction.                                                                                                       | Not line terminating equipment for AIS transmission and introduction. | Section terminating equipment if LTE=0 and PTE = 0. LTE and PTE control alarm propagation as shown in the Alarm Propagation Tables section below. |

| 0F9     | 1   | RRFRM | Receive Terminal-Side Framing Byte Control: Outgoing terminal data has framing bytes regenerated.                                                                                                          | Outgoing terminal data has framing bytes from the receive line.       | See Note 1.                                                                                                                                       |

| 0F9     | 0   | RRB1  | Receive Terminal-Side B1 Parity Byte Control: Outgoing terminal data has B1 byte recalculated.                                                                                                             | Outgoing terminal data has B1 byte from the receive line.             | See Notes 1 and 3.                                                                                                                                |

- 1. The TOH bytes are inserted into the terminal data only in the pass-through mode.

- 2. The SPE bytes are set to all ones when an AIS is sent. All TOH bytes except A1, A2, E1, H1, and H2 are set to zero.

- 3. When operating the SOT-1 in STS-1 mode RRB1 should be set high or else B1 errors will be transmitted on the receive terminal side.

| Address | Bit | Name   | Descrip                                                                                                                                                                                                                | tion                                                                                                                             | Comments                                               |

|---------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| (Hex)   | Ыl  | Name   | Bit Equal to 1 (High)                                                                                                                                                                                                  | Bit Equal to 0 (Low)                                                                                                             | Comments                                               |

| 0FA     | 7   | STS1   | STS-1/STS-N Mode Control: Line side in STS-1 mode. Received data is descrambled and transmit data is scrambled. Received B1 contains BIP-8 parity. Transmit B1 is recalculated.                                        | Line Side in STS-N mode. Data is NOT scrambled. Received B1 byte contains BIP-8 errors. Transmit B1 byte contains error mask.    | Controls<br>both receive<br>and transmit<br>line side. |

| OFA     | 6   | PARA   | Parallel/Serial Mode Control: Terminal side interface is parallel. In receive direction, both serial and parallel interfaces are active.                                                                               | Terminal side interface is serial. In receive direction, both serial and parallel interfaces are active except in SPE-only mode. |                                                        |

| 0FA     | 5   | HINT   | Hardware Interrupt Enable: Enables hardware interrupt.                                                                                                                                                                 | Disables hardware inter-<br>rupt.                                                                                                |                                                        |

| 0FA     | 4   | TRFERF | Transmit Line-Side FERF Enable: Enables automatic introduction of line FERF into line side output under the conditions indicated in the Receive Alarm Propagation Table section below as resulting in action code 'F'. | Disables automatic intro-<br>duction to line FERF into<br>line side output.                                                      |                                                        |

| 0FA     | 3   | ALTOW  | Orderwire Mode Control: Selects alternate orderwire interface -frame coincident with data MSB.                                                                                                                         | Selects normal orderwire interface - frame ahead of data MSB by one bit.                                                         | See Figures<br>5 and 6.                                |

| 0FA     | 2   | TIEN   | Transport Layer Interrupt Enable: Enables interrupts for alarms detected in the transport overhead bytes.                                                                                                              | Disables interrupts for alarms detected in the transport overhead bytes.                                                         | See Note 1.                                            |

| 0FA     | 1   | PIEN   | Path Layer Interrupt Enable:<br>Enables interrupts for alarms<br>detected in the path overhead<br>bytes.                                                                                                               | Disables interrupts for alarms detected in the path overhead bytes.                                                              | See Note 2.                                            |

| 0FA     | 0   | -VE    | Interrupt Edge Control: Interrupts on both positive and negative edges of alarms.                                                                                                                                      | Interrupts only on positive going edge of alarms.                                                                                | See Note 3.                                            |

- 1. The conditions for transport layer interrupt are transport layer alarms (RLOS, ROOF, RLOF, RLAIS, RFERF, RAPS, RPAIS, RLOP, TLOS, TOOF, TLOF, TLAIS, TPAIS, and TLOP), overflow of transport layer performance monitors (receive B1 counter, receive B2 counter, receive INC counter, receive DEC counter, transmit INC counter, transmit DEC counter, transmit B1 counter, and transmit B2 counter) and new debounced values of C1, F1, K1, K2, Z1, and Z2 receive overhead bytes.

- 2. The conditions for path layer interrupt are path yellow alarm, overflow of path layer performance monitors (receive B3 counter, receive FEBE counter, and transmit B3 counter), and new debounced values of C2, F2, Z3, Z4, and Z5 receive path overhead bytes.

- 3. Performance counter overflows, alarms RPNEW and RTNEW if enabled by PIEN or TIEN respectively, only cause interrupts on the positive edge of the alarm regardless of the setting of -VE.

| Address<br>(Hex) | Bit | Name   | Description                                                                                                                                |                                                                  | Comments                                               |

|------------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------|

|                  |     |        | Bit Equal to 1 (High)                                                                                                                      | Bit Equal to 0 (Low)                                             | Comments                                               |

| 1F8              | 7   | TRSD   | Transmit Line-Side Section Datacom Bytes Control: Outgoing line data has section datacom bytes from the section datacom interface. (D1-D3) | Outgoing line data has section datacom bytes from the terminal.  | See Notes 1, 2, and 4.                                 |

| 1F8              | 6   | TRLD   | Transmit Line-Side Line Datacom Bytes Control: Outgoing line data has line datacom bytes from the line datacom interface. (D4-D12).        | Outgoing line data has line datacom bytes from the terminal.     | See Notes 1, 2, and 4.                                 |

| 1F8              | 5   | TRE1   | Transmit Line Side E1 Byte Control: Outgoing line data has section orderwire byte from the orderwire interface.                            | Outgoing line data has section orderwire byte from the terminal. | See Notes 1, 2, and 4.                                 |

| 1F8              | 4   | TRE2   | Transmit Line-Side E2 Byte Control: Outgoing line data has line orderwire byte from the orderwire interface.                               | Outgoing line data has line orderwire byte from the terminal.    | See Notes 1, 2, and 4.                                 |

| 1F8              | 3   | TPATH  | Transmit Line-Side Path Overhead Control: Outgoing line data has path overhead (except H4) bytes from the RAM.                             | Outgoing line data has path overhead bytes from the terminal.    | Multi-frame indicator byte (H4) always passes through. |

| 1F8              | 2   | TRAPS  | Transmit Line-Side APS Control: Outgoing line data has APS bytes from the RAM.                                                             | Outgoing line data has APS bytes from the terminal.              | See Notes 2, 3, and 4.                                 |

| 1F8              | 1   | EXAPS  | External APS-to-RAM Enable: APS bytes from the orderwire interface loaded to the RAM every frame.                                          | RAM location for APS bytes not modified.                         | See Notes 2, 3, and 4.                                 |

| 1F8              | 0   | RTLOOP | Receive-to-Transmit Loop-<br>back Enable: Receive termi-<br>nal output looped back to<br>transmit terminal input.                          | Normal operation.                                                |                                                        |

- 1. Orderwire or datacom channels can come either from the terminal or the respective serial interface.