DATA SHEET

#### **FEATURES**

- DS3 payload access, bit-serial or nibble-parallel

- · C-bit parity or M13 operating mode

- C-bit interface (13 C-bits in, 14 out)

- Detect and generate DS3 AIS, and idle signals

- Transmit reference generator for serial operation

- Transmit and receive Far End Alarm and Control (FEAC) with double word capability and automatic transmission

- Maskable hardware interrupt for eight alarms

- Transmit single errors: framing, FEBE, C-bit parity, and P-bit parity

- FEBE, C-bit, and P-bit performance counters

- Counters for F-bit and M-bit errors

- Counter for coding violations and excessive zeros

- Transmit-to-Receive and Receive-to-Transmit loopbacks

- Outputs can be set to high-impedance state

- Selectable mode for TXC-03401 emulation

- Single +5 volt power supply

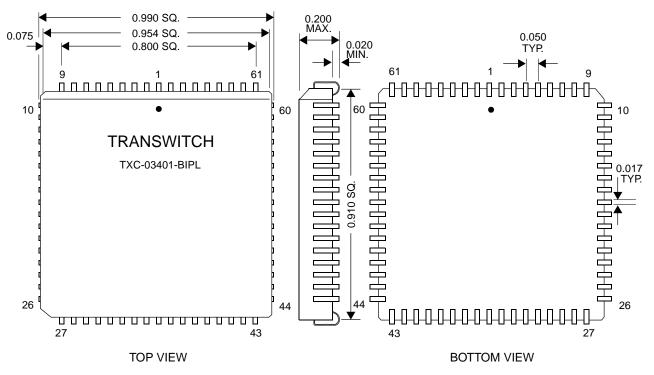

- 68-pin plastic leaded chip carrier

#### **DESCRIPTION**

The DS3F is designed for DS3 framer applications in which broadband payloads are mapped into the 44.736 Mbit/s DS3 frame format. Although the C-bit parity format is recommended, the DS3F can also operate in the M13 mode. In the C-bit parity format, the DS3F provides a separate interface for selected C-bits. The DS3F also provides for transmitting and receiving the FEAC channel and Blue code AIS conditions, and generates and detects DS3 AIS, DS3 idle, P-bit parity and C-bit parity. In addition, performance counters are provided, as well as the ability to generate single framing, FEBE, C-bit parity and P-bit parity errors. The device also provides X-bit inversion, receive loop timing and indications for FEAC idle channel, FEAC word stack overflow and Severely Errored Frame. The payload interface is selectable through software as either a bit-serial or nibble-parallel format.

#### **APPLICATIONS**

- Subrate multiplexing

- Wideband data or video transport

- DS3 monitor and test

- Channel extenders

- DS3 test sets

## TABLE OF CONTENTS

| Block Diagram       3         Block Diagram Description       3         Pin Diagram       6         Pin Descriptions       6         Absolute Maximum Ratings and Environmental Limitations       14         Thermal Characteristics       14         Recommended Operating Conditions and Power Requirements       14         Input, Output and I/O Parameters       15         Timing Characteristics       17         Operation       30         Power, Ground and External Components       30         Throughput Delays       30         Memory Map       31         Memory Map Descriptions       32         Package Information       43         Ordering Information       44         Standards Documentation Sources       45         List of Data Sheet Changes       47         Documentation Update Registration Form*       51 | SECTION                                                | <u>PAGE</u> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------|

| Block Diagram Description3Pin Diagram6Pin Descriptions6Absolute Maximum Ratings and Environmental Limitations14Thermal Characteristics14Recommended Operating Conditions and Power Requirements14Input, Output and I/O Parameters15Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map32Package Information43Ordering Information44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                            | Block Diagram                                          | 3           |

| Pin Diagram6Pin Descriptions6Absolute Maximum Ratings and Environmental Limitations14Thermal Characteristics14Recommended Operating Conditions and Power Requirements14Input, Output and I/O Parameters15Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                         |                                                        |             |

| Absolute Maximum Ratings and Environmental Limitations14Thermal Characteristics14Recommended Operating Conditions and Power Requirements14Input, Output and I/O Parameters15Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin Diagram                                            | 6           |

| Thermal Characteristics14Recommended Operating Conditions and Power Requirements14Input, Output and I/O Parameters15Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin Descriptions                                       | 6           |

| Recommended Operating Conditions and Power Requirements14Input, Output and I/O Parameters15Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Absolute Maximum Ratings and Environmental Limitations | 14          |

| Input, Output and I/O Parameters15Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Thermal Characteristics                                | 14          |

| Timing Characteristics17Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |             |

| Operation30Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input, Output and I/O Parameters                       | 15          |

| Power, Ground and External Components30Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |             |

| Throughput Delays30Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Operation                                              |             |

| Memory Map31Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                        |             |

| Memory Map Descriptions32Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Throughput Delays                                      |             |

| Package Information43Ordering Information44Related Products44Standards Documentation Sources45List of Data Sheet Changes47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |             |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Memory Map Descriptions                                |             |

| Related Products       44         Standards Documentation Sources       45         List of Data Sheet Changes       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Package Information                                    |             |

| Standards Documentation Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ordering Information                                   |             |

| List of Data Sheet Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Related Products                                       |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                        |             |

| Documentation Update Registration Form*51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | List of Data Sheet Changes                             | 47          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Documentation Update Registration Form*                | 51          |

\* Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

#### **LIST OF FIGURES**

| Figure 1.  | DS3F TXC-03401B Block Diagram                         | 3   |

|------------|-------------------------------------------------------|-----|

| Figure 2.  | DS3F TXC-03401B Pin Diagram                           | 6   |

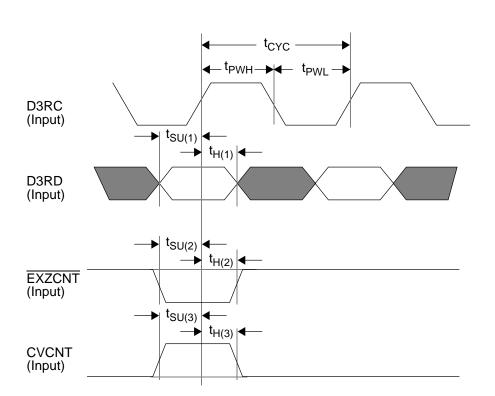

| Figure 3.  | Line Side DS3 Receive Input Timing                    | .17 |

| Figure 4.  | Line Side DS3 Transmit Output Timing                  | .18 |

| Figure 5.  | Terminal Side Receive Nibble Output Timing            | .19 |

| Figure 6.  | Terminal Side Transmit Nibble Input Timing            | 20  |

| Figure 7.  | Terminal Side Receive Serial Output Timing            | .21 |

| Figure 8.  | Terminal Side Transmit Serial Input Timing            | 22  |

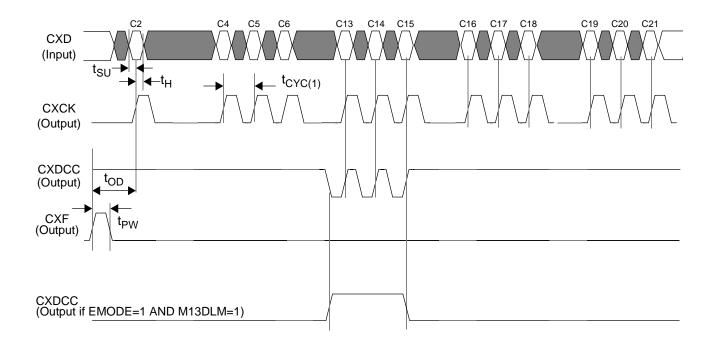

| Figure 9.  | C-Bit Transmit Input Timing                           |     |

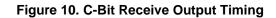

| Figure 10. | C-Bit Receive Output Timing                           | .24 |

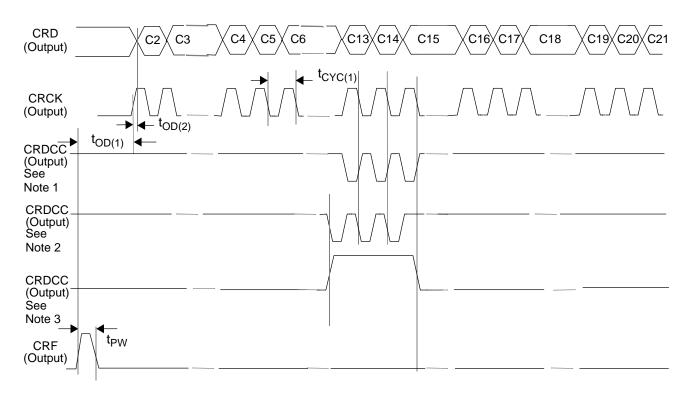

| Figure 11. | Transmit Reference Generator Timing                   | 25  |

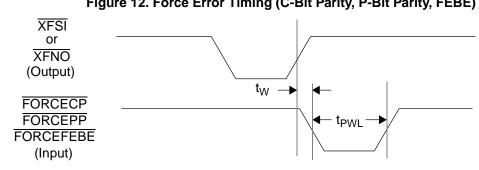

| Figure 12. | Force Error Timing (C-Bit Parity, P-Bit Parity, FEBE) | .26 |

| Figure 13. | Force Overhead Bit Error Timing                       | 26  |

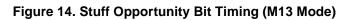

| Figure 14. | Stuff Opportunity Bit Timing (M13 Mode)               | .27 |

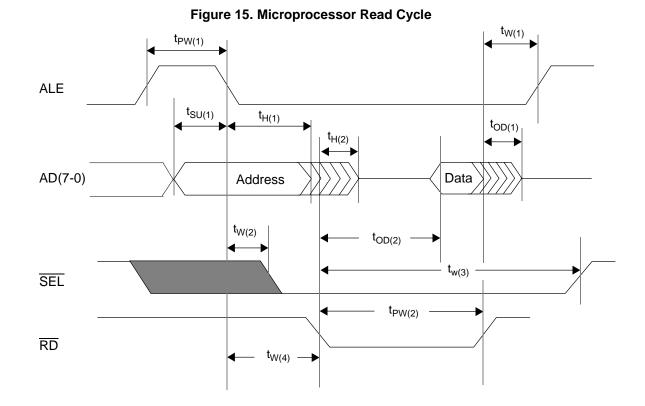

| Figure 15. | Microprocessor Read Cycle                             | 28  |

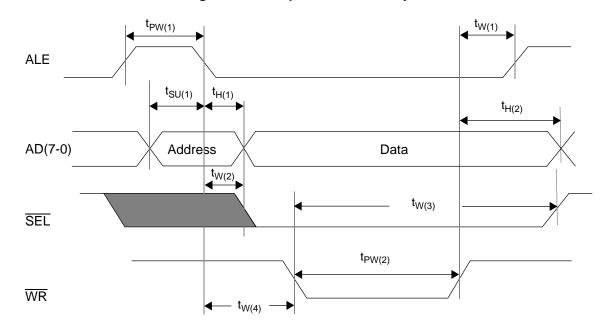

| Figure 16. | Microprocessor Write Cycle                            | .29 |

| Figure 17. | Power Supply Connections                              | .30 |

| Figure 18. | DS3F TXC-03401B 68-Pin Plastic Leaded Chip Carrier    | .43 |

## TRANSWITCH

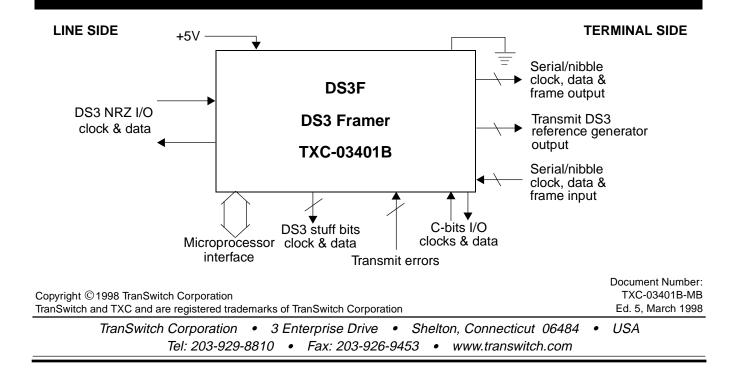

## **BLOCK DIAGRAM**

Figure 1. DS3F TXC-03401B Block Diagram

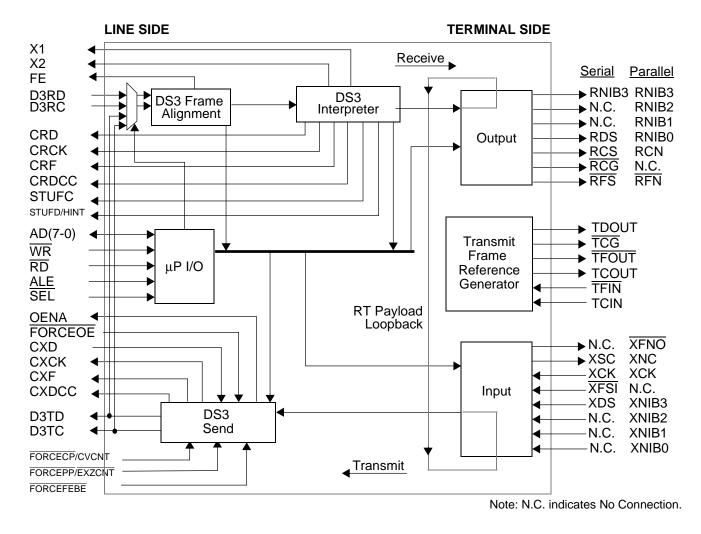

## **BLOCK DIAGRAM DESCRIPTION**

Figure 1 shows the block diagram of the DS3F device.

The DS3F is designed to operate in both "Normal" (N) and "Extended-features" (E) modes of operation. In the Normal mode, the device emulates the TranSwitch TXC-03401 DS3F device. In the Extended-features mode, all the additional capabilities described in this Data Sheet are available. Technical Bulletin TB-511 describes the differences between the TXC-03401 and the TXC-03401B (document number TXC-03401-TB1). Either mode of operation can be selected by setting control bit EMODE in the memory map. Two input pins (FORCECP/CVCNT and FORCEPP/EXZCNT) and one output pin (STUFD/HINT) can change their functions according to the mode selected (N/E). Memory map addresses above 07H are effective only in the Extended-features mode.

The DS3F receives a line side DS3 data signal (D3RD) and a clock signal (D3RC) from a line interface device such as the TranSwitch ART/ARTE VLSI device (TXC-02020/02021) or DS3LIM-SN module (TXC-20153D or TXC-20153G). The DS3 Frame Alignment Block performs DS3 frame alignment that will not lock to a false framing pattern. There are internal 8-bit F- and M-bit error counters included in the Extended-features mode of the framer to monitor errors. The DS3F also monitors the signal and the input clock for loss of signal (LOS), out of frame (OOF), and loss of clock (LOC). A framing error (FE) output is provided to indicate when any of the 31 framing bits in the DS3 signal are in error.

TRANSWITCH

The DS3 Interpreter Block performs P-bit and C-bit parity detection and error counting, receive AIS and idle pattern detection, far end block error (FEBE) detection and error counting, far end alarm and control (FEAC) code word detection of up to 4 different types, C-bit reception and X-bit reception. Serial interfaces are provided for the received X-bits and for 14 of the 21 C-bits. In the Extended-features mode, groups of the C-bits can be set by writing to the memory map. The receive C-bit interface consists of a serial data signal (CRD), clock signal (CRCK), framing pulse (CRF), and a data communication link clock signal (CRDCC). The clock signal (CRCK) is gapped and is available only for clocking out C-bits C2 through C6, and C13 through C21. The CRDCC clock signal is present only for C-bits C13, C14 and C15, which are assigned as a data communication channel when operating in the C-bit parity mode. In the Extended-features mode, the timing of the CRDCC receive clock edges can be reversed by setting a control bit in the memory map.

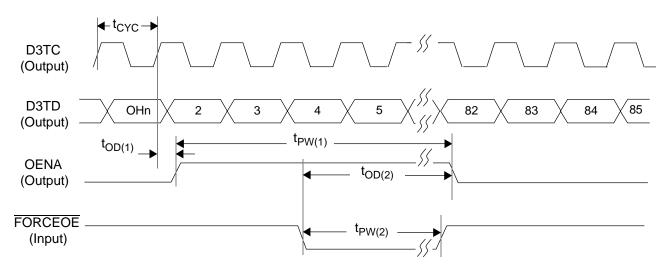

When operating in the M13 mode, an interface (output pin STUFD) that indicates the state of the stuff opportunity bit during each of the seven DS3 subframes and a clock signal (STUFC) are also provided. The Stuff Data Status (STUFD) output pin is shared with the Hardware Interrupt (HINT) pin for the Extended-features mode. The Hardware Interrupt output is used to the inform the microprocessor that a severe alarm condition has occurred. The polarity of the Hardware Interrupt output is selectable by a control bit to meet the requirements of the microprocessor's interrupt input pin. When a hardware interrupt does occur, it can be isolated to one of up to up to eight different latched alarm types if they are enabled in the memory map.

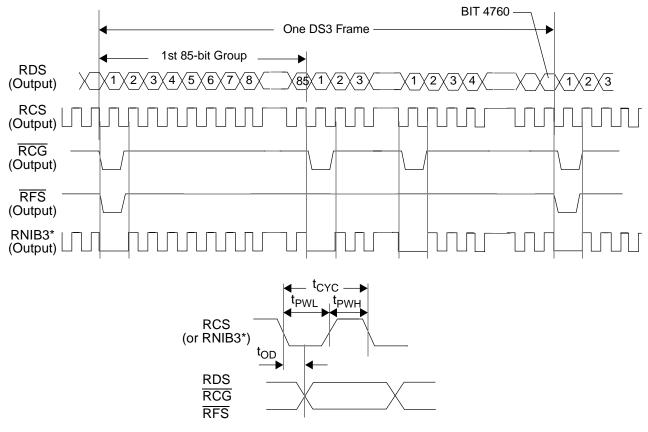

The Output Block provides a bit-serial or a nibble-parallel interface for C-bit parity mode. The M13 mode uses the bit-serial interface only. Note that since the sum of the payload and C-bits in a DS3 frame is not evenly divisible by four, M13 nibble mode operation is not feasible. The interface type is selected by writing to a control bit in the memory map (SER), and is common to the DS3F receive and transmit circuitry. The signals provided for the bit-serial interface consist of a data signal (RDS), a clock signal (RCS), a receive clock gap signal (RCG) and framing pulse (RFS). The nibble-parallel interface consists of the nibble data signal (RNIB3 through RNIB0), a clock out signal (RCN), and a framing pulse output (RFN). The RNIB3 bit corresponds to the first bit received in a four-bit serial bit stream segment.

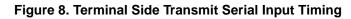

In the transmit direction, the Input Block provides either a bit-serial or nibble-parallel interface. The bit-serial interface consists of a data signal (XDS), clock signals (XCK and optionally XSC), and a framing pulse ( $\overline{XFSI}$ ). The nibble-parallel interface consists of the nibble data (XNIB3 through XNIB0), a clock out signal (XCK), a framing pulse ( $\overline{XFNO}$ ), and a nibble clock signal (XNC). The XNIB3 bit corresponds to the first bit transmitted.

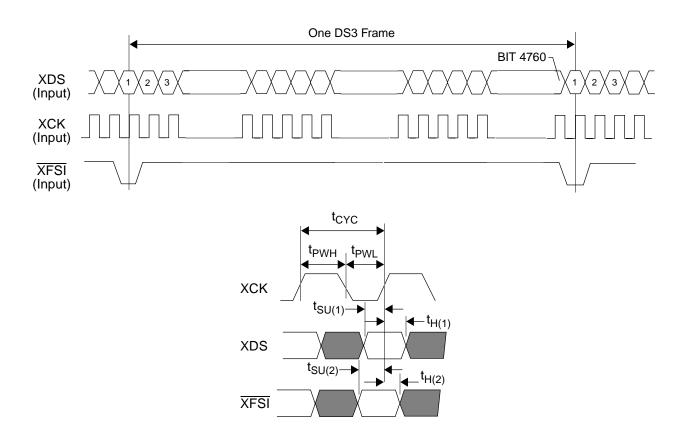

The DS3 Send Block performs P-bit and C-bit parity generation, AIS and idle pattern generation, far end alarm and control (single or double FEAC word) transmission, X-bit insertion, and C-bit insertion. For C-bit Parity mode, the C-bits may be generated internally (such as C-bit parity), written by the microprocessor (such as the FEAC channel), or provided from the external C-bit interface. In C-bit Parity mode, the C1 bit is always transmitted as a 1. The transmit C-bit interface consists of a data input signal (CXD), a clock signal (CXCK), a framing pulse (CXF) and a data communication link clock (CXDCC). For M13 mode, all of the C-bits are input from the terminal side's bit-serial interface. The DS3 transmit line side interface consists of the data signal (D3TD) and a clock signal (D3TC).

DS3F transmit-to-receive (TR) loopback is controlled by setting a bit in the memory map (3LOOP). The entire device is used when loopback is in effect, but the line side input data and clock are blocked (by the gate preceding the DS3 Frame Alignment Block shown in Figure 1). In the Extended-features mode of operation, a receive-to-transmit payload (RTP) loopback is also available by use of control bit RTPLOOP.

The capability to generate and transmit single overhead bit errors is also provided. External interfaces are provided for transmitting a far end block error (FORCEFEBE), a P-bit parity error (FORCEPP), a C-bit parity error (FORCECP) and an overhead bit error (FORCEOE). The FORCEOE signal is used in conjunction with the enable signal (OENA) for introducing an overhead bit error in the next 85-bit segment of the DS3 frame. When the Extended-features mode (EMODE), Coding Violation Enable (CVEN) and Excessive Zeros Enable (EXZEN) control bits in the memory map are set to 1, the Coding Violations Count (CVCNT) function and Excessive Zeros Count (EXZCNT) functions pin replace the FORCECP and FORCEPP functions, respectively. The purpose of these pins is to utilize the DS3F's 16-bit counter CVEXZ to count coding violation and/or excessive zeros events. Indications of these events are provided to the DS3F by TranSwitch's ART or ARTE devices (TXC-02020/02021). The ART's CV output pin indicates both coding violations and excessive zeros. Therefore, only the CVCNT input pin to the DS3F is required to count both types of event. When the ARTE is used in conjunction with the DS3F, there are separate CV and EXZ inputs available to the DS3F, which can be or-gated together in the DS3F's 16-bit counter, if required. The DS3F has an internal 16-bit shadow counter incorporated into its counter design. This prevents CV or EXZ counts being lost during a read cycle.

The Transmit Frame Reference Generator Block provides reference timing for bit-serial operation. This block accepts an external 44.736MHz clock signal (TCIN) and derives a clock signal (TCOUT), a framing pulse (TFOUT), a clock gap signal (TCG) and a data signal (TDOUT). The DS3 data signal consists of framing bits and zeros elsewhere. An optional input framing pulse (TFIN) is also provided, but is not required for normal operation.

The DS3F microprocessor bus interface consists of eight bidirectional data and address leads (AD0-AD7), along with other microprocessor control leads. The microprocessor bus is used to write control information and to read status information and alarms. When operating in the Extended-features mode the DS3F memory map contains twenty-one effective addresses (00H-14H), compared with eight (00H-07H) in the Normal mode.

When the DS3F is operating in the Extended-features mode, its many additional features may be activated via control bits in the memory map. These features include: ability to tri-state all output ports, X-bit inversion, receive loop timing, receive and transmit Blue Code AIS conditions, FEAC Idle Channel Indication, a receive FEAC FIFO stack overflow bit, a Severely Errored Frame indication, and double FEAC word handling.

Figure 2. DS3F TXC-03401B Pin Diagram

## **PIN DESCRIPTIONS**

#### POWER SUPPLY AND GROUND

VITCH<sup>®</sup>

TRA

| Symbol | Pin No.                 | I/O/P* | Туре | Name/Function                                |

|--------|-------------------------|--------|------|----------------------------------------------|

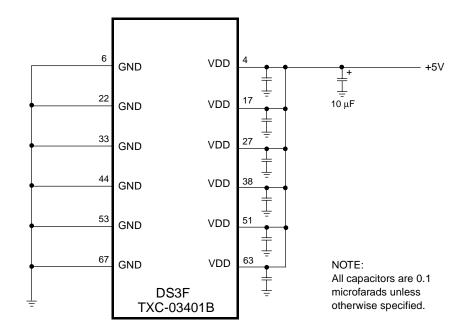

| VDD    | 4, 17, 27<br>38, 51, 63 | Р      |      | <b>VDD:</b> +5 volt supply voltage, $\pm$ 5% |

| GND    | 6, 22, 33<br>44, 53, 67 | Р      |      | Ground: 0 volts reference.                   |

\*Note: I = Input; O = Output; P = Power

## TRANSWITCH

#### **DS3 RECEIVE LINE SIDE INTERFACE**

| Symbol | Pin No. | I/O/P | Туре* | Name/Function                                                                                                                                                                                                       |

|--------|---------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D3RC   | 5       | I     | CMOS  | <b>DS3 Receive Clock:</b> A 44.736 MHz clock used for clock-<br>ing in receive data, and as the time base for the DS3F<br>receiver. Line side serial data is clocked into the DS3F on<br>rising edges of the clock. |

| D3RD   | 29      | I     | TTL   | DS3 Receive Data: DS3 line side serial receive data.                                                                                                                                                                |

#### DS3 TRANSMIT LINE SIDE INTERFACE

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                            |

|--------|---------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

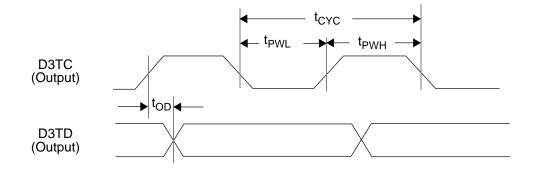

| D3TC   | 1       | 0     |         | <b>DS3 Transmit Clock:</b> A 44.736 MHz clock that is derived from the transmit clock (XCK) signal and is used for clock-ing out the line side DS3 data signal. Data (D3TD) is clocked out on rising edges of the clock. |

| D3TD   | 3       | 0     | CMOS4mA | DS3 Transmit Data: DS3 line side serial transmit data.                                                                                                                                                                   |

#### RECEIVE TERMINAL SIDE INTERFACE

| Symbol                               | Pin No.              | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|----------------------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

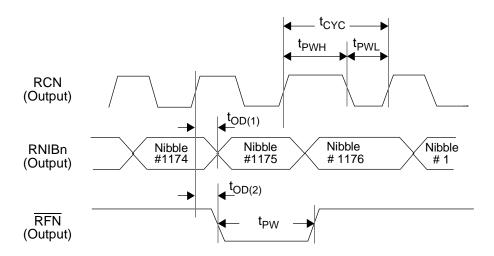

| RFS/RFN                              | 31                   | 0     | CMOS4mA | <b>Receive Framing Pulse Serial/Nibble Interface:</b> The framing pulse is active low for one clock cycle (RCS/RCN), and is synchronous with the first bit 1 in the DS3 frame. For the nibble interface, the framing pulse is synchronous with nibble 1175.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RCS/RCN                              | 34                   | 0     | CMOS4mA | <b>Receive Clock Serial/Nibble Interface:</b> Clock used for clocking out the terminal side receive serial and nibble data. This clock is derived from the line side clock (D3RC). Data is clocked out of the DS3F on falling edges of the RCS clock and on rising edges of the RCN clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RNIB3<br>RNIB2<br>RNIB1<br>RDS/RNIB0 | 39<br>40<br>41<br>42 | 0     | TTL4mA  | <b>Receive Nibble/Serial Interface:</b> Nibble data is clocked<br>out on rising edges of the nibble clock (RCN). There are<br>1176 nibbles provided each frame. The data and clock are<br>stretched to accommodate the 56 individual overhead bits<br>(first bit in the 85-bit group), which are not provided at the<br>interface. The first bit received in a nibble is present on<br>RNIB3. The nibble interface is operational in the C-bit par-<br>ity operating mode only. Serial data (RDS) consists of all<br>the bits in the frame (including the states of the overhead<br>bits), and is operational in either operating mode, M13 or<br>C-bit parity. Serial data is clocked out on falling edges of<br>the receive clock (RCS). For serial data, a gapped clock<br>signal is generated by the receive circuitry and provided<br>on the RNIB3 pin when control bits SER and RGCEN are<br>both set to 1. |

\*See Input, Output and I/O Parameters section for Type definitions.

|   | Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                             |

|---|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | RCG    | 32      | 0     |      | <b>Receive Clock Gap Signal:</b> The active low gap signal is synchronous with each overhead bit in the serial DS3 frame (first bit in the 85-bit group). |

#### TRANSMIT TERMINAL SIDE INTERFACE

| Symbol                               | Pin No.              | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|----------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

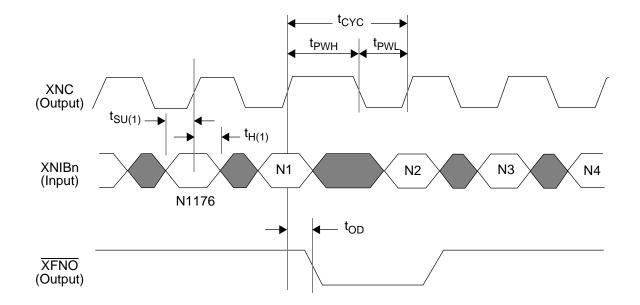

| XFNO                                 | 2                    | 0     | TTL4mA | <b>Transmit Nibble Interface Framing Pulse:</b> An active low, one nibble clock cycle wide (XNC) pulse that occurs during the second nibble time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XFSI                                 | 50                   | I     | TTLp   | <b>Serial Data Transmit Framing Pulse:</b> A framing pulse whose leading edge must be synchronous with bit 1 in the transmit serial data DS3 frame. The DS3F rewrites the 56 overhead bits based on the location of the transmit framing pulse. If this signal is held low for a duration greater than 1 frame, then all register bit positions at Addresses 02H-04H, 05H bit 6 and 08H-14H (except 10H bit 6) will be reset to 0 until the pin is taken high. The XFSI pulse must not be applied while control bit RTPLOOP is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XDS/XNIB3<br>XNIB2<br>XNIB1<br>XNIB0 | 56<br>58<br>59<br>60 | Ι     | TTL    | <b>Transmit Nibble/Serial Interface:</b> Nibble data is clocked<br>in on rising edges of the nibble clock (XNC). There are<br>1176 nibbles in each frame. The clock is stretched to<br>accommodate the 56 overhead bits which are not required<br>at the interface. The DS3F inserts the X, F, C, P, and M<br>overhead bits into the transmitted frame based on the<br>framing pulse XFNO. The first bit transmitted in a nibble is<br>present on XNIB3. The nibble interface is operational in<br>the C-bit parity mode only. The serial data should consist<br>of all the bits in the frame (4760 bits). The DS3F rewrites<br>the 56 overhead bits in the frame based on the location of<br>the framing pulse XFSI, when operating in the C-bit parity<br>mode. In the M13 operating mode, the 21 C-bits are<br>treated as user data, while the other overhead bits (X, F, P,<br>and M bits) are written into the DS3 frame by the DS3F.<br>Serial data is clocked into the DS3F on rising edges of the<br>transmit clock (XCK). |

| ХСК                                  | 62                   | I     | CMOS   | <b>Transmit Clock:</b> Provides the time base for the transmit-<br>ter in the DS3F. In order to meet cross-connect objectives,<br>the clock must operate at 44.736 Mbit/s with a stability of<br>$\pm 20$ ppm and a duty cycle of (50 $\pm 10$ )%. If XCK fails, the<br>DS3F uses the D3RC receive clock in its place.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Symbol  | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|---------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XSC/XNC | 66      | 0     | CMOS4mA | <b>Transmit Nibble/Serial Clock:</b> Clock signal derived from<br>the transmit clock (XCK). For nibble data, this clock (XNC)<br>is stretched in order to accommodate the 56 overhead bit<br>positions which are not required by the external terminal<br>circuitry for the nibble interface (XNIBn). For serial data, a<br>gapped clock signal (XSC) is generated and provided on<br>this pin when control bits SER and TGCEN are both set to<br>1. This signal is synchronous with bit 1 in each 85-bit<br>group (56 overhead bits) in the DS3 frame. |

#### TRANSMIT REFERENCE GENERATOR INTERFACE

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|---------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDOUT  | 45      | 0     | TTL4mA  | <b>Transmit Reference Generator Data Output:</b> DS3<br>frames are provided on this output that contain either all<br>zeros or all ones. The number of frames with ones is 7 of<br>every 18 frames. The pattern of the ones is one frame of<br>every three for 15 frames and two of the last 3 of the 18-<br>frame group; this completes the 7 of 18 pattern.<br>The purpose of this pattern is to ease the requirement to<br>provide an all-ones and all-zeros C-bit pattern to insure a<br>DS2 frequency that is very nearly equal to its specified<br>value. |

| TCG    | 46      | 0     | TTL4mA  | <b>Transmit Reference Generator Clock Gap Signal:</b> An active low, one clock cycle wide (TCOUT) signal that is synchronous with bit 1 in each 85-bit group (56 overhead bits) in the DS3 frame.                                                                                                                                                                                                                                                                                                                                                               |

| TFOUT  | 47      | 0     | TTL4mA  | <b>Transmit Reference Generator Framing Pulse:</b> An active low, one clock cycle wide (TCOUT) pulse that is synchronous with bit 1 in the DS3 frame. May be used as the serial data transmit framing pulse ( $\overline{XFSI}$ ) if properly delayed such that $\overline{XFSI}$ is aligned with an overhead-bit clock cycle.                                                                                                                                                                                                                                  |

| TCOUT  | 48      | 0     | CMOS4mA | Transmit Reference Generator Clock Out: Clock signal<br>that is derived from the transmit reference generator clock<br>input (TCIN). Provides a time base for multiplexing an<br>external payload into the serial signal TDOUT provided by<br>the reference generator. May be used as the transmit<br>input clock (XCK) in the serial mode. Transmit reference<br>generator signals are clocked out on rising edges of this<br>clock.                                                                                                                           |

| TCIN   | 52      | I     | TTL     | Transmit Reference Generator Clock In: Provides a time base for generating the various signals in the DS3F transmit reference generator. In order to meet DS3 cross-connect objectives, this clock must operate at 44.736 Mbit/s with a stability of $\pm 20$ ppm and a duty cycle of $(50\pm10)\%$ .                                                                                                                                                                                                                                                           |

### RECEIVE C-BIT INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRDCC  | 30      | 0     | TTL4mA | <b>C-Bit Receive Data Link Clock:</b> A gapped clock provided for clocking the three data link bits (C13, C14, and C15) into external circuitry from the serial data (CRD). The rising edge of CRDCC indicates when valid data is available. In Extended mode, control bits are available to convert the three cycles into a single envelope pulse and/ or to invert the signal's polarity (see Figure 10). |

| CRF    | 35      | 0     | TTL4mA | <b>C-Bit Receive Framing Pulse:</b> Provides a time base reference for clocking in the C-bits in a DS3 frame.                                                                                                                                                                                                                                                                                               |

| CRCK   | 36      | 0     | TTL4mA | <b>C-Bit Receive Clock:</b> A gapped clock which clocks C-bit data out of the DS3F. The falling edge of CRCK indicates when valid data is available.                                                                                                                                                                                                                                                        |

| CRD    | 37      | 0     | TTL4mA | <b>C-Bit Receive Data:</b> Serial interface for receiving the following C-bits in the C-bit parity mode: C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21. Availability of data is indicated by the clock signals CRDCC and CRCK, described above.                                                                                                                                       |

#### **TRANSMIT C-BIT INTERFACE**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                         |

|--------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CXD    | 28      | I     | TTL    | <b>C-Bit Transmit Data:</b> Serial interface for transmitting the following C-bits in the C-bit parity mode: C2, C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20, and C21. C-bit data is clocked into the DS3F on rising edges of the C-bit gapped clock (CXCK). A C-bit must be transmitted as a one if not used. |

| CXDCC  | 64      | 0     | TTL4mA | <b>C-Bit Transmit Data Link Clock:</b> A gapped clock provided for clocking the three data link bits (C13, C14, and C15). In Extended mode, a control bit is available to convert the three cycles into a single envelope pulse (see Figure 9).                                                                       |

| CXF    | 65      | 0     | TTL4mA | <b>C-Bit Transmit Framing Pulse:</b> Identifies the location of the first C-bit in the DS3 frame.                                                                                                                                                                                                                     |

| СХСК   | 68      | 0     | TTL4mA | <b>C-Bit Transmit Clock:</b> A gapped clock which clocks the external C-bit serial data into the DS3F on rising edges.                                                                                                                                                                                                |

## TRANSWITCH

### **OTHER SIGNALS**

| Symbol     | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST       | 7       | I     | TTLp   | TranSwitch Test Pin: Leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OENA       | 9       | 0     | TTL4mA | <b>Overhead Enable:</b> An active high signal that enables an overhead error to be introduced into the overhead bit in the next 85th group by placing a low on the FORCEOE lead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| X1         | 11      | 0     | TTL4mA | <b>DS3 Received X-Bit 1:</b> An output indication of the state of the first X-bit received in the DS3 frame (bit 1). The indication is active until the next X1 state is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| X2         | 13      | 0     | TTL4mA | <b>DS3 Received X-Bit 2:</b> An output indication of the state of the second X-bit received in the DS3 frame (bit 680). The indication is active until the next X2 state is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| STUFD/HINT | 15      | 0     | TTL4mA | Stuff Data Status / Hardware Interrupt: In the Normal mode of operation (EMODE=0), this pin performs the Stuff Data Status function. This output pin provides an indication of the state of the stuff opportunity bit from the receive DS3 frame when operating in the M13 mode. For an M13 DS3 formatted signal, the first stuff opportunity bit occurs in the first bit after F4 (last 85-bit group) in sub-frame 1, and the last stuff opportunity bit in the frame occurs in the seventh bit after F4 (last 85-bit group) in subframe 7. In the Extended-features mode of operation (EMODE=1), this output pin can be used (if HINTEN=1) to perform the Hardware Interrupt function. It may be used as input to the interrupt pin of the microprocessor. When at least one of the eight interrupt enable mask bits (Address 11H, bits 7-0) is 1, occurrence of a corresponding alarm condition causes the pin to go high. This pin is used to inform the microprocessor that a severe alarm condition has occurred. The Hardware Interrupt signal may be changed to active low by setting control bit HINTINV to 1. |

| STUFC      | 16      | 0     | TTL4mA | <b>Stuff Clock:</b> Provided for clocking out the stuff opportunity bit state. The rising edge occurs at the start of the second F-bit in a subframe and the falling edge occurs at the end of the fifth 85-bit group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FE         | 43      | 0     | TTL4mA | <b>Framing Error Indication:</b> The FE pin will go high for<br>every F-bit or M-bit framing error. It stays high for a period<br>of $1.9\mu$ s (85 clock periods). During an Out of Frame con-<br>dition the FE pin is held low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TFIN       | 49      | I     | TTLp   | <b>Transmit Framing Input:</b> An optional active low input signal which resets the counters of the Transmit Frame Reference Generator block to zero and holds the output signals of the block to their corresponding states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Symbol             | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|--------------------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FORCEOE            | 54      | I     | TTLp | Force DS3 Overhead Bit Error: An active low signal used in conjunction with the overhead enable signal (OENA) for introducing an overhead bit error in the next transmitted 85-bit group.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| FORCEPP/<br>EXZCNT | 55      | I     | ΤΤLp | Force P-Bit Parity Error / Excessive Zeros Count: In<br>the Normal mode of operation (EMODE=0), this pin pe<br>forms the Force DS3 P-Bit Parity Error function. An acti<br>low signal generates and transmits a P-bit error by inve<br>ing both P-bits. If an active low signal is applied during t<br>first subframe of the DS3 frame, the error is transmitted<br>that frame. Otherwise the error is transmitted in the new<br>frame.                                                                                                                                  |  |  |  |

|                    |         |       |      | In the Extended-features mode of operation (EMODE=1),<br>this pin performs the Excessive Zeros Count function<br>when EXZEN=1. An internal 16-bit counter, CVEXZ at<br>Addresses 12H and 13H, is incremented when the pin is<br>low during the rising edge of D3RC. This pin is intended to<br>be driven by the EXZ Excessive Zeros output pin of the<br>TranSwitch TXC-02021 ARTE device.                                                                                                                                                                               |  |  |  |

| FORCECP/<br>CVCNT  | 57      | 1     | ΤΤLp | Force C-Bit Parity Error / Coding Violation Count: In<br>the Normal mode of operation (EMODE=0), this pin per-<br>forms the Force DS3 C-Bit Parity Error function. An active<br>low signal generates and transmits a C-bit parity error<br>when operating in the C-bit parity mode. The error is<br>transmitted by inverting C7, C8 and C9 (C-bit parity value)<br>in subframe 3. If the active low signal is applied during the<br>first subframe of the DS3 frame, the error is transmitted in<br>that frame. Otherwise the error is transmitted in the next<br>frame. |  |  |  |

|                    |         |       |      | In the Extended-features mode of operation (EMODE=1),<br>this pin performs the performs the Coding Violation Count<br>function when CVEN=1. An internal 16-bit counter,<br>CVEXZ at Addresses 12H and 13H, is incremented when<br>the pin is high during the rising edge of D3RC. This pin is<br>intended to be driven by the CV Coding Violation / Exces-<br>sive Zeros output pin of the TranSwitch TXC-02020 ART<br>device or the CV Coding Violation output pin of the Tran-<br>Switch TXC-02021 ARTE device.                                                        |  |  |  |

| FORCEFEBE          | 61      | I     | TTLp | <b>Force FEBE Error:</b> An active low signal generates and transmits a far end block error (FEBE) when operating in the C-bit parity mode. If the active low signal is applied during the first subframe of the DS3 frame, the error is transmitted in that frame. Otherwise the error is transmitted in the next frame.                                                                                                                                                                                                                                                |  |  |  |

## MICROPROCESSOR INTERFACE

| Symbol             | Pin No.        | I/O/P | Туре   | Name/Function                                                                                                                                                                                            |  |  |  |

|--------------------|----------------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SEL                | 8              | I     | TTL    | <b>Microprocessor Select:</b> A low enables the microprocessor to access the DS3F memory map for control, status and alarm information.                                                                  |  |  |  |

| ALE                | 10             | I     | TTL    | Address Latch Enable: An active high signal generated<br>by the microprocessor. Used by the microprocessor to<br>hold an address stable during a read/write bus cycle on<br>the falling edge.            |  |  |  |

| RD                 | 12             | I     | TTL    | <b>Read:</b> An active low signal generated by the microproces sor for reading the registers which reside in the DS3F memory map. The DS3F memory I/O is selected by placing a low on the select lead.   |  |  |  |

| WR                 | 14             | I     | TTL    | Write: An active low signal generated by the microproces-<br>sor for writing to the registers which reside in the memory<br>map. The DS3F memory I/O is selected by placing a low<br>on the select lead. |  |  |  |

| AD(7-4)<br>AD(3-0) | 18-21<br>23-26 | I/O   | TTL8mA | Address/Data Bus: These leads constitute the time mul-<br>tiplexed address and data bus for accessing the registers<br>which reside in the DS3F memory map.                                              |  |  |  |

## ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS

| Parameter                           | Symbol          | Min  | Max                   | Unit   | Conditions                        |

|-------------------------------------|-----------------|------|-----------------------|--------|-----------------------------------|

| Supply voltage                      | V <sub>DD</sub> | -0.3 | +6.0                  | V      | Note 1                            |

| DC input voltage                    | V <sub>IN</sub> | -0.3 | V <sub>DD</sub> + 0.3 | V      | Note 1                            |

| Storage temperature range           | Τ <sub>S</sub>  | -55  | 150                   | °C     | Note 1                            |

| Ambient operating temperature range | T <sub>A</sub>  | -40  | 85                    | °C     | 0 ft/min linear airflow           |

| Component temperature x time        | TI              |      | 270 x 5               | °C x s | Note 1                            |

| Moisture Exposure Level             | ME              | 5    |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A    |

| Relative Humidity, during assembly  | RH              | 30   | 60                    | %      | Note 2                            |

| Relative Humidity, in-circuit       | RH              | 0    | 100                   | %      | non-condensing                    |

| ESD Classification                  | ESD             |      | ±2000                 | V      | per MIL-STD-883D<br>Method 3015.7 |

Notes:

1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

2. Pre-assembly storage in non-drypack conditions is not recommended. Please refer to the instructions on the "CAUTION" label on the drypack bag in which devices are supplied

#### THERMAL CHARACTERISTICS

| Parameter                                   | Min | Тур | Max | Unit | Test Conditions         |

|---------------------------------------------|-----|-----|-----|------|-------------------------|

| Thermal resistance -<br>junction to ambient |     | 40  | 42  | °C/W | 0 ft/min linear airflow |

## POWER REQUIREMENTS

| Parameter                        | Min  | Тур | Max  | Unit | Test Conditions  |

|----------------------------------|------|-----|------|------|------------------|

| V <sub>DD</sub> , supply voltage | 4.75 | 5.0 | 5.25 | V    |                  |

| I <sub>DD</sub> , supply current |      |     | 150  | mA   |                  |

| P <sub>DD</sub> , supply power   |      |     | 790  | mW   | Inputs switching |

## INPUT, OUTPUT AND I/O PARAMETERS

### Input Parameters For TTL

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                |

|-----------------------|-----|-----|-----|------|------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>≤</u> 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>≤</u> 5.25 |

| Input leakage current |     |     | 10  | μA   | V <sub>DD</sub> = 5.25                         |