DS3LIM-SN DS3/STS-1 Line Interface Module NRZ Clock/Data Output TXC-20153D, TXC-20153G

**DATA SHEET**

#### FEATURES

- Complete B3ZS analog to NRZ digital DS3/ STS-1 line interface unit in a compact 2.6 square inch, 50-pin DIP Module

- Single +5V power supply

- Analog inputs and outputs are transformer coupled

- Meets DSX cross connect frame mask requirements (ANSI Standard T1.102-1993)

- Adaptive equalization for zero to 900 feet of cable

- Input dynamic range of 20 dB (100mV 0.95V)

- Meets DS3/STS-1 jitter requirements of Bellcore Technical References

- · Full loopback capability

- Coding violation and loss of signal detection for received signal

- TXC-20153D has monitor pin for received signal input. TXC-20153G has pull-up for external clock input and improved performance margins.

- Speeds time to market for prototype development

- Eases parts inventory and acquisition

- · Eases field maintenance

#### **DESCRIPTION**

The DS3/STS-1 Line Interface Module (DS3LIM-SN) is a complete and compact full duplex analog line to digital terminal interface. It converts B3ZS-encoded line signals, in either DS3 asynchronous or STS-1 synchronous format, to and from NRZ data and clock signals. In addition to the synchronous signal option, this Module offers other improvements relative to the TranSwitch DS3 Line Interface Module (DS3LIM, TXC-20049D), which it can replace in some existing DS3 applications.

Sensitive analog circuitry meets DS3/STS-1 performance requirements for signal recovery and transmission, with direct line connection via on-board transformers. Integration of functions into a single Module frees the user from complex printed circuit board design and testing for the DS3/STS-1 analog section, reducing the time required for applications development and product introduction.

### **APPLICATIONS**

DS3/STS-1 interface for quick "time to market" products

# **TABLE OF CONTENTS**

| <u>SECTION</u>                                                        | <u>PAGE</u> |

|-----------------------------------------------------------------------|-------------|

| Product Overview                                                      | 4           |

| Block Diagram                                                         | 5           |

| Block Diagram Description                                             | 5           |

| Pin Diagram                                                           | 7           |

| Pin Descriptions                                                      | 7           |

| Absolute Maximum Ratings and Environmental Limitations                | 12          |

| Power Requirements                                                    | 12          |

| Input and Output Parameters                                           | 13          |

| Timing Characteristics                                                | 16          |

| Operation                                                             | 21-27       |

| Receiver Input Requirements                                           | 21          |

| Interfering Tone Tolerance                                            | 21          |

| Receiver Output Specifications                                        | 21          |

| Transmitter Specifications                                            |             |

| AIS and Loopback Control Signal Arbitration                           | 22          |

| Jitter Transfer                                                       | 23          |

| Jitter Generation                                                     |             |

| Jitter Tolerance                                                      |             |

| Interference Margin                                                   |             |

| Physical Design of Motherboard                                        |             |

| Functional Differences Between the DS3LIM-SN and DS3LIM Modules $\ .$ |             |

| Circuit Diagrams                                                      |             |

| Package Information                                                   |             |

| Ordering Information                                                  |             |

| Related Products                                                      |             |

| Standards Documentation Sources                                       |             |

| List of Data Sheet Changes                                            |             |

| Documentation Update Registration Form *                              | 41          |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

| Figure 1.  | DS3LIM-SN Block Diagram                                   | 5  |

|------------|-----------------------------------------------------------|----|

| Figure 2.  | DS3LIM-SN Pin Diagram                                     | 7  |

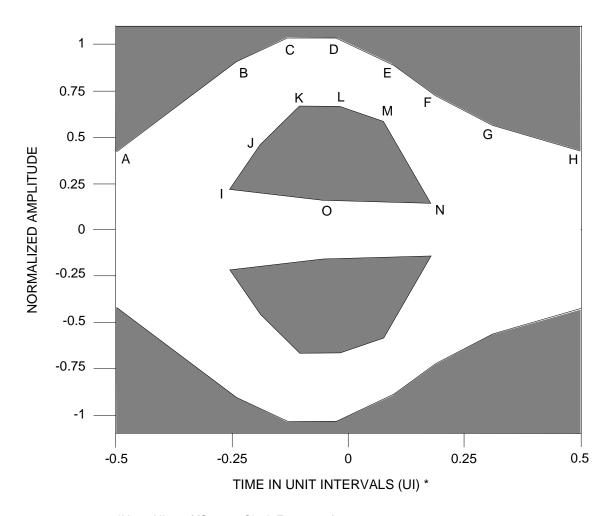

| Figure 3a. | DS3 Interface Isolated Pulse Mask                         | 16 |

| Figure 3b. | DS3 Interface Isolated Pulse Mask Equations               | 17 |

| Figure 3c. | STS-1 Interface Isolated Pulse Mask Equations             | 17 |

| Figure 3d. | STS-1 Interface Eye Diagram Mask                          | 18 |

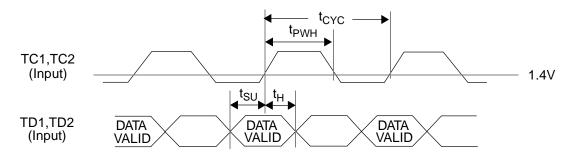

| Figure 4.  | NRZ Transmit Input Timing                                 | 19 |

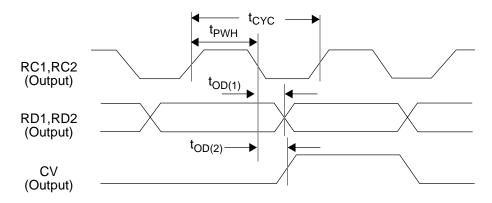

| Figure 5.  | NRZ Receive Output Timing                                 | 20 |

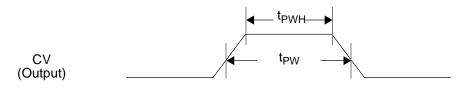

| Figure 6.  | Coding Violation Pulse Timing                             | 20 |

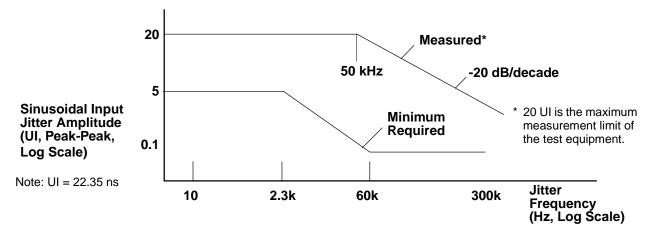

| Figure 7a. | DS3LIM-SN Input Jitter Tolerance for DS3 (Category I)     | 24 |

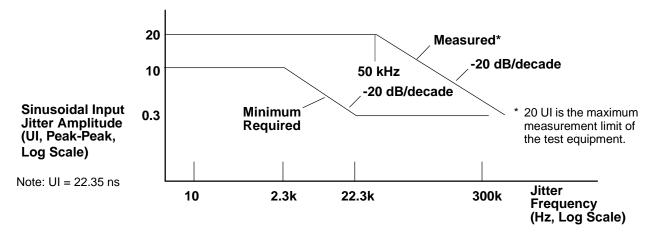

| Figure 7b. | DS3LIM-SN Input Jitter Tolerance for DS3 (Category II)    | 24 |

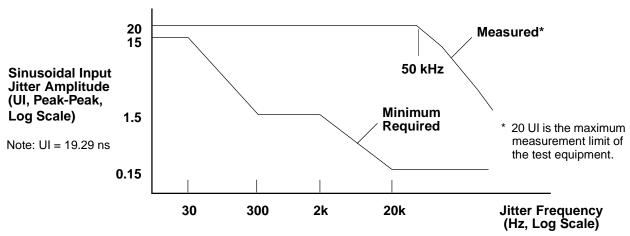

| Figure 7c. | DS3LIM-SN Input Jitter Tolerance for STS-1                | 24 |

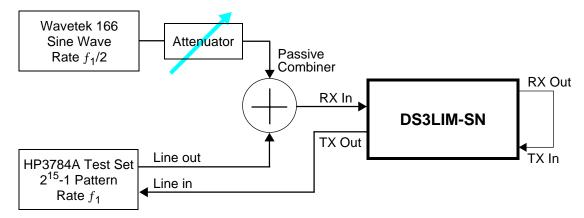

| Figure 8.  | Interference Margin Test Configuration                    | 25 |

| Figure 9.  | Power Supply and Ground Connections                       | 26 |

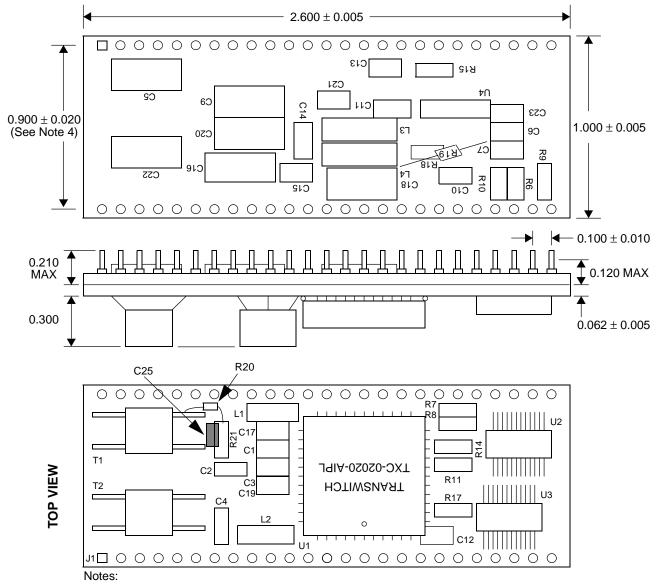

| Figure 10. | DS3LIM-SN Circuit Diagram (TXC-20153D, -20153G Edition 1) | 30 |

| Figure 11. | DS3LIM-SN Circuit Diagram (TXC-20153G Edition 2)          | 31 |

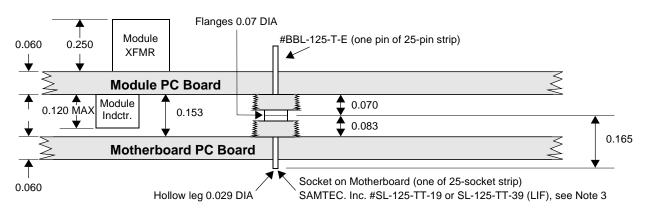

| Figure 12. | DS3LIM-SN Simplified Outline Drawing                      | 32 |

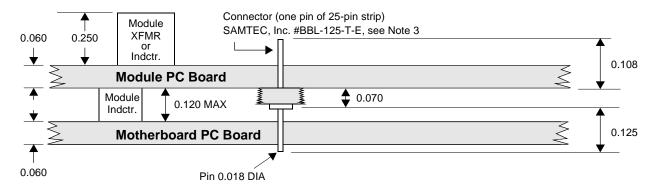

| Figure 13. | Installation Without Motherboard Socket                   |    |

| Figure 14  | Installation With Motherboard Socket                      | 33 |

### **PRODUCT OVERVIEW**

The DS3LIM-SN Module employs TranSwitch's latest DS3/STS-1 receiver/transmitter VLSI device on a small printed circuit board assembly with line-coupling transformers and dual-port terminal interface circuits. Use of the TranSwitch ART VLSI device (Advanced DS3/STS-1 Receiver/Transmitter, TXC-02020) provides improved performance and reduced cost relative to the TranSwitch DS3LIM Module, which is based on the DS3-only DS3RT receiver/transmitter VLSI device. In addition to the STS-1 synchronous capability, the ART device has on-board AGC, equalization and output amplification, functions which had to be provided with external components on the DS3LIM.

The DS3LIM-SN is mechanically compatible with the DS3LIM and is intended to supersede it for both existing and new applications. The reduced cost and improved performance (wider dynamic range, simultaneous loop-back capability) are advantages for existing applications, providing that certain constraints imposed by electrical differences from the DS3LIM can be accommodated (see the section below entitled "Functional Differences between DS3LIM-SN and DS3LIM Modules"). For new applications the STS-1 capability and single power supply are additional advantages.

Three versions of the DS3LIM-SN Module are available, with two different product numbers and part numbers (please see the Ordering Information section). The TXC-20153D product is the original version. It provides a pin (MON, pin 46) for monitoring the received signal input at the 75 ohm terminating resistor on the secondary side of the input transformer. Since this pin has electrical characteristics different from those of the corresponding pin on the DS3LIM Module, the TXC-20153D may not be suitable for substitution in DS3LIM applications where this pin is not used for monitoring but has a termination that takes advantage of the superior DS3LIM output characteristics. The TXC-20153G product was introduced for use in such applications. The first version of the TXC-20153G (Edition 1) has two layout differences relative to the TXC-20153D: it has no monitor output connection to pin 46, and it has a pull-up resistor on the external clock input (DCK, pin 27). However, this Edition 1 is less immune to noise than the TXC-20153D. In applications where excessive board noise is present, and when receiving a signal greater than 800 mV peak, bit errors may occur. Edition 2 of the TXC-20153G was introduced for use in such applications. It is identical to Edition 1, except for a modification to the receive input circuit that provides 4 dB attenuation of the input signal at the input to the ART device.

#### **BLOCK DIAGRAM**

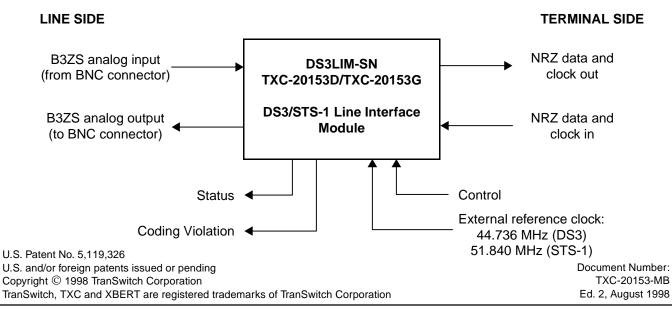

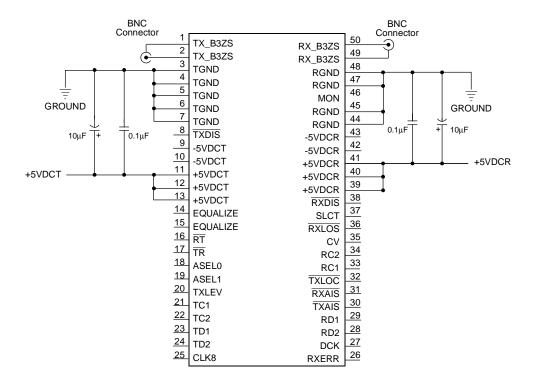

Figure 1. DS3LIM-SN Block Diagram

### **BLOCK DIAGRAM DESCRIPTION**

A block diagram for the DS3LIM-SN Module is shown in Figure 1, which is explained below.

In the receive direction, the DS3LIM-SN receives a bipolar B3ZS-encoded DS3 or STS-1 signal from the line via a BNC or other connector. This signal (RX\_B3ZS) is AC-coupled into the DS3LIM-SN through a 1:1 transformer (XFMR). From the transformer, the signal is terminated into a 75 ohm resistance, either as a single 75 ohm shunt resistor or as a 27/47 ohm resistor pair that provides 4 dB attenuation at its junction (in TXC-20153G Edition 2 only). The resulting signal is then routed to the input of an Automatic Gain Control (AGC) circuit in the ART device (dotted outline). A Monitor pin (MON) is provided for observing the received signal in the TXC-20153D only. The AGC provides the Adaptive Equalizer circuit with a constant signal level. The equalizer is switched in and out to recover narrow or wide width DS3/STS-1 signals, respectively. From the equalizer, the bipolar signal is connected to the LOS Detector and Clock Recovery blocks. The line signal is monitored for transitions, and a loss of signal indication is provided on the signal pin labelled RXLOS.

The Clock Recovery block requires an external 44.736 MHz (DS3) or 51.840 MHz (STS-1) clock (DCK) with a stability of  $\pm$  200 ppm. The stability of DCK must be increased to  $\pm$  20 ppm if the transmit or receive AIS features are used. The average time to recover the clock is approximately 1 ms when the line signal is applied.

The B3ZS (bipolar with 3-zero substitution) line coded data is decoded by the B3ZS Decoder block. Indications of coding violation errors, other than normal B3ZS coding substitutions, are provided on the signal pin CV. The decoder detects coding violation errors in the same fashion as the Telecommunication Techniques Corporation's TBERD™ model 305 DS3 Analyzer for system test purposes, but some differences may be encountered when testing with Scientific Atlanta or Wandel and Goltermann equipment. These errors can occur because of noise and other impairments on the line. The application that uses the DS3LIM-SN can count the CV pulses over a known time interval to calculate a close estimate for the Bit Error Rate (BER) performance of the line.

The DS3LIM-SN provides the capability to generate and insert a DS3 Alarm Indication Signal (AIS) into the NRZ receive data signal at the RD1 or RD2 pins. A low placed on the RXAIS pin enables the DS3 AIS insertion from the DS3 AIS Generator block. This pin may be connected to the receive loss of signal (RXLOS) pin to generate AIS. The DS3LIM-SN does not provide a corresponding capability for STS-1 operation.

The decoded signal is processed by the Receive I/O Control and Receive Terminal Interface Multiplexer blocks. Two receive output ports consisting of a clock and data signal are provided. The first receive output port has pins labelled RC1 and RD1; the second is labelled RC2 and RD2. Only one port can be active at a time. Data (RD1/RD2) is clocked out of the DS3LIM-SN with respect to the falling edge of the receive clock (RC1/RC2). The selection of the receive output port is controlled by the state of the select pin (SLCT, high for port 1). The unused port is forced into a high impedance state. In addition, the two receive ports can both be disabled and forced into a high impedance state by placing a low on the RXDIS pin.

In the transmit direction, two transmit ports consisting of clock and data are also provided. The first transmit port has pins labelled TC1 and TD1; the second is labelled TC2 and TD2. Transmit input data (TD1/TD2) is clocked into the DS3LIM-SN on positive transitions of the clock signal (TC1/TC2). As in the receiver section, the SLCT pin determines the transmit input port selection (high for port 1).

Transmit input clock and data signals are processed by the Transmit Terminal Interface Multiplexer and Transmit I/O Control blocks. The incoming data is encoded by the B3ZS encoder. In the B3ZS line code, each block of three consecutive zeros is removed and replaced by either of two codes that contain bipolar violations. These replacement codes are B0V and 00V, where B represents a pulse that conforms to the bipolar rule and V represents a pulse violating the rule. The choice of these codes is made so that an odd number of bipolar conforming pulses (B) is transmitted between consecutive bipolar violation pulses (V). The encoded data is connected to the Output Control block, which contains the formatting circuitry to transform the B3ZS-encoded data into pulses that meet the requirements for the DS3 or STS-1 line rates and a 75-ohm driver for the 1:1 output transformer. This block also provides the capability to transmit a DS3 Alarm Indication Signal (AIS), which is independent of the transmit data. A low placed on the TXAIS pin enables the transmit DS3 AIS insertion. A low placed on the TXDIS pin deactivates the transmit output. When TXDIS is set low, the output impedance of the TX\_B3ZS port becomes a high impedance state. The Output Control block contains a feature to adjust the output signal for cables longer than 50 feet, which is activated by setting the TXLEV pin low.

In addition to the alarms and control signals, the DS3LIM-SN provides two loopback capabilities for testing transmit and receive loopback via the Loopback Controls block. Transmit-to-Receive (terminal) loopback connects the data path from the Transmit I/O Control block output to the Receive I/O Control block input, and disables the external receiver input. Transmit-to-Receive loopback is activated by placing a low on the  $\overline{TR}$  signal pin. Receive-to-Transmit (line) loopback connects the receive data output path to the transmit input circuits and disables the NRZ transmit input. Receive-to-Transmit loopback is activated by placing a low on the  $\overline{RT}$  pin. Terminal and line loopbacks may be applied together, or at the same time as DS3 AIS insertion into the receive or transmit data output signals, as described under the heading "AIS and Loopback Control Signal Arbitration" in the Operation section of this Data Sheet.

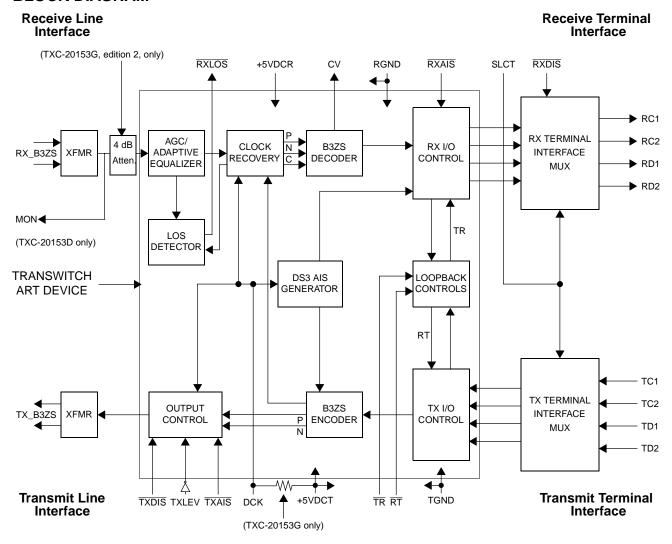

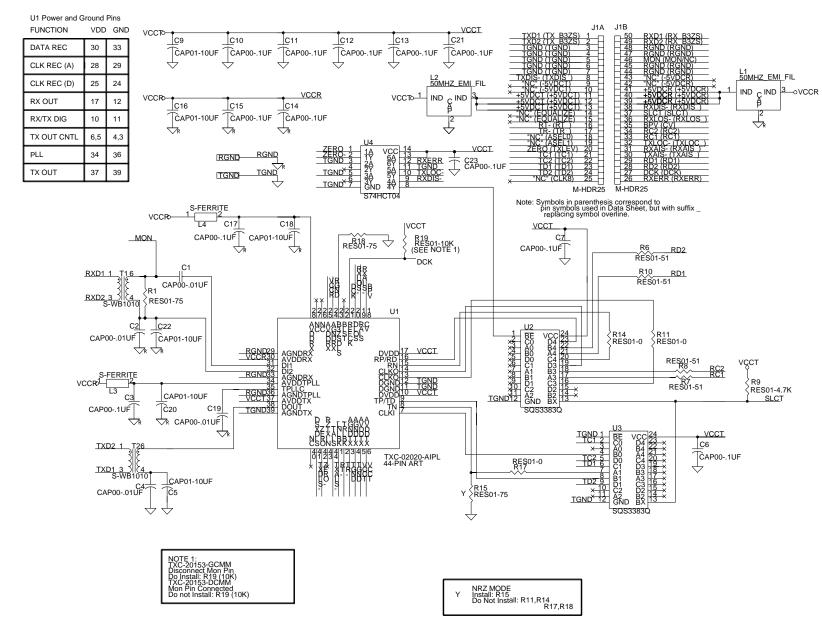

### **PIN DIAGRAM**

Note: Some pins do not perform the functions suggested by their labels, as explained in the Pin Descriptions section.

Figure 2. DS3LIM-SN Pin Diagram

### **PIN DESCRIPTIONS**

| Symbol * | Pin No.       | I/O/P ** | Type *** | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_B3ZS  | 1, 2          | 0        | Analog   | <b>Transmit DS3/STS-1 B3ZS Output:</b> These pins are AC-coupled, B3ZS-encoded DS3 or STS-1 output signals. They may be applied directly to a 75 $\Omega$ BNC connector. It is recommended that pin 2 should be connected to the center pin and pin 1 to the shield of the BNC connector. Under normal operation, this output has a 75 $\Omega$ source impedance. When $\overline{\text{TXDIS}}$ is low, this output is placed into a high-impedance disabled condition. |

| TGND     | 3, 4, 5, 6, 7 | Р        |          | Transmit Ground: Ground pin for transmit side circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TXDIS    | 8             | _        | TTLp     | <b>Transmit Disable:</b> An active low on this pin disables the DS3 or STS-1 transmitted signal. An external $10k\Omega$ pullup resistor to +5V is required to enable transmission.                                                                                                                                                                                                                                                                                      |

| -5VDCT   | 9, 10         | Р        |          | <b>Unused:</b> These pins are not connected within the Module, which does not require a -5V power supply. They may be connected to the -5V power supply in applications originally designed to use the DS3LIM Module. Otherwise they must be left floating.                                                                                                                                                                                                              |

<sup>\*</sup> Note: Symbols used here are the same as for the DS3LIM Module, although there are some pins for which the function is different or absent in the DS3LIM-SN, as indicated under Name/Function.

<sup>\*\*</sup> Note: I=Input; O=Output; P=Power

<sup>\*\*\*</sup> Note: See the Input and Output Parameters section below for digital input and output Type definitions.

| Symbol         | Pin No.    | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------------|------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| +5VDCT         | 11, 12, 13 | Р     |      | <b>Transmit +5VDC:</b> +5V, ±5% DC power supply for transmit side circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| EQUALIZE       | 14, 15     |       |      | <b>Unused:</b> These pins are not connected within the Module, which does not require a strap for short cable equalization. They may be left open or joined together for applications originally designed to use the DS3LIM Module.                                                                                                                                                                                                                                                                                                                                                                          |  |

| RT             | 16         | I     | TTLp | Receive-To-Transmit Loopback: An active low enables the receive (line) loopback feature. This loopback connects the receive terminal NRZ data and clock outputs to the transmit terminal NRZ data and clock inputs, and disables the NRZ transmit inputs. (See Note 1)                                                                                                                                                                                                                                                                                                                                       |  |

| TR             | 17         | I     | TTLp | Transmit-To-Receive Loopback: An active low enables the transmit (terminal) loopback feature. This loopback connects the B3ZS transmit line outputs to the B3ZS receive line inputs, and disables the DS3/STS-1 receive line signal input. (See Note 1)                                                                                                                                                                                                                                                                                                                                                      |  |

| ASEL0<br>ASEL1 | 18<br>19   |       |      | <b>Unused:</b> These pins are not connected within the Module, which does not require amplifier gain select bias. Each may be connected to $+5V$ by a $10k\Omega$ resistor in applications originally designed to use the DS3LIM Module. Otherwise they must be left floating.                                                                                                                                                                                                                                                                                                                               |  |

| TXLEV          | 20         | I     | TTL  | <b>Transmit Level:</b> This pin alters the shape of the transmitted pulse to meet ANSI T1.102 pulse mask requirements at the DSX with different cable lengths. The pin must be pulled high (with a $10k\Omega$ resistor to +5V) for cables shorter than 50 feet and must be set low for cables between 50 and 450 feet long. For applications originally designed to use the DS3LIM Module to meet ANSI mask requirements with 0-450 feet of cable this pin is tied low, and the DS3LIM-SN may not operate correctly with short cables. The transmit output mode is indeterminate if TXLEV is left floating. |  |

| TC1            | 21         | 1     | TTLr | Transmit Input Clock #1: When a high is placed or SLCT lead, TC1 is the input pin for the NRZ transmiclock. This clock has a $50\% \pm 5\%$ duty cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| TC2            | 22         | 1     | TTLr | Transmit Input Clock #2: When a low is placed on th SLCT lead, TC2 is the input pin for the NRZ transmit clock. This clock has a $50\% \pm 5\%$ duty cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| TD1            | 23         | I     | TTL  | DS3/STS-1 Transmit Input Data Port 1: Data is clocked in on positive transitions of TC1. This port is enabled by placing a high on the SLCT lead.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

Note 1: An external  $10k\Omega$  pull-up resistor to +5V is required to disable loopback. Setting  $\overline{RT}$  and  $\overline{TR}$  low simultaneously will enable both line and terminal side loopbacks (see Operation section for additional information on AIS and loopback control signal arbitration).

| Symbol | Pin No. | I/O/P | Туре     | Name/Function                                                                                                                                                                                                                                                                                                                     |

|--------|---------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TD2    | 24      | I     | TTL      | DS3/STS-1 Transmit Input Data Port 2: Data is clocked in on positive transitions of TC2. This port is enabled by placing a low on the SLCT lead.                                                                                                                                                                                  |

| CLK8   | 25      |       |          | <b>Unused:</b> This pin is not connected within the Module, which does not require an 8 kHz clock input as a time base for bit error rate measurement. The pin may have this clock connected in applications originally designed to use the DS3LIM Module. Otherwise it must be left floating.                                    |

| RXERR  | 26      | 0     | Tied low | <b>Unused:</b> This pin is tied low within the Module to simulate a low receive bit error rate indication for applications originally designed to use the DS3LIM Module, in which this pin goes high to indicate a high error rate. This pin should otherwise be left floating, since the DS3LIM-SN does not indicate error rate. |

| DCK    | 27      | I     | CMOS     | <b>External Clock</b> : An external 44.736 MHz (DS3) or 51.840 MHz (STS-1) clock having a stability of $\pm$ 200 ppm ( $\pm$ 20 ppm if the AIS feature is used), and a duty cycle of 50% $\pm$ 5%. If the duty cycle is relaxed, the transmitted mask may not meet pulse mask requirements. (See Note 4.)                         |

| RD2    | 28      | 0     | TTL4mA   | DS3/STS-1 Receive Output Data Port 2: Data is clocked out on negative transitions of RC2 (see Note 1). This port is enabled by placing a low on the SLCT lead. When this port is disabled, by placing a high on SLCT or a low on the RXDIS control lead, the output goes to a high impedance state.                               |

| RD1    | 29      | 0     | TTL4mA   | DS3/STS-1 Receive Output Data Port 1: Data is clocked out on negative transitions of RC1 (see Note 1). This port is enabled by placing a high on the SLCT lead. When this port is disabled, by placing a low on SLCT or a low on the RXDIS control lead, the output goes to a high impedance state.                               |

| TXAIS  | 30      | I     | TTLp     | Transmit AIS: An active low placed on this pin disables the transmit data input, and causes a DS3 alarm indication signal to be generated and sent as transmitted data on the TX_B3ZS output when the Module is operating with DS3 signals. (See Notes 2 and 3.)                                                                  |

- Note 1: Data is also clocked out on negative clock transitions in the DS3LIM Module. The Edition 3 Data Sheet for this Module incorrectly specifies positive transitions in the pin description.

- Note 2: An external  $10k\Omega$  pull-up resistor to +5V is required to enable data and disable the AIS.

- Note 3: DS3 AIS is defined as a valid M-frame with proper subframe structure. The data payload is a 1010 ... sequence starting with a 1 after each overhead bit. Overhead bits are as follows: F0=0, F1=1, M0=0, M1=1; C-bits are set to 0; X-bits are set to 1; and P-bits are set for valid parity.

- Note 4: In the TXC-20153G Module, the DCK input is connected to the Transmit +5VDC supply line via a 10  $k\Omega$  pull-up resistor and its input current characteristics are modified accordingly.

| Symbol | Pin No. | I/O/P | Туре        |                                                                                                                                                                                                                                                                     | N                                                                                                                                                                                                                                                                                                                                                            | lame/Functi                 | on                            |            |  |  |

|--------|---------|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|------------|--|--|

| RXAIS  | 31      | I     | TTLp        | Receive AIS: An active low placed on this pin disable the receive data, input, and causes a DS3 alarm indiction signal to be generated and sent on the RD1 or RI output pins when the Module is operating with DS3 sinals. (See Notes 2 and 3)                      |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

| TXLOC  | 32      | 0     | Pulled high | simulate a<br>nally desig<br>pin goes lo<br>(TC1, TC2<br>wise be le                                                                                                                                                                                                 | Unused: This pin is pulled high within the Module to simulate an error-free indication for applications originally designed to use the DS3LIM Module, in which this pin goes low to indicate that the transmit input clock (TC1, TC2) is stuck high or low. This pin should otherwise be left floating, since the DS3LIM-SN does not indicate loss of clock. |                             |                               |            |  |  |

| RC1    | 33      | 0     | CMOS8mA     | DS3/STS-1 Receive Output Clock Port 1: This port is enabled by placing a high on the SLCT lead. When this port is disabled by placing a low on SLCT or a low on the RXDIS control lead, the output goes to a high impedance state.                                  |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

| RC2    | 34      | 0     | CMOS8mA     | DS3/STS-1 Receive Output Clock Port 2: This port is enabled by placing a low on the SLCT lead. When this port is disabled by placing a high on SLCT or a low on the RXDIS control lead, the output goes to a high impedance state.                                  |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

| CV     | 35      | 0     | CMOS        | one clock                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                              | vided on this               | se having a c<br>s pin whenev |            |  |  |

| RXLOS  | 36      | 0     | CMOS        | <b>Receive Loss of Signal:</b> An active low alarm is generated when $175 \pm 75$ consecutive zeros appear in the incoming data stream. It is cleared when ones pulse density is in the range of 28% to 33% (or more than 33%) for $175 \pm 75$ consecutive pulses. |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

| SLCT   | 37      | I     | CMOSr       |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                              | he ports are<br>wing table: | enabled and                   | d disabled |  |  |

|        |         |       |             | Select High Low                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

|        |         |       |             | RD1 Enabled High Z                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

|        |         |       |             | RC1 Enabled High Z                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

|        |         |       |             | TD1 Enabled Disabled                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

|        |         |       |             | TC1 Enabled Disabled                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

|        |         |       |             |                                                                                                                                                                                                                                                                     | RD2                                                                                                                                                                                                                                                                                                                                                          | High Z                      | Enabled                       |            |  |  |

|        |         |       |             |                                                                                                                                                                                                                                                                     | RC2                                                                                                                                                                                                                                                                                                                                                          | High Z                      | Enabled                       |            |  |  |

|        |         |       |             |                                                                                                                                                                                                                                                                     | TD2                                                                                                                                                                                                                                                                                                                                                          | Disabled                    | Enabled                       |            |  |  |

|        |         |       |             |                                                                                                                                                                                                                                                                     | TC2                                                                                                                                                                                                                                                                                                                                                          | Disabled                    | Enabled                       |            |  |  |

|        |         |       |             |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                              |                             |                               |            |  |  |

| Symbol  | Pin No.        | I/O/P | Туре     | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------|----------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RXDIS   | 38             | I     | CMOSr    | Receive Disable Ports 1 and 2: An active low placed on this pin disables port 1 (RD1 and RC1), and port 2 (RD2 and RC2). The data and clock output signal leads are forced to a high impedance state. An external $10k\Omega$ pull-up resistor to +5V is required to enable port 1 and port 2.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| +5VDCR  | 39, 40, 41     | Р     |          | <b>Receive +5VDC:</b> +5V, $\pm 5\%$ DC power supply input for receive side circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| -5VDCR  | 42, 43         | Р     |          | Unused: These pins are not connected within the Module, which does not require a -5V power supply. They may be connected to the -5V power supply in applications originally designed to use the DS3LIM Module. Otherwise they must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RGND    | 44, 45, 47, 48 | Р     |          | Receive Ground: Ground pins for receive side circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| MON/NC  | 46             | O/-   | Analog/- | For TXC-20153D: DS3/STS-1 Received Signal Monitor Point: This output is directly tied to the terminating resistor after transformer coupling. Care must be taken to ensure very short trace lengths to the MON buffer, or oscillation of the AGC may occur. If a monitor output is not required, it is suggested that this pin be left open.  For TXC-20153G (Edition 1 and Edition 2): No Connect: This pin is not connected within the Module, which provides no capability to monitor the received input signal. This pin may be connected to an external termination in applications originally designed to use the DS3LIM Module, but it should otherwise be treated as a |  |  |

| RX_B3ZS | 49, 50         | I     | Analog   | "No Connect" pin and should be left floating.  Receive DS3/STS-1 B3ZS Input: These pins are the AC-coupled B3ZS-encoded DS3 or STS-1 input signal. They may come directly from a $75\Omega$ ohm BNC connector. If these signals originate from a BNC connector, it is recommended that the center pin should be connected to pin 50 and the shield to pin 49.                                                                                                                                                                                                                                                                                                                  |  |  |

# **ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS**

| Parameter                     | Symbol          | Min  | Max                   | Unit  | Conditions                     |

|-------------------------------|-----------------|------|-----------------------|-------|--------------------------------|

| +5V supply voltages           | V <sub>DD</sub> |      | +7.0                  | V     | Note 1                         |

| DC input voltage              | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V     | Note 1                         |

| Storage temperature range     | T <sub>S</sub>  | -55  | 150                   | °C    | Note 1                         |

| Ambient operating temperature | T <sub>A</sub>  | 0    | 70                    | °C    | 0 ft/min linear airflow        |

| Moisture Exposure Level       | ME              | 5    |                       | Level | per EIA/JEDEC<br>JESD22-A112-A |

| Relative Humidity, in-circuit | RH              | 0    | 100                   | %     | Non-condensing.<br>Note 2.     |

#### Notes:

- 1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

- 2. Pre-assembly storage in non-drypack conditions is not recommended. Please refer to the instructions on the "CAUTION" label on the drypack bag in which the Modules are supplied.

### **POWER REQUIREMENTS**

| Parameter       | Min  | Тур | Max  | Unit | Test Conditions         |

|-----------------|------|-----|------|------|-------------------------|

| V <sub>DD</sub> | 4.75 | 5.0 | 5.25 | V    |                         |

| I <sub>DD</sub> |      |     | 290  | mA   | V <sub>DD</sub> = 5.25V |

| P <sub>DD</sub> |      |     | 1.5  | W    | V <sub>DD</sub> = 5.25V |

# **INPUT AND OUTPUT PARAMETERS**

# **Input Parameters for CMOS**

| Parameter            | Min                                     | Тур | Max                   | Unit | Test Conditions         |

|----------------------|-----------------------------------------|-----|-----------------------|------|-------------------------|

| V <sub>IH</sub>      | V <sub>DD</sub> - (V <sub>DD</sub> / 3) |     | V <sub>DD</sub> + 0.3 | V    |                         |

| V <sub>IL</sub>      | - 0.3                                   |     | (V <sub>DD</sub> / 3) | V    |                         |

| I <sub>IH</sub>      |                                         |     | - 10                  | μΑ   | V <sub>DD</sub> = 5.25V |

| I <sub>IL</sub>      |                                         |     | 10                    | μΑ   | V <sub>DD</sub> = 5.25V |

| Input<br>Capacitance |                                         |     | 10                    | pF   |                         |

## **Input Parameters For CMOSr**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                   |

|-----------------------|-----|-----|-----|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| Input leakage current |     | 50  | 120 | μΑ   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |     | 5.5 |     | pF   |                                                   |

Note: Input has a 100k (nominal) internal pull-up resistor.

# **Input Parameters For TTL**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                   |

|-----------------------|-----|-----|-----|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                      |

| Input leakage current |     |     | 10  | μΑ   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |     | 5.5 |     | pF   |                                                   |

## **Input Parameters for TTLp**

| Parameter            | Min   | Тур | Max                   | Unit | Test Conditions         |

|----------------------|-------|-----|-----------------------|------|-------------------------|

| V <sub>IH</sub>      | 2.0   |     | V <sub>DD</sub> + 0.3 | V    |                         |

| V <sub>IL</sub>      | - 0.3 |     | 0.8                   | V    |                         |

| I <sub>IH</sub>      |       |     | - 10                  | μΑ   | V <sub>DD</sub> = 5.25V |

| I <sub>IL</sub>      |       |     | 550                   | μΑ   | V <sub>DD</sub> = 5.25V |

| Input<br>Capacitance |       |     | 10                    | pF   |                         |

Note: All TTLp inputs have an internal pull-up resistor.

# **Input Parameters For TTLr**

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                   |

|-----------------------|-----|-----|-----|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| Input leakage current |     | 50  | 120 | μΑ   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |     | 5.5 |     | pF   |                                                   |

Note: Input has a 100k (nominal) internal pull-up resistor.

# **Output Parameters for CMOS**

| Parameter         | Min                   | Тур | Max   | Unit | Test Conditions           |

|-------------------|-----------------------|-----|-------|------|---------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |       | V    | 4 mA source               |

| V <sub>OL</sub>   |                       |     | 0.5   | V    | 4 mA sink                 |

| I <sub>OH</sub>   |                       |     | - 4.0 | mA   | V <sub>DD</sub> = 4.75V   |

| I <sub>OL</sub>   |                       |     | 4.0   | mA   | V <sub>DD</sub> = 4.75V   |

| t <sub>RISE</sub> | 1.7                   | 2.7 | 4.2   | ns   | C <sub>LOAD</sub> = 15 pF |

| t <sub>FALL</sub> | 1.9                   | 2.8 | 4.1   | ns   | C <sub>LOAD</sub> = 15 pF |

# **Output Parameters For CMOS8mA**

| Parameter         | Min                   | Тур | Max  | Unit | Test Conditions                              |

|-------------------|-----------------------|-----|------|------|----------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |      | V    | $V_{DD} = 4.75$ ; $I_{OH} = -8.0 \text{ mA}$ |

| V <sub>OL</sub>   |                       |     | 0.4  | V    | $V_{DD} = 4.75$ ; $I_{OL} = 8.0 \text{ mA}$  |

| I <sub>OL</sub>   |                       |     | 8.0  | mA   |                                              |

| I <sub>OH</sub>   |                       |     | -8.0 | mA   |                                              |

| t <sub>RISE</sub> | 1.3                   | 2.4 | 3.8  | ns   | C <sub>LOAD</sub> = 25 pF                    |

| t <sub>FALL</sub> | 1.1                   | 1.8 | 2.5  | ns   | C <sub>LOAD</sub> = 25 pF                    |

## **Output Parameters For TTL4mA**

| Parameter         | Min | Тур | Max  | Unit | Test Conditions                                   |

|-------------------|-----|-----|------|------|---------------------------------------------------|

| V <sub>OH</sub>   | 2.4 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 mA |

| V <sub>OL</sub>   |     |     | 0.6  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0 mA  |

| I <sub>OL</sub>   |     |     | 4.0  | mA   |                                                   |

| I <sub>OH</sub>   |     |     | -4.0 | mA   |                                                   |

| t <sub>RISE</sub> | 2.8 | 6.5 | 9.2  | ns   | C <sub>LOAD</sub> = 15 pF                         |

| t <sub>FALL</sub> | 1.3 | 2.3 | 3.4  | ns   | C <sub>LOAD</sub> = 15 pF                         |

# **Receiver Sensitivity**

| Parameter     | Min | Тур | Max | Unit | Test Conditions |

|---------------|-----|-----|-----|------|-----------------|

| Dynamic Range | 100 |     | 950 | mVp  |                 |

# **Input Parameters For Transformer Coupling**

| Parameter         | Min  | Тур  | Max  | Unit | Test Conditions                                  |

|-------------------|------|------|------|------|--------------------------------------------------|

| Return Loss       |      | - 26 |      | dB   | DS3: 22.368 MHz; 25°C<br>STS-1: 25.920 MHz; 25°C |

| Isolation Voltage |      |      | 300  | Vrms |                                                  |

| Turns Ratio       |      | 1:1  |      |      |                                                  |

| Input Impedance   | 67.5 | 75   | 82.5 | ohms |                                                  |

# **Output Parameters For Transformer Coupling**

| Parameter                    | Min  | Тур  | Max  | Unit | Test Conditions |

|------------------------------|------|------|------|------|-----------------|

| Isolation Voltage            |      |      | 300  | Vrms |                 |

| Turns Ratio                  |      | 1:1  |      |      |                 |

| Output Impedance (TXDIS = 1) | 67.5 | 75   | 82.5 | ohms |                 |

| Output Impedance (TXDIS = 0) | 100k | 200k |      | ohms |                 |

### TIMING CHARACTERISTICS

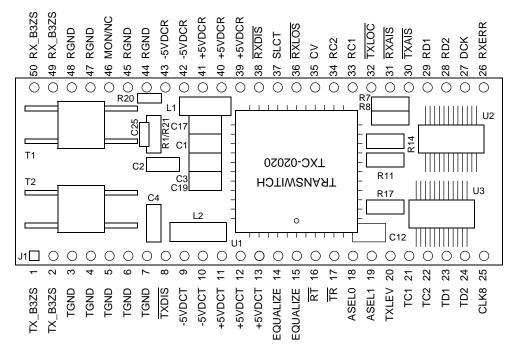

Detailed timing diagrams for the DS3LIM-SN are illustrated in Figures 3 through 6. All output times are measured with the maximum load capacitance appropriate for the pin type. Timing parameters are measured at signal levels of  $(V_{OH} + V_{OL})/2$  for outputs or  $(V_{IH} + V_{IL})/2$  for inputs.

#### **Line Side Timing Characteristics**

The line side signal characteristics are designed so that the output meets the requirements of ANSI standard T1.102-1993. When terminated into a test load of  $75\Omega \pm 5\%$  using ATT 734A coaxial cable the DS3LIM-SN Module will meet the DS3 or STS-1 interface isolated pulse masks defined below in Figures 3a through 3c for a cable length of 0 to 450 feet. For STS-1 pulse sequences, the output also meets the STS-1 interface eye diagram mask shown in Figure 3d.

<sup>\*</sup> Note: The DS3 curves shown are approximate representations of the equations in Figure 3b. The corresponding STS-1 curves (not shown) would be slightly different, as indicated by the equations in Figure 3c.

Figure 3a. DS3 Interface Isolated Pulse Mask

<sup>\*\*</sup>Note: UI = 1 / (System Clock Frequency)

| CURVE                       | TIME IN<br>UNIT INTERVALS                                                 | NORMALIZED<br>AMPLITUDE                                                                                                  |

|-----------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| MAXIMUM<br>(UPPER)<br>CURVE | $-0.85 \le T \le -0.68$<br>$-0.68 \le T \le 0.36$<br>$0.36 \le T \le 1.4$ | 0.03<br>0.5 $\left[1 + \sin{\frac{\pi}{2}}(1 + \frac{T}{0.34})\right] + 0.03$<br>0.08 + 0.407e -1.84(T-0.36)             |

| MINIMUM<br>(LOWER)<br>CURVE | $-0.85 \le T \le -0.36$<br>$-0.36 \le T \le 0.36$<br>$0.36 \le T \le 1.4$ | $ \begin{array}{c} -0.03 \\ 0.5 \left[ 1 + \sin \frac{\pi}{2} (1 + \frac{T}{0.18}) \right] - 0.03 \\ -0.03 \end{array} $ |

Figure 3b. DS3 Interface Isolated Pulse Mask Equations

| CURVE                       | TIME IN<br>UNIT INTERVALS                                                 | NORMALIZED<br>AMPLITUDE                                                                                                  |

|-----------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| MAXIMUM<br>(UPPER)<br>CURVE | $-0.85 \le T \le -0.68$<br>$-0.68 \le T \le 0.26$<br>$0.26 \le T \le 1.4$ | 0.03<br>0.5 $\left[1 + \sin{\frac{\pi}{2}}(1 + \frac{T}{0.34})\right] + 0.03$<br>0.1 + 0.61e -2.4(T-0.26)                |

| MINIMUM<br>(LOWER)<br>CURVE | $-0.85 \le T \le -0.38$<br>$-0.38 \le T \le 0.36$<br>$0.36 \le T \le 1.4$ | $ \begin{array}{c} -0.03 \\ 0.5 \left[ 1 + \sin \frac{\pi}{2} (1 + \frac{T}{0.18}) \right] - 0.03 \\ -0.03 \end{array} $ |

Figure 3c. STS-1 Interface Isolated Pulse Mask Equations

\*Note: UI = 1 / (System Clock Frequency)

| Out   | er region corner p | oints     | Inne  | er region corner p | gion corner points |  |  |

|-------|--------------------|-----------|-------|--------------------|--------------------|--|--|

| Point | Time               | Amplitude | Point | Time               | Amplitude          |  |  |

| А     | -0.5               | 0.426     | 1     | -0.245             | 0.214              |  |  |

| В     | -0.261             | 0.904     | J     | -0.187             | 0.455              |  |  |

| С     | -0.136             | 1.03      | К     | -0.104             | 0.67               |  |  |

| D     | -0.028             | 1.03      | L     | -0.017             | 0.67               |  |  |

| Е     | 0.094              | 0.883     | М     | 0.077              | 0.581              |  |  |

| F     | 0.187              | 0.723     | N     | 0.18               | 0.14               |  |  |

| G     | 0.31               | 0.566     | 0     | -0.054             | 0.16               |  |  |

| Н     | 0.5                | 0.426     |       |                    |                    |  |  |

Note - Both inner and outer regions are symmetric about zero amplitude axis.

Figure 3d. STS-1 Interface Eye Diagram Mask

# **Terminal Side Timing Characteristics**

Figure 4. NRZ Transmit Input Timing

| Parameter                                                 | Symbol           | Min | Тур    | Max | Unit |

|-----------------------------------------------------------|------------------|-----|--------|-----|------|

| TC1, TC2 DS3 input clock period                           | t <sub>CYC</sub> |     | 22.353 |     | ns   |

| TC1, TC2 STS-1 input clock period                         | t <sub>CYC</sub> |     | 19.290 |     | ns   |

| TC1, TC2 high time                                        | t <sub>PWH</sub> | 10  |        |     | ns   |

| TC1, TC2 duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                  | 45  |        | 55  | %    |

| TD1, TD2 set-up time to TC1↑, TC2↑                        | t <sub>SU</sub>  | 4.0 |        |     | ns   |

| TD1, TD2 hold time after TC1↑, TC2↑                       | t <sub>H</sub>   | 3.0 |        |     | ns   |

Note: TC1, TC2 symmetry is measured about the 1.4VDC threshold in order to assure symmetric output waveforms.

Figure 5. NRZ Receive Output Timing

| Parameter                                                 | Symbol             | Min | Тур    | Max | Unit |

|-----------------------------------------------------------|--------------------|-----|--------|-----|------|

| RC1, RC2 DS3 output clock period                          | t <sub>CYC</sub>   |     | 22.353 |     | ns   |

| RC1, RC2 STS-1 output clock period                        | t <sub>CYC</sub>   |     | 19.290 |     | ns   |

| RC1, RC2 high time                                        | t <sub>PWH</sub>   | 10  |        |     | ns   |

| RC1, RC2 duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                    | 45  |        | 55  | %    |

| RD1, RD2 output delay after RC1↓, RC2↓ (RXAIS = 1)        | t <sub>OD(1)</sub> | 1.0 |        | 5.5 | ns   |

| RD1, RD2 output delay after RC1↓, RC2↓ (RXAIS = 0)        | t <sub>OD(1)</sub> | 1.0 |        | 6.5 | ns   |

| CV output delay after RC1↓, RC2↓                          | t <sub>OD(2)</sub> | 1.0 |        | 5.5 | ns   |

Note: RC1, RC2 symmetry is measured about the 50% amplitude point.

Figure 6. Coding Violation Pulse Timing

| Parameter                             | Symbol           | Min | Тур | Max | Unit* |

|---------------------------------------|------------------|-----|-----|-----|-------|

| CV pulse width                        | t <sub>PW</sub>  | 0.9 | 1.0 | 1.1 | UI    |

| CV pulse high time                    | t <sub>PWH</sub> | 0.8 | 0.9 | 1.0 | UI    |

| CV delay from occurrence of violation | t <sub>D</sub>   |     | 7.0 |     | UI    |

\*Note: UI = 1 / (System Clock Frequency)

#### **OPERATION**

### **Receiver Input Requirements**

| Parameter                      | Value                                                                                                                                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Cable                | AT&T 728A/734A coaxial (or equivalent)                                                                                                           |

| Bit Rate:                      |                                                                                                                                                  |

| DS3                            | 44.736 Mbit/s ± 20 ppm                                                                                                                           |

| STS-1                          | 51.840 Mbit/s ± 20 ppm                                                                                                                           |

| Line Code                      | B3ZS                                                                                                                                             |

| Input Signal Amplitude:        | 100 mVp - 0.95 Vp AC (differential input)                                                                                                        |

| Cable Length                   | 0 - 900 feet                                                                                                                                     |

| Input Return Loss:             |                                                                                                                                                  |

| DS3                            | > 26 dB at 22.368 MHz with external 75Ω resistor                                                                                                 |

| STS-1                          | > 26 dB at 25.920 MHz with external 75Ω resistor                                                                                                 |

| Input Resistance               | $> 5k\Omega$                                                                                                                                     |

| Signal-to-Noise Toler-<br>ance | No greater than either the value produced by adjacent pulses in the data stream or $\pm 10\%$ of the peak pulse amplitude, whichever is greater. |

| Input Jitter Tolerance         | As defined by Figures 7a, 7b and 7c: "Input Jitter Tolerance"*                                                                                   |

<sup>\*</sup>Note: Refer to the Operation - Jitter Tolerance subsection below for DS3 and STS-1 minimum requirements and measured values.

## **Interfering Tone Tolerance**

The DS3LIM-SN will properly recover clock and present error-free output to the receive terminal side interface\* in the presence of a sinusoidal interfering tone signal at the following line rates:

## **Interfering Tone Tolerance**

| Data Rate (Mbit/s) | Tone Frequency (MHz) | Maximum Tone Level |

|--------------------|----------------------|--------------------|

| 51.84              | 25.97                | -20 dB             |

| 44.736             | 22.4                 | -20 dB             |

<sup>\*</sup>Note: See Figure 8: "Interference Margin Test Configuration"

### **Receiver Output Specifications**

| Parameter                               | Value                                                                    |

|-----------------------------------------|--------------------------------------------------------------------------|

| Clock Recovery Jitter<br>Peaking        | 1 dB maximum                                                             |

| Clock Recovery PLL pull-in time         | < 100 μS                                                                 |

| Sequences Reported as Coding Violations | ++,, not B0V, not 00V, three or more consecutive zeros (excessive zeros) |

### **Transmitter Specifications**

Note: A 75 $\Omega$  ±5% output load is assumed in these specifications. Measurements made at transmitter unless otherwise noted.

| Parameter                                   | Value                                                                                                                            |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| TX_B3ZS Output Characteristics, TXLEV low:  | The two pulse shapes specified below are to be measured at the end of 50-450 feet of cable, terminated by a $75\Omega$ resistor. |

| Pulse Shape (DS3)                           | As defined by Figure 2 in ANSI TI.404-1994                                                                                       |

| Pulse Shape (STS-1)                         | As defined by Figure 4-10 in GR-253-CORE, Issue 2, December 1995                                                                 |

| Amplitude                                   | ±0.81 Volts ±10% for DS3; ±0.95 for STS-1                                                                                        |

| Output jitter                               | 0.05 UI maximum with jitter-free input clock on TC1, TC2                                                                         |

| TX_B3ZS Output Characteristics, TXLEV high: | The two pulse shapes specified below are to be measured at the end of 0-50 feet of cable, terminated by a $75\Omega$ resistor.   |

| Pulse Shape (DS3)                           | As defined by Figure 2 in ANSI TI.404-1994                                                                                       |

| Pulse Shape (STS-1)                         | As defined by Figure 4-10 in GR-253-CORE, Issue 2, December 1995                                                                 |

| Amplitude                                   | ±0.67 Volts ±10% for DS3; ±0.8 for STS-1                                                                                         |

| Output jitter                               | 0.05 UI maximum with jitter-free input clock on TC1, TC2                                                                         |

<sup>\*</sup>Note: UI = 1 / (System Clock Frequency)

## **AIS and Loopback Control Signal Arbitration**

The response of the Module to combinations of the  $\overline{\text{RXAIS}}$ ,  $\overline{\text{TXAIS}}$ ,  $\overline{\text{RT}}$  and  $\overline{\text{TR}}$  input signals is tabulated below:

| RXAIS * | TXAIS * | RT (line) | TR (term.) | Terminal Output | Line Output   |

|---------|---------|-----------|------------|-----------------|---------------|

| 1       | 1       | 1         | 1          | Normal          | Normal        |

| 1       | 0       | Х         | 1          | Normal          | AIS           |

| 1       | 0       | Х         | 0          | Term Loopback   | AIS           |

| 0       | 1       | 1         | Х          | AIS             | Normal        |

| 0       | 1       | 0         | Х          | AIS             | Line Loopback |

| 0       | 0       | Х         | Х          | AIS             | AIS           |

| 1       | 1       | 1         | 0          | Term Loopback   | Normal        |

| 1       | 1       | 0         | 1          | Normal          | Line Loopback |

| 1       | 1       | 0         | 0          | Term Loopback   | Line Loopback |

Note: X = Don't Care

<sup>\*</sup> These signals may only be applied (active low) when the Module is operating with DS3 signals.

#### **Jitter Transfer**

Transfer of jitter through an individual unit of digital equipment is characterized by the relationship between the applied input jitter and the resulting output jitter as a function of frequency.

For DS3, Bellcore Technical Reference GR-499-CORE, Issue 1, December 1995 further describes and defines jitter transfer.

For STS-1, Bellcore Technical Reference GR-253-CORE, Issue 2, December 1995 further describes and defines jitter transfer.

In a looped back configuration (through the receive path and externally looped back through the transmit path), in the absence of applied input jitter the amount of jitter introduced by the DS3LIM-SN is maximum 0.065 Unit Intervals (UIs, where UI is 1 / System Clock Frequency) of peak-to-peak jitter over a jitter frequency range of 20 Hz to 1 MHz (filter with high-pass of 10 Hz and a low-pass of 1.1 MHz).

With applied input jitter, the maximum output jitter is the applied input jitter plus the above jitter introduced by the DS3LIM-SN.

#### **Jitter Generation**

Jitter generation is the process whereby jitter appears at the output port of an individual unit of digital equipment in the absence of applied input jitter.

For DS3, Bellcore Technical Reference GR-499-CORE, Issue 1, December 1995 specifies the maximum jitter generation to be 1.0 UI of peak-to-peak at the output of the terminal receiver for Category I equipment.

For STS-1, Bellcore Technical Reference GR-253-CORE, Issue 2, December 1995 specifies the maximum jitter generation to be 1.5 UI peak-to-peak maximum at the output of the terminal receiver for Category I equipment.

In a looped back configuration (through the transmit path and externally looped back through the receive path), the DS3/STS-1 jitter generation within the DS3LIM-SN is 0.145 UI peak-to-peak maximum for all frequencies specified in these two standards.

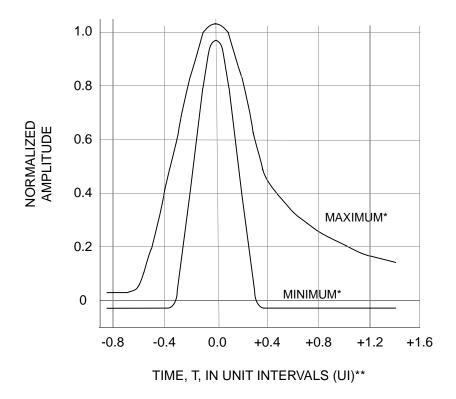

#### **Jitter Tolerance**

#### DS3:

Input jitter tolerance is the maximum amplitude of sinusoidal jitter at a given jitter frequency, which, when modulating the signal at an equipment port, results in no more than two errored seconds cumulative, where these errored seconds are integrated over successive 30-second measurement intervals, and the jitter amplitude is increased in each succeeding measurement interval.

Requirements for input jitter tolerance are specified in terms of compliance with a jitter mask, which represents a combination of points. Each point corresponds to minimum amplitude of sinusoidal jitter at a given jitter frequency which, when modulating the signal at an equipment input port, results in two or fewer errored seconds in a 30-second measurement interval. Bellcore Technical Reference GR-499-CORE, Issue 1, December 1995 specifies the minimum requirement mask for Category I and Category II equipment, which are shown in Figures 7a and 7b.