# TCLD0110G 10 Gbits/s Clocked Laser Driver

#### **Features**

- Internal optional data retiming latch to minimize output data pattern dependent jitter.

- 100 mA current drive capability (20  $\Omega$  load).

- Patent pending active termination output buffer to reduce power dissipation.

- Differential data and clock inputs.

- Single –5.2 V power supply.

- 25 ps rise and fall times.

- 2.0 ps rms jitter.

- Available in die form.

- Clock disable mode for data feed through.

- Laser shutdown mode.

## **Applications**

- Optical transmitters.

- Digital video transmission.

- SONET/SDH test equipment.

- SONET/SDH OC-192/STM-64 transmission systems.

- 10.7 Gbits/s and 12.5 Gbits/s forward error correction (FEC).

- 10G Ethernet 10.3125 Gbits/s.

#### **Functional Description**

The TCLD0110G is intended to drive direct modulated lasers at speeds up to 12.5 Gbits/s. The driver consists of an input level translator and limiting amplifier, followed by a pulse-width control circuit and dual output buffers with adjustable modulation current. The TCLD0110G also contains an adjustable bias current generator that can supply up to 100 mA of laser bias current.

The two output buffers can be combined to drive up to 100 mA into a 20  $\Omega$  to 25  $\Omega$  load. Alternatively, one buffer can be used to drive up to 50 mA into a 40  $\Omega$  to 50  $\Omega$  load. In the latter case, the unused output buffer is disabled to save power.

Each output buffer provides an active 50  $\Omega$  back termination that can absorb reflections and thus minimize jitter and overshoot. An internal operational amplifier is used to track the voltage drop across the laser and to allow dc coupling to the laser without excess loading of the laser bias circuit.

On-die sense resistors allow monitoring of both modulation and bias currents and can be employed as part of an external control loop.

For applications using an unregualted power supply, a connection is avaliable for an external 2.5 V shunt voltage reference used to stabilize operation over-temperature and power supply voltage range.

A selectable internal data retiming latch is integrated into this device. When an input clock is available, the internal latch can be used to eliminate pattern-dependent jitter on the data input. If no clock is available, the latch is disabled and the input signal bypasses this circuit.

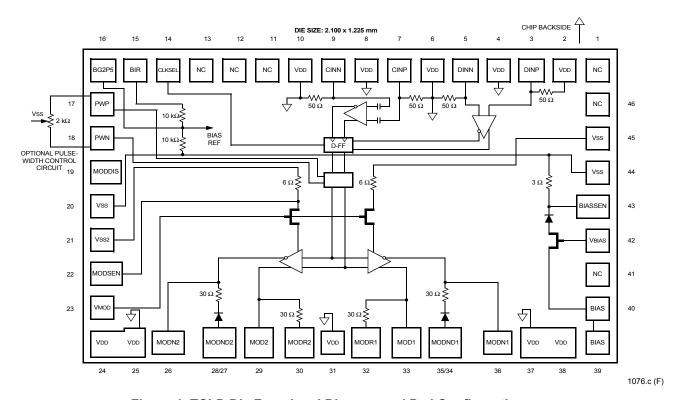

### **Functional Diagram**

Figure 1. TCLD Die Functional Diagram and Pad Configuration

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET: http://www.agere.com E-MAIL: docmaster@agere.com

N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA: Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC

Tel. (86) 21 50471212, FAX (86) 21 50472266

JAPAN: Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

EUROPE: Data Requests: DATALINE: **Tel. (44) 7000 582 368**, FAX (44) 1189 328 148

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot),

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.