TLCS-90 Series TMP90C141

#### **CMOS 8-Bit Microcontrollers**

#### TMP90C141N/TMP90C141F

#### 1. Outline and Characteristics

The TMP90C141 is a high-speed advanced 8-bit microcontroller applicable to a variety of equipment.

With its 8-bit CPU, A/D converter, multi-function timer/ event counter and general-purpose serial interface integrated into a single CMOS chip, the TMP90C041 allows the expansion of external memories for programs (up to 64K byte) and data (1M byte).

The TMP90C141N is a 64-pin shrink DIP product. (SDIP64-P750)

The TMP90C041F is a 64-pin flat package product. (QFP64-P1420A)

The characteristics of the TMP90C141 include:

- (1) Powerful instructions: 163 basic instructions, including Multiplication, division, 16-bit arithmetic operations, bit manipulation instructions

- (2) Minimum instruction executing time:320ns (at 12.5MHz oscillation frequency)

- (3) Internal RAM

- (4) Memory expansionExternal program memory: 63K byteExternal data memory: 1M byte

- (5) 8-bit A/D converter (6 channels)

- (6) General-purpose serial interface (1 Channel) Asynchronous mode, I/O interface mode

- (7) Multi-function 16-bit timer/event counter (1 channel)

- (8) 8-bit timers (4 channels)

- (9) Stepping motor control port (2 channels)

- (10) Input/Output ports (28 pins)

- (11) Interrupt function:10 internal interrupts and 4 external interrupts

- (12) Micro Direct Memory Access (µDMA) function (11 channels)

- (13) Watchdog timer

- (14) Standby function (4 HALT modes)

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments (office equipment, communication equipment, measuring equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

TOSHIBA CORPORATION 1/12

The information contained here is subject to change without notice.

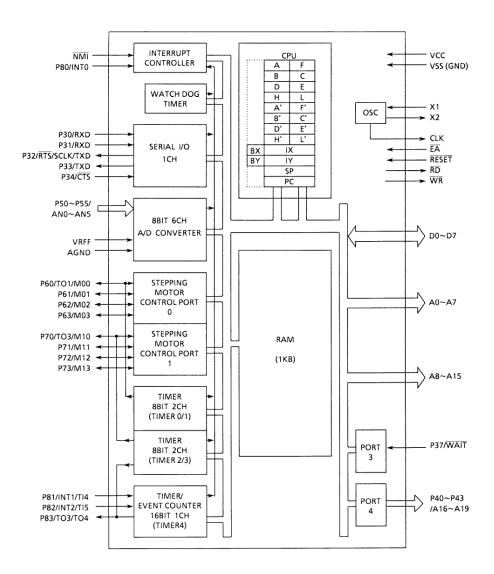

Figure 1. TMP90C141 Block Diagram

## 2. Pin Assignment and Functions

#### 2.1 Pin Assignment

The assignment of input/output pins, their names and functions are described below.

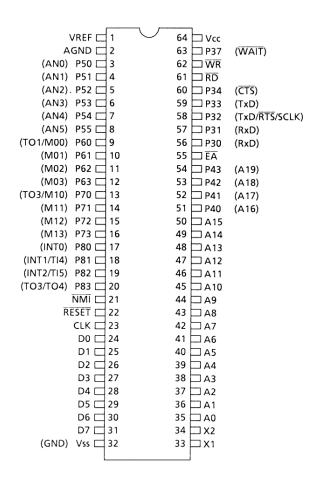

Figure 2.1 (1) shows pin assignment of the TMP90C141N.

Figure 2.1 (1). Pin Assignment (Shrink Dual Inline Package)

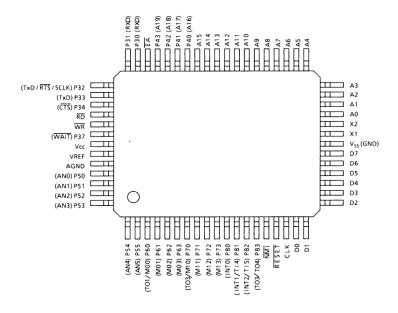

Figure 2.1 (2) shows pin assignment of

theTMP90C141F.

Figure 1. 1 (2). Pin Assignment (Flat Package)

#### 2.2 Pin Names and Functions

rized in Table 2.2.

The names of input/output pins and their functions are summa-

Table 2.2 Pin Names and Functions (1/2)

| Pin Name      | No. of pins | I/O 3 states | Function                                                                                |

|---------------|-------------|--------------|-----------------------------------------------------------------------------------------|

| D0 ~ D7       | 8           | 3 states     | Data bus: Also functions as 8-bit bidirectional data bus for external memory            |

| A0 ~ A7       | 8           | Output       | Address bus: The lower 8 bits address bus for external memory                           |

| A8 ~ A15      | 8           | Output       | Address bus: The upper 8 bits address bus for external memory                           |

| P30           | 1           | Input        | Port 30: 1-bit input port                                                               |

| /RxD          | 1           | Прис         | Receiver Serial Data                                                                    |

| P31           | 1           | Input        | Port 31: 1-bit input port                                                               |

| /RxD          | ı           | IIIput       | Receiver Serial Data                                                                    |

| P32           |             |              | Port 32: 1-bit input port                                                               |

| /TxD          | 1           | Output       | Transmitter Serial Data                                                                 |

| /RTS<br>/SCLK | !           | Output       | Request to send Serial Data                                                             |

| /SULK         |             |              | Serial clock output                                                                     |

| P33           | 1           | Output       | Port 33: 1-bit output port                                                              |

| /TxD          | !           | Output       | Transmitter Serial Data                                                                 |

| P34           | 1           | Input        | Port 34: 1-bit input port                                                               |

| /CTS          | 1           | mpat         | Clear to send Serial data                                                               |

| RD            | 1           | Output       | Read: Generates strobe signal for reading external memory                               |

| WR            | 1           | Output       | Write: Generates strobe signal for writing into external memory                         |

| <u>P37</u>    | 1           | Input        | Port 37: 1-bit input port                                                               |

| /WAIT         | ı ı         | IIIput       | Wait: Input pin for connecting slow speed memory or peripheral LSI                      |

| P40 ~ P43     |             |              | Port 4: 4-bit output port that allows selection of Port/Address Bus on bit basis        |

| /A16 ~ A19    | 4           | Output       | Address bus: Also functions as address bus for external memory (4 bits of bank address) |

Table 2.2 Pin Names and Functions (2/2)

| Pin Name              | No. of Pins | I/O 3 states     | Function                                                                         |

|-----------------------|-------------|------------------|----------------------------------------------------------------------------------|

| P50 ~ P55             | C           | lanut            | Port 5: 6-bit input port                                                         |

| /AN0 ~ AN5            | 6           | Input            | Analog input: 6 analog input to A/D converter                                    |

| VREF                  | 1           | -                | Input of reference voltage to A/D converter                                      |

| AGND                  | 1           | _                | Ground pin for A/D converter                                                     |

| P60 ~ P63             |             | 1/0              | Port 6: 4-bit I/O port that allows I/O selection on bit basis                    |

| /M00 ~ M03            | 4           | Output           | Stepping motor control port 0                                                    |

| /T01                  |             | Output           | Timer output 1: Output of Timer 0 or 1                                           |

| P70 ~ P73             |             | 1/0              | Port 7: 4-bit I/O port that allows I/O selection on bit basis                    |

| /M10 ~ M13            | 4           | Output           | Stepping motor control port 1                                                    |

| /T03                  |             | Output           | Timer output 3: Output of timer 2 or 3                                           |

|                       |             |                  | Port 80: 1-bit input port                                                        |

| P80                   |             |                  | Interrupt request pin 0: Interrupt request pin (Level/rising edge is             |

| /INTO                 | 1           | Input            | programmable)                                                                    |

|                       |             |                  |                                                                                  |

|                       |             |                  | Port 81: 1-bit input port                                                        |

| P81                   |             |                  | Interrupt request pin 1: Interrupt request pin (Rising/falling edge is           |

| /INT1                 | 1           | Input            | programmable)                                                                    |

| /TI4                  |             |                  |                                                                                  |

|                       |             |                  | Timer input 4: Counter/capture trigger signal for Timer 4                        |

| P82                   |             |                  | Port 82: 1-bit input port                                                        |

| /INT2                 | 1           | Input            | Interrupt request pin 2: rising edge interrupt request pin                       |

| /TI5                  |             |                  | Timer input 5: capture trigger signal for Timer 4                                |

| P82                   | 4           | 0.44             | Port 83: 1-bit output port                                                       |

| /T03/T04              | 1           | Output           | Timer output 3/4: Output of Timer 2, 3 or 4                                      |

|                       |             |                  | Non-maskable interrupt request pin: Falling edge interrupt request pin           |

| NMI                   | 1           | Input            |                                                                                  |

| CLK                   | 1           | Output           | Clock output: Generates clock pulse at 1/4 frequency of clock oscillation. It is |

| ULN                   | l l         | Output           | Pulled up internally during resetting.                                           |

| ĒΑ                    | 1           | Input            | External access: Connects with GND pin in the TMP90C141 with no internal         |

| RESET                 | 1           | · ·              | ROM.  Reset: Initializes the TMP90C141. (Built-in pull-up resister)              |

| UESEI                 | ·           | Input            |                                                                                  |

| X1/X2                 | 2           | Input/<br>Output | Pin for quartz crystal or ceramic resonator                                      |

| V <sub>CC</sub>       | 1           | _                | Power supply (+5V)                                                               |

| V <sub>SS</sub> (GND) | 1           | _                | Ground (OV)                                                                      |

### 3. Operation

The following explains the TMP90C141 functions and basic operations. The CPU functions and internal I/O functions of the TMP90C141 are the same as the TMP90C840A.

Refer to the "TMP90C840A" section concerning functions which are not explained the following.

#### 3.1 CPU

The TMP90C141 has an internal high-performance 8-bit CPU. Refer to the "TLCS-90 CPU" section concerning CPU operation.

#### 3.2 Memory Map

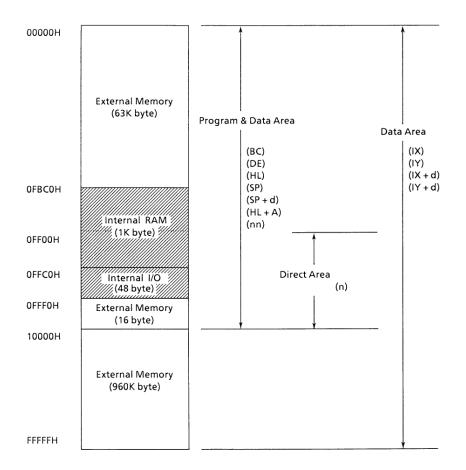

The TMP90C141 supports a program memory of up to 64K bytes and a data memory of maximum 1M bytes.

The program memory may be assigned to the address space from 00000H to 0FFFFH, while the data memory can be allocated to any address from 00000H to FFFFFH.

#### (1) Internal RAM

The TMP90C141 internally contains a 1K byte RAM, which is allocated to the address space from FBC0H to FFBFH. The CPU allows the access to a certain RAM area (FF00H to FFBFH, 192 bytes) by a short operation code (opcode) in a "direct addressing mode".

The addresses from FF10H to FF7FH in this RAM area can be used as parameter area for micro DMA processing (and for any other purposes when the micro DMA function is not used).

#### (2) Internal I/O

The TMP90C141 provides a 48-byte address space as an internal I/O area, whose addressess range from FFC0H to FFEFH. This I/O area can be accessed by the CPU using a short opcode in the "direct addressing mode".

Figure 3.1 is a memory map indicating the areas accessible by the CPU in the respective addressing mode.

Figure 3.2. Memory Map

## 4. Electrical Characteristics

TMP90C141N/TMP90C141F

## 4.1 Absolute Maximum Ratings

| Symbol              | Parameter                     | Rating                       | Unit  |  |

|---------------------|-------------------------------|------------------------------|-------|--|

| V <sub>CC</sub>     | Supply voltage                | -0.5 ~ + 7                   | V     |  |

| V <sub>IN</sub>     | Input voltage                 | -0.5 ~ V <sub>CC</sub> + 0.5 | V     |  |

| D                   | Power dissipation (Ta = 70°C) | F 500                        | mW    |  |

| $P_{D}$             | Tower dissipation (1a = 70 G) | N 600                        | IIIVV |  |

| T <sub>SOLDER</sub> | Soldering temperature (10s)   | 260                          | °C    |  |

| T <sub>STG</sub>    | Storage temperature           | -65 ~ 150                    | °C    |  |

| T <sub>OPR</sub>    | Operating temperature         | -20 ~ 70                     | °C    |  |

#### 4.2 DC Characteristics

TA = -20 ~ 70°C Vcc = 5V  $\pm$  10% Typical Values are for TA = 25°C and Vcc = 5V.

| Symbol                                                  | Parameter                                      | Min                                              | Max                      | Unit           | Test Conditions                                                                 |

|---------------------------------------------------------|------------------------------------------------|--------------------------------------------------|--------------------------|----------------|---------------------------------------------------------------------------------|

| V <sub>IL</sub>                                         | Input Low Voltage (D0 ~ D7)                    | -0.3                                             | 0.2V <sub>CC</sub> - 0.1 | V              | -                                                                               |

| V <sub>IL1</sub>                                        | P3, P5, P6, P7, P8                             | -0.3                                             | 0.3V <sub>CC</sub>       | V              | -                                                                               |

| V <sub>IL2</sub>                                        | RESET, INTO, NMI                               | -0.3                                             | 0.25V <sub>CC</sub>      | V              | -                                                                               |

| $V_{IL4}$                                               | X1                                             | -0.3                                             | 0.2V <sub>CC</sub>       | V              | -                                                                               |

| V <sub>IH</sub>                                         | Input Low Voltage (D0 ~ D7)                    | 0.2V <sub>CC</sub> + 1.1                         | V <sub>CC</sub> + 0.3    | V              | -                                                                               |

| V <sub>IH1</sub>                                        | P3, P5, P6, P7, P8                             | 0.7V <sub>CC</sub>                               | V <sub>CC</sub> + 0.3    | V              | -                                                                               |

| V <sub>IH2</sub>                                        | RESET, INTO, NMI                               | 0.75V <sub>CC</sub>                              | V <sub>CC</sub> + 0.3    | V              | -                                                                               |

| V <sub>IH4</sub>                                        | X1                                             | 0.8V <sub>CC</sub>                               | V <sub>CC</sub> + 0.3    | V              | -                                                                               |

| V <sub>OL</sub>                                         | Output Low Voltage                             | -                                                | 0.45                     | V              | I <sub>OL</sub> = 1.6mA                                                         |

| V <sub>OH</sub><br>V <sub>OH1</sub><br>V <sub>OH2</sub> | Output High Voltage                            | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub> | -                        | V<br>V<br>V    | I <sub>OH</sub> = -400μA<br>I <sub>OH</sub> = -100μA<br>I <sub>OH</sub> = -20μA |

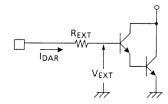

| I <sub>DAR</sub>                                        | Darlington Drive Current (8 I/O pins)          | -1.0                                             | -3.5                     | mA             | $V_{EXT} = 1.5V$<br>$R_{EXT} = 1.1k\Omega$                                      |

| I <sub>LI</sub>                                         | Input Leakage Current                          | 0.02 (Typ)                                       | ±5                       | μA             | 0.0 ≤ Vin ≤ V <sub>CC</sub>                                                     |

| $I_{L0}$                                                | Output Leakage Current                         | 0.05 (Typ)                                       | ±10                      | μA             | 0.2 ≤ Vin ≤ V <sub>CC</sub> - 0.2                                               |

| I <sub>CC</sub>                                         | Operating Current (RUN) Idle 1 Idle 2          | 20 (Typ)<br>1.5 (Typ)<br>9 (Typ)                 | 30<br>5<br>15            | mA<br>mA<br>mA | tosc = 12.5MHz                                                                  |

|                                                         | STOP (TA = -20 ~ 70°C)<br>STOP (TA = 0 ~ 50°C) | 0.2 (Typ)                                        | 50<br>10                 | μΑ<br>μΑ       | 0.2 ≤ Vin ≤ V <sub>CC</sub> - 0.2                                               |

| R <sub>RST</sub>                                        | RESET Pull Up Register                         | 50                                               | 150                      | ΚΩ             | -                                                                               |

| CIO                                                     | Pin Capacitance                                | _                                                | 10                       | pF             | testfreq = 1MHz                                                                 |

| V <sub>TH</sub>                                         | Schmitt width RESET, NMI, INTO                 | 0.4                                              | 1.0 (Typ)                | V              | _                                                                               |

Note:  $\ensuremath{I_{DAR}}$  is guaranteed for a total of up to 8 optional ports.

8/12 TOSHIBA CORPORATION

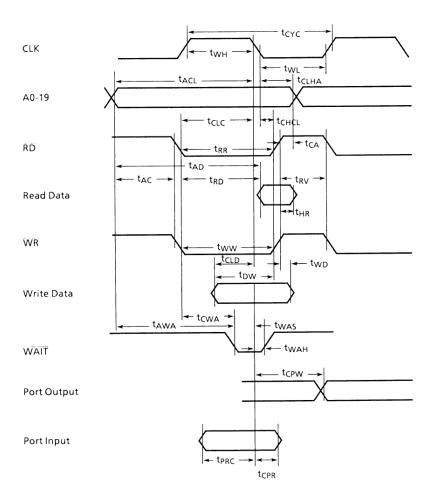

#### 4.3 AC Characteristics

TA = -20 ~ 70°CV  $_{CC}$  = 5V  $\pm$  10% CL = 50pF

| 0                 | Downwardow.                    | Vai       | riable     | 10MH | z Clock | 12.5M | llm:4 |      |

|-------------------|--------------------------------|-----------|------------|------|---------|-------|-------|------|

| Symbol            | Parameter                      | Min       | Max        | Min  | Max     | Min   | Max   | Unit |

| t <sub>OSC</sub>  | OSC. Period = x                | 80        | 1000       | 100  | _       | 80    | _     | ns   |

| t <sub>CYC</sub>  | CLK Period                     | 4x        | 4x         | 400  | -       | 320   | -     | ns   |

| t <sub>WL</sub>   | CLK Low width                  | 2x - 40   | -          | 160  | -       | 120   | -     | ns   |

| t <sub>WH</sub>   | CLK High width                 | 2x - 40   | -          | 160  | _       | 120   | _     | ns   |

| $t_{AC}$          | Address Setup to RD, WR        | x - 45    | -          | 55   | -       | 35    | _     | ns   |

| t <sub>RR</sub>   | RD Low width                   | 2.5x - 40 | -          | 210  | -       | 160   | -     | ns   |

| t <sub>CA</sub>   | Address Hold Time After RD, WR | 0.5x - 30 | -          | 20   | -       | 10    | -     | ns   |

| t <sub>AD</sub>   | Address to Valid Data In       | -         | 3.5x - 95  | -    | 255     | -     | 185   | ns   |

| t <sub>RD</sub>   | RD to Valid Data In            | -         | 2.5x - 80  | -    | 170     | -     | 120   | ns   |

| t <sub>HR</sub>   | Input Data Hold After RD       | 0         | -          | 0    | -       | 0     | _     | ns   |

| t <sub>ww</sub>   | WR Low width                   | 2.5x - 40 | -          | 210  | -       | 160   | -     | ns   |

| t <sub>DW</sub>   | Data Setup to WR               | 2x - 50   | -          | 150  | _       | 110   | _     | ns   |

| t <sub>WD</sub>   | Data Hold After WR             | 30        | 90         | 30   | 90      | 30    | 90    | ns   |

| t <sub>CWA</sub>  | RD, WR to Valid WAIT           | _         | 1.5x - 100 | -    | 50      | -     | 20    | ns   |

| t <sub>AWA</sub>  | Address to Valid WAIT          | _         | 2.5x - 130 | -    | 120     | -     | 70    | ns   |

| t <sub>WAS</sub>  | WAIT Setup to CLK              | 70        | _          | 70   | -       | 70    | _     | ns   |

| t <sub>WAH</sub>  | WAIT Hold After CLK            | 0         | -          | 0    | _       | 0     | _     | ns   |

| t <sub>RV</sub>   | RD/WR Recovery Time            | 1.5x - 35 | -          | 115  | -       | 85    | _     | ns   |

| t <sub>CPW</sub>  | CLK to Port Data Output        | _         | x + 200    | _    | 300     | _     | 280   | ns   |

| t <sub>PRC</sub>  | Port Data Setup to CLK         | 200       | -          | 200  | -       | 200   | _     | ns   |

| t <sub>CPR</sub>  | Port Data Hold After CLK       | 100       | _          | 100  | _       | 100   | _     | ns   |

| t <sub>CHCL</sub> | RD/WR Hold After CLK           | x - 60    | _          | 40   | _       | 20    | _     | ns   |

| t <sub>CLC</sub>  | RD/WR Setup to CLK             | 1.5x - 50 | _          | 100  | _       | 70    | _     | ns   |

| t <sub>CLHA</sub> | Address Hold After CLK         | 1.5x - 80 | -          | 70   | _       | 40    | -     | ns   |

| t <sub>ACL</sub>  | Address Setup to CLK           | 2.5x - 80 | _          | 170  | _       | 120   | _     | ns   |

| t <sub>CLD</sub>  | Data Setup to CLK              | x - 50    | _          | 50   | _       | 30    | _     | ns   |

• AC output level High 2.2V/Low 0.8V

• AC input level High 2.4V/Low 0.45V (D0 - D7)

High  $0.8V_{CC}/Low~0.2V_{CC}$  (excluding D0 – D7)

TOSHIBA CORPORATION 9/12

## 4.4 A/D Conversion Characteristics

| TA: | = -20 | ~ 7 | 0°C | $V_{CC}$ | = 5\ | l± | 10% |

|-----|-------|-----|-----|----------|------|----|-----|

|-----|-------|-----|-----|----------|------|----|-----|

| Symbol           | Parameter                                                             | Min                   | Тур             | Max             | Unit |

|------------------|-----------------------------------------------------------------------|-----------------------|-----------------|-----------------|------|

| V <sub>REF</sub> | Analog reference voltage                                              | V <sub>CC</sub> - 1.5 | V <sub>CC</sub> | V <sub>CC</sub> |      |

| A <sub>GND</sub> | Analog reference voltage                                              | V <sub>SS</sub>       | $V_{SS}$        | $V_{SS}$        | V    |

| V <sub>AIN</sub> | Allowable analog input voltage                                        | V <sub>SS</sub>       | _               | V <sub>CC</sub> |      |

| I <sub>REF</sub> | Supply current for analog reference voltage                           | _                     | 0.5             | 1.0             | mA   |

| Error            | Total error<br>(TA = 25°C, V <sub>CC</sub> = V <sub>REF</sub> = 5.0V) | -                     | -               | 1.0             | LSB  |

|                  | Total error                                                           | -                     | -               | 2.5             |      |

#### 4.5 Zero-Cross Characteristics

TA = -20 ~ 70°C  $V_{CC}$  = 5V  $\pm\,10\%$

| Symbol          | Parameter                            | Condition                   | Min  | Max | Unit      |

|-----------------|--------------------------------------|-----------------------------|------|-----|-----------|

| V <sub>ZX</sub> | Zero-cross detection input           | AC coupling $C = 0.1 \mu F$ | 1    | 1.8 | VAC p - p |

| A <sub>ZX</sub> | Zero-cross accuracy                  | 50/60Hz sine wave           | -    | 135 | mV        |

| F <sub>ZX</sub> | Zero-cross detection input frequency | -                           | 0.04 | 1   | kHz       |

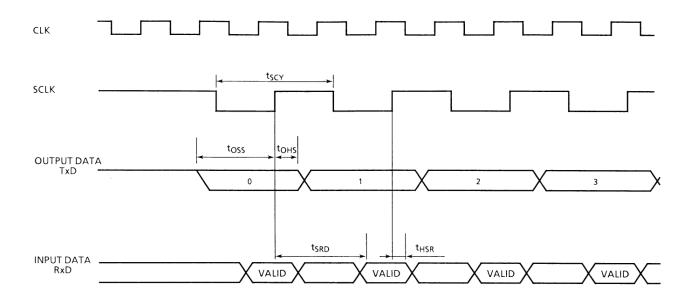

## 4.6 Serial Channel Timing-I/O Interface Mode

TA = -20 ~ 70°C  $V_{CC}$  = 5V  $\pm$  10% CL = 50pF

| Symbol           | Variable Parameter                      |          | 10MHz    | z Clock | 12.5MH | Unit |     |      |

|------------------|-----------------------------------------|----------|----------|---------|--------|------|-----|------|

| Syllibul         | yiiibui rarailletei                     | Min      | Max      | Min     | Max    | Min  | Max | UIII |

| t <sub>SCY</sub> | Serial Port Clock Cycle Time            | 8x       | -        | 800     | -      | 640  | -   | ns   |

| toss             | Output Data Setup SCLK Rising Edge      | 6x - 150 | -        | 450     | _      | 330  | -   | ns   |

| t <sub>OHS</sub> | Output Data Hold After SCLK Rising Edge | 2x - 120 | -        | 80      | -      | 40   | -   | ns   |

| t <sub>HSR</sub> | Input Data Hold After SCLK Rising Edge  | 0        | -        | 0       | -      | 0    | -   | ns   |

| t <sub>SRD</sub> | SCLK Rising Edge to Input DATA Valid    | -        | 6x - 150 | -       | 450    | -    | 330 | ns   |

#### 4.7 16-bit Event Counter

TA = -20 ~ 70°C  $V_{CC}$  = 5V  $\pm\,10\%$

| Symbol            | vmbol Parameter            |          | Variable |     | 10MHz Clock |     | 12.5MHz Clock |      |

|-------------------|----------------------------|----------|----------|-----|-------------|-----|---------------|------|

| Symbol            | i arameter                 | Min      | Max      | Min | Max         | Min | Max           | Unit |

| t <sub>VCK</sub>  | TI4 clock cycle            | 8x + 100 | -        | 900 | -           | 740 | -             | ns   |

| t <sub>VCKL</sub> | TI4 Low clock pulse width  | 4x + 40  | -        | 440 | -           | 360 | -             | ns   |

| t <sub>VCKH</sub> | TI4 High clock pulse width | 4x + 40  | -        | 440 | -           | 360 | -             | ns   |

10/12 TOSHIBA CORPORATION

## 4.8 Interrupt Operation

TA = -20 ~ 70°C  $V_{CC}$  = 5V  $\pm$  10%

| Symbol             | Parameter                         | Variable |     | 10MHz Clock |     | 12.5MHz Clock |     | Unit |

|--------------------|-----------------------------------|----------|-----|-------------|-----|---------------|-----|------|

| Symbol             | raiailletei                       | Min      | Max | Min         | Max | Min           | Max | Unit |

| t <sub>INTAL</sub> | NMI, INTO Low level pulse width   | 4x       | -   | 400         | -   | 320           | -   | ns   |

| t <sub>INTAH</sub> | NMI, INTO High level pulse width  | 4x       | -   | 400         | ı   | 320           | -   | ns   |

| t <sub>INTBL</sub> | INT1, INT2 Low level pulse width  | 8x + 100 | I   | 900         | ı   | 740           | -   | ns   |

| t <sub>INТВН</sub> | INT1, INT2 High level pulse width | 8x + 100 | -   | 900         | -   | 740           | -   | ns   |

## (Reference) Definition of IDAR

## 4.9 I/O Interface Mode Timing Chart

TOSHIBA CORPORATION 11/12

## 4.10 Timing Chart

# 5. Differences Between TMP90C841A and TMP90C141

Specifications of TMP90C841A and TMP90C141 are the same except below.

| Name                                      | TMP90C841A                                                | TMP90C141                                                  |

|-------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|

| RAM                                       | 256 bytes of internal RAM are provided. (OFECOH ~ OFFBFH) | 1024 bytes of internal RAM are provided. (0FBC0H ~ 0FFBFH) |

| A0 ~ A15                                  | High-Impedance state during reset                         | Driving state during reset.                                |

| P0 (0FFC1H)<br>P1 (0FFC1H)<br>P2 (0FFC4H) | Provided (same chip as TMP90C840A)                        | R/W function is not provided.                              |

| P01CR (0FFC2H)                            | Provided                                                  | EXT, P1C, P0C is not provided.                             |

| P2CR (0FFC5H)                             | Provided                                                  | P2XC register is not provided                              |

<sup>\*</sup> Note: Connect  $\overline{\mathsf{EA}}$  pin with GND pin.