## **BUS COMPATIBLE 4-DIGIT CMOS DECODER/DRIVER**

#### **FEATURES**

- 4-Digit Non-Multiplexed 7-Segment LCD Outputs With Backplane Driver

- Input and Digit Select Data Latches

- RC Oscillator On-Chip Generates Backplane Drive Signal

- Eliminates DC Bias Which Degrades LCD Life

- Backplane Input/Output Pin Permits

Synchronization of Cascaded Slave Device to a Master Backplane Signal

- Binary and BCD Inputs Decoded to Code B (0 to 9, —, E, H, L, P, Blank)

- Pin Compatible and Functionally Equivalent to ICM7211AM

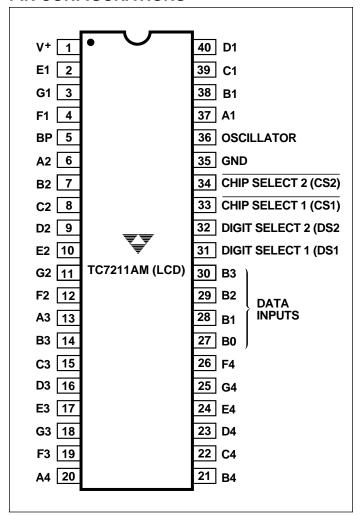

#### **PIN CONFIGURATIONS**

#### **GENERAL DESCRIPTION**

The TC7211AM (LCD Decoder/driver) is a CMOS direct drive, 4-digit, 7-segment display decoder and driver.

The TC7211AM drives conventional LCDs. An RC oscillator, divider chain, backplane driver, and 28-segment outputs are provided on a single CMOS chip. The segment drivers supply square waves of the same frequency as the backplane, but in-phase for an OFF segment and out-of-phase for an ON segment. The net DC voltage applied between driver segment and backplane is near zero maximizing display lifetime.

The four bit binary input is decoded into the seven segment alphanumeric code known as "Code B". The "Code B" output format results in a 0 to 9,—, E, H, L, P or blank display. True BCD or binary inputs will be correctly decoded to the seven segment display format.

#### ORDERING INFORMATION

|           | Driver |             | Input  | Output       |

|-----------|--------|-------------|--------|--------------|

| Part No.  | Type   | Package     | Code   | Config.      |

| TC7211AMI | PL LCD | 40-Pin      | Code B | Data and     |

|           |        | Plastic DIP |        | Digit Select |

|           |        |             |        | Latches      |

# BUS COMPATIBLE, 4-DIGIT CMOS DECODER/DRIVER

### **TC7211AM**

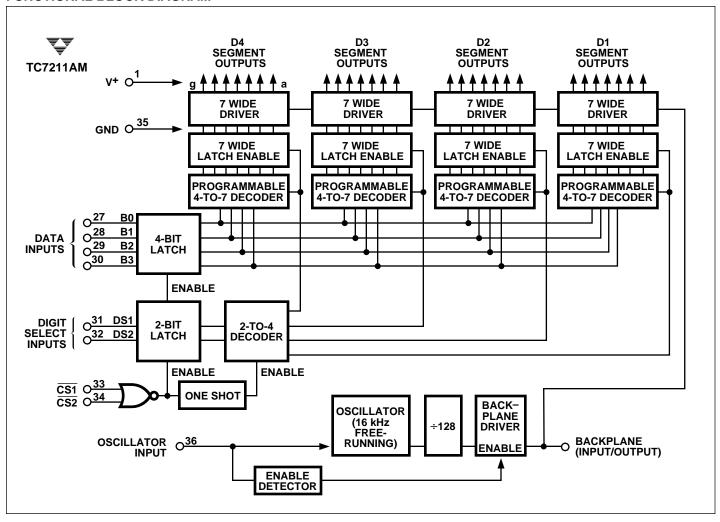

#### **FUNCTIONAL BLOCK DIAGRAM**

## BUS COMPATIBLE, 4-DIGIT CMOS DECODER/DRIVER

## **TC7211AM**

nsec

nsec

μsec

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage                               | +6.5V                     |

|----------------------------------------------|---------------------------|

| Input Voltage, Any Terminal                  |                           |

| (Note 2)                                     | $V^{+}$ +0.3V, GND - 0.3V |

| Power Dissipation $T_A \le 70^{\circ}C$ (Not | e 1)1.23W                 |

| Operating Temperature Range                  | 20°C to +85°C             |

| Storage Temperature Range                    | 65°C to +150°C            |

| Lead Temperature (Soldering, 10 s            | sec)+300°C                |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above

those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**NOTES:** 1. This limit refers to that of the package and will not be realized during normal operation.

2. Due to the SCR structure inherent in the CMOS process, connecting any terminal to voltages greater than V+ or less than GND may cause destructive latch-up. For this reason, it is recommended that inputs from external sources not operating on the same power supply not be applied to the device before its supply is established, and, in multiple supply systems, the supply to the TC7211AM be turned on first.

## TYPICAL CHARACTERISTICS: All parameters measured with V+ = 5V, T<sub>A</sub> = 25°C

| Symbol            | Parameter                      | Parameter Test Conditions            |       | Тур   | Max | Unit |

|-------------------|--------------------------------|--------------------------------------|-------|-------|-----|------|

| V <sub>SUP</sub>  | Operating Voltage Range        |                                      | 3     | 5     | 6   | V    |

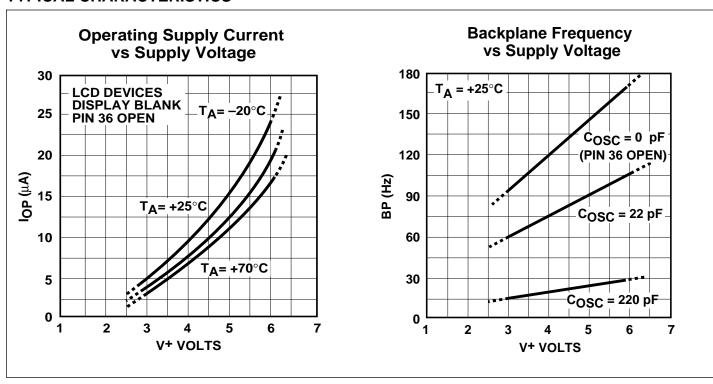

| I <sub>OP</sub>   | Operating Current              | Display Blank                        | _     | 10    | 50  | μΑ   |

| I <sub>OSCI</sub> | Oscillator Input Current       | Pin 36                               | _     | ±2    | ±10 | μΑ   |

| t <sub>RFS</sub>  | Segment Rise/Fall Time         | $C_L = 200 \text{ pF}$               | _     | 0.5   | _   | μsec |

| t <sub>RFB</sub>  | Backplane Rise/Fall Time       | C <sub>L</sub> = 5000 pF             | _     | 1.5   | _   | μsec |

| fosc              | Oscillator Frequency           | Pin 36 Floating                      | _     | 16    | _   | kHz  |

| f <sub>BP</sub>   | Backplane Frequency            | Pin 36 Floating                      | _     | 125   | _   | Hz   |

| Input Chara       | cteristics                     |                                      |       |       |     |      |

| V <sub>IH</sub>   | Logic "1" High Input Voltage   |                                      | 3     | _     | _   | V    |

| $V_{IL}$          | Logic "0" Low Input Voltage    | _                                    | _     | 1     | V   |      |

| I <sub>ILK</sub>  | Input Leakage Current          |                                      | ±0.01 | ±1    | μΑ  |      |

| C <sub>IN</sub>   | Input Capacitance              | Pins 27-34                           | _     | 5     | _   | pF   |

| I <sub>BPLK</sub> | BP Input Current<br>Leakage    | Measured at Pin 5 With Pin 36 at GND | _     | ±0.01 | ±1  | μΑ   |

| C <sub>BPI</sub>  | BP Input Capacitance           | _                                    | 200   | _     | pF  |      |

| AC Characte       | eristics                       |                                      |       |       |     |      |

| Symbol            | Parameter                      | Test Conditions                      | Min   | Тур   | Max | Unit |

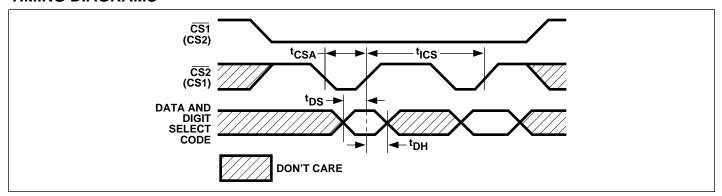

| tcsa              | Chip Select Active Pulse Width | (Note 1)                             | 200   |       |     | nsec |

NOTE: 1. Other chip select (CS) is either held at logic zero or both CS1 and CS2 driven together.

**Data Setup Time**

Data Hold Time

Inter-Chip Select Time

$t_{DS}$

$t_{DH}$

$t_{\text{ICS}}$

100

10

2

0

# BUS COMPATIBLE, 4-DIGIT CMOS DECODER/DRIVER

## **TC7211AM**

#### **TIMING DIAGRAMS**

Figure 1: BUS Interface Timing Diagram

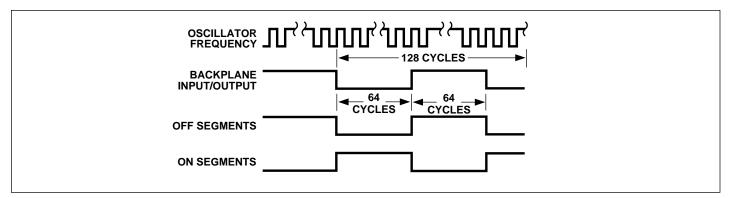

Figure 2: LCD Display Waveforms

#### **INPUT DEFINITIONS**

In this table, V<sup>+</sup> and GND are considered to be normal operating input logic levels. For lowest power consumption, input signals should swing over the full supply.

| Input | Pin No. | Condition                                     | Function                                                                                                                                  |                                        |  |  |

|-------|---------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

| B0    | 27      | V <sup>+</sup> = Logic "1"<br>GND = Logic "0" | Ones (Least Significant)                                                                                                                  | )                                      |  |  |

| B1    | 28      | V <sup>+</sup> = Logic "1"<br>GND = Logic "0" | Twos                                                                                                                                      | Data Input Bits                        |  |  |

| B2    | 29      | V <sup>+</sup> = Logic "1"<br>GND = Logic "0" | Fours                                                                                                                                     |                                        |  |  |

| В3    | 30      | V <sup>+</sup> = Logic "1"<br>GND = Logic "0" | Eights (Most Significant)                                                                                                                 |                                        |  |  |

| OSC   | 36      | Floating or with external capacitor GND       | Oscillator input. Disables BP output devices, allowing segments to be synchronized to an external signal input at the BP terminal (pin 5) |                                        |  |  |

| DS1   | 31      | V <sup>+</sup> = Logical One                  | DS2, DS1 = 00 Selects D4                                                                                                                  |                                        |  |  |

| DS2   | 32      | GND = Logical Zero                            | DS2, DS1 = 01 Selects D3 DS2, DS1 = 10 Selects D2 DS2, DS1 = 11 Selects D1                                                                | Digit Select Inputs                    |  |  |

| CS1   | 33      | V <sup>+</sup> = Inactive                     |                                                                                                                                           | LOW, the data and digit select input   |  |  |

| CS2   | 34      | GND = Active                                  | <ul> <li>latches are open or enabled.</li> <li>On the rising of CS1 or CS2,</li> <li>the output drive latches.</li> </ul>                 | data is latched, decoded and stored in |  |  |

#### **OUTPUT DEFINITIONS**

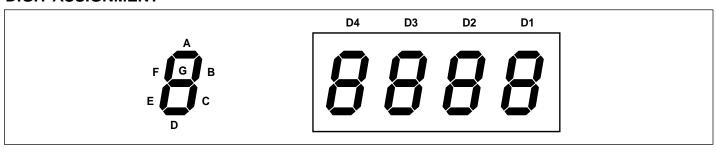

Output pins are defined by the alphabetical segment assignment and numerical digital assignment.

| Output | Pin No. |   | Function      |             |       | Output | Pin No. |   | Function      |         |          |

|--------|---------|---|---------------|-------------|-------|--------|---------|---|---------------|---------|----------|

| A1     | 37      | Α | Segment Drive | Digit 1     | (LSD) | A3     | 13      | Α | Segment Drive | Digit 3 |          |

| B1     | 38      | В | I             | Ĭ           | `     | B3     | 14      | В |               | Ī       |          |

| C1     | 39      | С |               |             |       | C3     | 15      | С |               |         |          |

| D1     | 40      | D |               |             |       | D3     | 16      | D |               |         |          |

| E1     | 2       | Ε |               |             |       | E3     | 17      | Ε |               |         |          |

| F1     | 4       | F |               |             |       | F3     | 19      | F |               |         |          |

| G1     | 3       | G | <b>*</b>      | ▼           | ▼     | G3     | 18      | G | *             | ▼       |          |

| A2     | 6       | Α | Segment Drive | Digit 2     |       | A4     | 20      | Α | Segment Drive | Digit 4 | (MSD)    |

| B2     | 7       | В | ı             | ĺ           |       | B4     | 21      | В | I             | Ī       | Ì        |

| C2     | 8       | С |               |             |       | C4     | 22      | С |               |         |          |

| D2     | 9       | D |               |             |       | D4     | 23      | D |               |         |          |

| E2     | 10      | Ε |               |             |       | E4     | 24      | Ε |               |         |          |

| F2     | 12      | F |               |             |       | F4     | 26      | F |               |         |          |

| G2     | 11      | G | ₩             | <b>\psi</b> |       | G4     | 25      | G | <b>★</b>      | \       | <b>★</b> |

#### **DIGIT ASSIGNMENT**

### **TC7211AM**

#### TYPICAL CHARACTERISTICS

#### **BASIC OPERATION**

The TC7211AM drives 4-digit, 7-segment LCDs. This device contains 28 individual segment drivers, a backplane driver, a self-contained oscillator, and a divider chain to generate the backplane signal.

The 28 CMOS segment drivers and backplane driver contain ratioed N- and P-channel transistors for identical ON resistance. The equal resistances eliminate the DC output driver component resulting from unequal rise and fall times. This ensures maximum LCD life.

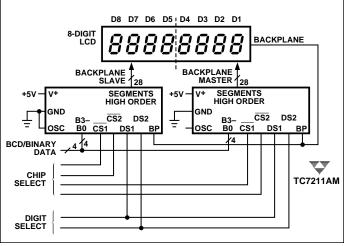

The backplane output driver can be disabled by grounding the OSCILLATOR input (pin 36). The 28 output segment drivers can therefore be synchronized directly to an input signal at the backplane (BP) terminal (pin 5). Several slave devices may be cascaded to the backplane output of a master device. The backplane signal may also be derived from an external source. These features permit interfacing to single backplane LCDs with characters in multiples of four.

Each slave's backplane input represents a 200pF capacitive load to the master backplane driver (comparable to one additional segment). The number of slave devices drivable by a master device is therefore set by the larger display backplane capacitive load. The master backplane output will drive the display backplane of 16 one-half-inch characters with rise and fall times under 5  $\mu sec$ . This represents a system with three slave devices and a fourth master device driving the backplane.

If more than four devices are slaved together, the backplane signal should be derived externally and all TC7211AM devices slaved to it. The external drive signal must drive a high capacitive load with 1 $\mu$ sec to 2  $\mu$ sec rise and fall times. The backplane frequency is normally 125 Hz. At lower display ambient temperatures, the frequency may be reduced to compensate for display response time.

The on-chip RC oscillator free-runs at approximately 16 kHz. A divide-by 128 circuit provides the 125 Hz backplane frequency. The oscillator frequency may be reduced by connecting an external capacitor between the oscillator terminal and V<sup>+</sup>. (See typical operating characteristics curves.)

The free-running oscillator may be overridden (if desired) by an external clock. The backplane driver, however, must not be disabled during the external clock's negative or IOW portion, as this will result in a DC drive component being applied to the LCD, limiting the LCD's life. To prevent backplane driver disabling, the oscillator input should be driven from the positive supply to no less than one-fifth the supply voltage above ground. A backplane disable signal will not be sensed if the driving signal remains above ground by one-fifth the supply voltage. An alternate method for externally driving the oscillator permits the oscillator input to swing the full supply voltage range. The oscillator input signal duty cycle is skewed so the LOW

portion duration is less than 1  $\mu$ sec. The backplane disable sensing circuit will not respond to such a short signal.

Figure 3. TC7211AM Driving an 8-Digit LCD Display in Master/Slave Configuration

## Input Configuration and Output Codes

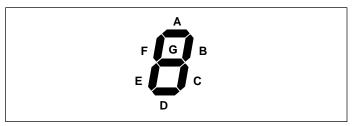

The TC7211AM accepts a 4-bit, true binary (positive level = logic "1") input at pin 27 (LSB) through pin 30 (MSB). The binary input is decoded to the 7-segment output known as Code B. The output display format is 0 to 9, —, E, H, L, P and blank display (see Table 1). Segment assignments are shown in Figure 4. The TC7211AM will correctly decode binary and BCD true codes to a 7-segment output.

The TC7211AM is designed to interface with a data bus and display data under microprocessor control. Four data inputs (pins 27–30) and two digit select input bits (pins 31 and 32) are written into input buffer latches. The rising edge of either chip select causes data to be latched, decoded and stored in the selected digit output data latch. The 2-bit digit code selects the appropriate output digit latch. The 4-bit display data word is decoded to the "Code B" 7-segment output format.

For applications where bus compatibility is not required, refer to the TC7211AM (LCD) 4-digit decoder driver datasheet. This device is designed to accept multiplexed BCD/binary input data for display under the control of four separate digit select control signals.

**Table 1. Binary Codes Versus Character Displayed**

|    | Binary | / Input | Character Displayed |          |

|----|--------|---------|---------------------|----------|

| В3 | B2     | B1      | B0                  | (Code B) |

| 0  | 0      | 0       | 0                   | 0        |

| 0  | 0      | 0       | 1                   | 1        |

| 0  | 0      | 1       | 0                   | 2        |

| 0  | 0      | 1       | 1                   | 3        |

| 0  | 1      | 0       | 0                   | 4        |

| 0  | 1      | 0       | 1                   | 5        |

| 0  | 1      | 1       | 0                   | 6        |

| 0  | 1      | 1       | 1                   | 7        |

| 1  | 0      | 0       | 0                   | 8        |

| 1  | 0      | 0       | 1                   | 9        |

| 1  | 0      | 1       | 0                   | _        |

| 1  | 0      | 1       | 1                   | E        |

| 1  | 1      | 0       | 0                   | Н        |

| 1  | 1      | 0       | 1                   | L        |

| 1  | 1      | 1       | 0                   | Р        |

| 1  | 1      | 1       | 1                   | Blank    |

Figure 4. Segment Assignment

#### **Special Order Decoder Option**

The TC7211AM is mask programmed to give the 16 combinations of 7-segment output codes. For large volume orders (50K pieces minimum), custom decoder options are available. Contact TelCom Semiconductor for details.

## **BUS COMPATIBLE, 4-DIGIT CMOS DECODER/DRIVER**

#### **TC7211AM**

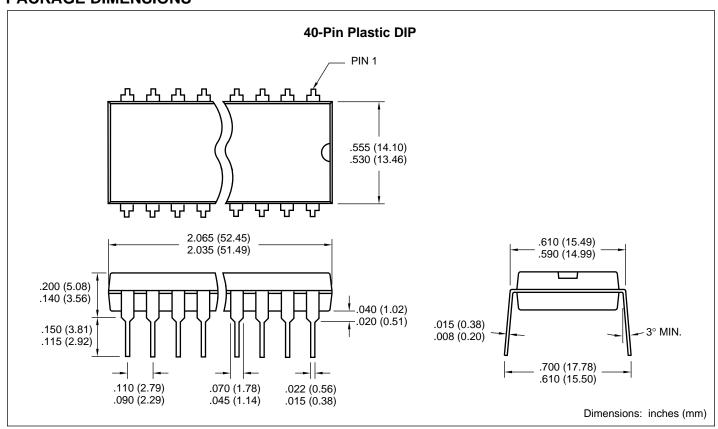

#### **PACKAGE DIMENSIONS**

#### **Sales Offices**

#### **TelCom Semiconductor**

1300 Terra Bella Avenue P.O. Box 7267 Mountain View, CA 94039-7267 TEL: 415-968-9241

FAX: 415-967-1590

E-Mail: liter@c2smtp.telcom-semi.com

#### **TelCom Semiconductor**

Austin Product Center 9101 Burnet Rd. Suite 214 Austin, TX 78758 TEL: 512-873-7100

FAX: 512-873-8236

TelCom Semiconductor H.K. Ltd.

10 Sam Chuk Street, Ground Floor San Po Kong, Kowloon Hong Kong

TEL: 852-2324-0122 FAX: 852-2354-9957