SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

- **Supports Distributed Arbitration for** Futurebus+ Master Selection

- Supports Arbitrated Messages in **Distributed and Central Modes**

- Enables Use of a Common Hardware and Software Interface for Both Distributed and **Central Modes**

- **Requires No Hardware Modifications for** • **Changing Between Distributed and Central** Modes

- Provides a CSR Bus Interface for Easy Integration into the Futurebus+ CSR **Address Space**

- Has Two Bus Request Lines That Each May Be Assigned Any One of 256 Priority Levels

- **Supports Round-Robin Fairness Arbitration** Within Two Separate Priority Levels to Avoid Starvation of Any Single Module

- Supports Distributed-Mode Bus Parking to Improve Performance of Successive Bus Acquisitions By a Single Module During **Idle Bus Conditions**

- **Offers Accurate Arbitration Settling Time** and Glitch Filter Programmability to Allow **Optimal Arbitration Bus Performance**

- Provides a FIFO for Capturing up to Four **Incoming Arbitrated Messages**

- **Provides Hardware Support of Targeted** Interrupts

- **Supports Power-Fail Message Indication** With a Separate Terminal and Interrupt

- **Provides On-Chip Error Time-Out Detection**

- Has a JTAG Test Port

#### description

The TFB2010 arbitration bus controller (ABC) is a member of the Texas Instruments Futurebus+ chip set. This chip set provides an integrated approach to the Futurebus+ interface that reduces new-product design time, allows more functionality per circuit board, improves overall interface reliability, and reduces end-user down time through built-in test capabilities.

The TFB2010 performs the Futurebus+ distributed-arbitration protocol to gain tenure of the bus (distributed mode only), to send and receive arbitrated messages (central or distributed mode), and to update central-mode arbiter priorities (central mode only).

The TFB2010 can be used in conjunction with a central-bus arbiter as an arbitrated-message controller to program the central-bus arbiter, send asynchronous interrupts, or send event messages or interrupts to other modules. In the case of a failure in the central-bus arbiter or if distributed arbitration is desired, it can be used as a distributed-arbitration controller without a change in the host software. Priority changes are sent to the central arbiter as arbitrated messages. This device monitors the bus for arbitration messages, storing these in a FIFO or in the targeted interrupt register for reference by the processor. It also provides the necessary control functions to gain control of the Futurebus+ for a module attempting to perform a bus transaction when operating in the distributed-arbitration mode.

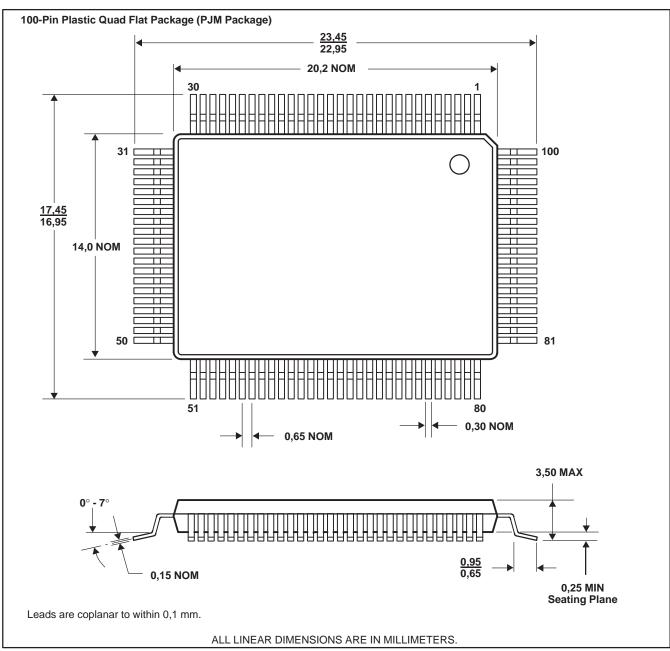

The TFB2010 is offered in a 100-pin plastic quad flat package (PJM) to enhance interface capability. The TFB2010 is characterized for operation over the commercial temperature range of 0°C to 70°C.

NOTE: To maintain consistency with the notation used in the Futurebus+ standard (IEEE Std 896.1–1991), an active low-signal is denoted herein by use of the trailing asterisk (\*) on the signal name.

Copyright © 1993, Texas Instruments Incorporated

SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

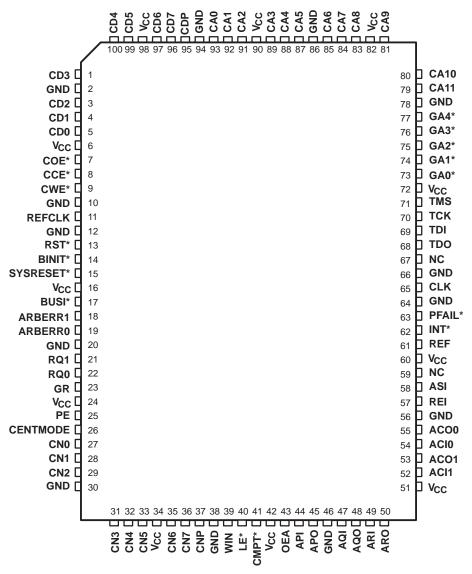

#### terminal assignments

#### PJM . . . PACKAGE (TOP VIEW)

NC - No internal connection

SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

## **Terminal Functions**

#### CSR bus

| TERM     | TERMINAL                                    |     | FROM/TO | DESCRIPTION                 |  |  |

|----------|---------------------------------------------|-----|---------|-----------------------------|--|--|

| NAME     | NO.                                         | I/O | FROM/TO | DESCRIPTION                 |  |  |

| CA<11:0> | 79,80,81,83,<br>84,85,87,88,<br>89,91,92,93 | I   | CSR bus | CSR bus address inputs      |  |  |

| CCE*     | 8                                           | I   | CSR bus | CSR bus chip enable input   |  |  |

| CD<7:0>  | 96,97,99,<br>100,1,3,4,5                    | I/O | CSR bus | CSR bus data                |  |  |

| CDP      | 95                                          | I/O | CSR bus | CSR bus data odd parity     |  |  |

| COE*     | 7                                           | I   | CSR bus | CSR bus output enable input |  |  |

| CWE*     | 9                                           | I   | CSR bus | CSR bus write enable input  |  |  |

## protocol controller interface

| TERMINA     | AL.   | 1/0 | FROM/TO | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-------------|-------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME        | NO.   | 1/0 | FROW/TO | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ARBERR<1:0> | 18,19 | 0   |         | Arbitration error outputs:LLNo errorLHAC0 and AC1 asserted during phase 3HLArbitration comparison error or parity errorHHArbitration time-out error (phase 2 or 4)                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| GR          | 23    | 0   |         | Futurebus + mastership has been granted output (bus tenure may begin). This signal remains in the high-impedance state while in the central-bus arbitration mode.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| PE          | 25    | I/O |         | In distributed mode when this device is the bus master, the TFB2010 asserts PE to indicate that a module with a higher priority has become the master elect. PE is released along with GR when RQ1 and RQ0 are released. In central mode, the TFB2010 puts this output in a high-impedance state to allow the central-arbitration controller to control preemption. PE is monitored by the TFB2010 during a Futurebus+ system reset to determine the system operational mode (central or distributed) following the reset. |  |  |  |  |

| RQ<1:0>     | 21,22 | I   |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

## **Terminal Functions**

## other module interfaces

| TERMIN | TERMINAL I/O |                       | FROM/TO                                                                                                                                                                                                                                                          | DESCRIPTION                                                                                                                   |  |

|--------|--------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

|        |              | <b>↓</b>              |                                                                                                                                                                                                                                                                  |                                                                                                                               |  |

| CLK    | 65           | I                     |                                                                                                                                                                                                                                                                  | Clock input. CLK is used by the CSR bus master(s).                                                                            |  |

| INT*   | 62           | O<br>(open-collector) | Host interrupt output. When an enabled interrupt condition occurs, INT is<br>Interrupts are cleared by writing a zero to the appropriate bit in the interrupt<br>interrupt goes high during the write cycle to the interrupt register even if and<br>is pending. |                                                                                                                               |  |

| PFAIL* | 63           | 0                     |                                                                                                                                                                                                                                                                  | Power-fail message received output                                                                                            |  |

| REFCLK | 11           | I                     | Module                                                                                                                                                                                                                                                           | Clock input. The recommended frequency and duty cycle are 33 MHz, 50%±5%; 25 MHz to 33 MHz and 50% $\pm5\%$ can be tolerated. |  |

## JTAG test port

| TERMIN |     |     | EDOM/TO | DESCRIPTION                 |  |  |  |

|--------|-----|-----|---------|-----------------------------|--|--|--|

| NAME   | NO. | I/O | FROM/TO | DESCRIPTION                 |  |  |  |

| TCK    | 70  | I   | Module  | JTAG test clock input       |  |  |  |

| TDI    | 69  | I   | Module  | JTAG test data input        |  |  |  |

| TDO    | 68  | 0   | Module  | JTAG test data output       |  |  |  |

| TMS    | 71  | I   | Module  | JTAG test mode select input |  |  |  |

## reset port

| TERMIN    | TERMINAL |             | <b>FROM/TO</b> | DESCRIPTION                                                                                                                                                                                           |  |  |

|-----------|----------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO.      | I/O FROM/TO |                |                                                                                                                                                                                                       |  |  |

| BINIT*    | 14       | I           | Module         | Bus interface reset input. BINIT is an open-collector signal indicating that a bus interface reset is required                                                                                        |  |  |

| BUSI*     | 17       | I           |                | Bus has been idle for longer than 1 $\mu$ s, and reset is asserted by this module.                                                                                                                    |  |  |

| REF       | 61       | 0           |                | Futurebus+ reset filtered output                                                                                                                                                                      |  |  |

| REI       | 57       | I           |                | Futurebus+ reset input                                                                                                                                                                                |  |  |

| RST*      | 13       | Ι           | Module         | Module power-up reset input. RST resets all logic; output signals go to their inactive states; 3-state outputs and bidirectionals go to the high-impedance state (for live-insertion considerations). |  |  |

| SYSRESET* | 15       | I           | Module         | System reset input. SYSRESET* signal indicates that a system reset is required.                                                                                                                       |  |  |

SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

#### **Terminal Functions**

| TERMINAL      |                                | 1/0 |                                                                                                              |  |

|---------------|--------------------------------|-----|--------------------------------------------------------------------------------------------------------------|--|

| NAME          | NO.                            | I/O | DESCRIPTION                                                                                                  |  |

| ACI<1:0>      | 52,54                          | I   | Futurebus+ arbitration condition input                                                                       |  |

| ACO<1:0>      | 53,55                          | 0   | Futurebus+ arbitration condition output                                                                      |  |

| API, AQI, ARI | 44,47,49                       | I   | Futurebus+ arbitration handshake input                                                                       |  |

| APO, AQO, ARO | 45,48,50                       | 0   | Futurebus+ arbitration handshake output                                                                      |  |

| ASI           | 58                             | I   | Futurebus+ address handshake input                                                                           |  |

| CENTMODE      | 26                             | 0   | Central-mode operation is in effect output                                                                   |  |

| CMPT*         | 41                             | 0   | Arbitration contest logic compete indication output. Connects to COMPETE and OEB or competition transceiver. |  |

| CN<7:0>, CNP  | 36,35,33,32,31,<br>29,28,27,37 | I/O | Futurebus+ contest number and parity                                                                         |  |

| GA<4:0>*      | 77,76,75,74,73                 | I   | Futurebus+ geographical address input                                                                        |  |

| LE*           | 40                             | 0   | Enable latch on competition transceiver output (1 = competition number latched)                              |  |

| OEA           | 43                             | 0   | Enable TTL drivers on competition transceiver output                                                         |  |

| WIN           | 39                             | I   | Arbitration contest logic win indication input                                                               |  |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)                         | -0.5 V to 7 V |

|----------------------------------------------------------------------------|---------------|

| Output voltage range, V <sub>O</sub><br>Continuous total power dissipation |               |

| Power dissipation                                                          |               |

| Operating free-air temperature range, T <sub>A</sub>                       |               |

| Storage temperature range                                                  |               |

| Case temperature for 10 seconds                                            |               |

NOTE 1: All voltage values are with respect to GND.

| DISSIPATION RATING TABLE |                       |                             |                       |  |  |  |  |

|--------------------------|-----------------------|-----------------------------|-----------------------|--|--|--|--|

| PACKAGE                  | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C |  |  |  |  |

|                          | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          |  |  |  |  |

12 mW/°C

960 mW

1500 mW

#### recommended operating conditions

PJM

|                                                      | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                      | 4.75 | 5   | 5.25 | V    |

| High-level input voltage, VIH                        | 2    |     | VCC  | V    |

| Low-level input voltage, VIL                         | -0.5 |     | 0.8  | V    |

| Operating free-air temperature range, T <sub>A</sub> | 0    |     | 70   | °C   |

SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|       | PARAMETER                              | MACRO   | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|-------|----------------------------------------|---------|-----------------------------------|-----|-----|-----|------|

| VIT   | Input threshold voltage                | IPI04LK | $V_{I} = V_{CC} \text{ or } 0 V,$ |     | 1.3 |     | V    |

| VIT+  | Positive-going input threshold voltage | IPI09LK | $I_I = \pm 1 \mu A$ ,             |     | 1.6 |     | V    |

| VIT – | Negative-going input threshold voltage | IPI09LK | C <sub>L</sub> = 7.4 pF           |     | 1.2 |     | V    |

| VOH   | High-level output voltage              | OPJ43LK | $I_{OH} = -4 \text{ mA}$          | 3.7 |     |     | V    |

| VOL   | Low-level output voltage               | UPJ43LK | I <sub>OL</sub> = 4 mA            |     |     | 0.5 | V    |

| ∨он   | High-level output voltage              | OPJ83LK | $I_{OH} = -8 \text{ mA}$          | 3.7 |     |     | V    |

| VOL   | Low-level output voltage               | OPJ63LK | I <sub>OL</sub> = 8 mA            |     |     | 0.5 | V    |

| Vон   | High-level output voltage              | OPI43LK | $I_{OH} = -4 \text{ mA}$          | 3.7 |     |     | V    |

| VOL   | Low-level output voltage               | UP143LK | I <sub>OL</sub> = 4 mA            |     |     | 0.5 | V    |

| VOL   | Low-level output voltage               | OPI42LK | I <sub>OL</sub> = 4 mA            |     |     | 0.5 | V    |

#### macros

Table 1 lists the internal and external buffer macros used in the TFB2010 design. To use this table, find the pin of interest and note the macro name(s). If there is an entry only in the input macro column, the pin is an input. If there is an entry only in the output macro column, the pin is an output. If there is an entry in both columns, this is a 3-state bidirectional pin. The macro(s) are also listed in the electrical characteristics table.

| PIN NAME    | INPUT MACRO | OUTPUT MACRO |

|-------------|-------------|--------------|

| ACI<1:0>    | IPI04LK     |              |

| ACO<1:0>    |             | OPI43LK      |

| API         | IPI04LK     |              |

| APO         |             | OPI43LK      |

| AQI         | IPI04LK     |              |

| AQO         |             | OPI43LK      |

| ARBERR<1:0> |             | OPI43LK      |

| ARI         | IPI04LK     |              |

| ARO         |             | OPI43LK      |

| ASI         | IPI04LK     |              |

| BINIT*      | IPI09LK     |              |

| BUSI*       | IPI09LK     |              |

| CA<11:0>    | IPI04LK     |              |

| CCE*        | IPI04LK     |              |

| CD<7:0>     | IPI04LK     | OPJ83LK      |

| CDP         | IPI04LK     | OPJ83LK      |

| CENTMODE    |             | OPI43LK      |

| CLK         | IPI04LK     |              |

| CMPT*       |             | OPI43LK      |

| CN<7:0>     | IPI04LK     | OPI43LK      |

| CNP         | IPI04LK     | OPI43LK      |

#### Table 1. TFB2010 (ABC) Pin Names and Macro Numbers

| PIN NAME  | INPUT MACRO | OUTPUT MACRO |

|-----------|-------------|--------------|

| COE*      | IPI04LK     |              |

| CWE*      | IPI04LK     |              |

| GA<4:0>*  | IPI04LK     |              |

| GR        |             | OPI43LK      |

| INT*      |             | OPI42LK      |

| LE*       |             | OPI43LK      |

| OEA       |             | OPI43LK      |

| PE        | IPI04LK     | OPI43LK      |

| PFAIL*    |             | OPI43LK      |

| REF       |             | OPI43LK      |

| REFCLK    | IPI04LK     |              |

| REI       | IPI04LK     |              |

| RQ<1:0>   | IPI04LK     |              |

| RST*      | IPI09LK     |              |

| SYSRESET* | IPI09LK     |              |

| ТСК       | IPI04LK     |              |

| TDI       | IPI04LK     |              |

| TDO       |             | OPI43LK      |

| TMS       | IPI04LK     |              |

| WIN       | IPI04LK     |              |

SLLS125A - OCTOBER 1990 - REVISED NOVEMBER 1993

MECHANICAL DATA

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current and complete.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated