# **THC63DV151**

120MHz 24Bit COLOR DVI Compliant Receiver

### **General Description**

The THC63DV151 is a receiver compliant with DVI Rev.1.0. The THC63DV151 supports display resolution from VGA to SXGA(25-120MHz), up to 24bit/pixel. The built-in PLL requires no external component. Based on THine's original technologies used in the THine's LVDS products, the THC63DV151 realizes low power and high skew tolerance.

#### **Features**

- Compliant with DVI Rev.1.0

- Wide Frequency Range:25MHz-120MHz

- PLL requires No external components

- High Skew Tolerance:1 full input clock cycle

- Programmable Single/Dual Pixel Mode

- Programmable TTL Output Clock Polarity

- Programmable TTL Output Current

- Power down mode

- Low power single 3.3V CMOS design

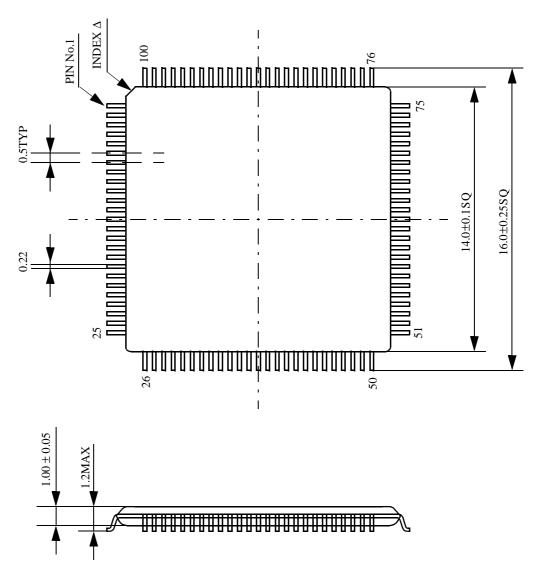

- 100pin TQFP

- Pin Compatible with the Silicon Image SiI151

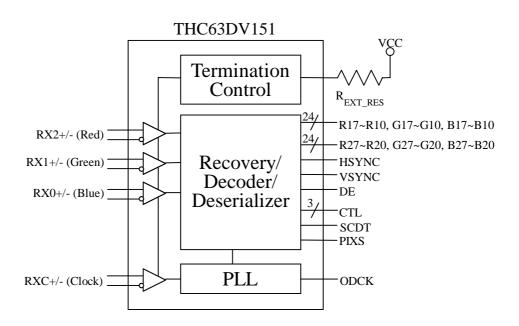

### **Block Diagram**

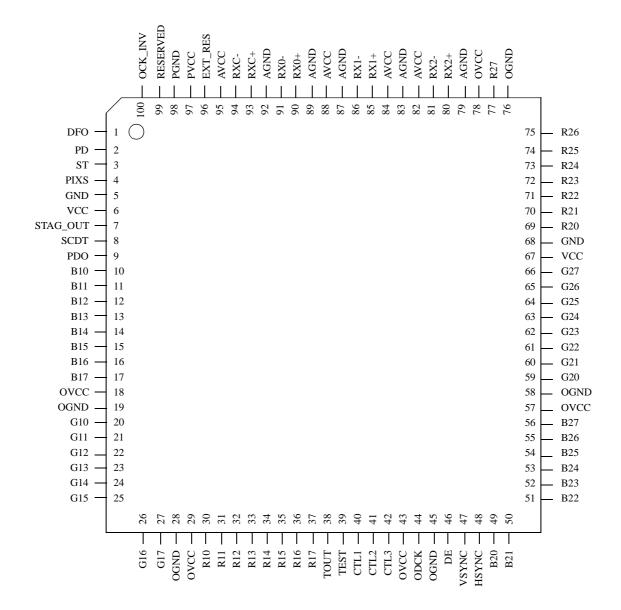

### Pin Out

## Pin Description

| Pin Name   | Pin #                             | Type | Description                                                                                                                                                                    |

|------------|-----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX0+, RX0- | 90, 91                            | In   |                                                                                                                                                                                |

| RX1+, RX1- | 85, 86                            | In   | Differential Data Inputs.                                                                                                                                                      |

| RX2+, RX2- | 80, 81                            | In   |                                                                                                                                                                                |

| RXC+, RXC- | 93, 94                            | In   | Differential Clock Input.                                                                                                                                                      |

| R17 ~ R10  | 37, 36, 35, 34,<br>33, 32, 31, 30 | Out  | First Pixel Data Outputs. These outputs correspond to 24-bit                                                                                                                   |

| G17 ~ G10  | 27, 26, 25, 24,<br>23, 22, 21, 20 | Out  | pixel data for 1-pixel/clock mode and to the first 24-bit pixel data for 2-pixels/clock mode. PD=L or PDO=L make the output drivers into a high impedance mode with weak pull- |

| B17 ~ B10  | 17, 16, 15, 14,<br>13, 12, 11, 10 | Out  | down.                                                                                                                                                                          |

| R27 ~ R20  | 77, 75, 74, 73,<br>72, 71, 70, 69 | Out  | Second Pixel Data Outputs. These outputs correspond to the second 24-bit pixel data for 2-pixels/clock mode and are                                                            |

| G27 ~ G20  | 66, 65, 64, 63,<br>62, 61, 60, 59 | Out  | driven low for 1-pixel/clock mode. PD=L or PDO=L make the output drivers into a high impedance mode with weak                                                                  |

| B27 ~ B20  | 56, 55, 54, 53,<br>52, 51, 50, 49 | Out  | pull-down.                                                                                                                                                                     |

| ODCK       | 44                                | Out  | Clock Output.                                                                                                                                                                  |

| DE         | 46                                | Out  | Data Enable Output.                                                                                                                                                            |

| VSYNC      | 47                                | Out  | Vsync Output.                                                                                                                                                                  |

| HSYNC      | 48                                | Out  | Hsync Output.                                                                                                                                                                  |

| CTL3~CTL1  | 42, 41, 40                        | Out  | Control Signal Outputs.                                                                                                                                                        |

|            |                                   |      | ODCK Polarity.                                                                                                                                                                 |

| OCK_INV    | 100                               | In   | H: Inverted                                                                                                                                                                    |

|            |                                   |      | L: Normal                                                                                                                                                                      |

|            |                                   |      | Pixel Select.                                                                                                                                                                  |

| PIXS       | 4                                 | In   | H: Two pixels per clock                                                                                                                                                        |

|            |                                   |      | L: Single pixel per clock                                                                                                                                                      |

| DFO        | 1                                 | In   | Output Data Format. Must be L for all DVI applications                                                                                                                         |

|            | 7                                 | T    | Staggered Output. This function is only available for 2-pixels per clock mode.                                                                                                 |

| STAG_OUT   | 7                                 | In   | H: Simultaneous output drive                                                                                                                                                   |

|            |                                   |      | L: Staggered output drive                                                                                                                                                      |

|            |                                   |      | Sync Detect.                                                                                                                                                                   |

|            |                                   |      | H: All channels establish synchronization with the data                                                                                                                        |

| SCDT       | 8                                 | Out  | streams. Link is active.                                                                                                                                                       |

|            |                                   |      | L: Any channel does not establish synchronization or RXC+/RXC- pair is not actively toggling. Link is down.                                                                    |

|            |                                   |      | Output Drive Power Down.                                                                                                                                                       |

| PDO        | 9                                 | In   | H: Normal operation                                                                                                                                                            |

|            |                                   |      | L: All output drivers except SCDT and CTL1 into a high impedance mode with weak pull-down                                                                                      |

|            |                                   |      | Output Drive Strength.                                                                                                                                                         |

| ST         | 3                                 | In   | H: High output drive strength                                                                                                                                                  |

|            |                                   |      | L: Low output drive strength                                                                                                                                                   |

| Pin Name | Pin #                 | Type   | Description                                                                                                                                  |

|----------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          |                       |        | Power Down.                                                                                                                                  |

|          |                       |        | H: Normal operation                                                                                                                          |

| PD       | 2                     | In     | L: Power down mode. All output drivers are disabled with weak pull-down, all circuitries are powered down, and all inputs are disabled.      |

| TEST     | 39                    | In     | Test pin. Must be L for normal operation.                                                                                                    |

| TOUT     | 38                    | Out    | Test Output. This pin is in high impedance mode during normal operation and can be tied H for the pin compatibility with the other products. |

| EXT_RES  | 96                    | Analog | Impedance Matching Control. Resistor value should be ten times the termination resistance of each channel.                                   |

| RESERVED | 99                    | In     | Reserved. Must be H for normal operation.                                                                                                    |

| VCC      | 6, 67                 | Power  | Power Supply Pins for digital core.                                                                                                          |

| GND      | 5, 68                 | Ground | Ground Pins for digital core.                                                                                                                |

| OVCC     | 18, 29, 43, 57,<br>78 | Power  | Power Supply Pins for output drive.                                                                                                          |

| OGND     | 19, 28, 45, 58,<br>76 | Ground | Ground Pins for output drive.                                                                                                                |

| AVCC     | 82, 84, 88, 95        | Power  | Power Supply Pins for analog circuitry.                                                                                                      |

| AGND     | 79, 83, 87, 89,<br>92 | Ground | Ground Pins for analog circuitry.                                                                                                            |

| PVCC     | 97                    | Power  | Power Supply Pin for PLL circuitry.                                                                                                          |

| PGND     | 98                    | Ground | Ground Pin for PLL circuitry.                                                                                                                |

# Absolute Maximum Ratings 1

| Supply Voltage (V <sub>CC</sub> )  | -0.3V ~ +4.0V                |

|------------------------------------|------------------------------|

| CMOS/TTL Input Voltage             | $-0.3V \sim (V_{CC} + 0.3V)$ |

| CMOS/TTL Output Voltage            | $-0.3V \sim (V_{CC} + 0.3V)$ |

| TMDS Receiver Input Voltage        | $-0.3V \sim (V_{CC} + 0.3V)$ |

| DC Output Current                  | -30mA ~ 30mA                 |

| Junction Temperature               | +125°C                       |

| Storage Temperature Range          | -55°C ~+125°C                |

| Lead Temperature (Soldering, 4sec) | +260°C                       |

| Maximum Power Dissipation @+25°C   | 1.4W                         |

### **Electrical Characteristics**

## **DC Digital I/O Specifications**

$V_{CC} = 3.0V \sim 3.6V$ , Ta = 0°C ~ +70°C

| Symbol           | Parameter                 | Conditions                          | Min. | Тур. | Max. | Units |

|------------------|---------------------------|-------------------------------------|------|------|------|-------|

| V <sub>IH</sub>  | High Level Input Voltage  |                                     | 2.0  |      |      | V     |

| V <sub>IL</sub>  | Low Level Input Voltage   |                                     |      |      | 0.8  | V     |

| V.               | High Level Output Voltage | I <sub>OH</sub> = -2mA, -4mA (ODCK) | 2.4  |      |      | V     |

| V <sub>OH</sub>  |                           | $I_{OH}$ = -1mA, -2mA (Others)      | 2.4  |      |      |       |

| V.               | Low Lovel Output Voltage  | I <sub>OL</sub> = 2mA, 4mA (ODCK)   |      |      | 0.4  | V     |

| $V_{OL}$         | Low Level Output Voltage  | I <sub>OL</sub> = 1mA, 2mA (Others) |      |      | 0.4  | V     |

| I <sub>INC</sub> | Input Current             | $0V \le V_{IN} \le V_{CC}$          | -10  |      | +10  | μΑ    |

## **DC** Differential Input Specifications

$V_{CC} = 3.0V \sim 3.6V$ ,  $Ta = 0 \,^{\circ}C \sim +70 \,^{\circ}C$

| Symbol             | Parameter                  | Conditions | Min.    | Тур. | Max.   | Units |

|--------------------|----------------------------|------------|---------|------|--------|-------|

| V <sub>IDIFF</sub> | Differential Input Voltage |            | 150     |      | 1200   | mV    |

| V <sub>ICM</sub>   | Input Common Mode Voltage  |            | Vcc-300 |      | Vcc-37 | mV    |

<sup>1. &</sup>quot;Absolute Maximum Ratings" are those valued beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

## **Supply Current**

$V_{CC} = 3.0V \sim 3.6V$ , Ta = 0°C ~ +70°C

| Symbol            | Parameter                                 | Condition                                          | Тур. | Max. | Units |

|-------------------|-------------------------------------------|----------------------------------------------------|------|------|-------|

|                   |                                           | DCLK=60MHz, 2-pixel/clock mode,                    |      |      |       |

| $I_{CCRG}$        | Receiver Supply Current                   | $C_{LOAD}$ =10pF, $R_{EXT\_SWING}$ =400 $\Omega$ , | 140  | 165  | mA    |

|                   | Current                                   | Gray Scale Pattern                                 |      |      |       |

|                   | Receiver Supply<br>Current                | DCLK=60MHz, 2-pixel/clock mode,                    |      |      |       |

| I <sub>CCRW</sub> |                                           | $C_{LOAD}$ =10pF, $R_{EXT\_SWING}$ =400 $\Omega$ , | 205  | 235  | mA    |

|                   |                                           | Worst Case Pattern                                 |      |      |       |

| I <sub>CCRD</sub> | Receiver Discon-<br>nected Supply Current | Disconnected or Transmitter Disabled               | 35   |      | mA    |

| I <sub>CCRS</sub> | Receiver Power Down<br>Supply Current     | PD = L                                             |      | 100  | μΑ    |

#### 256 Gray Scale Pattern

#### Worst Case Pattern

## **AC Specifications**

$V_{CC} = 3.0V \sim 3.6V$ ,  $Ta = 0 ° C \sim +70 ° C$

| Symbol            | Parameter                                                                                                             | Conditions                      | Min. | Тур. | Max. | Units              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|--------------------|

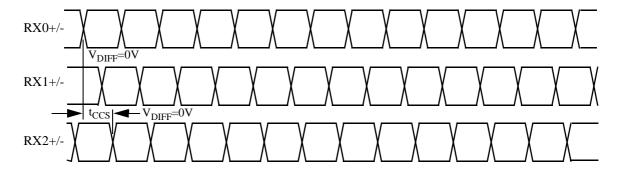

| t <sub>DPS</sub>  | Intra-Pair Skew                                                                                                       |                                 |      |      | 0.4  | T <sub>bit</sub>   |

| t <sub>CCS</sub>  | Inter-Pair Skew                                                                                                       |                                 |      |      | 1.0  | T <sub>pixel</sub> |

| t <sub>IJIT</sub> | Differential Input Clock Jitter Tolerance                                                                             |                                 |      |      | 0.3  | T <sub>bit</sub>   |

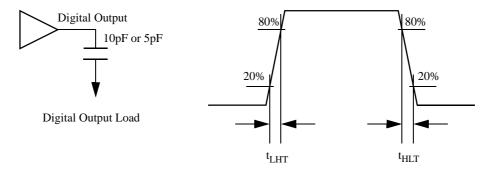

|                   | L-to-H Transition Time                                                                                                | C <sub>LOAD</sub> =10pF<br>ST=H |      |      | 3.1  | ns                 |

| t <sub>CCS</sub>  | Data and Controls                                                                                                     | C <sub>LOAD</sub> =5pF<br>ST=L  |      |      | 5.0  | ns                 |

| LHT               | ODCK                                                                                                                  | C <sub>LOAD</sub> =10pF<br>ST=H |      |      | 2.0  | ns                 |

|                   | ODCK                                                                                                                  | C <sub>LOAD</sub> =5pF<br>ST=L  |      |      | 2.9  | ns                 |

|                   | H-to-L Transition Time                                                                                                | C <sub>LOAD</sub> =10pF<br>ST=H |      |      | 2.8  | ns                 |

| t.u.m             | Data and Controls                                                                                                     | C <sub>LOAD</sub> =5pF<br>ST=L  |      |      | 3.9  | ns                 |

| HLI               | ODCK                                                                                                                  | C <sub>LOAD</sub> =10pF<br>ST=H |      |      | 1.5  | ns                 |

|                   |                                                                                                                       | C <sub>LOAD</sub> =5pF<br>ST=L  |      |      | 2.5  | ns                 |

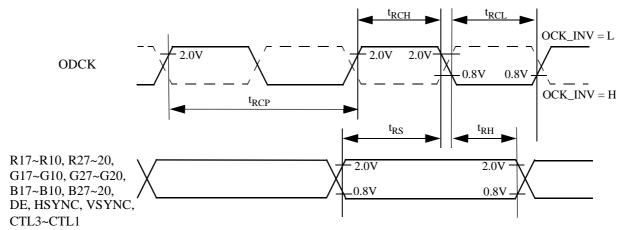

|                   | Data, DE, VSYNC, HSYNC, and CTL[3:1] Setup<br>Time to ODCK falling edge                                               | C <sub>LOAD</sub> =10pF<br>ST=H | 3.2  |      |      | ns                 |

|                   | (OCK_INV=L, 120MHz, 1-pixel/clock, PIXS=L)                                                                            | C <sub>LOAD</sub> =5pF<br>ST=L  | 3.5  |      |      | ns                 |

|                   | Data, DE, VSYNC, HSYNC, and CTL[3:1] Setup<br>Time to ODCK falling edge<br>(OCK_INV=L, 60MHz, 2-pixels/clock, PIXS=H) | C <sub>LOAD</sub> =10pF<br>ST=H | 7.4  |      |      | ns                 |

| tng               |                                                                                                                       | C <sub>LOAD</sub> =5pF<br>ST=L  | 7.7  |      |      | ns                 |

| rrs               | Data, DE, VSYNC, HSYNC, and CTL[3:1] Setup<br>Time to ODCK rising edge<br>(OCK_INV=H, 120MHz, 1-pixel/clock, PIXS=L)  | C <sub>LOAD</sub> =10pF<br>ST=H | 3.2  |      |      | ns                 |

|                   |                                                                                                                       | C <sub>LOAD</sub> =5pF<br>ST=L  | 3.5  |      |      | ns                 |

|                   | Data, DE, VSYNC, HSYNC, and CTL[3:1] Setup<br>Time to ODCK rising edge                                                | C <sub>LOAD</sub> =10pF<br>ST=H | 7.4  |      |      | ns                 |

|                   | (OCK_INV=H, 60MHz, 2-pixels/clock, PIXS=H)                                                                            | C <sub>LOAD</sub> =5pF<br>ST=L  | 7.7  |      |      | ns                 |

# **AC Specifications (continued)**

| Symbol           | Parameter                                                              | Conditions                      | Min. | Тур. | Max.                                               | Units            |

|------------------|------------------------------------------------------------------------|---------------------------------|------|------|----------------------------------------------------|------------------|

|                  | Data, DE, VSYNC, HSYNC, and CTL[3:1] Hold<br>Time to ODCK falling edge | C <sub>LOAD</sub> =10pF<br>ST=H | 3.2  |      |                                                    | ns               |

|                  | (OCK_INV=L, 120MHz, 1-pixel/clock, PIXS=L)                             | C <sub>LOAD</sub> =5pF<br>ST=L  | 2.9  |      |                                                    | ns               |

|                  | Data, DE, VSYNC, HSYNC, and CTL[3:1] Hold<br>Time to ODCK falling edge | C <sub>LOAD</sub> =10pF<br>ST=H | 7.4  |      |                                                    | ns               |

| torr             | (OCK_INV=L, 60MHz, 2-pixels/clock, PIXS=H)                             | C <sub>LOAD</sub> =5pF<br>ST=L  | 7.1  |      |                                                    | ns               |

| t <sub>RH</sub>  | Data, DE, VSYNC, HSYNC, and CTL[3:1] Hold<br>Time to ODCK rising edge  | C <sub>LOAD</sub> =10pF<br>ST=H | 3.2  |      |                                                    | ns               |

|                  | (OCK_INV=H, 120MHz, 1-pixel/clock, PIXS=L)                             | C <sub>LOAD</sub> =5pF<br>ST=L  | 2.9  |      |                                                    | ns               |

|                  | Data, DE, VSYNC, HSYNC, and CTL[3:1] Hold<br>Time to ODCK rising edge  | C <sub>LOAD</sub> =10pF<br>ST=H | 7.4  |      |                                                    | ns               |

|                  | (OCK_INV=H, 60MHz, 2-pixels/clock, PIXS=H)                             | C <sub>LOAD</sub> =5pF<br>ST=L  | 7.1  |      |                                                    | ns               |

| t <sub>RCP</sub> | ODCK Cycle Time (1-pixel/clock)                                        |                                 | 8.33 |      | 40                                                 | ns               |

| $f_{RCP}$        | ODCK Frequency (1-pixel/clock)                                         |                                 | 25   |      | 120                                                | MHz              |

| t <sub>RCP</sub> | ODCK Cycle Time (2-pixels/clock)                                       |                                 | 16.7 |      | 80                                                 | ns               |

| $f_{RCP}$        | ODCK Frequency (2-pixels/clock)                                        |                                 | 12.5 |      | 60                                                 | MHz              |

| tneu             | ODCK High Time                                                         | C <sub>LOAD</sub> =10pF<br>ST=H | 3.0  |      |                                                    | ns               |

| t <sub>RCH</sub> | (120MHz, 1-pixel/clock, PIXS=L)                                        | C <sub>LOAD</sub> =5pF<br>ST=L  | 1.1  |      |                                                    | ns               |

| 4                | ODCK Low Time                                                          | C <sub>LOAD</sub> =10pF<br>ST=H | 3.5  |      |                                                    | ns               |

| t <sub>RCL</sub> | (120MHz, 1-pixel/clock, PIXS=L)                                        | C <sub>LOAD</sub> =5pF<br>ST=L  | 2.1  |      |                                                    | ns               |

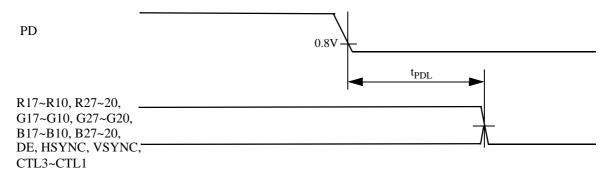

| t <sub>PDL</sub> | Delay from PD Low to High impedance outputs                            |                                 |      |      | 10                                                 | ns               |

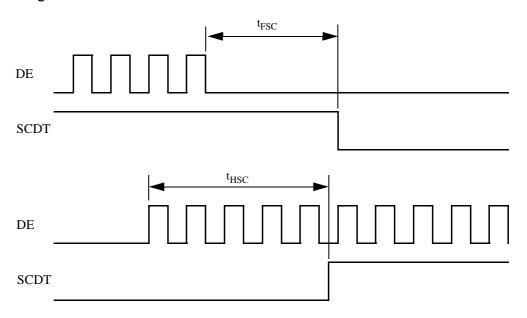

| t                | Link disabled (DE inactive) to SCDT Low                                |                                 |      | 1    |                                                    | μs               |

| t <sub>FSC</sub> | Link disabled (Tx power down) to SCDT Low                              |                                 |      | 1    |                                                    | μs               |

| t <sub>HSC</sub> | Link enabled (DE active) to SCDT High                                  |                                 |      | 25   |                                                    | DE<br>edges      |

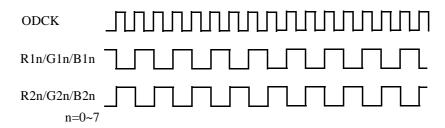

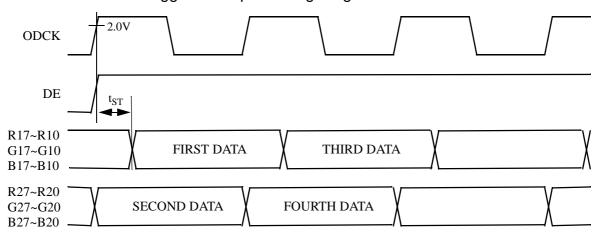

| t <sub>ST</sub>  | ODCK High to even data output (OCK_INV=L)                              |                                 |      | 0.25 |                                                    | t <sub>RCP</sub> |

| 31               | ODCK Low to even data output (OCK_INV=H)                               |                                 |      | 0.25 | 120<br>80<br>60<br>10<br>1<br>1<br>1<br>25<br>0.25 | $t_{RCP}$        |

## **AC Timing Diagrams**

### **Digital Output Transition Times**

### **Output Timing**

### Inter-Pair Skew Timing

Note:

$$V_{DIFF} = (RXn+) - (RXn-), (RXC+) - (RXC-)$$

### **AC Timing Diagrams (continued)**

Output Signals Disabled Timing from PD Active

### SCDT Timing from DE Inactive/Active

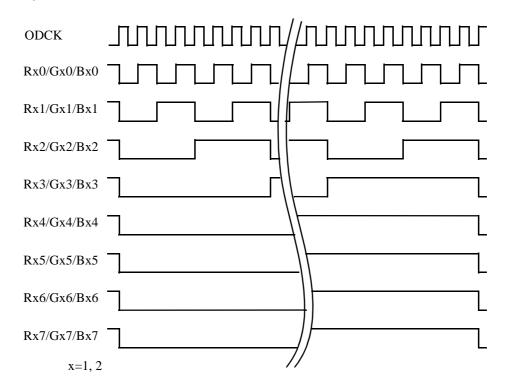

## 2-Pixels/Clock Staggered Output Timing Diagram

# <u>Package</u>

UNITS:mm

#### **Notes to Users:**

- 1. The contents of this data sheet are subject to change without prior notice.

- 2. Circuit diagrams shown in this data sheet are examples of application. Therefore, please pay sufficient attention when designing circuits. Even if there are incorrect descriptions, we are not responsible for any problem due to them. Please note that incorrect descriptions sometimes cannot be corrected immediately if found.

- 3. Our copyright and know-how are included in this data sheet. Duplication of the data sheet and disclosure to other persons are strictly prohibited without our permission.

- 4. We are not responsible for any problems of industrial proprietorship occurring during THC63DV151 use, except for those directly related to THC63DV151's structure, manufacture or functions. THC63DV151 is designed on the premise that it should be used for ordinary electronic devices. Therefore, it shall not be used for applications that require extremely high-reliability (space equipment, nuclear control equipment, medical equipment that affects people's lives, etc.). In addition, when using THC63DV151 for traffic signals, safety devices and control/safety units in transportation equipment, etc., appropriate measures should be taken.

- 5. We are making the utmost effort to improve the quality and reliability of our products. However, there is a very slight possibility of failure in semiconductor devices. To avoid damage to social or official organizations, much care should be taken to provide sufficient redundancy and fail-safe design.

- 6. No radiation-hardened design is incorporated in THC63DV151.

- 7. Judgment on whether THC63DV151 comes under strategic products prescribed by the Foreign Exchange and Foreign Trade Control Law is the user's responsibility.

- 8. This technical document was provisionally created during development of THC63DV151, so there is a possibility of differences between it and the product's final specifications. When designing circuits using THC63DV151, be sure to refer to the final technical documents.

- 9. User acknowledges that no warranty whatsoever, whether express, implied or statutory, of non-infringement of patent rights or any other intellectual property rights of other's is provided hereunder for the use of LSI sold by THine in any implementation or application not in compliance, in part or in whole, with the Digital Visual Interface (DVI) specification as being promoted by Digital Display Working Group (DDWG), and User further acknowledges that User shall be solely responsible for any consequence, technical or legal, of such implementation or application.

THine Electronics, Inc.

6F-1-10-7, Hatchobori, Chuo-ku, Tokyo, 104-0032 Japan

Tel: 81-3-3555-0666 Fax: 81-3-3555-0677