TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9172AP, TC9227P, TC9228P

# HIGH SPEED PLL WITH BUILT-IN PRESCALER

TC9172AP, TC9227P and TC9228P are high-speed PLL-LSI developed for digital tuning system use, and contain 2-modulus prescaler.

When they are used in combination with system controller LSI TC9301AN, TC9302AF, TC9303AN, TC9306F series, high performance digital synthesized tuner can be realized.

#### **FEATURES**

- They contain prescaler, and can directly input the frequency signal of 120MHz max. at FM band.

- Either pulse swallow dividing type or direct dividing type can be applied depending upon receiving band.

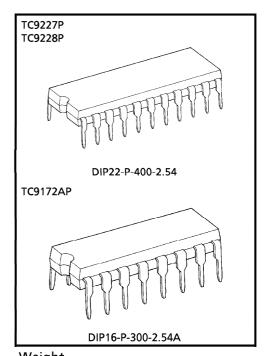

- Both high function type (DIP22 pin) and conventional type (DIP16 pin) are provided.

High function type contains IF counter which counts IF signal at FM/AM band each and produces auto-stop signal.

Weight

DIP22-P-400-2.54 : 2.1g (Typ.)

DIP16-P-300-2.54A : 1.0g (Typ.)

- Reference frequency is supplied from the controller LSI, and no crystal oscillator is required on the PLL LSI.

- They have two phase comparator outputs, and can use two kinds of low pass filters without changing.

- Abundant general purpose input-output terminals make possible the control of radio frequency circuit part.

- Frequency input terminals are provided for FM and AM, independently.

- IF offset can be easily controlled at FM band.

- As serial ports are contained, control of all functions including frequency division number setting is performed through four serial bus lines.

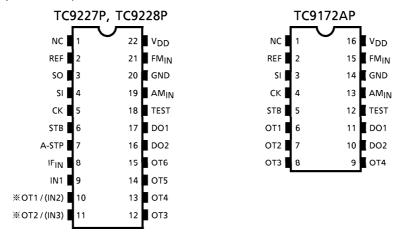

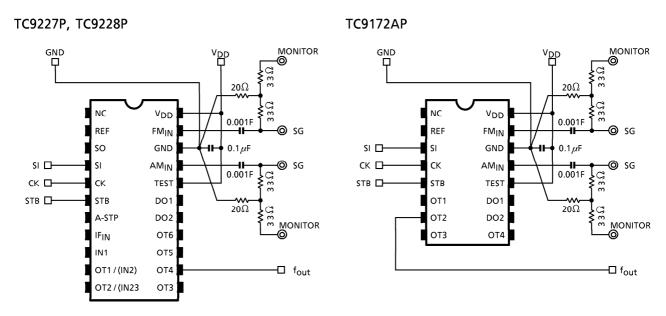

## PIN CONNECTION (TOP VIEW)

(Note) \* Bracketed letters indicate TC9228P terminal name. Others indicate common terminals.

## **VERSION TABLE**

| PRODUCTION NAME         | TC9172AP                               | TC9227P           | TC9228P   |  |  |  |

|-------------------------|----------------------------------------|-------------------|-----------|--|--|--|

| Package                 | DIP16 pin                              | DIP22 pin         | DIP22 pin |  |  |  |

| Process                 | !                                      | Silicon CMOS gate |           |  |  |  |

| Frequency Dividing Type | Pulse swallow and direct dividing type |                   |           |  |  |  |

| Serial Port             | 0                                      | 0                 | 0         |  |  |  |

| Input Port              | <del>_</del>                           | 2                 | 4         |  |  |  |

| Output Port             | 4                                      | 6                 | 4         |  |  |  |

| IF Counter              | _                                      | 0                 | 0         |  |  |  |

| Phase Comparator Output | 2                                      | 2                 | 2         |  |  |  |

| Supply Voltage          | 5V ± 10% single power supply           |                   |           |  |  |  |

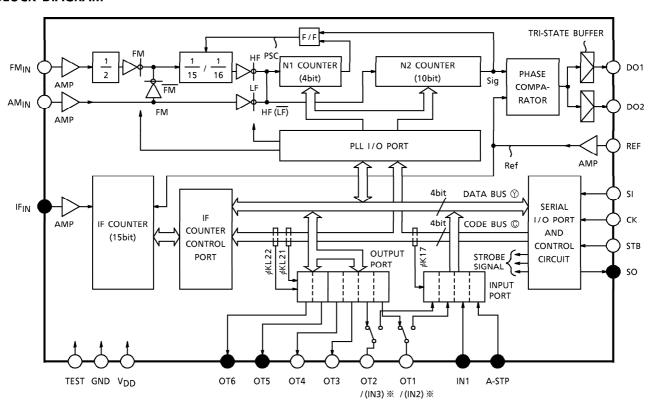

## **BLOCK DIAGRAM**

(Note) \* Bracketed letters indicate TC9228P terminal name.

Terminal does not exist in TC9172AP.

## PIN FUNCTION

( ): Terminal of TC9172AP

| PIN No. | SYMBOL | PIN NAME                     | EXPLANATION OF FUNCTIONS AND OPERATIONS                                                                              | REMARKS                                  |

|---------|--------|------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 1, (1)  | NC     | No<br>connection             | _                                                                                                                    | _                                        |

| 2, (2)  | REF    | Reference<br>frequency input | Input of reference frequency signal supplied from controller LSI. Bilt-in Amp. C coupling small amplitude operation. |                                          |

| 3, (—)  | so     | Serial output                | Serial I/O ports. Carries out between controller the setting of frequency                                            | V <sub>DD</sub>                          |

| 4, (3)  | SI     | Serial input                 | dividing number, dividing type, and the transfer of data for controlling IF counter, general purpose I/O ports.      | SO S |

| 5, (4)  | СК     | Clock signal input           | As TC9172AP has no serial output mode. SO terminal does not exist.                                                   |                                          |

| 6, (5)  | STB    | Strobe signal input          | SO terminal is P-ch open drain output, and SI, CK, STB terminals are Schmitt trigger inputs.                         | SI, CK, STB                              |

3 2001-06-19

| PIN No   | SYMBOL           | PIN NAME                               | EXPLANATION OF FUNCTIONS AND OPERATIONS                                                                                   | REMARKS         |

|----------|------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------|

|          | A-STP            |                                        | Inputs auto stop signal. It can be used as general                                                                        | C No            |

| 7, (—)   | A-31P            | Auto stop input                        | purpose input port also. (TC9227P, TC9228P)                                                                               | 0-70-           |

| 8, (—)   | IF <sub>IN</sub> | IF signal input                        | IF signal input of IF counter to detect auto stop. Built-in Amp. C coupling small amplitude operation (TC9227P, TC9228P). | O-F             |

| 9, (—)   | IN1              | General purpose input port             | Freely usable general purpose input terminal (TC9227P, TC9228P)                                                           | 0>              |

| 10, (6)  | OT1<br>※ (IN2)   | أمرم                                   |                                                                                                                           |                 |

| 11, (7)  | OT2<br>※ (IN3)   |                                        | Freely usable general purpose output terminals.  They can be used for switching control signal output of                  |                 |

| 12, (8)  | ОТЗ              | General purpose                        | radio frequency circuit.  • TC9172AP: 4                                                                                   | <br>            |

| 13, (9)  | OT4              | output ports                           | ● TC9227P : 6<br>● TC9228P : 4                                                                                            |                 |

| 14, (—)  | ОТ5              |                                        | (Note) ※ In TC9228P, 10, 11 pins are indicated as input port.                                                             |                 |

| 15, (—)  | ОТ6              |                                        |                                                                                                                           |                 |

| 16, (10) | DO2              | Phase comparator                       | Tri-state outputs of phase comparator.                                                                                    | V <sub>DD</sub> |

| 17, (11) | DO1              | outputs                                | DO1, DO2 are parallel outputs.                                                                                            |                 |

| 18, (12) | TEST             | Test terminal                          | Test mode control input. With pull-down resistance. Usually, used in OPEN state or GND connected.                         |                 |

| 19, (13) | AMIN             | AM local oscillator signal input       | Programmable counter input at AM band. Built-in Amp. C coupling small amplitude operation.                                |                 |

| 21, (15) | FM <sub>IN</sub> | FM local<br>oscillator signal<br>input | Prescaler input at FM band. f <sub>MAX</sub> = 120MHz<br>Built-in Amp. C coupling small amplitude operation.              |                 |

| 22, (16) | $V_{DD}$         | Power supply                           | Supply 5V ± 10%                                                                                                           | _               |

| 20, (14) | GND              | terminal                               | Supply 50 = 1570                                                                                                          | _               |

# I/O MAP ● TC9227P, TC9228P I/O MAP

|                 | 1/0      | .9220F 1/C                                 | PLL           | (1)          |             | GENE | GENERAL PURPOSE OUTPUT (2) |           |     |

|-----------------|----------|--------------------------------------------|---------------|--------------|-------------|------|----------------------------|-----------|-----|

| CODE            |          | Y1                                         | Y2            | Y4           | Y8          | Y1   | Y2                         | Y4        | Y8  |

|                 |          | Programmable counter dividing type setting |               |              |             |      |                            |           |     |

|                 | 0        | HF                                         | ⊿IF + 1       | ⊿IF – 1      | FM          |      |                            |           |     |

|                 | 1        | Programmal                                 | ble counter o | dividing num | ber setting | G    | eneral pur                 | pose outp | ut  |

|                 | <u>'</u> | P0                                         | P1            | P2           | P3          | OT1  | OT2                        | OT3       | OT4 |

|                 | 2        |                                            | Same a        | s above      |             |      | eneral pur                 | pose outp | ut  |

| *               |          | P4                                         | P5            | P6           | P7          | OT5  | ОТ6                        |           |     |

| l RC            | 3        |                                            | Same a        |              |             |      |                            |           |     |

| INPUT PORT (K)  |          | P8                                         | P9            | P10          | P11         |      |                            |           |     |

| 5               | 4        |                                            | Same a        | s above      |             | ·    |                            |           |     |

| 집               |          | P12                                        | P13           |              |             |      |                            |           |     |

|                 | 5        |                                            |               |              |             |      |                            |           |     |

|                 | 6        |                                            |               | r control    |             |      |                            |           |     |

|                 |          | BUSY                                       | WIDE          | STOP         |             |      |                            |           |     |

|                 | 7        |                                            | eneral pu     |              |             |      |                            |           |     |

|                 |          | A-STP                                      | IN1           | IN2          | IN3         |      |                            |           |     |

|                 | 8        | Programmable counter dividing type setting |               |              |             |      |                            |           |     |

|                 | Ľ        | HF                                         | ⊿IF + 1       | ⊿IF – 1      | FM          |      |                            |           |     |

|                 | 9        | Programmal                                 | ble counter o | dividing num | ber setting |      | eneral pur                 |           |     |

|                 |          | P0                                         | P1            | P2           | P3          | OT1  | OT2                        | OT3       | OT4 |

| _               | A        |                                            | Same a        | s above      |             | G    | eneral pur                 | pose outp | ut  |

| OUTPUT PORT (L) |          | P4                                         | P5            | P6           | P7          | OT5  | ОТ6                        |           |     |

| l RC            | В        |                                            | Same a        | s above      |             |      |                            |           |     |

| Z               |          | P8                                         | P9            | P10          | P11         |      |                            |           |     |

| 5               | c        |                                            | Same a        | s above      |             |      |                            |           |     |

| ᆸ               |          | P12                                        | P13           |              |             |      |                            |           |     |

| 3               | D        |                                            |               | de data      |             |      |                            |           |     |

|                 |          | 1                                          | 2             | 4            |             |      |                            |           |     |

|                 | E        |                                            | IF counte     |              |             |      |                            |           |     |

|                 |          | START                                      | WIDE          | RESET        |             |      |                            |           |     |

|                 | F        | Ch                                         | ip select c   | - ac aata    | <b>′1″</b>  |      | ip select c                |           | 2"  |

|                 | <u>'</u> | 1                                          | 0             | 0            | 0           | 0    | 1                          | 0         | 0   |

## • TC9172AP I/O MAP

|                     | 1/0 |                                            | PLL           | (1)          |             | GENERAL PURPOSE OUTPUT (2) |             |            | JT (2) |

|---------------------|-----|--------------------------------------------|---------------|--------------|-------------|----------------------------|-------------|------------|--------|

| CODE                | \   | Y1                                         | Y2            | Y4           | Y8          | Y1                         | Y2          | Y4         | Y8     |

|                     | 0   |                                            |               |              |             |                            |             |            |        |

| $\overline{\Sigma}$ | 1   |                                            |               |              |             |                            |             |            |        |

| )<br> -             | 2   |                                            |               |              |             |                            |             |            |        |

| g                   | 3   |                                            |               |              |             |                            |             |            |        |

| <u>L</u>            | 4   |                                            |               |              |             |                            |             |            |        |

| INPUT PORT (K)      | 5   |                                            |               |              |             |                            |             |            |        |

| =                   | 6   |                                            |               |              |             |                            |             |            |        |

|                     | 7   |                                            |               |              |             |                            |             |            |        |

|                     | 8   | Programmable counter dividing type setting |               |              |             |                            |             |            |        |

|                     |     | HF                                         | ⊿IF + 1       | ⊿IF – 1      | FM          |                            |             |            |        |

|                     | 9   | Programma                                  | ble counter o | dividing num | ber setting | General purpose output     |             |            | ut     |

|                     |     | P0                                         | P1            | P2           | P3          | OT1                        | OT2         | OT3        | OT4    |

| ] E                 | Α   |                                            | Same a        | above        |             |                            |             |            |        |

| RT                  |     | P4                                         | P5            | P6           | P7          |                            |             |            |        |

| S                   | В   |                                            | Same a        | above        |             |                            |             |            |        |

| OUTPUT PORT (L)     |     | P8                                         | Р9            | P10          | P11         |                            |             |            |        |

| E                   | С   |                                            | Same a        | above        |             |                            |             |            |        |

| ŏ                   |     | P12                                        | P13           |              |             |                            |             |            |        |

|                     | D   |                                            |               |              |             |                            |             |            |        |

|                     | E   |                                            |               |              |             |                            |             |            |        |

|                     | F   | Ch                                         | ip select c   | ode data "   | 1"          | Ch                         | ip select c | ode data ' | '2"    |

|                     | '   | 1                                          | 0             | 0            | 0           | 0                          | 1           | 0          | 0      |

(Note) TC9172AP contains no input port.

As it contains IF counter, there is no control port of it.

#### **OPERATIONS**

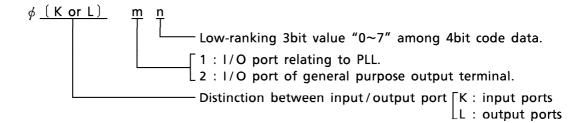

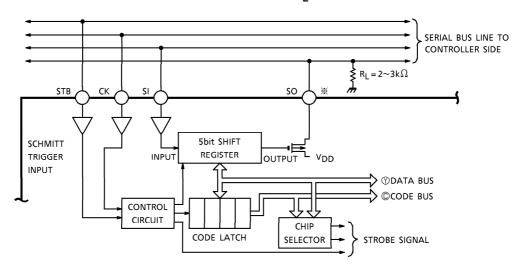

In TC9172AP, TC9227P, TC9228P as indicated in the block diagram, each function is controlled by accessing the ports connected with 4bit data bus  $\odot$  and code bus  $\odot$ .

Each data on this data bus and code bus is conducted from the controller LSI by four terminals of SI, SO, CK, STB (three terminals of SI, CK, STB in the case of TC9172AP).

As control is all made with port, explanations will be given here chiefly about the functions of each port. These ports are constituted with 4bit units, and selected by 4bit code data. Code assignment of each port is shown in I/O map indicated previously. On the whole, code "0H~7H" is assigned to input port, and code "8H~FH" to output port.

(Note 1) "Input port" and "Output port" mentioned here are always based on the controller LSI. Thus, the port served when putting out data from controller LSI is called the output port, while the port (which data is taken from PLL side) to controller LSI is called the input port.

(Note 2) In this explanation, code assignment of each port is encoded as shown below.

(Example)  $\phi$  K17 : General purpose input port  $\phi$  L21 : General purpose output ports OT1~OT4

#### Programmable counter

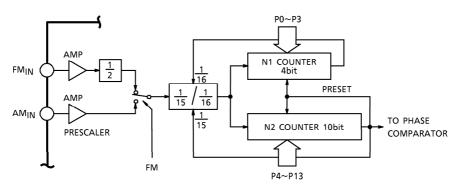

Programmable counter block is composed of two modulus prescaler, 4bit + 10bit programmable binary counter, and PLL I/O ports to control the above.

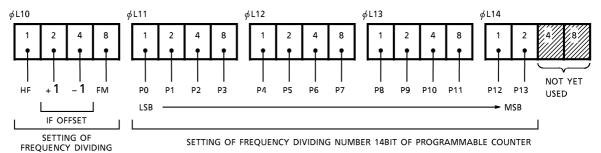

- 1. PLL I/O ports ( $\phi$  KL10 $\sim$  $\phi$  KL14)

- (1) Exclusive PLL ports to entirely control frequency dividing number, dividing type and IF correction (IF offset) at FM band.

- (2) In TC9227P, TC9228P PLL ports are entirely I/O port structure. Therefore, it is possible to take the set data again into the controller LSI by accessing input port. ( $\phi$ K10 $\sim$  $\phi$ K14)

7 2001-06-19

# (3) PLL port configuration

# (4) Setting of frequency dividing type

Selection of pulse swallow dividing type or direct dividing type is made by HF, FM ports. Make selection from the following three types according to the applied frequency band.

| HF | FM | FREQUENCY DIVIDING TYPE                                                          | RECEIVING<br>BAND<br>EXAMPLE | INPUT<br>FREQUENCY<br>RANGE | INPUT<br>TERMINAL | FREQUENCY<br>DIVIDING<br>NUMBER |

|----|----|----------------------------------------------------------------------------------|------------------------------|-----------------------------|-------------------|---------------------------------|

| 0  | 0  | Direct dividing                                                                  | LW, MW, SW <sub>L</sub>      | 0.5~ 10MHz                  | AMIN              | n                               |

| 1  | 0  | $\left(\frac{1}{15} / \frac{1}{16}\right)$ pulse swallow type                    | sw <sub>H</sub>              | 8~ 60MHz                    | AMIN              | n                               |

| 0  | 1  | Not use                                                                          |                              |                             |                   |                                 |

| 1  | 1  | $\left(\frac{1}{2} \times \frac{1}{15} / \frac{1}{16}\right)$ pulse swallow type | FM                           | 50~140MHz                   | FM <sub>IN</sub>  | 2·n                             |

(Note) n represents programmed frequency dividing numeral value.

#### (5) IF offset function at FM band

When pulse swallow dividing type is selected, it is possible to vary actual frequency dividing number by  $\pm 1$  without changing the programmed dividing numerals by  $\Delta IF \pm 1$  ports. Thus, it can be applied to IF offset at FM band. In the case of direct dividing type selection, IF off set function does not operate.

| ⊿IF + 1 | ⊿IF – 1 | FREQUENCY DIVIDING NUMBER (AT FM BAND) |

|---------|---------|----------------------------------------|

| 0       | 0       | 2·n                                    |

| 0       | 1       | 2· (n − 1)                             |

| 1       | 0       | 2· (n + 1)                             |

| 1       | 1       | 2· (n − 1)                             |

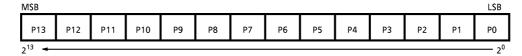

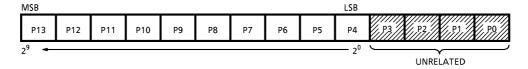

(6) Setting of frequency dividing number

Dividing number of programmable counter is set on P0~P13 ports with binary.

• At pulse swallow type (14bit)

- $\times$  Frequency dividing number setting range (pulse swallow type)  $n = 210H \sim 3FFFH$  (528 $\sim 16383$ )

- At direct dividing type (10bit)

- \*\* Frequency dividing number setting range (direct dividing type)  $n = 10H \sim 3FFH (16 \sim 1023)$

- (Note 1) As the programmable counter is not provided with frequency dividing offset, the programmed dividing number becomes the actual frequency dividing number. However, in the case of FM band, the actual frequency dividing number becomes two times of programmed value.

- (Note 2) In the case of direct dividing type, P0 $\sim$ P3 port ( $\phi$ L11) data become unrelated, and P4 port becomes LSB.

- (Note 3) Frequency dividing number is entirely renewed at the time of data setting of MSB port ( $\phi$ L14). For this reason, the data of MSB port ( $\phi$ L14) must be set at the end of dividing number setting.

- Even when the data setting is considered unnecessary (When the data is same as the previous one), the data setting must be executed for MSB port ( $\phi$ L14).

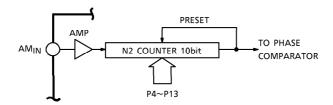

- 2. Circuit configuration of prescaler and programmable counter.

- (1) Circuit configuration of pulse swallow dividing type

The circuit is composed of 1/15, 1/16 2-modulus prescaler and binary programmable counter of 4bit on N1 side and 10bit on N2 side.

In the case of FM band, 1/2 divider is added to the front stage of prescaler.

(2) Circuit configuration of direct dividing type

In this case, prescaler block is passed and N2 side counter 10 bits is used.

(3) Both FM<sub>IN</sub>, AM<sub>IN</sub> terminals have built-in amp. and small amplitude operation is possible with capacitor coupling.

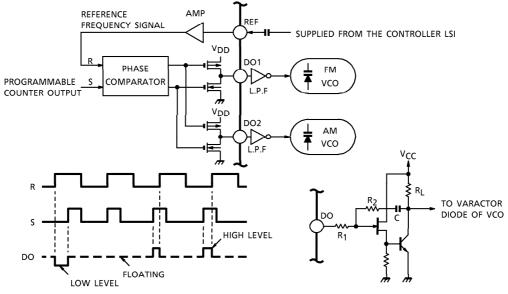

#### Phase comparator

Phase comparator compares the phase difference between the reference frequency signal applied to REF terminal and programmable counter dividing output signal, and puts out its error component. Further, it controls VCO through low pass filter as that the frequency and phase of these two signals may agree with each other.

- 1. Two tri-state buffer DO1, DO2 terminals are put out in parallel from the phase comparator. For this reason, optimum design of filter constant can be made for each of FM/AM band.

- 2. Reference frequency signal is supplied from the controller LSI to the REF terminal, and no crystal oscillator is needed on PLL LSI.

- 3. REF input has built-in amp. and small amplitude operation is possible with capacitor coupling.

DO output timing chart

Example of active low pass filter

Shown above are indicated DO output timing chart and example of active low pass filter circuit by darlington connection of FET and transistor.

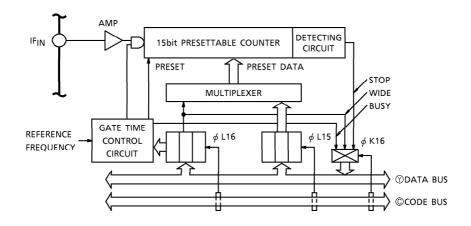

#### ○ IF counter (TC9227P, TC9228P)

TC9227P, TC9228P have IF counter which counts intermediate frequency (IF) of FM or AM during auto search tuning, and produces auto stop signal when that frequency has entered in the specified range. TC9172AP contains no IF counter.

IF counter block is composed of 15bit presettable counter and IF counter control ports.

# 1. Operation of IF counter

IF counter counts IF signal of 10.7MHz at FM band and 450kHz at AM band, and its gate-time is made of the reference frequency signal supplied to REF input.

- (1) IF<sub>IN</sub> terminal has built-in amp. and is capable of making small amplitude operation with capacitor coupling.

- (2) IF counter has two kinds of detectability, WIDE/NARROW.

- (3) Gate time and detectability in each band are shown below.

|        | REFERENCE          | NAF               | RROW                  | WIDE              |                       |  |

|--------|--------------------|-------------------|-----------------------|-------------------|-----------------------|--|

| BAND   | FREQUENCY<br>(kHz) | GATE TIME<br>(ms) | DETECTABILITY<br>(Hz) | GATE TIME<br>(ms) | DETECTABILITY<br>(Hz) |  |

| LW     | 1                  | 20                | 450k ± 600            | 5.0               | 450k ± 2.4k           |  |

| SW     | 5                  | 4.0               | 450k ± 3k             | 1.0               | 450k ± 12k            |  |

| MW 9k  | 9                  | 2.2               | 450k ± 5.4k           | 0.55              | 450k ± 21.6k          |  |

| MW 10k | 10                 | 2.0               | 450k ± 6k             | 0.50              | 450k ± 24k            |  |

| FM     | 12.5               | 1.6               | 10.7M ± 15k           | 0.4               | 10.7M ± 60k           |  |

| FIVI   | 25                 | 0.8               | 10.7W ± 15K           | 0.2               | 10.71VI ± 60K         |  |

## 2. IF counter control output port

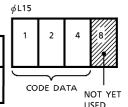

(1) REF code data output port ( $\phi$ L15)

It sets the code data corresponding to the reference frequency which serves as time base. Never fail to set the code of the presently employed reference frequency signal.

• Reference frequency code table

| CODE DATA              | 0  | 1*  | 2  | 3*   | 4  | 5   | 6     | 7   |

|------------------------|----|-----|----|------|----|-----|-------|-----|

| Reference<br>Frequency | 1k | 50k | 5k | 100k | 9k | 10k | 12.5k | 25k |

(Note) \* : Code "1", "3" can not use.

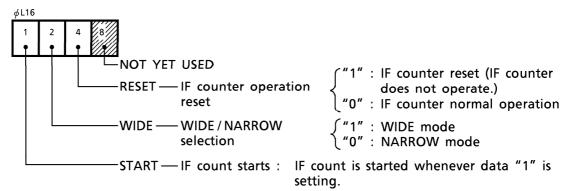

(2) IF counter control output port ( $\phi$ L16)

(3) IF counter control input port ( $\phi$ K16)

- (Note 1) In the case of auto stop detection by IF counter, refer to the contents of STOP port after confirmation that BUSY port is "0" (counting completed).

- (Note 2) IF counter cannot be used when reference frequency of 50kHz or 100kHz is used at FM band or when IF off set is carried out. The same applies to the case where frequency other than 10.7MHz and 450kHz is used for IF signal.

- O General purpose input and output ports

They have general purpose input/output terminals controlled with 4bit units. However, TC9172AP has output terminals only.

|          | NUMBER OF INPUT<br>TERMINAL | NUMBER OF OUTPUT<br>TERMINAL |

|----------|-----------------------------|------------------------------|

| TC9172AP | _                           | 4                            |

| TC9227P  | 2                           | 6                            |

| TC9228P  | 4                           | 4                            |

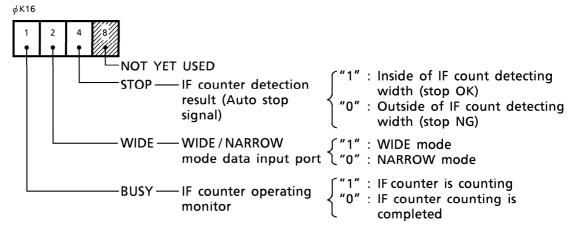

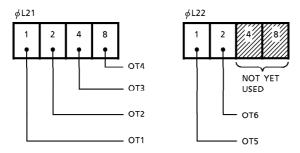

# (1) General purpose output ports ( $\phi$ L21, $\phi$ L22)

(Note) TC9172AP has no  $\phi$ L22 port. In the case of TC9228P, OT1, OT2 ports are not output terminals.

The set data is put out in positive logic.

Output terminals are CMOS structure. In TC9227P, TC9228P general purpose output ports are entirely I/O ports structure. Therefore, it is possible to take the set data again into the controller side by accessing input ports ( $\phi$ K21,  $\phi$ K22).

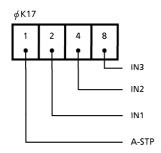

## (2) General purpose input port ( $\phi$ K17)

- (Note 1) In TC9227P, data of IN2, IN3 ports is "0".

Further, TC9172AP has no general purpose input port.

- (Note 2) A-STP port is for auto stop signal input use, but it can be applied to other use.

Data is got in positive logic. Input terminals are CMOS structure.

#### ○ Serial I/O ports

As shown previously, each port is controlled through serial ports and serial bus line. Serial ports control the data transfer between the serial bus line and code data bus line of IC inside.

Number of input/output terminals of serial port is as follows:

TC9172AP ...... 3 terminals (SI, CK, STB), without input port.

TC9227P, TC9228P . . 4 terminals (SO, SI, CK, STB), with input port.

SI, CK, STB terminals contain Schmitt trigger input, and SO terminal has P-ch FET open drain output construction.

(Note) SO terminal needs external load resistance. ( $R_L = 2k \sim 3k\Omega$ )

(Note) \* TC9172AP has no SO terminal.

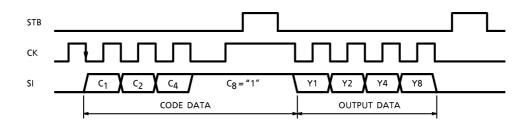

#### 1. Data transfer format

(1) Data output timing (access of output port)

Code data ( $C_1 \sim C_8$ ) 4 bits of output port and output data (Y1 $\sim$ Y8) 4 bits are serially transferred to SI terminal with the timing shown above.

SI data is read in with the rising of CK.

(Note) During the designation of output port, code data "Cg" is "1" at all times.

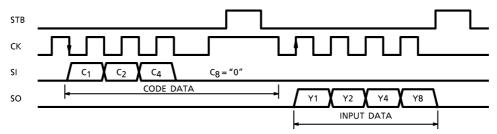

## (2) Data input timing (access of input port)

When code data ( $C_1 \sim C_8$ ) 4 bits of input port is transferred to SI terminal with the above timing, the data of designated port is output to SO terminal with 4bit serial of Y1 $\sim$ Y8. SI data is read in with the rising of CK signal, and SO data is output with the rising of CK signal.

(Note) During the designation of input port, code data "C8" is "0" at all times.

### 2. Designation of chip select

Besides PLL IC, various peripheral option ICs can be connected on the serial bus line. It is necessary, therefore, to designate the IC connected with controller LSI through bus line, between which data is to be transferred.

Chip select code is provided to designate the controlled IC on the bus line. Select code for designating TC9172AP, TC9227P and TC9228P is as follows:

- Chip select code for PLL I/O ports : 1

- Chip select code for general purpose output ports: 2

- (1) Select code is set up to the chip select code data output port. (code "FH")

- (2) Select code must be set up first at the time of serial data transfer.

- (3) Select code once set maintains the same data unless otherwise designated, and so, there is no need of designating select code every time serial data is transferred.

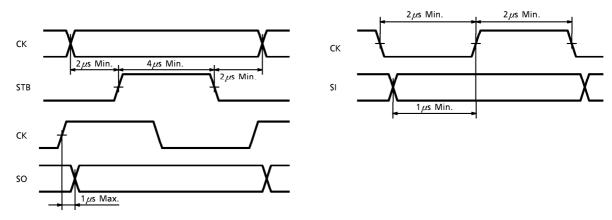

#### 3. Pulse width of serial timing

| MAXIMI | JM RAT | INGS (* | $\Gamma a = 25^{\circ}C$ |

|--------|--------|---------|--------------------------|

| CHARACTERISTIC        | SYMBOL           | RATING                   | UNIT |

|-----------------------|------------------|--------------------------|------|

| Supply Voltage        | $V_{DD}$         | -0.3~6.0                 | V    |

| Input Voltage         | VIN              | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Power Dissipation     | PD               | 300                      | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>-</b> 30∼75           | Ĵ    |

| Storage Temperature   | T <sub>stg</sub> | <b>-</b> 55∼125          | °C   |

**ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, Ta = 25°C, V<sub>DD</sub> = 5V)

| CHARACTERISTIC                    | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|-----------------|----------------------|---------------------------|------|------|------|------|

| Operating Supply<br>Voltage Range | V <sub>DD</sub> | _                    | *                         | 4.5  | 5.0  | 5.5  | ٧    |

| Operating Supply<br>Current       | lDD             | _                    | FM <sub>IN</sub> = 120MHz | _    | 15   | 25   | mA   |

Operating frequency range

|                            | <u> </u>         |   |                       |   |     |   |     |     |

|----------------------------|------------------|---|-----------------------|---|-----|---|-----|-----|

| FMIN                       | fFM1             | 1 | $V_{IN} = 0.5V_{p-p}$ | * | 50  | ~ | 140 | MHz |

| FM <sub>IN</sub>           | f <sub>FM2</sub> | 1 | $V_{IN} = 0.3V_{p-p}$ | * | 50  | ~ | 120 | MHz |

| AM <sub>IN</sub> (HF Mode) | fAMH             | 1 | $V_{IN} = 0.3V_{p-p}$ | * | 8   | ~ | 60  | MHz |

| AM <sub>IN</sub> (LF Mode) | fAML             | 1 | $V_{IN} = 0.3V_{p-p}$ | * | 0.5 | ~ | 10  | MHz |

| IFIN                       | fIF              | _ | $V_{IN} = 0.3V_{p-p}$ | * | 0.4 | ~ | 13  | MHz |

| REF Input                  | fREF             | _ | $V_{IN} = 0.2V_{p-p}$ | * | 1   | ~ | 100 | kHz |

Operating input amplitude range

| FM <sub>IN</sub>           | V <sub>IN1</sub> (FM) | 1 | f <sub>IN</sub> = 50~140MHz | * | 0.5 | ~ | V <sub>DD</sub> – 0.5 | V <sub>p-p</sub> |

|----------------------------|-----------------------|---|-----------------------------|---|-----|---|-----------------------|------------------|

| FM <sub>IN</sub>           | V <sub>IN2</sub> (FM) | 1 | f <sub>IN</sub> = 50~120MHz | * | 0.3 | ~ | V <sub>DD</sub> – 0.5 | $V_{p-p}$        |

| AM <sub>IN</sub> (HF Mode) | VIN (AMH)             | 1 | f <sub>IN</sub> = 8~60MHz   | * | 0.3 | ~ | V <sub>DD</sub> – 0.5 | V <sub>p-p</sub> |

| AM <sub>IN</sub> (LF Mode) | VIN (AML)             | 1 | f <sub>IN</sub> = 0.5~10MHz | * | 0.3 | ~ | V <sub>DD</sub> – 0.5 | V <sub>p-p</sub> |

| IFIN                       | VIN (IF)              | _ | f <sub>IN</sub> = 0.4~13MHz | * | 0.3 | ~ | V <sub>DD</sub> – 0.5 | V <sub>p-p</sub> |

| REF Input                  | VIN (REF)             | _ | f <sub>IN</sub> = 1~100kHz  | * | 0.2 | ~ | $V_{DD}$              | V <sub>p-p</sub> |

OT1~6, DO1~2, SO

| Output                    | "H" Level | Iон             | _ | V <sub>OH</sub> = 4V, SO terminal is excepted | - 0.5 | - 1.0 | 1     | mA      |

|---------------------------|-----------|-----------------|---|-----------------------------------------------|-------|-------|-------|---------|

| Current                   | "L" Level | lOL             | _ | V <sub>OL</sub> = 1V, SO terminal is excepted | 0.5   | 10    | _     | IIIA    |

| SO Terminal<br>Current    | Output    | I <sub>SO</sub> | _ | V <sub>OH</sub> = 4V                          | - 2.0 | - 3.0 | _     | mA      |

| SO Terminal<br>Current    | Off Leak  | lOFF            | _ | V <sub>OUT</sub> = 0V                         | _     |       | - 1.0 | $\mu$ A |

| DO Termina<br>Leakage Cui |           | I <sub>TL</sub> | _ | V <sub>TLH</sub> = 5V, V <sub>TLL</sub> = 0V  | _     |       | ± 0.5 | $\mu$ A |

IN1~3, SI, CK, STB, A-STP

| Input   | "H" Level | lн              |   | V <sub>IH</sub> = 5V | _   | _ | 1.0   | μΑ    |

|---------|-----------|-----------------|---|----------------------|-----|---|-------|-------|

| Current | "L" Level | կլ              | _ | V <sub>IL</sub> = 0V | _   | _ | - 1.0 | $\mu$ |

| Input   | "H" Level | V <sub>IH</sub> | _ | _                    | 4.0 | ~ | 5.0   | V     |

| Voltage | "L" Level | V <sub>IL</sub> | _ | _                    | 0   | ~ | 1.0   | \ \ \ |

(Note) : \* Marked characteristics are guaranteed in a range of  $V_{DD} = 4.5 \sim 5.5 \text{V}$ ,  $T_a = -30 \sim 75 ^{\circ}\text{C}$ .

## **TEST CIRCUIT**

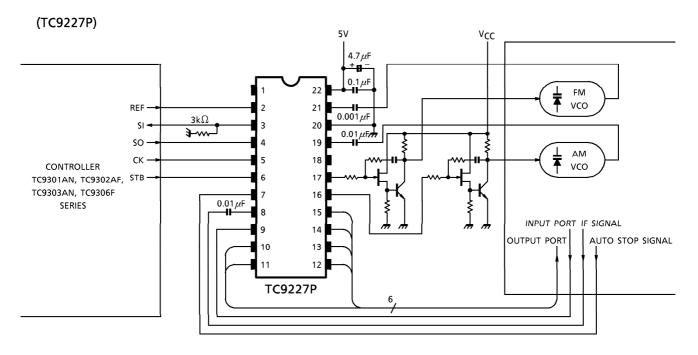

## **EXAMPLE FOR APPLICATION CIRCUIT**

19

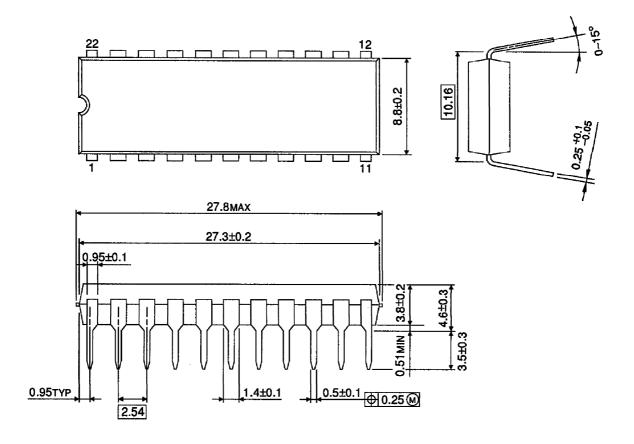

## **PACKAGE DIMENSIONS**

Weight: 2.1g (Typ.)

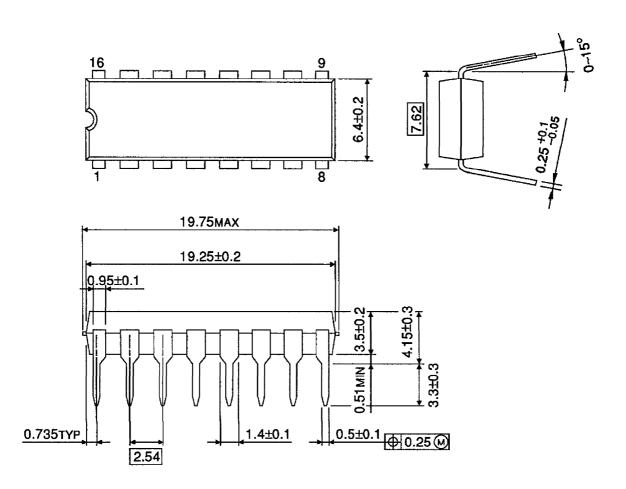

## PACKAGE DIMENSIONS DIP16-P-300-2.54A

Unit: mm

Weight: 1.0g (Typ.)

#### RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.