TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9314F

# SINGLE-CHIP DTS MICROCONTROLLER (DTS-22)

TC9314F is a 4bit CMOS microcontroller for single-chip digital tuning systems with built-in prescaler, PLL and LCD driver.

The CPU has 4bit parallel addition/subtraction (eg, AI and SI instructions), logical operations (eg, OR and AN), several bit judge and compare instructions (eg, TM and SL), and time base functions.

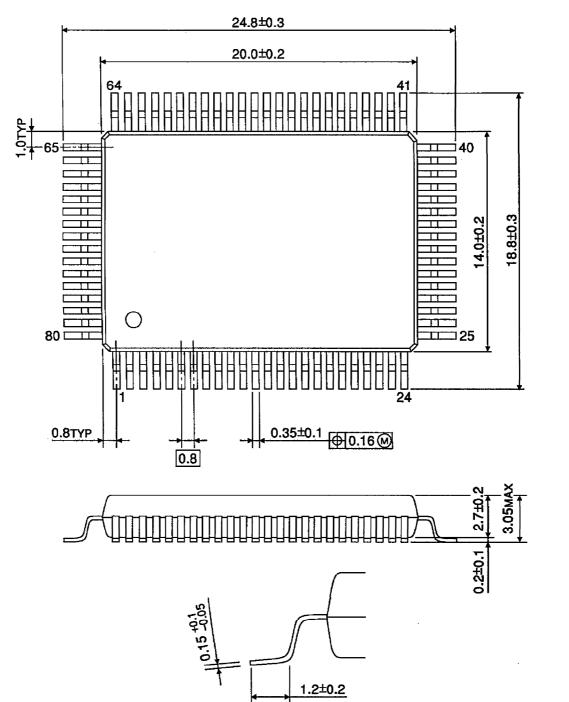

The device is in an 80pin mini flat package. It includes abundant I/O ports controlled by powerful input and output instructions (IN1-3, OUT1-3) exclusive key input ports, abundant LCD output ports, interrupts, a BUZR port, 6bit A/D and D/A converters, serial interface, and IF counter.

With CMOS architecture for low power consumption, TC9314F is ideal for providing digital tuning for multiband radios, radio-cessatte players and other portable equipment.

Weight: 1.57g (Typ.)

#### **FEATURES**

- 4bit microcontroller for single-chip digital tuning systems

- Operating voltage V<sub>DD</sub> of 2.7~5.5V, with CMOS architecture for low power consumption

- On-chip prescaler (fixed to 1/2 frequency division +2-modulus prescaler: fmax≥ 130MHz)

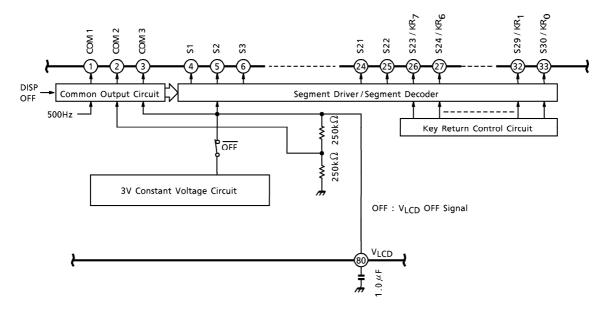

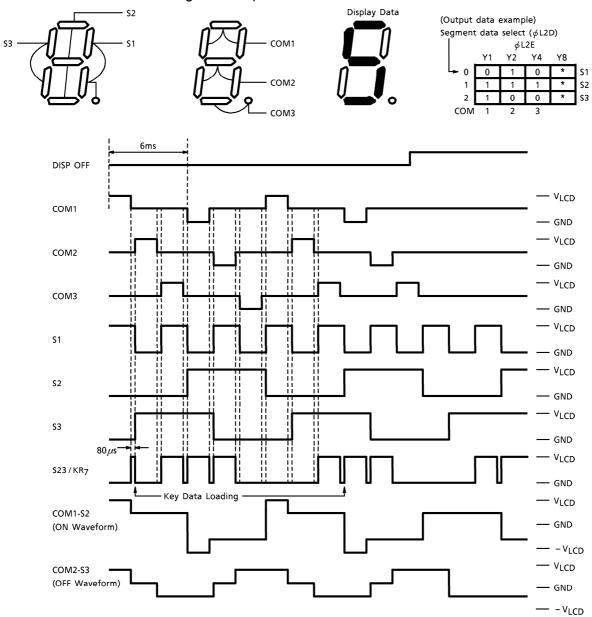

- 1/3-duty, 1/2-bias driven LCD driver, with on-chip 3V constant-voltage display circuit

- Easy backup of data memory (RAM) and various ports

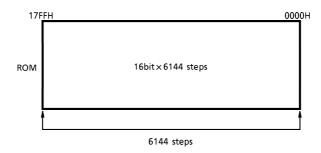

- Program ROM : 16 bits × 6144 steps

Data memory (RAM) : 4 bits × 384 words

- Powerful instruction set with 54 1-word instructions

- Instruction execution time of 40  $\mu$ s (75kHz crystal connected; 80  $\mu$ s for MVGS and DAL instructions)

- 4 add and 4 subtract instructions

(Note) This device is vulnerable to surge voltage. Take it into account when using this device in your system.

- Powerful compound judge instructions (TMTR, TMFR, TMT, TMF, TMTN and TMFN)

- Data transfer at the same row address (MVSR instruction)

- Register indirect transfer available (MVGD and MVGS instructions)

- 16 powerful general registers assigned in RAM

- Stack levels: 4

- No concepts of pages or fields in program ROM. Features 6144 steps that allow JUMP or CAL instructions at any point.

- 16bit contents of any address in 1024 steps of the program ROM can be referenced freely. (DAL instruction)

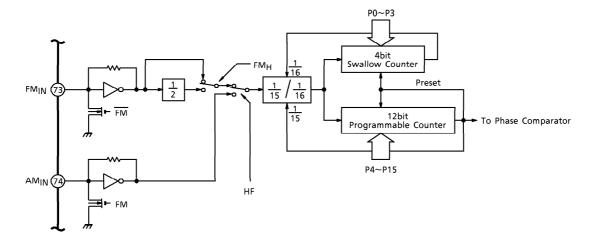

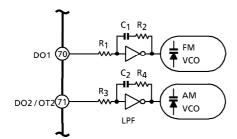

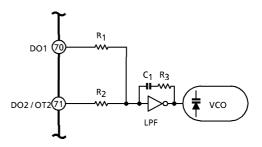

- Independent FM<sub>IN</sub> and AM<sub>IN</sub> pins for FM and AM frequency input and two phase comparison outputs (DO1 and DO2).

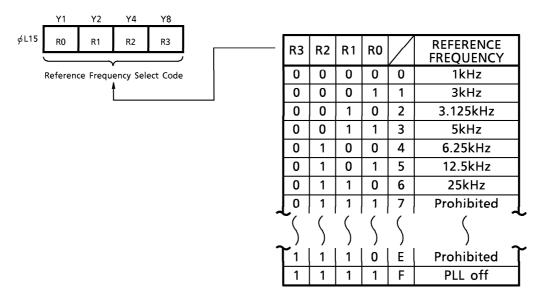

- Choice of seven reference frequencies by program

- Powerful input and output instructions (IN1~3 and OUT1~3)

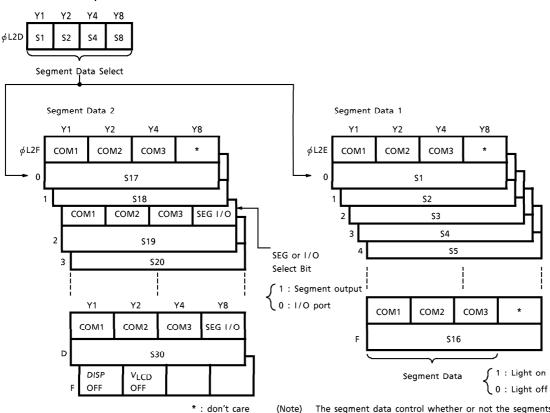

- Input-only ports (K0~K3) for key inputs and 33 LCD drive pins (90 segments maximum).

- 26 I/O ports (16 ports specifiable in units of bits, 10 output-only ports). Three pins (IF<sub>IN1</sub>, IF<sub>IN2</sub> and DO2) can be switched using instructions for use as input-only ports IN1 and IN2, and output-only port OT2, respectively. In addition LCD output pins \$19~\$30 can be switched to I/O ports in units of bits.

- 2 external interrupt input ports.

These are able to switch for use as general input ports by program.

- Three backup modes can be implemented using instructions : CPU operation only, clock generation only or clock stop.

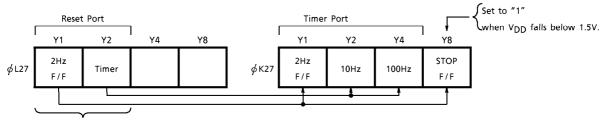

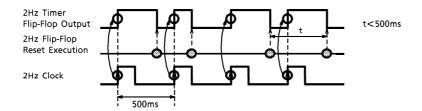

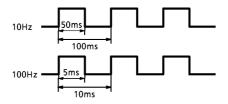

- Features a built-in 2Hz timer flip-flop and 10/100Hz interval pulse output (internal time-based port)

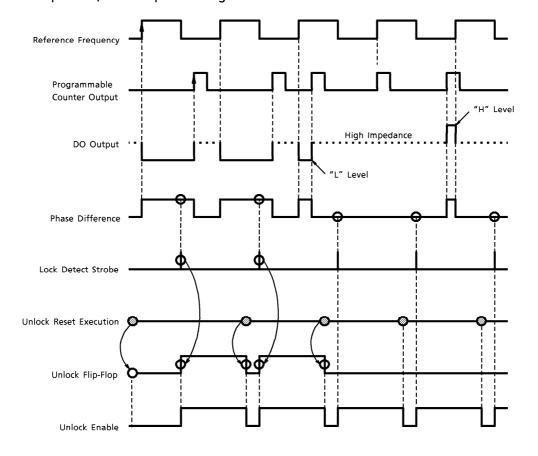

- Detection of PLL locked state supported.

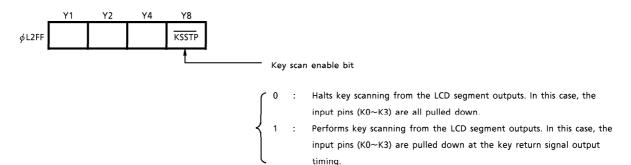

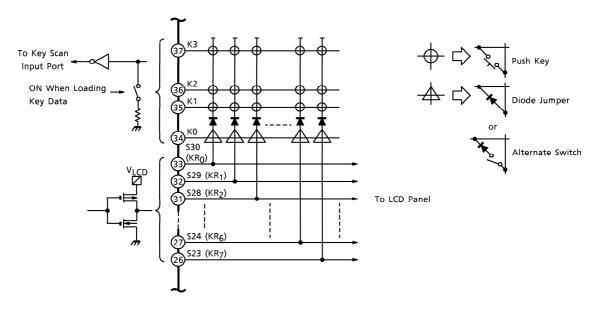

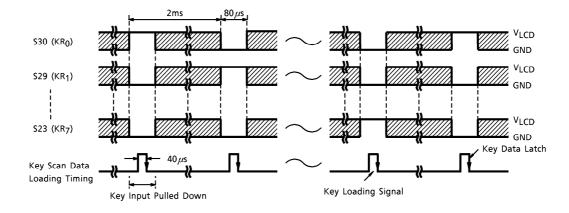

- 8 of the LCD segment outputs (\$23~\$30) can also be used as key return timing outputs (KR<sub>0</sub>~KR<sub>7</sub>), so that output ports are not monopolized by key return outputs and are available for other uses.

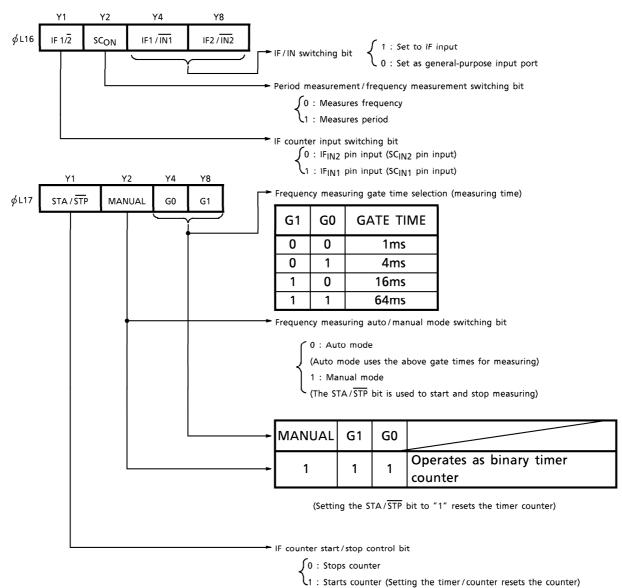

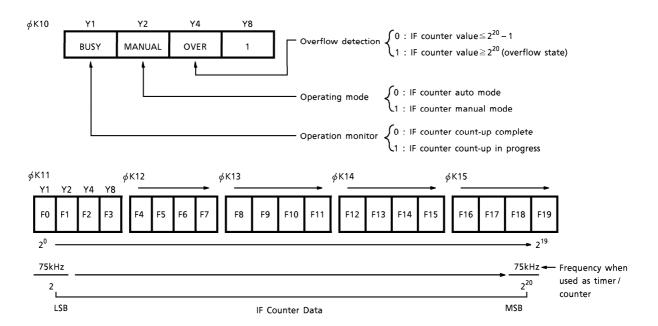

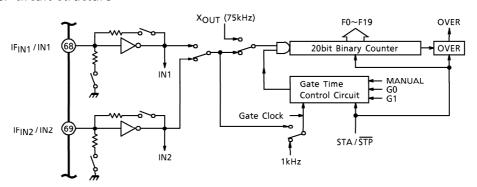

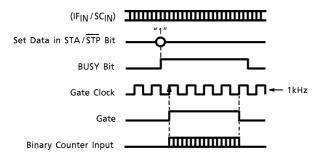

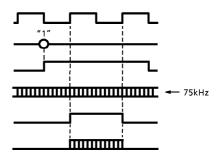

- Built-in 20bit general-purpose IF counter counts central frequencies for each band, providing station detection during automatic tuning.

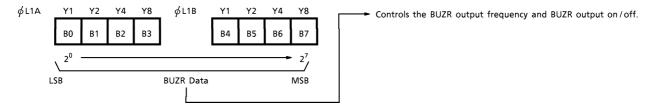

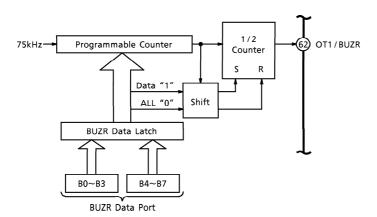

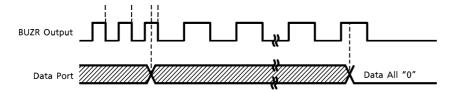

- Built-in 8bit buzzer output circuit supports generation of 254-level tone signals.

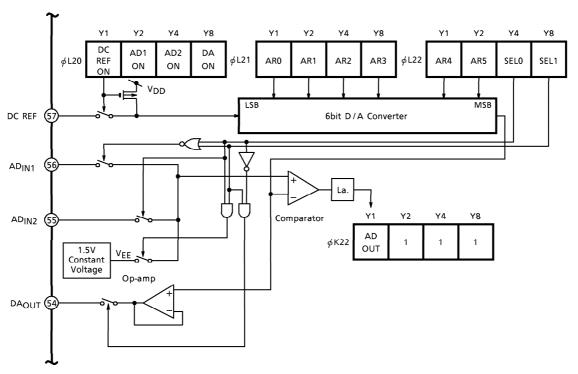

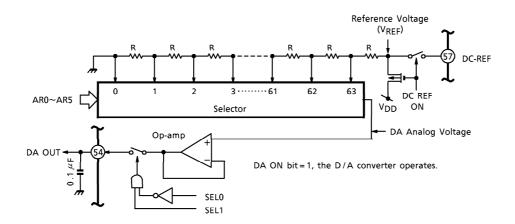

- Built-in 2-channel, 6bit A/D converter and 1-channel, 6bit D/A converter.

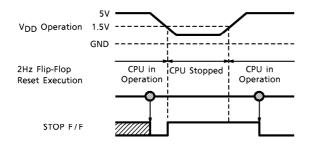

- Low-voltage detection circuit stops the CPU when power supply voltage drops below 1.5V to prevent malfunction.

- OTP Product : TC93P14F

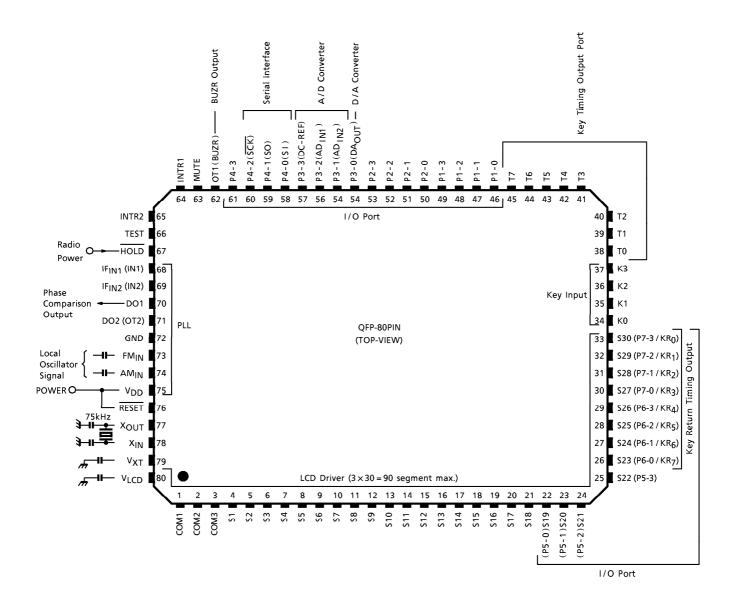

## PIN CONNECTION

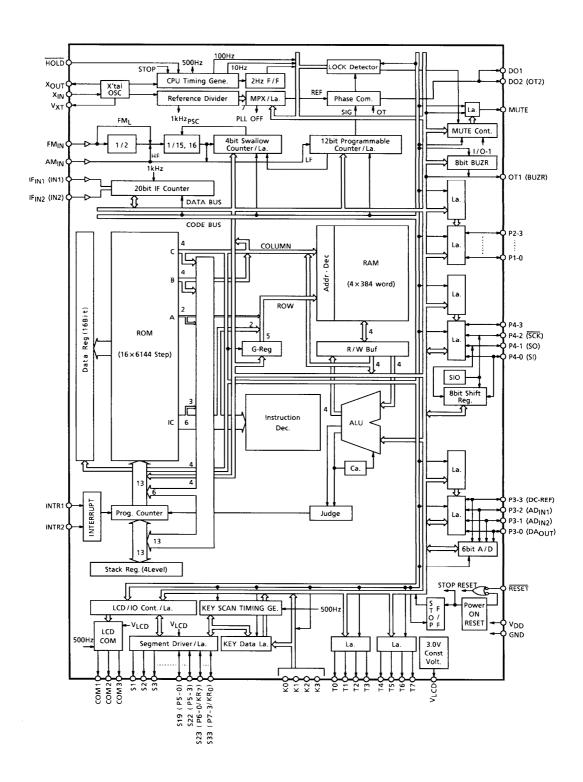

#### **BLOCK DIAGRAM**

4

# PIN FUNCTION

| PIN No. | SYMBOL                                                             | PIN NAME                                                    | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                      | REMARKS                              |

|---------|--------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

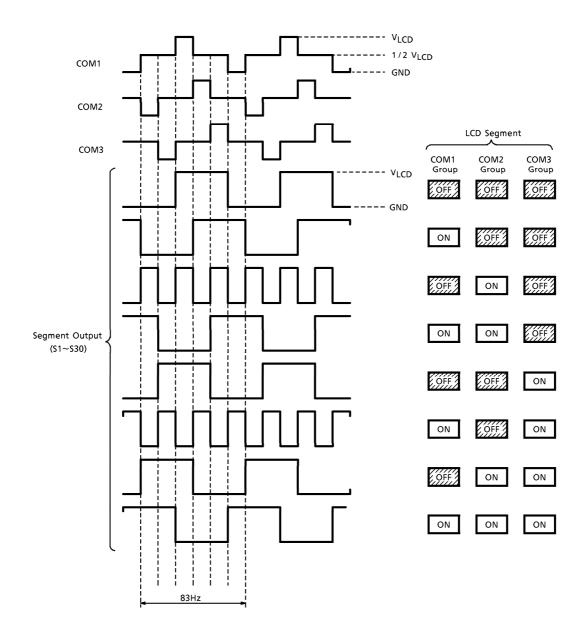

| 1       | COM1                                                               |                                                             | Common output pins for the LCD panel. Can display up to 90 segments in a matrix with S1-S30.                                                                                                                                                                                                                | ☑ VLCD                               |

| 2       | COM2                                                               | LCD common outputs                                          | Three value levels, V <sub>LCD</sub> , 1/2V <sub>LCD</sub> and GND, are output at 2ms intervals at an 83Hz cycle. After system reset or clock stop are                                                                                                                                                      | 1/2V <sub>LCD</sub>                  |

| 3       | сомз                                                               |                                                             | released, 1/2V <sub>LCD</sub> is output, setting the DISP OFF bit to 0 and outputting the common signal.                                                                                                                                                                                                    |                                      |

| 4~21    | S1~S18                                                             | LCD segments outputs                                        | Segment signal output pins for the LCD panel. Together with COM1, COM2 and COM3, a matrix is formed that can                                                                                                                                                                                                | V <sub>LCD</sub>                     |

| 22~25   | S19 / P5-0                                                         | LCD segment<br>outputs /<br>I/O ports                       | display a maximum of 90 segments.  Pins S19~S30 can programmed as I/O  ports.                                                                                                                                                                                                                               | Z <sup>VLCD</sup> <b>₹</b> VDD       |

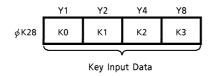

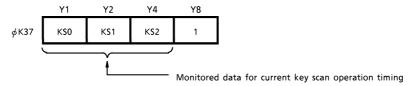

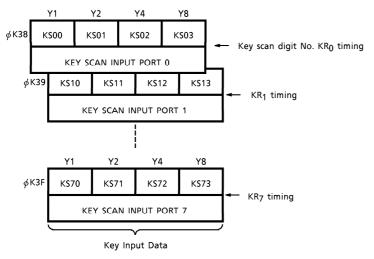

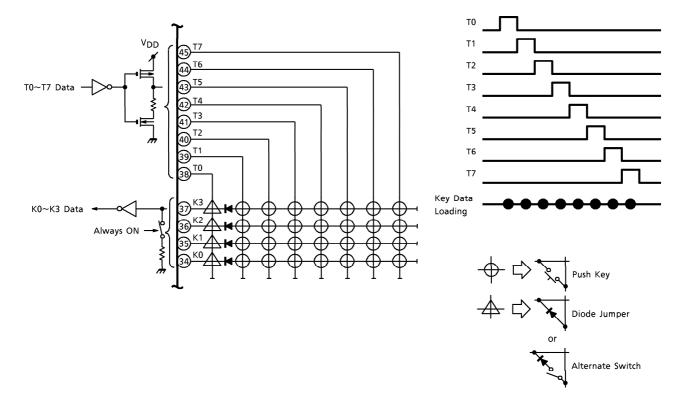

| 26~33   | S23 / P6-0 /<br>KR <sub>7</sub><br>S30 / P7-3 /<br>KR <sub>0</sub> | LCD segment outputs / I/O ports / key return timing outputs | The signals for the key matrix and the segment signals from \$23 / KR7~\$30 / KR0 are output on a time division basis.  4×8=32 key matrix can be configured with key input ports K0~K3.                                                                                                                     | V <sub>DD</sub>                      |

| 34~37   | K0~K3                                                              | Key input ports                                             | 4bit port for key-matrix inputs. In combination with key return timing outputs KR <sub>0</sub> ~KR <sub>7</sub> for the LCD segment pins, these ports support data input for up to 4×8=32 keys. Pull-down resistors are built in.  A key matrix can also be configured using key timing output ports T0~T7. | V <sub>DD</sub>                      |

| 38~45   | T0~T7                                                              | Key timing output ports                                     | Key matrix timing signal output ports. To configure the key matrix, N-channel load resistors are built in. When keys are connected, the matrix diodes can be omitted.                                                                                                                                       | V <sub>DD</sub><br>R <sub>ON</sub> → |

| 46~53   | P1-0<br>{<br>P2-3                                                  | I/O ports 1 and 2                                           | 8bit I/O port. Input or output can be programmed for each bit.                                                                                                                                                                                                                                              | V <sub>DD</sub> V <sub>DD</sub>      |

| PIN No. | SYMBOL                                                                    | PIN NAME                                                                                                              | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REMARKS                         |

|---------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

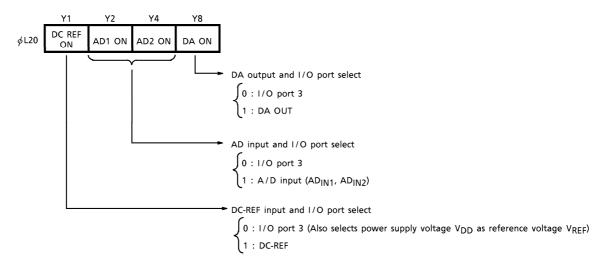

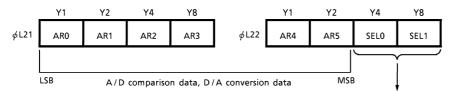

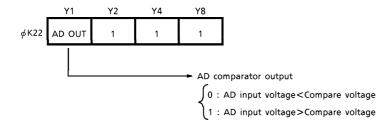

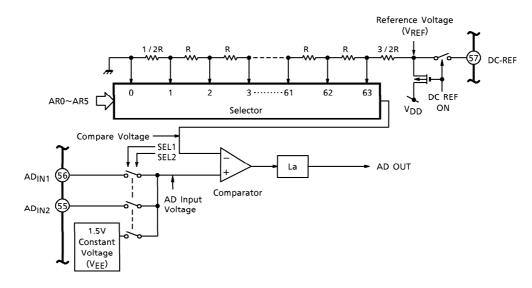

| 54~57   | P3-0 /<br>DAOUT<br>P3-1 /<br>ADIN2<br>P3-2 /<br>ADIN1<br>P3-3 /<br>DC-REF | I/O port 3 /D/A analog voltage output  /A/D analog voltage input  /A/D analog voltage input  /reference voltage input | 4bit I/O port. Input or output can be programmed for each bit. Pins P3-0 through P3-2 serve as the analog inputs and outputs for the built-in A/D and D/A converters. The A/D converter operates by successive comparison method based on software control. Pins can be set to A/D, D/A analog input/output in units of bits as necessary. P3-3 can be set to reference voltage input. Reference voltage can be set to the internal supply voltage (VDD). It is also possible to input VEED to the A/D analog input, enabling measurement of battery voltage and the like. The D/A converter outputs analog voltage through the operating amplifier with shared the comparison voltage generator circuit used by the A/D converter. To share the reference voltage generator circuit with the A/D converter, D/A converter output is set to high impedance during A/D conversion. It is necessary at such times to connect an analog voltage hold capacitor to the D/A output pin. The A/D and D/A converters, as well as their controls, are all programmable. | VDD VDD To A/D or D/A converter |

| PIN No.  | SYMBOL                              | PIN NAME                                                                                    | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | REMARKS                         |

|----------|-------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

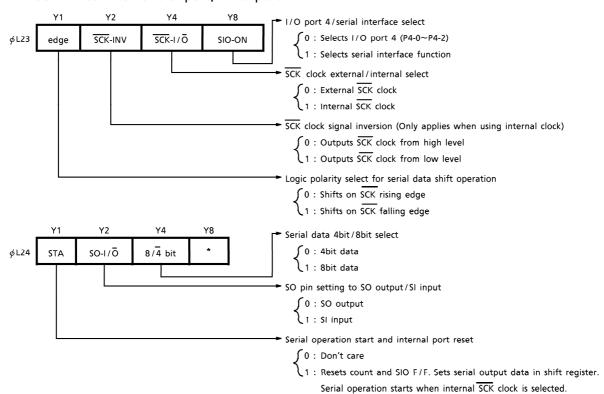

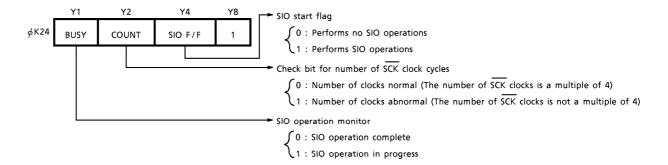

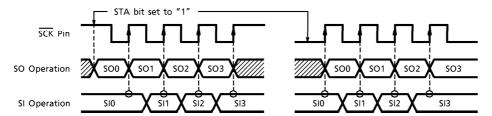

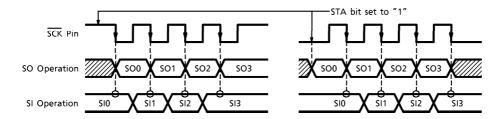

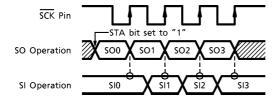

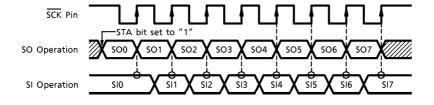

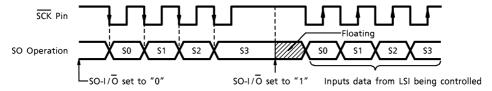

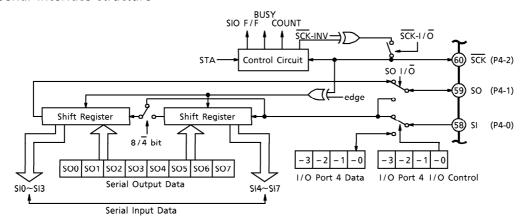

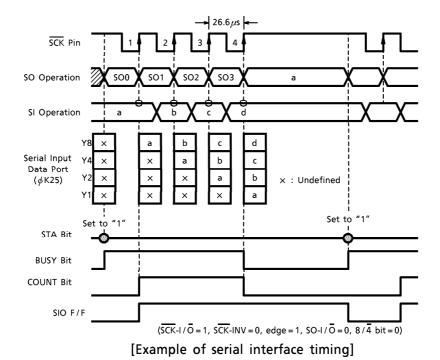

| 58~61    | P4-0 / SI P4-1 / SO P4-2 / SCK P4-3 | I/O port 4  /serial data input  /serial data output  /serial clock input/output  I/O port 4 | 4bit I/O port. Input or output can be programmed for each bit. Pins P4-0 through P4-2 also serve as input/output pins for the serial interface circuit (SIO). SIO inputs 4bit or 8bit serial data at the clock edge of the SCK pin; outputs data from the SO pin. The serial operating clock (SCK) allows selection between internal and external, and between rising and falling clock edge shift. The SO pin can be switched to serial input (SI), facilitating control of a variety of LSIs and communication between controllers. All SIO inputs have built-in Schmittcircuits. All SIOs and their controls can be used or set by program. | V <sub>DD</sub> V <sub>DD</sub> |

| 62       | OT1/BUZR                            | General-purpose<br>output port<br>/buzzer output                                            | 1bit output port that also serves as the built- in buzzer circuit output. Buzzer buzzes in 254 levels from 18.75kHz to 147Hz, with a duty factor of 50%. Buzzer output control can be used or set by program.                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>DD</sub>                 |

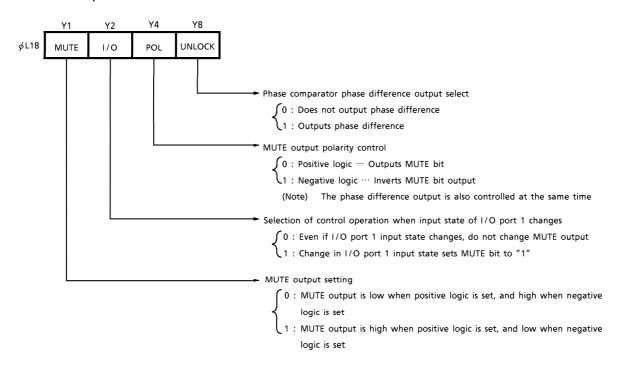

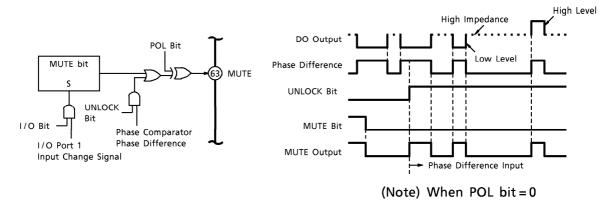

| 63       | MUTE                                | Muting output port                                                                          | 1bit output port. Normally used for output of the muting control signal. It allows the internal MUTE bit to be set to 1 based on I/O port 1 input state. It can also change MUTE bit output logic and output PLL phase differences.                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>DD</sub>                 |

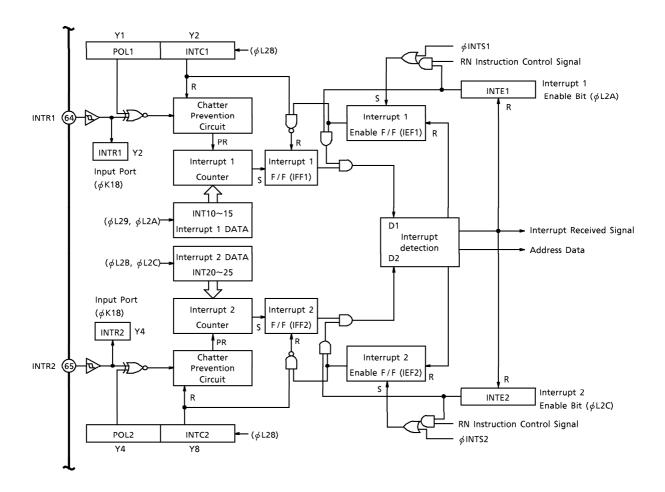

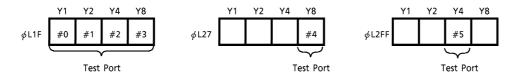

| 64<br>65 | INTR1<br>INTR2                      | External interrupt input                                                                    | External interrupt input pins. Can be used for remote control signal input or tape travel detection input. Can also be programmed as general-purpose input ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u> </u>                        |

| 66       | TEST                                | Test mode control input                                                                     | Input pin for controlling test mode. When the pin is high, test mode; when low, normal operation. Normally used low or in the NC state. (pull-down resistance built in)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>DD</sub>                 |

| PIN No.  | SYMBOL                                             | PIN NAME                       | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REMARKS         |

|----------|----------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

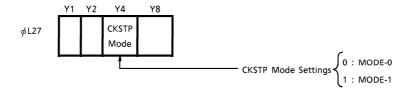

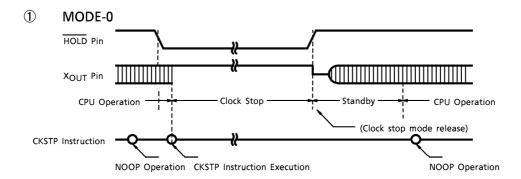

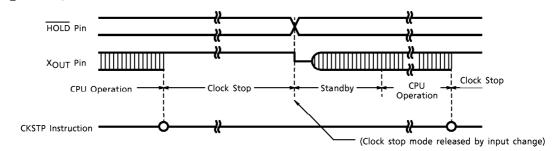

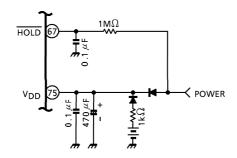

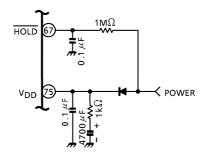

| 67       | HOLD                                               | Hold mode<br>control input     | Input pin used to request/cancel a hold state.  Normally used for the radio mode select signal input or for the battery detection signal input.  Hold states can be either clock stop mode (crystal oscillation stopped) or wait mode (CPU stopped). The mode is set by a CKSTP or WAIT instruction. When CKSTP instruction is executed, the hold state request/cancel differs depending on the internal MODE bit. When the MODE bit is 0 (MODE-0), executing the CKSTP instruction while the HOLD pin is low stops the clock generator and the CPU, and enters memory backup state. When the MODE bit is 1 (MODE-1), executing the CKSTP instruction regardless of whether the HOLD pin is high or low enters memory backup state. This state is canceled in MODE-0 when the HOLD pin changes to high; in MODE-1, when the input at the HOLD pin changes. When a WAIT instruction is executed, the state is cancelled by changes in inputs at this pin.  During memory backup, current consumption is reduced (to 1μA or less) and all output pins (display outputs, output ports, etc.) automatically are set to low. | V <sub>DD</sub> |

| 68<br>69 | IF <sub>IN1</sub> / IN1<br>IF <sub>IN2</sub> / IN2 | IF signal input<br>/input port | IF signal input pin for the IF counter; counts the IF signals for the FM and AM bands and detects autostop. Input frequency is 0.3~12MHz (0.2V <sub>p-p</sub> min). The built-in input amplifier operates at small amplitude withcapacitors connected. The IF counter is a 20bit counter with gate time selectable to 1, 4, 16 or 64 ms, allowing 20 bits of data to be loaded to memory directly. This input pin can be programmed as an input port (IN port). When set to IN port, input is CMOS level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RfIN            |

| PIN No.  | SYMBOL          | PIN NAME                                                       | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REMARKS         |

|----------|-----------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

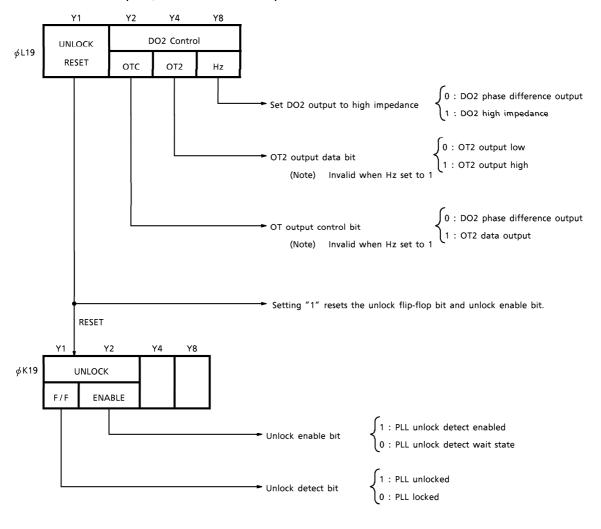

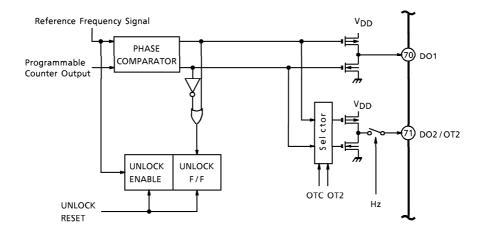

| 70<br>71 | DO1<br>DO2/OT2  | Phase comparator output  Phase comparator output / output port | PLL phase comparator output pin. Tri-state output. When the divider output of the programmable counter is higher than the reference frequency, high level is output; when lower, low level is output. When they accord, the output is at high impedance. DO1 and DO2 are parallel outputs, allowing optimized design of filter constants for both the FM and AM bands. The DO2 pin can also be set to high impedance or as an output port (OT2) by program. Thus these two pins can be used to improve lockup time, or to provide effective use of pins as output ports. | V <sub>DD</sub> |

| 75       | V <sub>DD</sub> | Power supply                                                   | Pin for applying the power supply.  Normally, a V <sub>DD</sub> of 2.7~5.5V is applied during PLL operation. When PLL is stopped, a V <sub>DD</sub> of 1.8~5.5V is applied.  During backup (at execution of the CKSTP instruction), voltage can be reduced to 1.2V. If voltage drops below 1.5V with the CPU in operation, the CPU is stopped to prevent CPU malfunction (stop mode) and is restarted when the voltage reaches 1.5V.  The STOP F/F bit detects whether stop mode is in effect or not, so that initialization or clock modification may                   | V <sub>DD</sub> |

| 72       | GND             | pins                                                           | be programmed as desired.  To detect and control CPU malfunction using an external circuit, stop mode operation can be programmed invalid, at which time all 4 bits of the internal test port are set to 1.  If a voltage of 0V to 1.8V or more is applied to this pin, the system is reset and the program starts from address 0 (power on reset).  (Note) Due to the power on reset operation, use the device with a supply voltage rise time of between 10ms and 100ms.                                                                                               | GND             |

| PIN No. | SYMBOL             | PIN NAME                              | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REMARKS                                        |

|---------|--------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

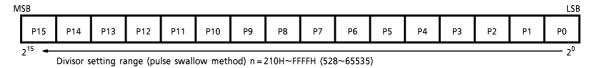

| 73      | FMIN               | FM broadcast<br>signal input          | A programmable counter input pin for the FM band.  Either the 1/2+pulse swallow method (FMH mode) or the pulse swallow method (FML mode) can be selected by program.  In FM mode, a 50 to 130MHz (0.3Vp-pmin) locally oscillated output (VCO output) is input.  The built-in input amplifier operates at small amplitude with capacitors connected.  (Note) In PLL off mode and when AMIN input is set, input is pulled down.                                                                       | R <sub>f</sub> (IN)<br>V <sub>DD</sub>         |

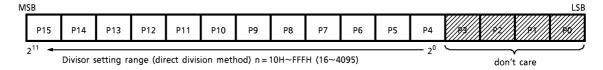

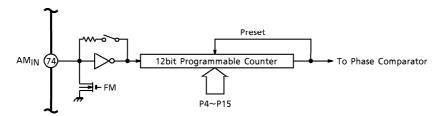

| 74      | AM <sub>IN</sub>   | AM broadcast signal input pin         | A programmable counter input pin for the AM band. Either the pulse swallow method (HF mode) or the direct frequency division method can be selected by program.  In HF mode, a 1 to 60MHz (0.3V <sub>p-p</sub> min) locally oscillated output (VCO output) is input; in LF mode, 0.5 to 10MHz (0.2V <sub>p-p</sub> min).  The built-in input amplifier operates at small amplitude with capacitors connected.  (Note) In PLL off mode and when FM <sub>IN</sub> input is set, input is pulled down. | RfIN VDD                                       |

| 76      | RESET              | Reset input                           | System reset signal input pin. When a reset occurs while RESET is low, the pin is set to high and the program starts from address 0. Normally, if a voltage of 0V to 1.8V or more is supplied to V <sub>DD</sub> , the system is reset (power on reset) so use this pin fixed to high.                                                                                                                                                                                                              | V <sub>DD</sub>                                |

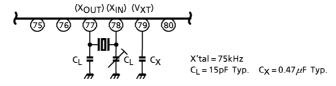

| 77      | X <sub>OUT</sub>   |                                       | Crystal oscillator pin. A 75kHz reference crystal oscillator is                                                                                                                                                                                                                                                                                                                                                                                                                                     | X <sub>OUT</sub> R <sub>f</sub> x <sub>T</sub> |

| 78      | 78 X <sub>IN</sub> | Crystal oscillator<br>pin             | connected to the $X_{IN}$ and $X_{OUT}$ pins. Oscillation stops during execution of a CKSTP instruction. The $V_{XT}$ pin is the power supply for the                                                                                                                                                                                                                                                                                                                                               | V <sub>IN</sub> PE                             |

| 79      | $V_{XT}$           |                                       | crystal oscillator. Connect a capacitor (0.47 $\mu$ F Typ.) for stabilization.                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |

| 80      | V <sub>LCD</sub>   | 3V constant-<br>voltage output<br>pin | 3V constant-voltage output pin for driving the LCDs. Connect a capacitor (1.0 $\mu$ F Typ.) for stabilization.                                                                                                                                                                                                                                                                                                                                                                                      | V.CD V.CD                                      |

(Note 1) When a device is reset (V<sub>DD</sub> from 0V to 1.8V or more, or RESET from low to high), the I/O ports are set to input; the LCD output and I/O port common pins are set to LCD output, the I/O ports and common pins with additional functions (eg, SIO, A/D converter) are set to I/O port input pins; the IF<sub>IN</sub> pin is set to IF input.

- (Note 2) In PLL off mode (all 4 bits of the internal reference port are set to 1), IF<sub>IN</sub> and the FM<sub>IN</sub> and AM<sub>IN</sub> pins are pulled down, and DO1 and DO2 are at high-impedance.

- (Note 3) In clock stop mode (during execution of the CKSTP instruction), output ports and LCD output pins are all set to low. The constant-voltage circuit (V<sub>LCD</sub>) and clock generator power supply (V<sub>XT</sub>) are turned off.

- (Note 4) When a device is reset, the contents of output ports and internal ports are undefined. Therefore, initialize by program as required.

#### **EXPLANATION OF OPERATION**

## ○ CPU

CPU is composed of program counter, stack register, ALU, program memory, data memory, Gregister, carry F/F and judging circuit.

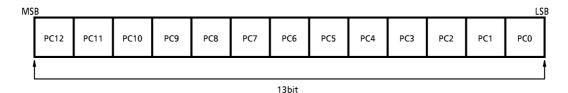

## 1. Program counter (PC)

Program Counter is a block to designate the address of program memory (ROM), and is composed of 13 bits binary up counter. This is cleared by system reset, and the program starts from zero address.

Usually, it's increment is made one by one everytime the one instruction is executed, but when JUMP instruction or CAL instruction is executed, the address designated at operand part of that instruction is loaded.

Further, when the instruction (SLT1, TMT, SKP, RNS instructions, etc.) having skip function is executed, two increments of program counter is made if the result is the condition to be skipped, and the succeeding instruction is skipped.

## 2. Stack register (STACK)

This is a register composed of 4x13 bits during the execution of subroutine call instruction, the

housed. The content of stack register is loaded on the program counter by the execution of return instruction. (RN, RNS instructions)

This stack level is 4 level, and nesting is 4 level.

#### 3. ALU

ALU has binary 4 bits parallel addition and subtraction, logical operation, comparison and plural bit judge functions.

This CPU has no accumulator, and all operations directly treat the contents of data memory.

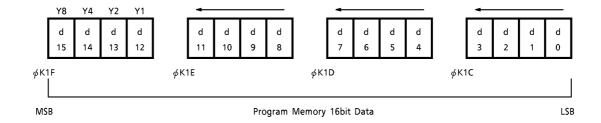

## 4. Program memory (ROM)

Program memory is composed of 16bit × 6144 steps and is the address of 0000H~17FFH.

Program memory has no concept of page or field, so JUMP instruction and CAL instruction can be freely used among 6144 steps.

Further, it is possible to use optional address of program memory as data area, and its content, 16 bits, can be loaded to the data register by executing DAL instruction.

- (Note) Provide the data area at the address outside the program loop in the program memory.

- (Note) In DAL instruction, the address of program memory can be designated as the data area becomes 1024 steps of 0000H~03FFH.

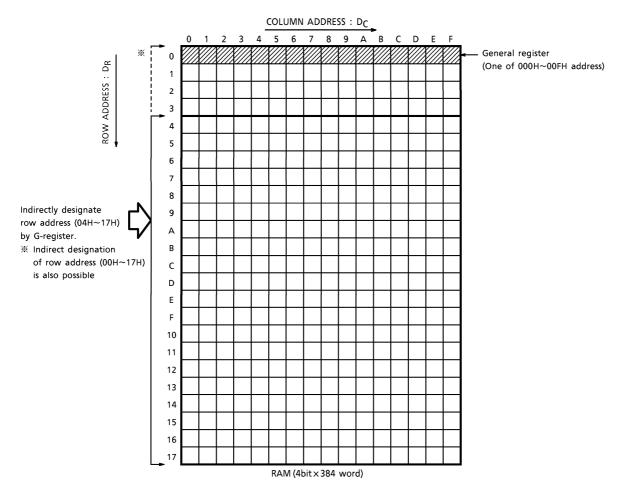

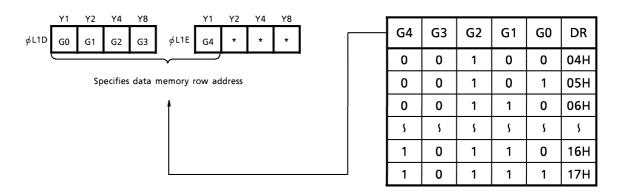

#### 5. Data memory (RAM)

Data memory is composed of 4bit × 384 words and used for storing data. This 384 words are expressed with row address (5 bits) and column address (4 bits). 320 words (row address = 04H~17H) among the data memory are indirect addressing by Gregister. For this reason, when carrying out data processing within this territory, it is necessary to designate row address by G-register beforehand Area of 000H~00FH address in data memory is called general register, and can be used only by designating column address (4 bits). These 16 general registers can be used for operation and transfer between data memories. Further, it can also be used as ordinary data memory.

- (Note) The column address (4 bits) to designate general register becomes register number of the general register.

- (Note) It is also possible to indirectly designate all of row address (=  $00H\sim17H$ ) by G-register.

- (Note) 256 words (row address = 00H~0FH) among the data memory are direct addressing by LD or ST instructions.

#### 6. G-register (G-REG.)

G-register is a 5 bits register for addressing row address ( $D_R = 04H \sim 17H$ ) of 320 words in data memory.

Content of this register is effective during executing MVGD instruction, MVGS instruction, and is not related with the execution of other instructions.

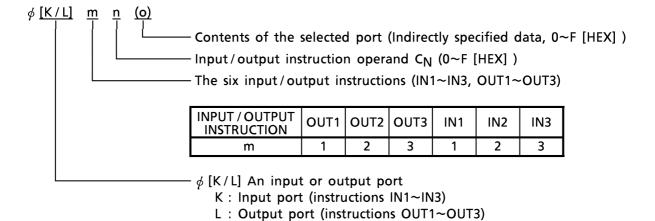

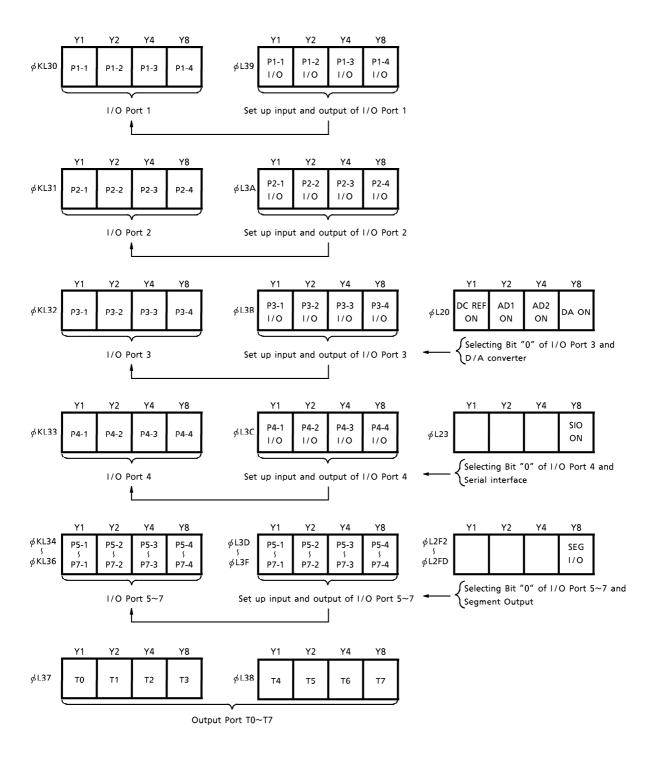

This register is treated as one of the port, and its content is set by the execution of OUT1 instruction among input and output instructions.

(refer to register port item 1)

Content of this register can directly setting by the execution STIG instruction.

## 7. Data register (DATA REG.)

This is a register composed of 1×16 bits. In this register, 16 bits data of optional address among the program memory is loaded during executing of DAL instruction. This register is treated as one of the port, and when KEY instruction among input and output instruction is executed, it's content is read in the data memory in 4 bits unit. (refer to register port item 2 page 39)

## 8. Carry F/F (C·F/F)

This is set when carry or borrow is produced as a result of executing operational instruction, and is reset when it is not produced. Content of carry F/F changes only when addition and subtraction instruction is executed, and does not change during the execution of other instructions.

# 9. Judging circuit (J)

When a instruction with skip function is executed, this circuit judges it's skip condition. When skip condition is satisfied, this circuit makes two increments of program counter, and skips the succeeding instruction.

It is provided with 15 kinds of instructions having abundant skip function. (refer to Item 11, explanation list of function and operation of instructions, % marked instruction)

#### 10.List of instruction set

54 kinds of instruction set are included, all of which consisting of one word instruction. These instructions are expressed with 6 bits instruction code.

| Higher<br>Lower |        | 00         | 0        | )1     | 10                     | 11                        |

|-----------------|--------|------------|----------|--------|------------------------|---------------------------|

| Rank 4 bits     | 2 bits | 0          |          | 1      | 2                      | 3                         |

| 0000            | 0      | Al M, I    | TMTR     | r, M   |                        | SLTI M, I                 |

| 0001            | 1      | AIC M, I   | TMFR     | r, M   |                        | SGEI M, I                 |

| 0010            | 2      | SI M, I    | SEQ      | r, M   |                        | SEQI M, I                 |

| 0011            | 3      | SIB M, I   | SNE      | r, M   | CALL ADDR <sub>1</sub> | SNEI M, I                 |

| 0100            | 4      | ORIM M, I  |          |        |                        | TMTN M, N                 |

| 0101            | 5      | ANIM M, I  | <b>—</b> |        |                        | TMT M, N                  |

| 0110            | 6      | XORIM M, I | LD       | r, M*  |                        | TMFN M, N                 |

| 0111            | 7      | MVIM M, I  |          |        |                        | TMF M, N                  |

| 1000            | 8      | AD r, M    |          |        |                        | IN1 M, C                  |

| 1001            | 9      | AC r, M    |          | a a.t. |                        | IN2 M, C                  |

| 1010            | Α      | SU r, M    | ST       | M*, r  |                        | IN3 M, C                  |

| 1011            | В      | SB r, M    |          |        |                        | OUT1 C, M                 |

| 1100            | С      | ORR r, M   | CLT      | r, M   |                        | OUT2 C, M                 |

| 1101            | D      | ANDR r, M  | CLTC     | r, M   |                        | OUT3 C, M                 |

| 1110            | Е      | XORR r, M  | MVGD     | r, M   | JUMP ADDR <sub>1</sub> | DAL ADDR <sub>2</sub> , r |

|                 |        |            |          |        | ]                      | SHRC M                    |

|                 |        |            |          |        |                        | RORC M                    |

|                 |        |            |          |        |                        | STIG I*                   |

|                 |        |            |          |        |                        | SKP, SKPN, RN,            |

| 1111            | F      | MVSR M1, N | /12 MVGS | M, r   |                        | RNS                       |

|                 |        |            |          |        |                        | WAIT P                    |

|                 |        |            |          |        |                        | SKSTP                     |

|                 |        |            |          |        |                        | XCH M                     |

|                 |        |            |          |        |                        | NOOP                      |

11. Explanation list of function and operation of instructions (Explanation of symbols)

M : Data memory address

Normally, one of 000H~03FH address of data memory.

M\* : Data memory address (256 word)

One of 000H~0FFH address of data memory (Available at executing ST and

LD instruction)

r : General register

One of 00H~0FH address of data memory.

PC : Program counter (13bit)

STACK : Stack register (13bit)

G : G-register (5bit)

DATA : Data register (16bit)

I : Immediate data (4bit)

I\* : Immediate data (5bit)

N : Bit position (4bit)

— : All "0"

C : Code No. of port (4bit)

C<sub>N</sub>: Lower rank 3bit of port code No. (4bit)

R<sub>N</sub> : General register No. (4bit)

ADDR<sub>1</sub> : Program memory address in page 0 or 1 (13bit)

ADDR<sub>2</sub> : Higher rank 6bit of program memory address in page 0

Ca : Carry b : Borrow

IN1~IN3 : Port treated during the execution IN1~IN3 instruction

OUT1~OUT3 : Port treated during the execution OUT1~OUT3 instruction

: Register or data memory content

[ ]<sub>C</sub> : Content of port indicated by code No. C (4bit)

[ ] : Content of data memory indicated by the content of register or data memory

[ ]p : Content of program memory (16bit)

IC : Instruction code (6bit)

Instruction having skip function

DC : Data memory column address (4bit)

DR : Data memory row address (2bit)

DR\* : Data memory row address (4bit) (Available at executing ST and LD

instruction)

(M)  $b0\sim$ (M) b3: Bit data for content of data memory

| Ŀ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |       | N<br>0          | EVEL ANATION OF                                                 | EVELANATION OF           | МАСНІ        | NE LAN         | GUAGE                                     | (16bit)        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------|-----------------------------------------------------------------|--------------------------|--------------|----------------|-------------------------------------------|----------------|

| INST<br>GR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MNEM | MONIC | SK I P<br>FUNCT | EXPLANATION OF FUNCTION                                         | EXPLANATION OF OPERATION | IC<br>(6bit) | A<br>(2bit)    | B (4bit) DC | C<br>(4bit)    |

| Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ΑI   | M, I  |                 | Add immediate data to memory                                    | M←(M) +I                 | 000000       | D <sub>R</sub> | DC                                        | I              |

| ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AIC  | M, I  |                 | Add immediate data to memory with carry                         | M←(M) +I+ca              | 000001       | D <sub>R</sub> | DC                                        | I              |

| TRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AD   | r, M  |                 | Add memory to general register                                  | r← (r) + (M)             | 001000       | D <sub>R</sub> | DC                                        | R <sub>N</sub> |

| SUBTRACTION ADDITION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION INSTRUCTION IN INSTRUCTION | AC   | r, M  |                 | Add memory to general register with carry                       | r←(r) + (M) + ca         | 001001       | D <sub>R</sub> | DC                                        | R <sub>N</sub> |

| CT 10N<br>ICT 10N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SI   | M, I  |                 | Subtract immediate data from memory                             | M←(M) –I                 | 000010       | D <sub>R</sub> | DC                                        | I              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SIB  | М, І  |                 | Subtract immdediate data from memory with borrow                | M← (M) – I – b           | 000011       | D <sub>R</sub> | DC                                        | I              |

| BTR/<br>STRI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SU   | r, M  |                 | subtract memory form general register                           | r← (r) – (M)             | 001010       | D <sub>R</sub> | DC                                        | R <sub>N</sub> |

| N N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SB   | r, M  |                 | subtract memory form<br>general register with<br>borrow         | r←(r) - (M) - b          | 001011       | D <sub>R</sub> | DC                                        | R <sub>N</sub> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SLTI | M, I  | *               | Skip if memory is less than immediate data                      | Skip if (M) <1           | 110000       | D <sub>R</sub> | DC                                        | I              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SGEI | М, І  | *               | Skip if memory is<br>greater than or equal<br>to immediate data | Skip if (M) ≧ I          | 110001       | D <sub>R</sub> | DC                                        | I              |

| NO<br>NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SEQI | М, І  | *               | Skip if memory is equal to immediate data                       | Skip if (M) = I          | 110010       | D <sub>R</sub> | D <sub>C</sub>                            | I              |

| OM PAR I SON<br>NS TRUCT I ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SNEI | М, І  | *               | Skip if memory is not equal to immediate data                   | Skip if (M) ≠ I          | 110011       | D <sub>R</sub> | DC                                        | I              |

| COM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SEQ  | r, M  | *               | Skip if general register is equal to memory                     | Skip if $(r) = (M)$      | 010010       | D <sub>R</sub> | DC                                        | R <sub>N</sub> |