# CDB Device Cell Delineation Block TXC-05150

DATA SHEET

Preliminary

### **FEATURES I**

- ATM cell delineation per ITU I.432

- · ATM cell rate adaptation

- Selectable cell output: FIFO, SARA, and UTOPIA (Universal Test & Operations Physical Interface for ATM)

- Identifies OAM F4 cells and non-user cells

- Operation from 1.544 Mbit/s to 155.52 Mbit/s

- Programmable interfaces to DS1, DS3, E1, STS-1, STS-3c, and STM-1

- DS3 interface with HEC-based mapping of ATM cells

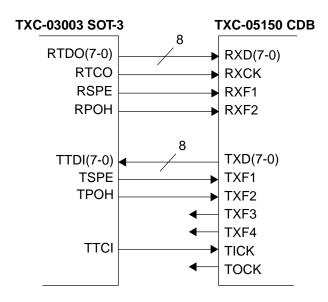

- Interfaces with TranSwitch SOT-1, SOT-3, DS3F, JT2F and the SARA ATM chipset

- 0.7 μm low power CMOS technology

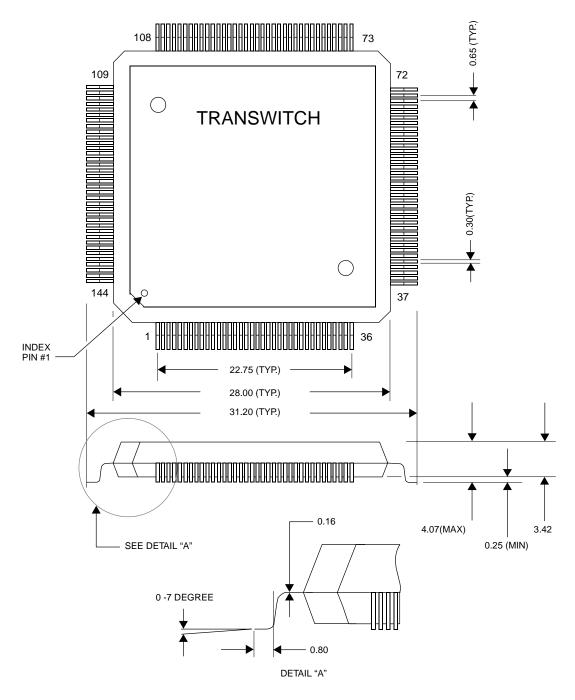

- 144-pin plastic quad flat pack (PQFP)

- IEEE 1149.1 boundary scan

### DESCRIPTION

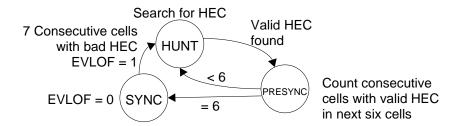

The Cell Delineation Block (CDB) is an ATM cell interface device. The CDB function is to extract ATM cells from, and insert ATM cells into, a line interface signal having one of several possible transmission formats. This function corresponds to portions of the Transmission Convergence (TC) sublayer and the ATM Layer in the BISDN Protocol Reference Model. Specifically, cell delineation is performed by means of a Header Error Control (HEC) byte search. Cell rate adaptation is also performed by generating and terminating unassigned ATM cells of a specified format.

The CDB also supports a limited cell address screening function. A programmable VPI/VCI number register and VPI/VCI mask register are provided. Each incoming cell with address matching in all VPI/VCI bit positions which are not masked will generate an "Address Match" indication.

### **APPLICATIONS I**

- ATM switch interfaces

- ATM terminal adapters

- Cell multiplexers

- Routers and bridges

Copyright © 1994 TranSwitch Corporation TXC and TranSwitch are registered trademarks of TranSwitch Corporation

Document Number: TXC-05150-MB Ed. 4, October 1994 **PRELIMINARY** information documents contain information on products in the sampling, pre-production or early production phases of the product life cycle. Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

# **TABLE OF CONTENTS**

| SECTION                               | <u>PAGE</u> |

|---------------------------------------|-------------|

| Block Diagram                         | 3           |

| Block Diagram Description             | 3-4         |

| Pin Diagram                           |             |

| Pin Descriptions                      |             |

| Absolute Maximum Ratings              | 11          |

| Thermal Characteristics               | 11          |

| Power Requirements                    | 11          |

| Input, Output And I/O Parameters      | 12          |

| Timing Characteristics                | 13-34       |

| Operation                             | 35-56       |

| Internal Device Operations            | 35          |

| Receive                               | 35          |

| Transmit                              | 40          |

| Line And Terminal External Operations | 42          |

| Control                               | 49          |

| Testing                               | 50          |

| Initialization                        | 50          |

| Control Bit And Register Memory Map   | 51          |

| Control Bit And Register Descriptions |             |

| Packaging                             | 57          |

| Ordering Information                  | 58          |

| Related Products                      | 58          |

| Standards Documentation Sources       | 59          |

| List Of Data Sheet Changes            | 60-62       |

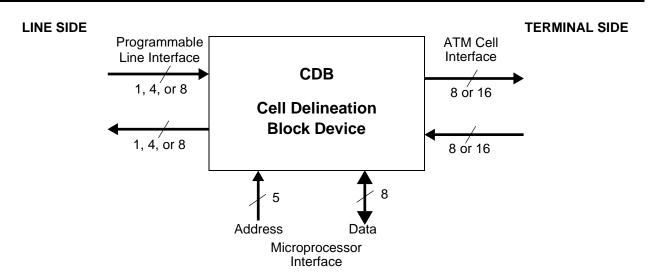

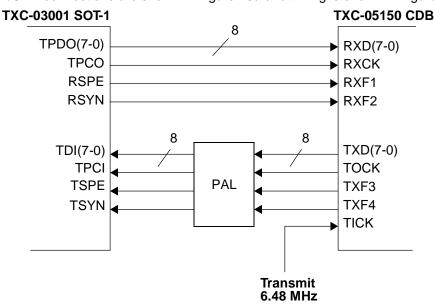

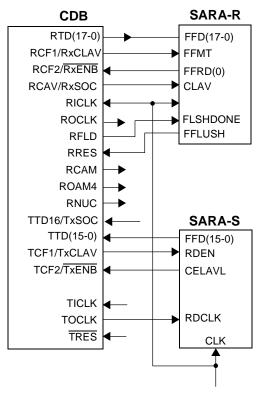

### **BLOCK DIAGRAM**

Figure 1. CDB Block Diagram

### **BLOCK DIAGRAM DESCRIPTION**

#### **Receive Path**

The Cell Delineation Block (CDB) block diagram is shown in Figure 1. The receive line interface of the CDB accepts data from the line in one of several formats. The device then finds cell framing by searching for a valid Header Error Control (HEC) sequence. The extracted cells are optionally descrambled and passed to the cell output formatter which can interface to an ATM switch, cell bus, or adaptation layer functionality. Performance counters maintain counts of busy cells received. Idle cells are identified and may be dropped. Incoming cell headers are checked for the presence of either an OAM F4 flow cell or a non-user cell (e.g., OAM F5 flow cell). An OAM F4 flow cell is defined by a VCI value equal to either 3 decimal or 4 decimal. An OAM F5 cell is defined as a cell with the MSB of the 3-bit Payload Type Indication (PTI) field set to "1".

The CDB also provides a limited cell address screening function. A 28-bit programmable VPI/VCI number register and VPI/VCI mask register are provided. Each incoming cell with address matching in all VPI and VCI bit positions which are not masked out will generate an address match indication.

### **Transmit Path**

The ATM terminal passes cells to the cell input block to be transmitted through the line interface. The device counts busy cells and generates idle cells to adapt the cell rate to the line interface. The 48-byte cell payload may optionally be scrambled and a HEC byte calculated prior to sending the cell to the transmit line interface.

#### Line Interface

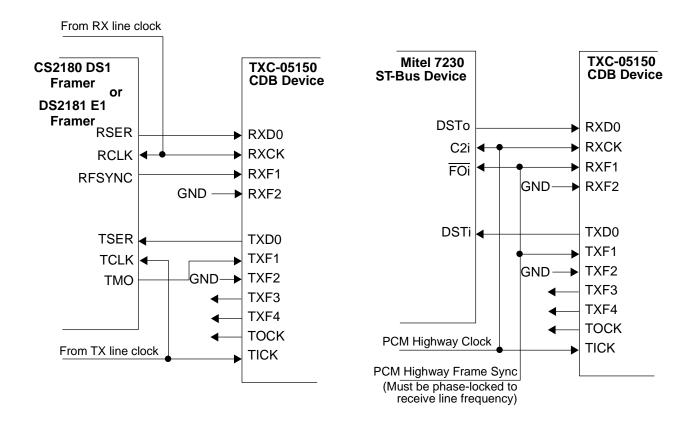

The CDB supports cell delineation and cell rate adaptation with the following line rates and associated line framing devices:

| Transmission Standard | Line Rate     | Interface Device                      |

|-----------------------|---------------|---------------------------------------|

| STS-3c, STM-1         | 155.52 Mbit/s | TXC-03003 (SOT-3)                     |

| STS-1                 | 51.840 Mbit/s | TXC-03001 (SOT-1)                     |

| DS3                   | 44.736 Mbit/s | TXC-03401 (DS3F, direct mapping only) |

| DS1                   | 1.544 Mbit/s  | Various standard devices              |

| E1                    | 2.048 Mbit/s  | Various standard devices              |

The CDB also supports alternate physical interfaces at different rates, having byte, nibble parallel, or bit serial inputs and byte alignment.

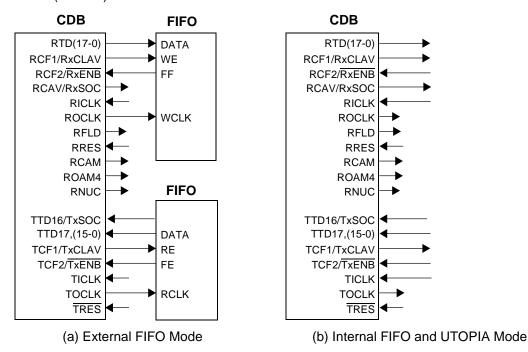

#### **Cell Interface**

Cells are transferred between the CDB and a terminal device in one of four modes:

| External FIFO | Supports the use of external synchronous FIFO for both the cell output formatter and the cell input.                      |

|---------------|---------------------------------------------------------------------------------------------------------------------------|

| Internal FIFO | The CDB internally emulates synchronous FIFO, both on the cell output formatter and the cell input.                       |

| SARA          | Direct connection to the TranSwitch SARA ATM/AAL chipset.                                                                 |

| UTOPIA        | The CDB supports a fully compliant UTOPIA interface on the cell I/O. This includes timing standards and pin designations. |

The cell output formatter includes control signals for cell timing as well as indicators for special cell types. OAM F4 flow cells are output with a ROAM4 indication. Non-user cells are output with a RNUC indication. Cells matching the programmed VPI/VCI value or range of values are output with a RCAM indication. The cell output formatter and cell input data lines can be configured for either 8-bits or 16-bits wide to interface with various ATM/AAL circuitry.

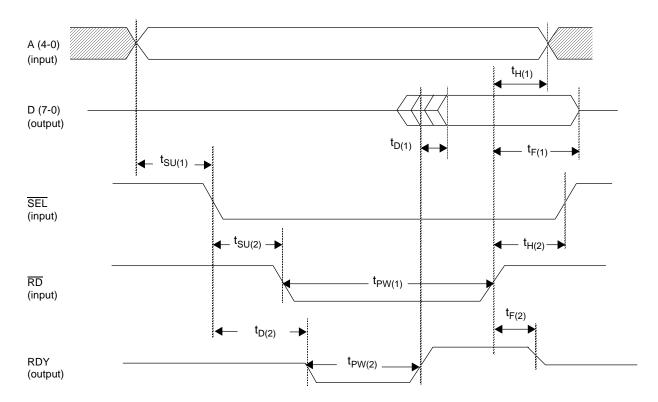

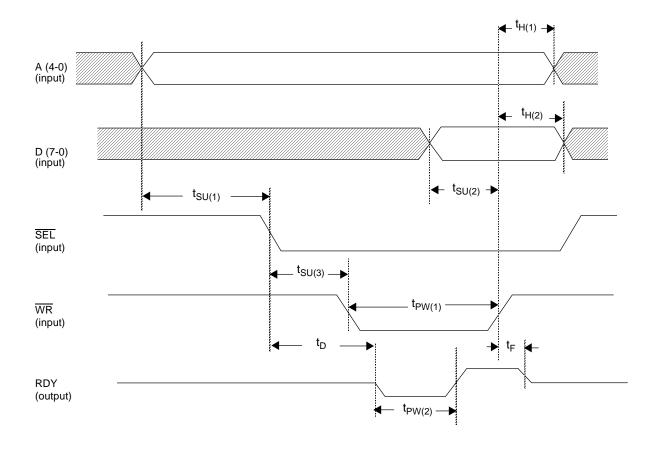

### **Microprocessor Interface**

Access to the CDB registers is provided by the microprocessor interface consisting of an 8-bit data bus, 5-bit address bus, and control signals. The interface can be configured for Intel or Motorola processors, and it uses an independent processor clock for the interface.

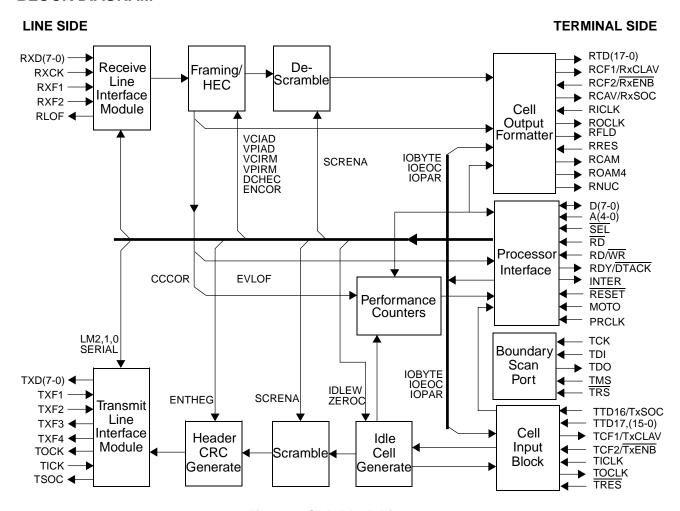

### **PIN DIAGRAM**

Figure 2. CDB Pin Diagram With Names and Numbers

# **PIN DESCRIPTIONS**

## **Power Supply and Ground:**

| Symbol | Pin No.                                                                                 | I/O/P* | Туре | Name/Function            |

|--------|-----------------------------------------------------------------------------------------|--------|------|--------------------------|

| VDD    | 7, 16, 23, 32,<br>41, 50, 58, 65,<br>72, 78, 86, 94,<br>102, 110, 116,<br>124, 132, 140 | Р      |      | VDD: +5-volt supply, ±5% |

| GND    | 12, 20, 27, 36,<br>46, 54, 62, 68,<br>75, 82, 90, 98,<br>106, 113, 120,<br>128, 136,144 | Р      |      | Ground.                  |

<sup>\*</sup>Note: I = Input; O = Output; P = Power

## **Microprocessor Interface**

| Symbol                     | Pin No.                 | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                           |

|----------------------------|-------------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| МОТО                       | 1                       | I     | TTL    | <b>Motorola/Intel Processor Select:</b> = 1 selects Motorola mode, = 0 selects Intel mode.                                                                                                                                                                                                                              |

| A(3-0)<br>A4               | 6-3<br>8                | I     | TTL    | <b>Address Bus:</b> Read/write address for microprocessor interface.                                                                                                                                                                                                                                                    |

| SEL                        | 9                       | I     | TTL    | <b>Select:</b> A low enables data transfers between the microprocessor and the CDB RAM during a read/write cycle.                                                                                                                                                                                                       |

| RD/WR                      | 10                      | I     | TTL    | Read/Write (Motorola Mode) or Write (Intel mode): Motorola Mode - An active high signal generated by the microprocessor for reading the RAM locations. An active low signal is used to write to RAM locations.  Intel Mode - An active low signal generated by the microprocessor for writing to the CDB RAM locations. |

| RD                         | 11                      | I     | TTL    | Read (Intel mode): An active low signal generated by the microprocessor for reading the RAM locations.                                                                                                                                                                                                                  |

| D(2-0)<br>D(5-3)<br>D(7-6) | 15-13<br>19-17<br>22-21 | I/O   | TTL    | Data Bus: Data in or out. These bidirectional data lines are used to transfer data between the CDB and the microprocessor.                                                                                                                                                                                              |

<sup>\*</sup>See Input, Output and I/O Parameters section below for Type definitions.

| Symbol        | Pin No. | I/O/P | Туре               |                                                                                                                         | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | lame/Function                                                                                                                                                                                                                                                                        |

|---------------|---------|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY/<br>DTACK | 24      | 0     | CMOS<br>Open drain | ment (Moto<br>Intel Mode<br>addressed in<br>pleted. A lo<br>the transfer<br>be generate<br>Motorola Mo<br>indicates the | rola moder - A high<br>RAM locative indicative cycle, and d.<br>bode - Duler informaticycle, a locative informaticycle, a locative recommendative r | or Data Transfer Acknowledg-de):  is an acknowledgment from the ation that the transfer can be complete that the CDB cannot complete and microprocessor wait states must ring a read bus cycle, a low signal tion on the data bus is valid. During ow signal acknowledges the accep- |

| INTER         | 25      | 0     | CMOS4mA            |                                                                                                                         | <u>de</u> - active<br><u>Mode</u> - a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                      |

| RESET         | 35      | I     | TTL                | resets the mance coul                                                                                                   | processo<br>nters to<br>eset of th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | second (minimum) low on this pin<br>r interface and clears the perfor-<br>zero. Reset provides a complete<br>ne CDB, except for the boundary<br>elow).                                                                                                                               |

| PRCLK         | 2       | I     | TTL                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ocal clock for microprocessor bus um clock speed is 20 MHz.                                                                                                                                                                                                                          |

| SMODE0        | 73      | I     | TTL                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | : The connection of these pins to                                                                                                                                                                                                                                                    |

| SMODE1        | 74      | I     | TTL                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | o) sets the operating mode of the following table:                                                                                                                                                                                                                                   |

|               |         |       |                    | SMODE<br>1                                                                                                              | SMODE<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interface Mode                                                                                                                                                                                                                                                                       |

|               |         |       |                    | 0                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External FIFO mode. CDB writes (RX side) and reads (TX side) cells to external synchronous FIFO.                                                                                                                                                                                     |

|               |         |       |                    | 0                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Internal FIFO mode. CDB RX FIFO is read (RX) or written (TX) as a synchronous FIFO.                                                                                                                                                                                                  |

|               |         |       |                    | 1                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UTOPIA mode.                                                                                                                                                                                                                                                                         |

|               |         |       |                    | 1                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Direct SARA interface mode.                                                                                                                                                                                                                                                          |

# **Line Input**

| Symbol               | Pin No.        | I/O/P | Туре | Name/Function                                                                                                                                 |

|----------------------|----------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| RXD(3-0)<br>RXD(7-4) | 40-37<br>45-42 | I     |      | Receive Line Data Input: Line input bit serial data (DS1/E1, RXD0), nibble data (DS3, RXD(3-0)), byte data (STS-1 or STS-3c/STM-1, RXD(7-0)). |

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                   |

|--------|---------|-------|---------|-------------------------------------------------------------------------------------------------|

| RXF1*  | 47      | I     | TTL     | Receive Line Frame Indication 1: RSPE if SOT-3 or SOT-1 Frame sync if DS3 Frame sync if DS1/E1. |

| RXF2*  | 48      | I     | TTL     | Receive Line Frame Indication 2:<br>RPOH if SOT-3<br>RSYN if SOT-1.                             |

| RXCK   | 49      | I     | TTL     | Receive Line Clock in: Line input clock.                                                        |

| RLOF   | 51      | 0     | CMOS4mA | Receive Line Loss of Frame: High if loss of cell synchronization.                               |

<sup>\*</sup> Note: Tie to ground or VDD if not used.

# **Line Output**

| Symbol                           | Pin No.                 | I/O/P | Туре    | Name/Function                                                                                                                                        |

|----------------------------------|-------------------------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOCK                             | 52                      | 0     | CMOS4mA | Transmit Line Output Clock: Transmit output clock for SOT-1.                                                                                         |

| TSOC                             | 53                      | 0     | CMOS4mA | Transmit Start of Cell Indication: High during first byte of a transmitted cell.                                                                     |

| TXD(2-0)<br>TXD(5-3)<br>TXD(7-6) | 57-55<br>61-59<br>64-63 | 0     | CMOS4mA | <b>Transmit Line Data Out:</b> Line output bit serial data (DS1/E1, TXD0), nibble data (DS3, TXD(3-0)), byte data (STS-1 or STS-3c/STM-1, TXD(7-0)). |

| TXF3                             | 66                      | 0     | CMOS4mA | Transmit Line SPE Indication: TSPE for SOT-1.                                                                                                        |

| TXF4                             | 67                      | 0     | CMOS4mA | Transmit Line SYN Indication:<br>TSYN (C1J1) for SOT-1.                                                                                              |

| TXF1*                            | 69                      | I     | TTL     | Transmit Line Frame Indication: Transmit TSPE if SOT-3 Transmit frame if DS3 Transmit frame if DS1/E1.                                               |

| TXF2*                            | 70                      | I     | TTL     | Transmit Line POH Indication: Transmit TPOH if SOT-3.                                                                                                |

| TICK                             | 71                      | I     | TTL     | Transmit Line REF Clock: Input clock for transmit side data output.                                                                                  |

<sup>\*</sup> Note: Tie to ground or VDD if not used.

# **Cell Output**

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                        |

|--------|---------|-------|---------|--------------------------------------------------------------------------------------|

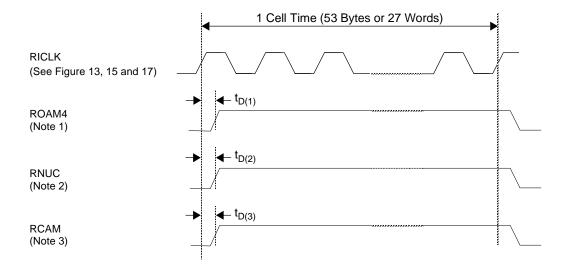

| ROAM4  | 107     | 0     | CMOS4mA | Receive Terminal OAM F4 Indication: High during entire cell if OAM F4 flow cell.     |

| RNUC   | 108     | 0     |         | Receive Terminal Non-user Indication: High during entire cell if non-user type cell. |

| Symbol                                                                    | Pin No.                                                        | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------|----------------------------------------------------------------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCAM                                                                      | 109                                                            | 0     | CMOS4mA | Receive Cell Address Match Indication: High during entire cell, if both VPI and VCI values are declared matched.                                                                                                                                                                                                                                         |

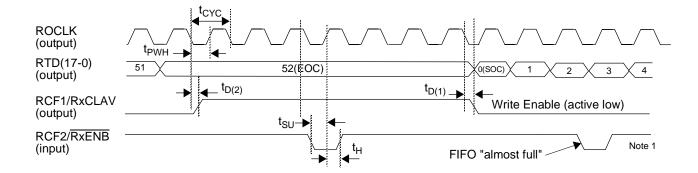

| ROCLK                                                                     | 111                                                            | 0     | CMOS4mA | Receive Terminal Clock Output: Output clock in external FIFO mode.                                                                                                                                                                                                                                                                                       |

| RFLD                                                                      | 112                                                            | 0     | CMOS4mA | Receive Terminal Flush Indication: Flush done to SARA-R.                                                                                                                                                                                                                                                                                                 |

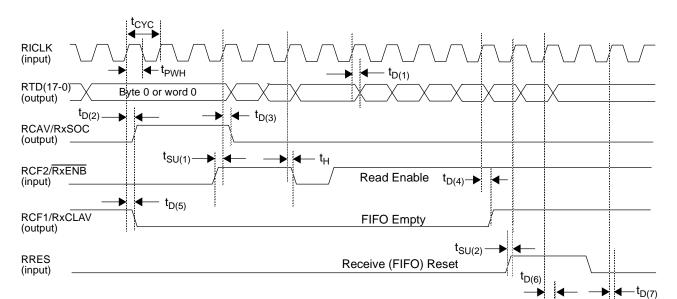

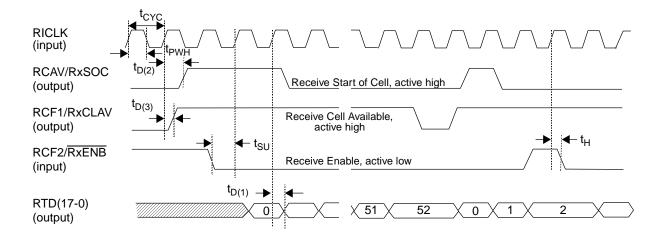

| RCAV/<br>RxSOC                                                            | 114                                                            | 0     | CMOS4mA | Receive Terminal Cell Available Indication: Cell available in SARA mode, Receive Start of Cell in UTOPIA mode.                                                                                                                                                                                                                                           |

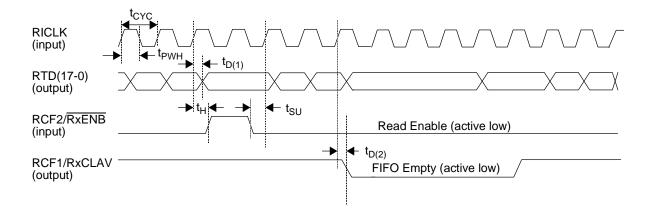

| RCF1/<br>RxCLAV                                                           | 115                                                            | 0     | CMOS4mA | Receive Terminal Control Line 1: Write enable if external FIFO mode (RCF1 active low) FIFO empty if internal FIFO mode (RCF1 active low) FIFO empty if SARA mode (RCF1 active high) Complete cell available for transfer in UTOPIA mode (RxCLAV active high).                                                                                            |

| RTD(2-0)<br>RTD(5-3)<br>RTD(8-6)<br>RTD(11-9)<br>RTD(14-12)<br>RTD(17-15) | 119-117<br>123-121<br>127-125<br>131-129<br>135-133<br>139-137 |       | CMOS4mA | Receive Terminal Data Out: Received data and parity. In the byte mode, RTD (7-0) are data and RTD (8) is an even parity / start of cell indicator. In the word mode, RTD (15-0) are data and RTD (17,16) are even parity / start of cell indicators. If the UTO-PIA mode is active, odd parity is provided, but start of cell is on pin 114, RCAV/RxSOC. |

| RICLK                                                                     | 141                                                            | I     | TTL     | Receive Input Clock: Read FIFO input clock. Its maximum frequency is 20 MHz.                                                                                                                                                                                                                                                                             |

| RCF2/<br>RxENB                                                            | 142                                                            | I     | TTL     | Receive Terminal Control Line 2: FIFO almost full input if external FIFO mode (RCF2 active low) Read enable input if internal FIFO mode (RCF2 active low) Read enable from SARA-R if SARA mode (RCF2 active high) Read enable in UTOPIA mode (RXENB active low).                                                                                         |

| RRES                                                                      | 143                                                            | I     | TTL     | Receive Terminal Reset: Receive side cell reset clears the output FIFO. It must be high for at least 100 nanoseconds.                                                                                                                                                                                                                                    |

# **Cell Input**

| Symbol          | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                 |

|-----------------|---------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

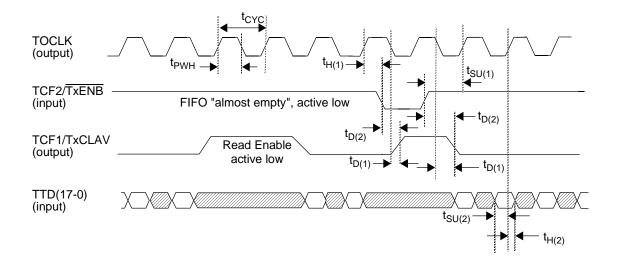

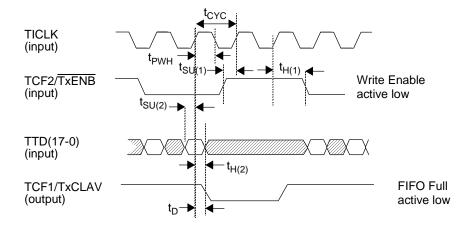

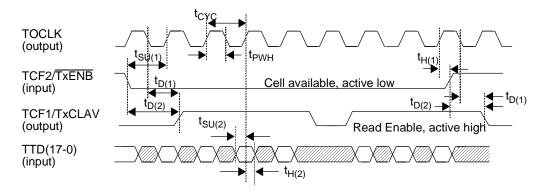

| TCF1/<br>TxCLAV | 76      | 0     | CMOS4mA | Transmit Terminal Control Line 1: Read enable output, external FIFO mode (TCF1 active low) FIFO full output, internal FIFO mode (TCF1 active low) RDEN to SARA-S in SARA mode (TCF1 active high) Transmit Cell Available in UTOPIA mode (TxCLAV active high). |

| TOCLK           | 77      | 0     | CMOS4mA | <b>Transmit Terminal Clock Output:</b> Read clock for external FIFO and SARA modes. Maximum frequency is 20 MHz.                                                                                                                                              |

| Symbol                                                                    | Pin No.                                             | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------|-----------------------------------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TTD(2-0)<br>TTD(5-3)<br>TTD(8-6)<br>TTD(11-9)<br>TTD(14-12)<br>TTD(17,15) | 81-79<br>85-83<br>89-87<br>93-91<br>97-95<br>101,99 | ı     | TTL  | Transmit Terminal Data In: Transmit data and parity. In the byte mode, TTD (7-0) are data and TTD (8) is an even parity / start of cell indicator. In the word mode, TTD (15-0) are data and TTD (17,16) are even parity / start of cell indicators. If the UTOPIA mode is active, there is no parity on the CDB cell input and start of cell is provided on pin 100, TTD16/TxSOC. |

| TTD16/<br>TxSOC                                                           | 100                                                 | I     | TTL  | Transmit Terminal Data In: Parity bit or start of cell in UTOPIA mode (TxSOC).                                                                                                                                                                                                                                                                                                     |

| TICLK                                                                     | 103                                                 | I     | TTL  | Transmit Input Clock: Write clock internal FIFO mode. Maximum frequency is 20 MHz.                                                                                                                                                                                                                                                                                                 |

| TCF2/<br>TxENB                                                            | 104                                                 | I     | TTL  | Transmit Terminal Control Line 2: FIFO almost empty input in external FIFO mode (TCF2 active low) Write enable in internal FIFO mode (TCF2 active low) CELAVL from SARA-S in SARA mode (TCF2 active low) Transmit Enable in UTOPIA mode (TxENB active low).                                                                                                                        |

| TRES                                                                      | 105                                                 | I     | TTL  | Transmit Terminal Reset: Clears the input FIFOs. This signal must be low for at least 100 nanoseconds.                                                                                                                                                                                                                                                                             |

# **Boundary Scan and Test**

| Symbol   | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                   |  |  |  |

|----------|---------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TDO      | 26      | 0     | CMOS4mA | <b>Test Data Output:</b> Data and test instructions from internal test registers output.                                        |  |  |  |

| TRS      | 28      | I     | TTLp    | Test Mode Reset: A 100 nanosecond (minimum) low this pin resets the boundary scan; recommended power-up initialization as well. |  |  |  |

| TMS      | 29      | I     | TTLp    | Test Mode Select: Mode select.                                                                                                  |  |  |  |

| TDI      | 30      | I     | TTLp    | Test Data Input: Data and test instruction input.                                                                               |  |  |  |

| TCK      | 31      | I     | TTLp    | Test Clock: Clock in signals on rising edge.                                                                                    |  |  |  |

| SCANTEST | 33      | I     | TTLp    | Scan Test Select: Scan test, tie low for normal operating conditions.                                                           |  |  |  |

| SCANEN   | 34      | I     | TTLp    | Scan Test Enable: Scan enable, tie low for normal operating conditions.                                                         |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                      | Symbol          | Min  | Max                   | Unit |

|--------------------------------|-----------------|------|-----------------------|------|

| Supply voltage                 | V <sub>DD</sub> | -0.3 | 7.0                   | V    |

| DC input voltage               | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Continuous Power Dissipation   | P <sub>C</sub>  |      |                       | mW   |

| Ambient operating temperature  | T <sub>A</sub>  | -40  | 85                    | °C   |

| Operating junction temperature | T <sub>J</sub>  |      | 150                   | °C   |

| Storage temperature range      | T <sub>S</sub>  | -55  | 150                   | °C   |

<sup>\*</sup>Note: Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

## THERMAL CHARACTERISTICS

| Parameter                                | Min | Тур | Max | Unit | Test Conditions |

|------------------------------------------|-----|-----|-----|------|-----------------|

| Thermal resistance - junction to ambient |     | 43  |     | °C/W |                 |

## **POWER REQUIREMENTS**

| Parameter       | Min  | Тур | Max  | Unit | Test Conditions            |

|-----------------|------|-----|------|------|----------------------------|

| $V_{DD}$        | 4.75 | 5.0 | 5.25 | V    |                            |

| I <sub>DD</sub> |      | 98  |      | mA   |                            |

| P <sub>DD</sub> |      | 490 |      | mW   | Inputs switching at 20 MHz |

# INPUT, OUTPUT AND I/O PARAMETERS

## Input Parameters For TTL and TTLp\*

| Parameter             | Min | Тур  | Max | Unit | Test Conditions                                   |

|-----------------------|-----|------|-----|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |      |     | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| V <sub>IL</sub>       |     |      | 0.8 | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| Input leakage current |     | -1   |     | μΑ   |                                                   |

| Input capacitance     |     | 2.95 |     | pF   |                                                   |

<sup>\*</sup> The TTLp pins have internal 10K $\Omega$  pull-ups.

## **Output Parameters For CMOS4mA**

| Parameter         | Min | Тур | Max  | Unit | Test Conditions                                |

|-------------------|-----|-----|------|------|------------------------------------------------|

| V <sub>OH</sub>   | 2.4 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = 4.0  |

| V <sub>OL</sub>   |     |     | 0.5  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = -4.0 |

| I <sub>OL</sub>   |     |     | -4.0 | mA   |                                                |

| I <sub>OH</sub>   |     |     | 4.0  | mA   |                                                |

| t <sub>RISE</sub> |     | 2.3 |      | ns   | C <sub>LOAD</sub> = 15pF                       |

| t <sub>FALL</sub> |     | 3.3 |      | ns   | C <sub>LOAD</sub> = 15pF                       |

## **Output Parameters For CMOS Open Drain (4mA)**

| Parameter         | Min | Тур | Max | Unit | Test Conditions                               |

|-------------------|-----|-----|-----|------|-----------------------------------------------|

| V <sub>OL</sub>   |     |     | 0.5 | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0 |

| I <sub>OL</sub>   |     |     | 4.0 | mA   |                                               |

| t <sub>RISE</sub> |     | 0.8 |     | ns   | C <sub>LOAD</sub> = 15pF                      |

| t <sub>FALL</sub> |     | 3.3 |     | ns   | C <sub>LOAD</sub> = 15pF                      |

Note: Open Drain requires use of 4.7 KOhm external pull-up resistor. If this resistor is not provided the output behaves as tristate, as shown in Figures 20-23.

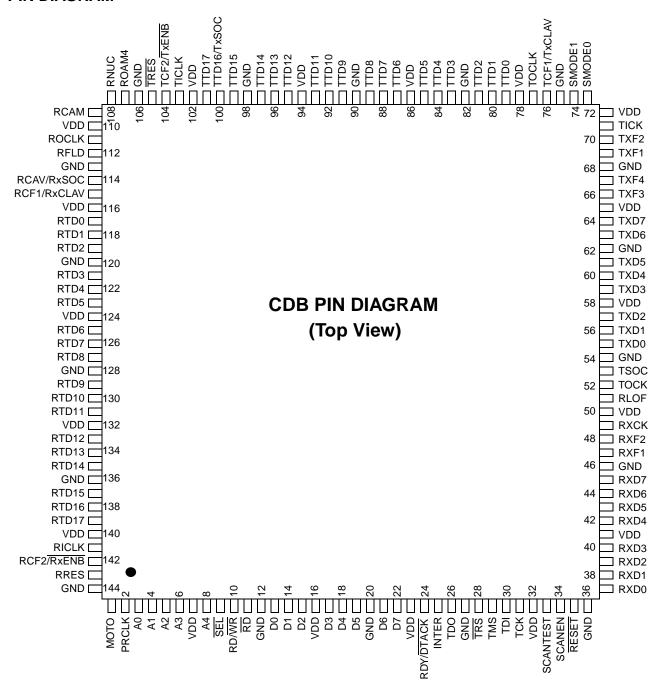

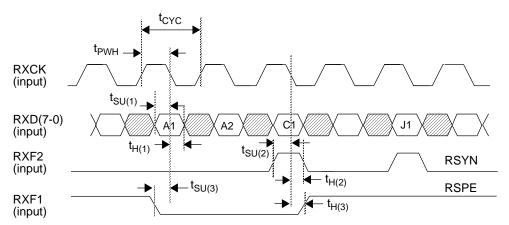

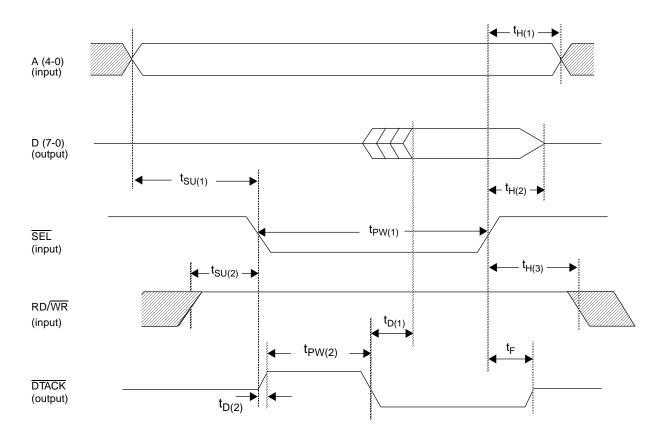

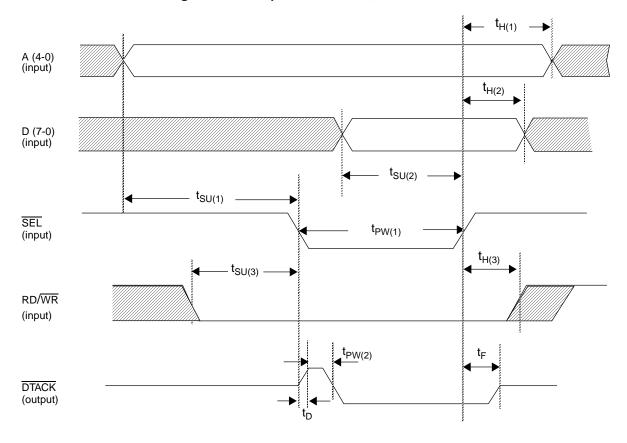

### **TIMING CHARACTERISTICS**

Detailed timing diagrams for the CDB are illustrated in Figures 3 through 23, with values of the timing intervals following each figure. All output times are measured with a maximum 25 pF load capacitance. Timing parameters are measured at  $(V_{OH} - V_{OL})/2$  or  $(V_{IH} - V_{IL})/2$  as applicable.

RXCK (input)  $t_{SU(1)}$  RXD(7-0) (input)  $t_{SU(1)}$  RXF1 (input) RXF2 (input) RSPE RPOH

Figure 3. Receive Line Interface Timing, STS-3c/STM-1 Mode

| Parameter                                           | Symbol             | Min | Тур  | Max | Unit |

|-----------------------------------------------------|--------------------|-----|------|-----|------|

| RXCK clock period                                   | t <sub>CYC</sub>   |     | 51.4 |     | ns   |

| RXCK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub> |                    | 40  |      | 60  | %    |

| RXD(7-0) set-up time to RXCK↑                       | t <sub>SU(1)</sub> | 10  |      |     | ns   |

| RXD(7-0) hold time after RXCK↑                      | t <sub>H(1)</sub>  | 4   |      |     | ns   |

| RXF1 set-up time to RXCK↑                           | t <sub>SU(2)</sub> | 10  |      |     | ns   |

| RXF1 hold time after RXCK↑                          | t <sub>H(2)</sub>  | 4   |      |     | ns   |

| RXF2 set-up time to RXCK↑                           | t <sub>SU(3)</sub> | 10  |      |     | ns   |

| RXF2 hold time after RXCK↑                          | t <sub>H(3)</sub>  | 4   |      |     | ns   |

$t_{H(3)}$

TSOC

(output)

TICK (input)

TXD(7-0) (output)

TXF1 (input)

TXF2 (input)

Byte 1 of ATM cell

Figure 4. Transmit Line Interface Timing, STS-3c/STM-1 Mode

| Parameter                                           | Symbol             | Min | Тур  | Max | Unit |

|-----------------------------------------------------|--------------------|-----|------|-----|------|

| TICK clock period                                   | t <sub>CYC</sub>   |     | 51.4 |     | ns   |

| TICK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub> |                    | 40  |      | 60  | %    |

| TXF1 low set-up time to TICK↑                       | t <sub>SU(1)</sub> | 10  |      |     | ns   |

| TXF1 high set-up time to TICK↑                      | t <sub>SU(2)</sub> | 10  |      |     | ns   |

| TXD(7-0) delay after TICK↑                          | t <sub>D(1)</sub>  | 4   |      | 20  | ns   |

| TXF2 set-up time to TICK↑                           | t <sub>SU(3)</sub> | 10  |      |     | ns   |

| TXF2 hold time after TICK↑                          | t <sub>H</sub>     | 4   |      |     | ns   |

| TSOC delay after TICK↑                              | t <sub>D(2)</sub>  | 4   |      | 20  | ns   |

Note that TSOC (Transmit Start Of Cell) can occur anywhere in the output data with respect to the STS-3c /STM-1 frame. It is exactly one byte long and it is synchronous with the first byte of the output cell.

Figure 5. Receive Line Interface Timing, STS-1 Mode

| Parameter                                           | Symbol             | Min | Тур | Max | Unit |

|-----------------------------------------------------|--------------------|-----|-----|-----|------|

| RXCK clock period                                   | t <sub>CYC</sub>   |     | 154 |     | ns   |

| RXCK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub> |                    | 40  |     | 60  | %    |

| RXD(7-0) set-up time to RXCK↓                       | t <sub>SU(1)</sub> | 10  |     |     | ns   |

| RXD(7-0) hold time after RXCK↓                      | t <sub>H(1)</sub>  | 4   |     |     | ns   |

| RXF2 set-up time to RXCK↓                           | t <sub>SU(2)</sub> | 10  |     |     | ns   |

| RXF2 hold time after RXCK↓                          | t <sub>H(2)</sub>  | 4   |     |     | ns   |

| RXF1 set-up time to RXCK↓                           | t <sub>SU(3)</sub> | 10  |     |     | ns   |

| RXF1 hold time after RXCK↓                          | t <sub>H(3)</sub>  | 4   |     |     | ns   |

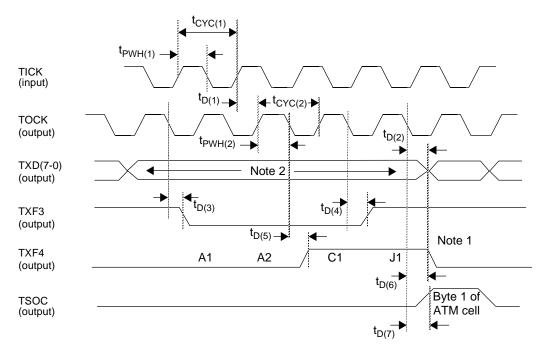

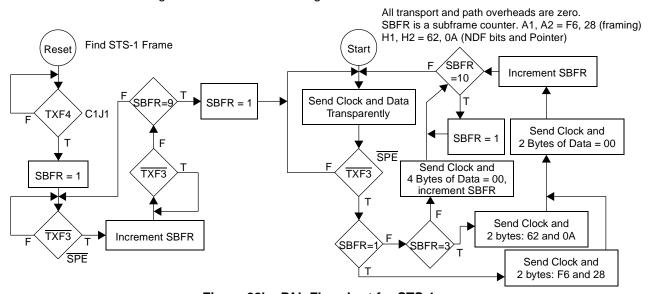

Figure 6. Transmit Line Interface Timing, STS-1 Mode

| Parameter                                                 | Symbol              | Min | Тур | Max | Unit |

|-----------------------------------------------------------|---------------------|-----|-----|-----|------|

| TICK clock period                                         | t <sub>CYC(1)</sub> |     | 154 |     | ns   |

| TICK duty cycle, t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> |                     | 40  |     | 60  | %    |

| TOCK clock period                                         | t <sub>CYC(2)</sub> |     | 154 |     | ns   |

| TOCK duty cycle, t <sub>PWH(2)</sub> /t <sub>CYC(2)</sub> |                     | 40  |     | 60  | %    |

| TOCK↑ delay after TICK↑                                   | t <sub>D(1)</sub>   | 3.0 |     | 12  | ns   |

| TXD(7-0) delay after TOCK↓                                | t <sub>D(2)</sub>   | 0.5 |     | 6   | ns   |

| TXF3↓ delay after TOCK↓                                   | t <sub>D(3)</sub>   | 0.5 |     | 5   | ns   |

| TXF3 <sup>↑</sup> delay after TOCK↓                       | t <sub>D(4)</sub>   | 0.5 |     | 5   | ns   |

| TXF4 <sup>↑</sup> delay after TOCK↓                       | t <sub>D(5)</sub>   | 0.5 |     | 5   | ns   |

| TXF4↓ delay after TOCK↓                                   | t <sub>D(6)</sub>   | 0.5 |     | 5   | ns   |

| TSOC delay after TOCK↓                                    | t <sub>D(7)</sub>   | 1.5 |     | 7   | ns   |

Note 1: TXF4 is only active high for C1 and J1.

Note 2: Regardless of TXF4, TXD(7-0) are held for 5 clock pulses.

Note 3: TSOC (Transmit Start of Cell) can occur anywhere in the output data with respect to the STS-1 frame. It is exactly one byte long and it is synchronous with the first byte of the output cell.

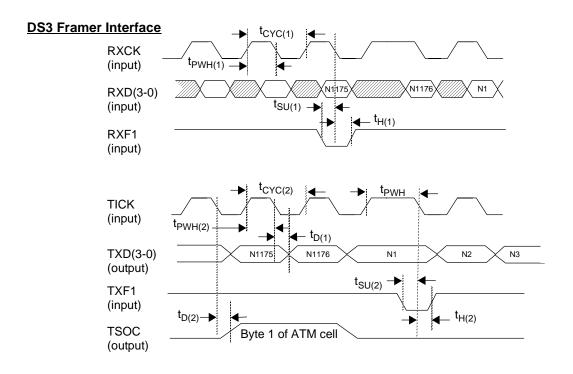

Figure 7. Receive/Transmit Line Interface Timing for DS3

| Parameter                                                 | Symbol              | Min | Тур  | Max | Unit |

|-----------------------------------------------------------|---------------------|-----|------|-----|------|

| RXCK clock period                                         | t <sub>CYC(1)</sub> |     | 89.4 |     | ns   |

| RXCK duty cycle, t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> |                     | 40  |      | 60  | %    |

| RXF1 set-up time to RXCK↓                                 | t <sub>SU(1)</sub>  | 10  |      |     | ns   |

| RXF1 hold time after RXCK↓                                | t <sub>H(1)</sub>   | 4   |      |     | ns   |

| TICK clock period                                         | t <sub>CYC(2)</sub> |     | 89.4 |     | ns   |

| TICK duty cycle, t <sub>PWH(2)</sub> /t <sub>CYC(2)</sub> |                     | 40  |      | 60  | %    |

| TICK long high time                                       | t <sub>PWH</sub>    |     | 67   |     | ns   |

| TXD(3-0) delay after TICK↓                                | t <sub>D(1)</sub>   | 4   |      | 21  | ns   |

| TXF1 set-up time to TICK↓                                 | t <sub>SU(2)</sub>  | 10  |      |     | ns   |

| TXF1 hold time after TICK↓                                | t <sub>H(2)</sub>   | 4   |      |     | ns   |

| TSOC delay after TICK↓                                    | t <sub>D(2)</sub>   | 4   |      | 21  | ns   |

Note: The TSOC output is two nibbles (one byte) long. It indicates the first byte of the cell in the DS3 output. Should the first byte in the cell occur with a stretched clock (to account for DS3 overhead insertion), the TSOC will also be stretched. The TSOC output is synchronous with the output DS3 nibbles.

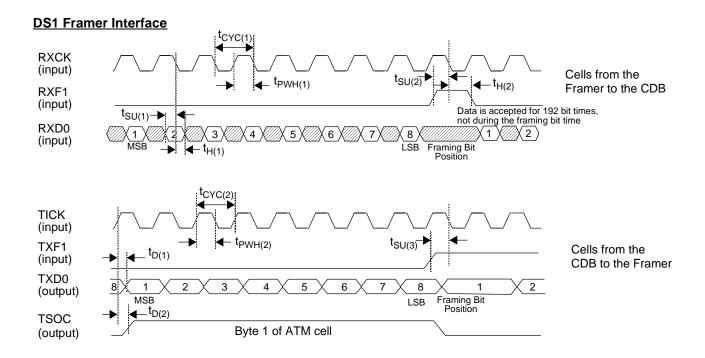

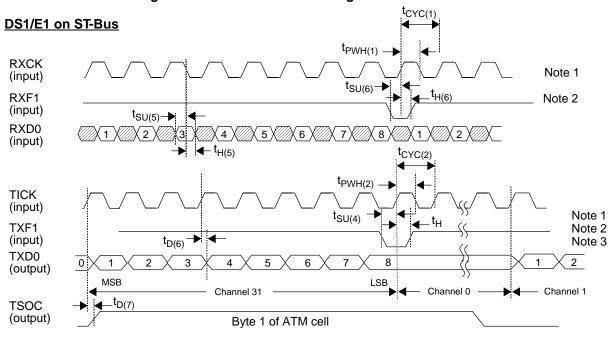

Figure 8a. Receive/Transmit Line Interface Timing for DS1

| Parameter                                                 | Symbol              | Min | Тур | Max | Unit |

|-----------------------------------------------------------|---------------------|-----|-----|-----|------|

| RXCK clock period                                         | t <sub>CYC(1)</sub> |     | 648 |     | ns   |

| RXCK duty cycle, t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> |                     | 40  |     | 60  | %    |

| RXD0 set-up time to RXCK↓                                 | t <sub>SU(1)</sub>  | 10  |     |     | ns   |

| RXD0 hold time after RXCK↓                                | t <sub>H(1)</sub>   | 4   |     |     | ns   |

| RXF1 set-up time to RXCK↓                                 | t <sub>SU(2)</sub>  | 10  |     |     | ns   |

| RXF1 hold time after RXCK↓                                | t <sub>H(2)</sub>   | 4   |     |     | ns   |

| TICK clock period                                         | t <sub>CYC(2)</sub> |     | 648 |     | ns   |

| TICK duty cycle, t <sub>PWH(2)</sub> /t <sub>CYC(2)</sub> |                     | 40  |     | 60  | %    |

| TXD0 delay after TICK↑                                    | t <sub>D(1)</sub>   | 4   |     | 20  | ns   |

| TXF1 set-up time to TICK↓                                 | t <sub>SU(3)</sub>  | 10  |     |     | ns   |

| TSOC delay after TICK↑                                    | t <sub>D(2)</sub>   | 4   |     | 20  | ns   |

Note: The TSOC output is 8 bits (one byte) long. It indicates the first byte of the cell in the DS1 output, and it is synchronous with the DS1 bits.

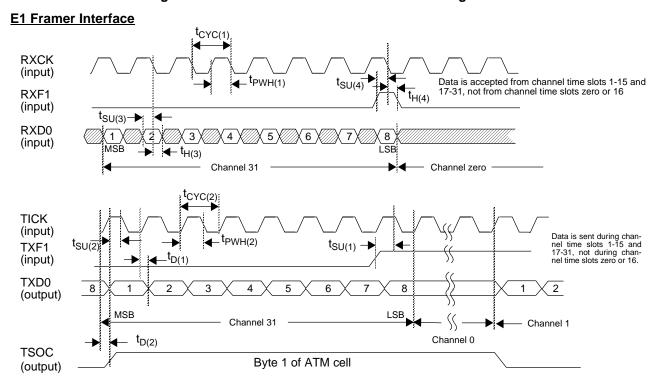

Figure 8b. Receive/Transmit Line Interface Timing for E1

| Parameter                                                 | Symbol              | Min | Тур | Max | Unit |

|-----------------------------------------------------------|---------------------|-----|-----|-----|------|

| RXCK clock period                                         | t <sub>CYC(1)</sub> |     | 488 |     | ns   |

| RXCK duty cycle, t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> |                     | 40  |     | 60  | %    |

| RXD0 set-up time to RXCK↓                                 | t <sub>SU(3)</sub>  | 10  |     |     | ns   |

| RXD0 hold time after RXCK↓                                | t <sub>H(3)</sub>   | 4   |     |     | ns   |

| RXF1 set-up time to RXCK↓                                 | t <sub>SU(4)</sub>  | 10  |     |     | ns   |

| RXF1 hold time after RXCK↓                                | t <sub>H(4)</sub>   | 4   |     |     | ns   |

| TICK clock period                                         | t <sub>CYC(2)</sub> |     | 488 |     | ns   |

| TICK duty cycle, t <sub>PWH(2)</sub> /t <sub>CYC(2)</sub> |                     | 40  |     | 60  | %    |

| TXD0 delay after TICK↑                                    | t <sub>D(1)</sub>   | 4   |     | 20  | ns   |

| TXD0 set-up time to TICK↓                                 | t <sub>SU(2)</sub>  | 10  |     |     | ns   |

| TXF1 set-up time to TICK↓                                 | t <sub>SU(1)</sub>  | 10  |     |     | ns   |

| TSOC delay after TICK↑                                    | t <sub>D(2)</sub>   | 4   |     | 20  | ns   |

Note: The TSOC output is 8 bits (one byte) long. It indicates the first byte of the cell in the E1 output, and it is synchronous with the E1 bits. Since the first byte of the cell in Figure 9 is in channel 31 of the E1 frame, the TSOC signal is extended over the channel 0 byte of the frame (the framing byte) to the beginning of the second byte of the cell in channel 1. It would also be extended over channel 16 should the first byte of the cell occur in channel 15. Otherwise, the TSOC signal is one byte long.

Figure 9. Receive/Transmit Timing for ST-Bus DS1/E1

### E1 Channels on 2048 Kbit/s ST-Bus PCM Highway

| DX  | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30  | 31 |

|-----|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|

| DS1 |   | 1 | 2 | 3 |   | 4 | 5 | 6 |   | 7 | 8  | 9  |    | 10 | 11 | 12 |    | 13 | 14 | 15 |    | 16 | 17 | 18 |    | 19 | 20 | 21 |    | 22 | 173 | 24 |

### **DS1 Channels on ST-Bus PCM Highway**

Note 1: For DS1 data the CDB neither accepts nor sends for channel time slots 0, 4, 8, 12, 16, 20, 24 and 28.

Note 2: For E1 data the CDB neither accepts nor sends for channel time slots 0 and 16.

**Note 3**: The TSOC (Transmit Start Of Cell) signal on pin 53 is high during the first byte of an output cell for either DS1 or E1. The TSOC signal is synchronous with the first bit of the output byte and is held for 8 bits unless the first byte of the cell is just before an empty slot for DS1 or channel 0 or 15 of E1. In these cases, TSOC is held for 16 bits or 2 bytes to the start of the second byte of the output ATM cell.

| Parameter                                                 | Symbol              | Min | Тур | Max | Unit |

|-----------------------------------------------------------|---------------------|-----|-----|-----|------|

| RXCK clock period                                         | t <sub>CYC(1)</sub> |     | 488 |     | ns   |

| RXCK duty cycle, t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> |                     | 40  |     | 60  | %    |

| RXD0 set-up time to RXCK↓                                 | t <sub>SU(5)</sub>  | 10  |     |     | ns   |

| RXD0 hold time after RXCK↓                                | t <sub>H(5)</sub>   | 4   |     |     | ns   |

| RXF1 set-up time to RXCK↑                                 | t <sub>SU(6)</sub>  | 10  |     |     | ns   |

| RXF1 hold time after RXCK↑                                | t <sub>H(6)</sub>   | 4   |     |     | ns   |

| TICK clock period                                         | t <sub>CYC(2)</sub> |     | 488 |     | ns   |

| TICK duty cycle, t <sub>PWH(2)</sub> /t <sub>CYC(2)</sub> |                     | 40  |     | 60  | %    |

| TXD0 delay after TICK↑                                    | t <sub>D(6)</sub>   | 4   |     | 20  | ns   |

| TXF1 set-up time to TICK↑                                 | t <sub>SU(4)</sub>  | 10  |     |     | ns   |

| TXF1 hold time after TICK↑                                | t <sub>H</sub>      | 4   |     |     | ns   |

| TSOC delay after TICK↑                                    | t <sub>D(7)</sub>   | 4   |     | 20  | ns   |

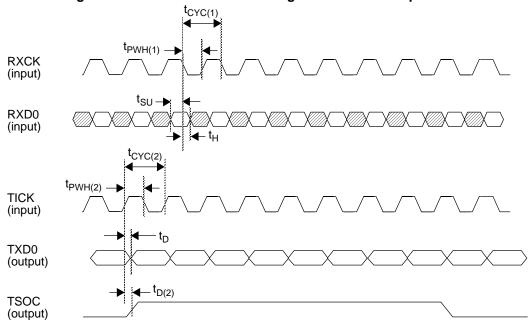

Figure 10. Receive / Transmit Timing for Serial Mode Operation

The maximum frequency of the two input clocks (RXCK and TICK) is 20 MHz.

All unused inputs (RXF1, RXF2, TXF1 and TXF2) must not be left open. It is preferred that they be taken to ground, though they can be taken to VDD. The CDB is unaffected by their state when it is operated in the serial mode.

| Parameter                                                 | Symbol              | Min | Тур | Max | Unit |

|-----------------------------------------------------------|---------------------|-----|-----|-----|------|

| RXCK clock period                                         | t <sub>CYC(1)</sub> |     | 488 |     | ns   |

| RXCK duty cycle, t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> |                     | 40  |     | 60  | %    |

| RXD0 set-up time to RXCK↓                                 | t <sub>SU</sub>     | 10  |     |     | ns   |