- 58-MHz Max Clock Rate

- Two Transition Complement Array Terms

- 16-Bit Internal State Registers

- 8-Bit Output Registers

- Outputs Programmable for Registered or Combinational Operation

- Ideal for Waveform Generation and High-Performance State Machine Applications

- Programmable Output Enable

- Programmable Clock Polarity

# description

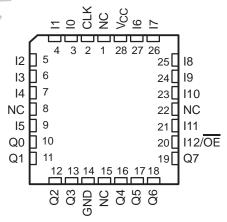

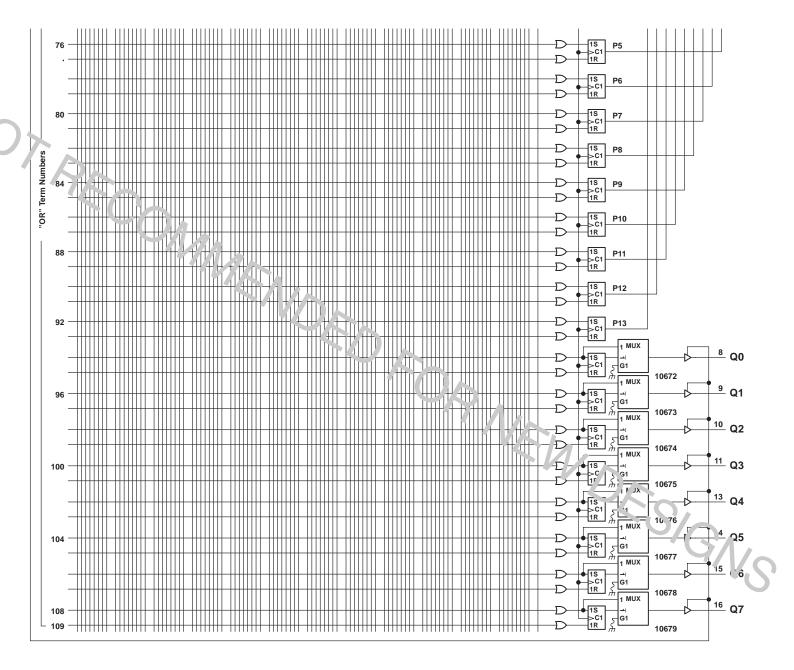

The TIBPLS506AC is a TTL field-programmable state machine of the Mealy type. This state machine (logic sequencer) contains 97 product terms (AND terms) and 48 sum terms (OR terms). The product and sum terms are used to control the 16-bit internal state registers and the 8-bit output registers.

The outputs of the internal state registers (P0–P15) are fed back and combined with the 13 inputs (I0–I12) to form the AND array. In admittion, two sum terms are complemented and fed back to the AND array, which allows any product term to be summed, complemented, and used as input to the AND array.

The eight output cells can by individually programmed for registered or combinational operation. Nonregistered operation is selected by blowing the output multiplexer rose. Registered output operation is selected by leaving the output multiplexer fuse intact.

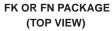

NC - No internal connection

Pin 17 can be programmed to 1 unction as an input and/or an output enable. Blowing the output enable fuse lets pin 17 function as an output chable but does not disconnect pin 17 from the input array. When the output enable fuse is intact, pin 17 functions only as an input with the outputs being permanently enabled.

The state and output recisters are synchronously clocked by the fuse programmable clock input. The clock polarity fuse selected by postive-or negative-edge triggering. Negative-edge triggering is selected by blowing the clock polarity fuse. Leaving this fuse intact selects positive-edge triggering. After power-up, the device must be initialized to the assired state. When the output multiplexer fuse is left intact, registered operation is selected.

The TIBPLS506AC is characterized for operation from 0°C to 75°C.

# TIBPLS506AC $13 \times 97 \times 8$ FIELD-PROGRAMMABLE LOGIC SEQUENCER

SRPS003C - D3090, DECEMBER 1987 - REVISED NOVEMBER 1995

All inputs to AND gates, exclusive-OR gates, and multiplexers with a blown link assume the logic-1 state. All OR gate inputs with a blown link assume the logic-0 state.

#### S-R FUNCTION TABLE (see Note 1)

| CLK POLARITY FUSE | CLK          | S | R | STATE REGISTER    |

|-------------------|--------------|---|---|-------------------|

| INTACT            | 1            | L | L | Q <sub>0</sub>    |

| INTACT            | <b>↑</b>     | L | Н | L                 |

| INTACT            | <b>↑</b>     | Н | L | Н                 |

| INTACT            | <b>↑</b>     | Н | Н | INDETERMINATE     |

| BLOWN             | $\downarrow$ | L | L | $Q_0$             |

| BLOWN             | $\downarrow$ | L | Н | L /               |

| BLOWN             | $\downarrow$ | Н | L | H                 |

| BLOWN             | $\downarrow$ | Н | Н | INDETF & Mir 'ATE |

NOTE 1: Q<sub>0</sub> is the state of the S-R registers before the active clock edge.

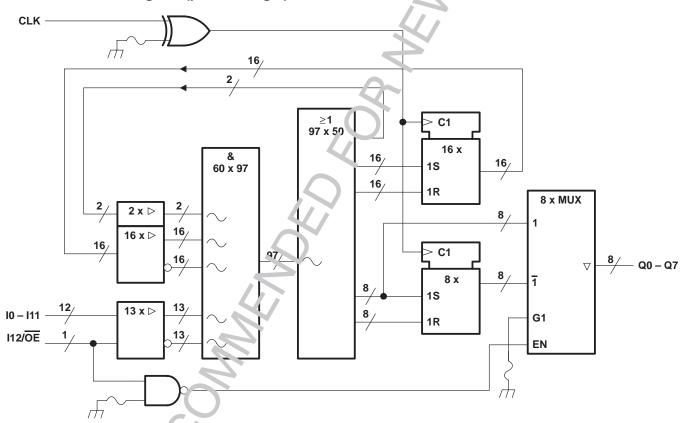

# functional block diagram (positive logic)

$\sim$  denotes fused inputs

SRPS003C - D3090, DECEMBER 1987 - REVISED NOVEMBER 1995

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 2)    | <br>7 V         |

|-------------------------------------------------|-----------------|

| Input voltage (see Note 2)                      | <br>5.5 V       |

| Voltage applied to disabled output (see Note 2) | <br>5.5 V       |

| Operating free-air temperature range            | <br>0°C to 75°C |

| Storage temperature range                       |                 |

NOTE 2: These ratings apply except when programming pins during a programming cycle or during lacensuic testing.

# recommended operating conditions

|                               |                                          |                                               |                  | MIN  | NOM | MAX  | UNIT |

|-------------------------------|------------------------------------------|-----------------------------------------------|------------------|------|-----|------|------|

| VCC                           | Supply voltage                           |                                               |                  | 4.75 | 5   | 5.25 | V    |

| VIH                           | High-level input voltage, Vo             | CC = 5.25 V                                   |                  | 2    |     | 5.5  | V    |

| V <sub>IL</sub>               | Low-level input voltage, VC              | C = 4.75 V                                    |                  |      |     | 0.8  | V    |

| ІОН                           | High-level output current                |                                               |                  |      |     | -3.2 | mA   |

| loL                           | Low-level output current                 |                                               | 4/1              |      |     | 16   | mA   |

| t Dulas dunation              | Clock high                               |                                               | 6                |      |     | ns   |      |

| t <sub>W</sub> Pulse duration |                                          | Clock low                                     |                  | 6    |     |      | 115  |

|                               | 0 / / 01/                                | Input or feedback to S/R↑ inputs              | Without C-array  | 12   |     |      |      |

| t <sub>su</sub>               | Setup time before CLK active transition† | Input or feedback to S/R↓ inputs <sup>†</sup> | Williout G-allay | 20   |     |      | ns   |

|                               | active transition.                       | Input or feedback to S/R inputs               | With C-array     | 25   |     |      |      |

| th                            | Hold time after CLK                      | Input or feedback to S/R inputs               | -                | 0    |     |      | ns   |

| TA                            | Operating free-air temperature           |                                               |                  |      | 25  | 75   | °C   |

<sup>†</sup> The active edge of CLK is determined by the programmed state of CLC polarity fuse.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER        |                            | Tr.si CONDITIONS            |              | MIN | TYP§ | MAX   | UNIT |

|------------------|----------------------------|-----------------------------|--------------|-----|------|-------|------|

| VIK              | V <sub>CC</sub> = 4.75 V,  | I <sub>I</sub> –′ 8 mA      |              |     |      | -1.2  | V    |

| VOH              | $V_{CC} = 4.75 \text{ V},$ | l <sub>C1.1</sub> = −3.2 mA |              | 2.4 | 3    |       | V    |

| V <sub>OL</sub>  | V <sub>CC</sub> = 4.75 V,  | .oL = 16 mA                 |              |     | 0.37 | 0.5   | V    |

| lozh             | V <sub>CC</sub> = 5.25 V,  | V <sub>O</sub> = 2.7 V      |              |     |      | 20    | μΑ   |

| lozL             | V <sub>CC</sub> = 5.25 V,  | V <sub>O</sub> = 0.4 V      |              |     |      | -20   | μΑ   |

| I <sub>I</sub>   | V <sub>CC</sub> = 5.25 V.  | V <sub>I</sub> = 5.5 V      |              |     |      | 0.1   | mA   |

| lіН              | V <sub>CC</sub> = 5.25 V,  | V <sub>I</sub> = 2.7 V      |              |     |      | 20    | μΑ   |

| I <sub>IL</sub>  | $V_{CC} = 5.25 \text{ v},$ | V <sub>I</sub> = 0.4 V      |              |     |      | -0.25 | mA   |

| IO¶              | V <sub>CC</sub> = £ .25 V, | $V_0 = 0.5 V$               |              | -30 |      | -130  | mA   |

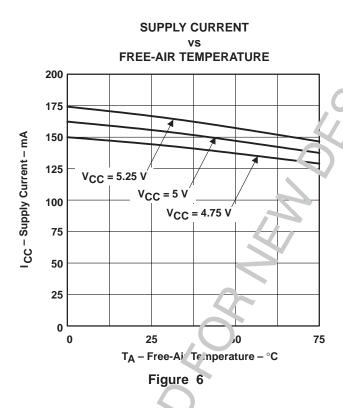

| Icc              | V <sub>CC</sub> - 5.25 v,  | See Note 3,                 | Outputs open |     | 156  | 210   | mA   |

| Ci               | f = 1 MHz,                 | V <sub>I</sub> = 2 V        |              |     | 7    |       | pF   |

| Co               | f = 1 MHz,                 | V <sub>O</sub> = 2 V        | ·            |     | 11   |       | pF   |

| C <sub>clk</sub> | f = 1 M Hz,                | V <sub>CLK</sub> = 2 V      |              |     | 14   |       | pF   |

NOTE 3: When the clock is programmed for negitive edge, then V<sub>I</sub> = 4.75 V. When the clock is programmed for positive edge, then V<sub>I</sub> = 0.

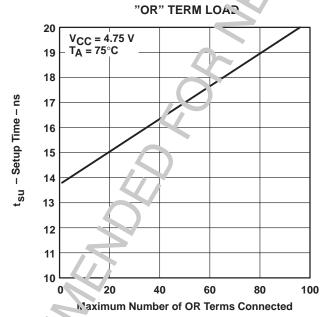

<sup>‡</sup> See the OR term loading section and Figure 3.

<sup>§</sup> All typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C. ¶ This parameter approximates  $v_{CS}$ . The condition  $v_{CS}$  = 0.5 V takes tester noise into account. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER          | FROM<br>(INPUT)  | TO<br>(OUTPUT)    | TEST CONDITION      | Mix  | түр† | MAX | UNIT    |

|--------------------|------------------|-------------------|---------------------|------|------|-----|---------|

|                    | Without          | C-array           |                     | 20   | 65   |     |         |

| , +                | With C           | -array            | ] (                 | 33   | 45   |     | N 41 1- |

| f <sub>max</sub> ‡ | External feedbac | k without C-array |                     | 45   | 60   |     | MHz     |

|                    | External feedba  | ck with C-array   | R1 = $300 \Omega$ , | 28.5 | 40   |     |         |

|                    | 01.14            | Q (nonregistered) | R2 = 390 Ω          | 6    |      | 25  |         |

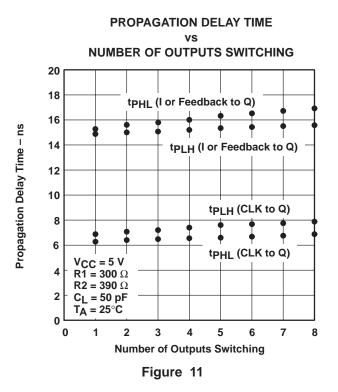

| t <sub>pd</sub>    | CLK              | Q (registered)    | See Figu: > 5       | 3    |      | 10  | ns      |

|                    | I or Feedback    | Q (nonregistered) |                     | 6    |      | 20  | ns      |

| <sup>t</sup> en    | OE↓              | Q                 |                     | 1    | 6    | 10  | ns      |

| <sup>t</sup> dis   | ŌE↑              | Q                 |                     | 1    | 6    | 10  | ns      |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

# f<sub>max</sub> calculations

The following is a brief description of how the different operating frequencies can be achieved when using the TIBPLS506A.

$f_{max}$  without C-(complementary) array =  $\frac{1}{t_{SU} + t_{rd}}$  CLK to Q where setup time  $t_{SU}$  before CLK at the S/R register inputs = 12 ns and propagation delay time  $t_{rd}$  CLK to Q for the internal S/R registers = 5ns (difference in  $t_{rd}$  from CLK and feedback, 25 to 20).

Thus:

$$f_{max}$$

for this condition =  $\frac{1}{(12+5)}$  ns =  $\frac{1}{17}$  ns = 58 MHz.

$f_{max}$  with the C-array =  $\frac{1}{t_{SU} + t_{p,1}}$  CLK to Q where  $t_{SU}$  setup time before CLK at the S/R register inputs = 25 ns and propagation delay time  $t_{pd}$  CLK to Q for the internal S/R registers = 5 ns (difference in  $t_{pd}$  from CLK and feedback, 25 to 20)

Thus:

$$f_{\text{max}}$$

for this condition =  $\frac{1}{(2\sqrt[3]{5})}$  ns =  $\frac{1}{30}$  ns = 33 MHz.

$f_{max}$  external feedback without the C-array =  $\frac{1}{t_{su} + t_{pd}}$  CLK to Q where setup time  $t_{su}$  before CLK at the S/R register inputs = 12  $\frac{1}{t_{su}}$  propagation delay time  $t_{pd}$  CLK to Q for the internal S/R registers = 10 ns

Thus:

$$f_{max}$$

for this condition =  $\frac{1}{(12+10)}$  ns =  $\frac{1}{22}$  ns = 45 MHz.

$f_{max}$  external feec back with the C-array =  $\frac{1}{t_{SU} + t_{pd}}$  CLK to Q where setup time  $t_{SU}$  before CLK at the S/R register inputs = 25 Ls and propagation delay time  $t_{pd}$  CLK to Q for the internal S/R registers = 10 ns.

Thus:

$$f_{max}$$

for this condition =  $\frac{1}{(25 + 10) \text{ ns}} = \frac{1}{35 \text{ ns}} = 28.5 \text{ MHz}.$

<sup>‡</sup> See the f<sub>max</sub> calculations section.

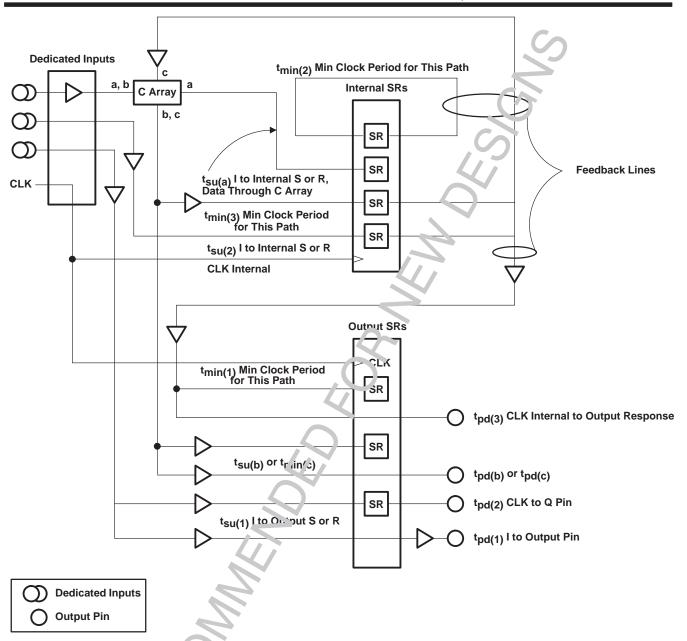

Figure 1. Timing Model

SRPS003C - D3090, DECEMBER 1987 - REVISED NOVEMBER 1995

# glossary — timing model

- t<sub>pd(1)</sub> Maximum time interval from the time a signal edge is received at any input pint of the time any logically affected combinational output pin delivers a response.

- t<sub>pd(2)</sub> Maximum time interval from a positive edge on the clock input pin to data aclivery on the output pin corresponding to any output SR register.

- t<sub>pd(3)</sub> Maximum time interval from the positive edge on the clock input pin to the response on any logically affected combinational configured output (at the pin), where date cug it is any internal SR register.

- t<sub>pd(b)</sub> Maximum time interval from the time a signal edge is received a any input pin to the time any logically affected combinational output pin delivers a response, where date passes through a C-array once before reaching the affected output.

- Maximum time interval from the positive edge on the clock input pin to the response on any logically affected combinational configured output (at the pin), where data origin is any internal SR register and data passes once through a C-array before reaching in affected output.

- t<sub>su(1)</sub> Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin when data affects the S or R line of any output SR register.

- t<sub>su(2)</sub> Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin when data affects the S or R line of any internal SR register.

- Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin when data passes once through a C-array before reaching an affected S or R line on any internal SR register.

- t<sub>su(b)</sub> Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin when data passes once through a C-array before reaching an affected S or R line on any output SF. register.

- t<sub>min(1)</sub> Minimum clock period (or 1/[maxir.jur.i frequency]) that the device will accommodate when using feedback from any internal SR register or counter bit to feed the S or R line of any output SR register.

- t<sub>min(2)</sub> Minimum clock period (or 1/[maxi.num frequency]) that the device will accommodate when using feedback from any internal CR register to feed the S or R line of any internal SR register.

- t<sub>min(3)</sub> Minimum clock period (or ./[maximum frequency]) that the device will accommodate when using feedback from any into that SR register to feed the S or R line of any internal SR register and data passes once through a C-array before reaching an affected S or R line on any internal SR register.

- t<sub>min(c)</sub> Minimum clock period (or 1/[maximum frequency]) that the device will accommodate when using feedback from any internal SR register to feed the S or R line of any output SR register and data passes once through a C-array before reaching an affected S or R line on any output SR register.

#### PARAMETER VALUES FOR TIMING MODEL

| $t_{pd(1)} = 20 \text{ ns}$ | t <sub>su(1)</sub> = 12 ns <sup>†</sup> | $t_{min(1)} = 20 \text{ ns}$ |

|-----------------------------|-----------------------------------------|------------------------------|

| $t_{pd(2)} = 10 \text{ ns}$ | t <sub>su(2)</sub> = 12 ns†             | $t_{min(2)} = 20 \text{ ns}$ |

| $t_{pd(3)} = 25 \text{ ns}$ | $t_{su(a)} = 25 \text{ ns}$             | $t_{min(3)} = 25 \text{ ns}$ |

|                             | $t_{SU(b)} = 25 \text{ ns}$             | $t_{min(c)} = 25 \text{ ns}$ |

#### **INTERNAL NODE NUMBERS**

| Q0-Q7 | RESET 25-32 | P0-P15 | SET 33-48    |

|-------|-------------|--------|--------------|

| C0    | 65          |        | RESET 49- 54 |

| C1    | 66          |        |              |

<sup>†</sup> Use tsu = 20 ns for applications where the setup time for  $S/R \downarrow$  inputs are required.

# diagnostics

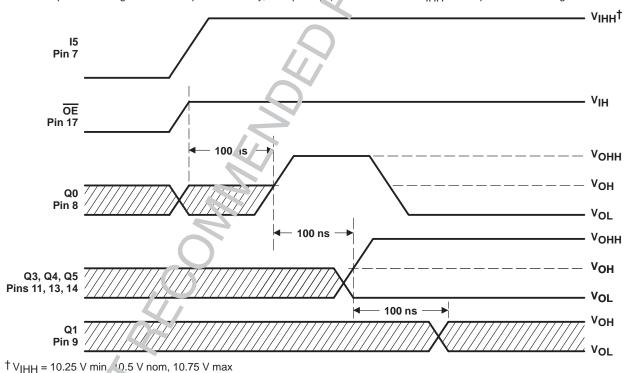

A diagnostic mode is provided with these devices that allows the user to inspect the contents of the state registers. The step-by-step procedures required to use the diagnostics follow.

- Step 1. Disable all outputs by taking pin 17 (OE) high (c. e Note 4).

- Step 2. Take pin 8 (Q0) to V<sub>IHH</sub> to enable the diagnostics test sequence.

- Step 3. Apply appropriate levels of voltage to pir 5 11 (Q3), 13 (Q4), and 14 (Q5) to select the desired state register (see Table 1).

The voltage level monitored on pin 9 will indicate the state of the selected state register.

NOTE 4: If pin 17 is being used as an input to the array, then pin 7 (1) r ust be taken to VIHH before pin 17 is taken high.

Figure 2. Diagnostics Waveforms

Table 1. Addressing State Registers

During Diagnostics<sup>†</sup>

| REGISTE | R BINARY | BURIED REGISTER |          |  |

|---------|----------|-----------------|----------|--|

| PIN 11  | PIN13    | PIN 14          | SELECTED |  |

| L       | L        | L               | C1       |  |

| L       | L        | Н               | P15      |  |

| L       | L        | HH              | C0       |  |

| L       | Н        | L               | P14      |  |

| L       | Н        | Н               | P0       |  |

| L       | Н        | HH              | P1       |  |

| L       | HH       | L               | P2       |  |

| L       | HH       | Н               | P3       |  |

| L       | HH       | HH              | 1.4      |  |

| Н       | L        | L               | 75       |  |

| Н       | L        | Н               | P6       |  |

| Н       | L        | HH              | 7/       |  |

| Н       | Н        | L               | P8       |  |

| Н       | Н        | Н               | P9       |  |

| Н       | Н        | HH              | P10      |  |

| Н       | HH       | L               | P11      |  |

| Н       | HH       | Н               | P12      |  |

| Н       | НН       | H.H.            | P13      |  |

<sup>†</sup> V<sub>IHH</sub> = 10.25 V min, 10.5 V nc. 10.75 V max

# programming information

Texas Instruments programmable logic devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, also ithms, and the latest information on hardware, software, and firmware are available upon request Information on programmers that are capable of programming Texas Instruments programmable logic is also available, upon request, from the nearest TI sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 997-5666.

# **OR term loading**

As shown in Figure 3 and by the  $f_{max}$  calculations,  $f_{max}$  is affected by the number of terms connected to each OR array line. Theoretically,  $f_{max}$  is calculated as:

$$f_{\text{max}} = \frac{1}{t_{\text{SU}} + t_{\text{pd}} \text{ CLK to Q}}$$

Since the setup time (input or feedback to  $S/R\downarrow$ ) varies with the number of trans connected to each OR array line, (due to capacitance loading)  $f_{max}$  will also vary. Figure 3 illustrates the relationship between the number of terms connected per OR line and the setup time.

Use Figure 3 to determine the worst-case setup time for a particular application. Identify the OR array line with the maximum number of terms connected. Count the number of terms and upe the graph to determine the setup time.

# WORST-CASE SETUP TIME (input or feedback to \$?,↓) vs

Figure 3

SRPS003C - D3090, DECEMBER 1987 - REVISED NOVEMBER 1995

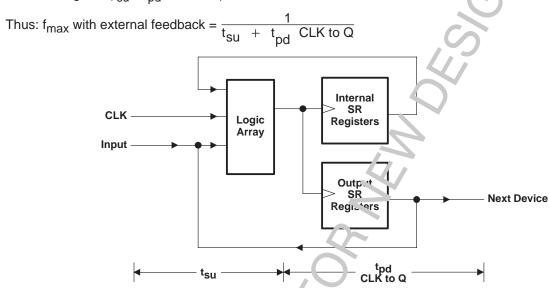

# f<sub>max</sub> with external feedback

The configuration shown is a typical state-machine design with feedback signals sent off chip. This external feedback could go back to the device inputs or to a second device in a multi-chip state machine. The slowest path defining the clock period is the sum of the clock-to-output delay time and the cetup time for the input or feedback signals (t<sub>su</sub> + t<sub>pd</sub> CLK to Q).

Figure 4

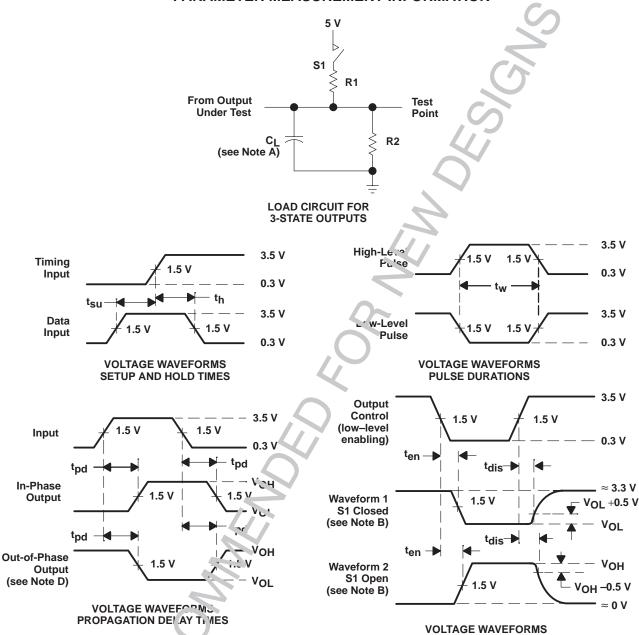

### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $C_L$  includes probe and jig capacitance and is 50 pF for  $t_{pd}$  and  $t_{en}$ , 5 pF for  $t_{dis}$ .

**ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS**

- C. All input pulses he ve the following characteristics:  $PRR \le 1$  MHz,  $t_r = t_f \le 2$  ns, duty cycle = 50%.

- D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

- E. Equivalent pads may be used for testing.

Figure 5. Load Circuit and Voltage Waveforms

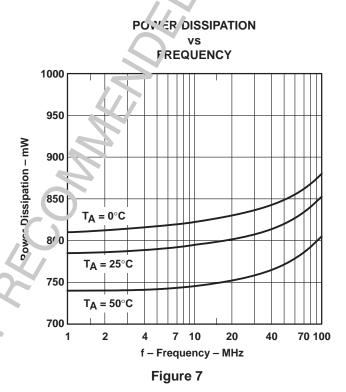

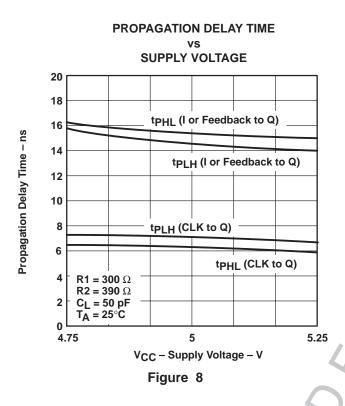

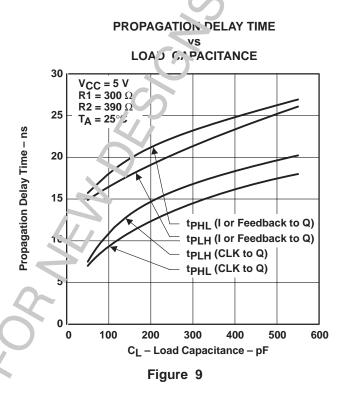

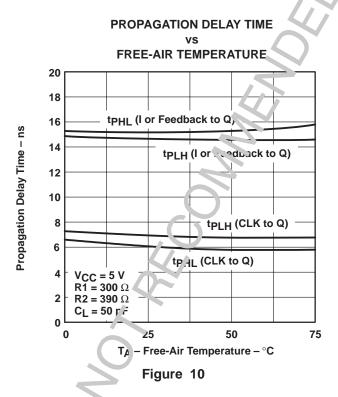

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated