#### TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

#### 524.288-WORD BY 18-BIT SYNCHRONOUS NO-TURNAROUND STATIC RAM

#### **DESCRIPTION**

The TC55VL818FF is a synchronous static random access memory (SRAM) organized as 524,288 words by 18 bits. NtRAM<sup>TM</sup>(no-turnaround SRAM) offers high bandwidth by eliminating dead cycles during the transition from a read to a write and vice versa. All inputs except Output Enable  $\overline{OE}$  and the Snooze pin ZZ are synchronized with the rising edge of the CLK input. A Read operation is initiated by the ADV Address Advanced Input signal; the input from the address pins and all control pins except the  $\overline{OE}$  and ZZ pins are loaded into the internal registers on the rising edge of CLK in the cycle in which ADV is asserted. The output data is available in the same clock cycle as that in which ADV is asserted. Write operations are internally self-timed and are initiated by the rising edge of CLK in the cycle in which ADV is asserted. The input from the address pins and all control pins except the  $\overline{OE}$  and ZZ pins are loaded into the internal registers on the rising edge of CLK in the cycle in which ADV is asserted. Input data is loaded in the cycle following the cycle in which ADV is asserted. Byte Write Enables ( $\overline{BW1}$  to  $\overline{BW2}$ ) allow from one to two Byte Write operations to be performed. A 2-bit burst address counter and control logic are integrated into this SRAM. The TC55VL818FF uses a single power supply (3.3 V) or dual power supplies (3.3 V for core and 2.5 V for output buffer) and is available in a 100-pin low-profile plastic QFP (LQFP).

#### **FEATURES**

- Organized as 524,288 words by 18 bits

- Fast cycle time of 12 ns minimum (83 MHz maximum)

- Fast access time of 9 ns maximum (from clock edge to data output)

- No-turnaround operation with flow-through data output

- 2-bit burst address counter (support for interleaved or linear burst sequences)

- Synchronous self-timed Write

- Byte Write control

- Snooze mode pin (ZZ) for power down

- LVTTL-compatible interface

- Single power supply (3.3 V) or Dual power supplies (3.3 V for core and 2.5 V for output buffer)

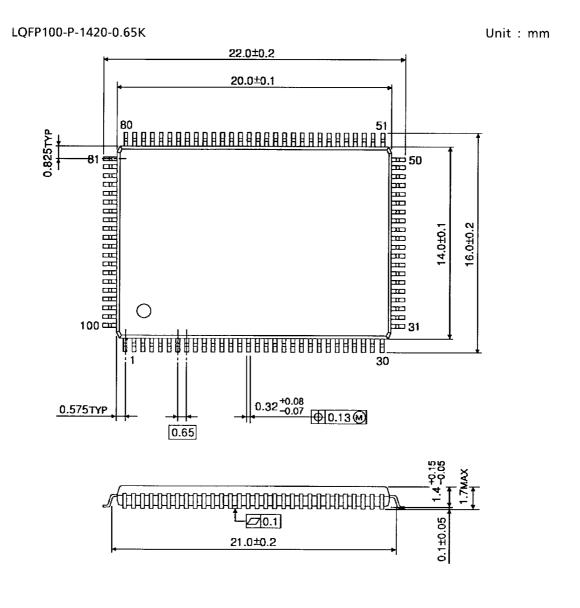

- Available in 100-pin LQFP package (LQFP100-P-1420-0.65K; pitch:0.65 mm, height:1.6 mm, weight:0.56 grams (typical))

#### PIN ASSIGNMENT (TOP VIEW)

#### NC 11 1 NC 12 NC 13 VDDQ 14 97 95 93 91 89 87 85 83 81 79 III NC 78 III NC 100 98 94 92 90 88 86 84 74 I/O9 73 III I/O8 VDDQ III VDD III 68 11 1/O5 67 11 Vss 66⊞ Vss 16 65 VDD 64 ZZ Vss | 17 I/O14 | 18 I/O15 | 19 VDDQ | 20 63 1/04 62 I/O3 61 VDDQ VSSQ 21 I/O16 22 I/O17 23 I/O18 24 NC 25 VSSQ 22 VSSQ 22 60III Vssc 59 I/O2 58 I/O1 56Ⅲ NC 55 Wssq VDDQ 27 NC 28 54TTT VDDG 29 32 34 36 38 40 42 44 46 48 50 30 31 33 35 37 39 41 43 45 47 49

#### **PIN NAMES**

| CLK                | Clock Input                    |

|--------------------|--------------------------------|

| A0 to A18          | Address Inputs                 |

| CE, CE2, CE2       | Chip Enable Inputs             |

| ŌĒ                 | Output Enable Input            |

| WE                 | Write Enable input             |

| BW1 to BW2         | Byte Write Enable              |

| ADV                | Address Advance Input          |

| CKE                | Clock Enable                   |

| ZZ                 | Snooze Input                   |

| I/O1 to I/O18      | Data Inputs/Outputs            |

| MODE               | Mode select Input              |

| NC                 | No Connection                  |

| NU                 | Not Usable                     |

| $V_{DD}$           | Power Supply for Core          |

| $V_{\mathrm{DDQ}}$ | Power Supply for Output Buffer |

| V <sub>SS</sub>    | Ground for Core                |

| $V_{\rm SSQ}$      | Ground for Output Buffer       |

| TM                 | ·                              |

Note: NtRAM M and No-Turnaround Random Access Memory are trademarks of Samsung Electronics Co., Ltd..

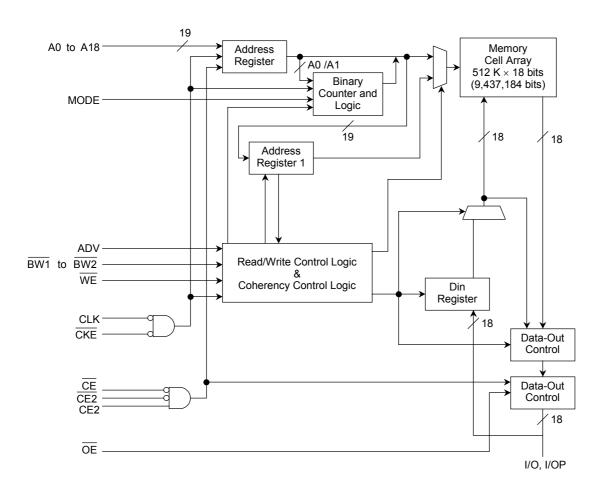

# **BLOCK DIAGRAM**

# PIN DESCRIPTIONS

| PIN NUMBER                                                                  | SYMBOL     | TYPE                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 89                                                                          | CLK        | Input<br>(NA)           | Clock Input  All synchronous input signals are registered on the rising edge of CLK. When the chip is enabled, address inputs and control pins except for OE and ZZ must meet the specified setup and hold times with respect to the CLK rising edge.                                                                                                         |

| 37, 36, 35, 34, 33, 32, 100, 99, 82, 81, 44, 45, 46, 47, 48, 49, 50, 83, 80 | A0 to A18  | Input<br>(synchronous)  | Address Inputs  These address inputs are registered on the rising edge of CLK.  When the chip is enabled, address inputs must meet the specified setup and hold times with respect to the CLK rising edge.                                                                                                                                                    |

| 98                                                                          | CE         | Input<br>(synchronous)  | Chip Enable Input This active-Low signal controls the chip status (enabled or disabled). It is sampled only when a new external address is loaded.                                                                                                                                                                                                            |

| 92                                                                          | CE2        | Input<br>(synchronous)  | Chip Enable Input This active-Low signal controls the chip status (enabled or disabled). It is sampled only when a new external address is loaded.                                                                                                                                                                                                            |

| 97                                                                          | CE2        | Input<br>(synchronous)  | Chip Enable Input This active-High signal controls the chip status (enabled or disabled). It is sampled only when a new external address is loaded.                                                                                                                                                                                                           |

| 86                                                                          | ŌĒ         | Input (asynchronous)    | Output Enable Input This active-Low signal controls all 18 bits of the I/O output buffer.                                                                                                                                                                                                                                                                     |

| 88                                                                          | WE         | Input<br>(synchronous)  | Write Enable Input This active-Low input controls Read/Write operations.                                                                                                                                                                                                                                                                                      |

| 93, 94                                                                      | BW1 to BW2 | Input (synchronous)     | Byte Write Enable These active-Low inputs control Byte Write operations when a Write cycle is active. A Byte Write pin controls I/O pins as follows.  BW1: I/O1 to I/O9  BW2: I/O10 to I/O18                                                                                                                                                                  |

| 85                                                                          | ADV        | Input (synchronous)     | Address Advance Input This is used to load the internal registers with the input from the address and control signals when it is Low on the rising edge of CLK. When it is High, the internal burst address counter is incremented. The external address inputs are ignored when this signal is High.                                                         |

| 87                                                                          | CKE        | Input (synchronous)     | Clock Enable When High, CLK input is ignored and outputs retain the same state.                                                                                                                                                                                                                                                                               |

| 64                                                                          | ZZ         | Input<br>(asynchronous) | Snooze Input This active-High signal is used to place the device into Sleep Mode (Low-Power Standby Mode). When Low, the device remains in the Active state. When High, the device goes into the Sleep state and memory data is retained. After this signal has been de-asserted, the device will wake up when a read or write operation is initiated by ADV. |

| PIN NUMBER                                                                            | SYMBOL        | TYPE                    | DESCRIPTION                                                                                                                     |

|---------------------------------------------------------------------------------------|---------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 58, 59, 62, 63, 68, 69, 72, 73, 74, 8, 9, 12, 13, 18, 19, 22, 23, 24                  | I/O1 to I/O32 | I/O<br>(synchronous)    | Data Input/Output                                                                                                               |

| 31                                                                                    | MODE          | Input<br>(synchronous)  | Mode Select Input This signal selects the burst sequence. When High, the burst sequence is interleaved. When Low, it is linear. |

| 1, 2, 3, 6, 7, 25, 28, 29, 30, 39, 42, 43, 51, 52, 53, 56, 57, 75, 78, 79, 84, 95, 96 | NC            | NC                      | Not Connected                                                                                                                   |

| 38                                                                                    | NU            | Input<br>(asynchronous) | Not Usable                                                                                                                      |

| 15, 16, 41, 65, 91                                                                    | VDD           | Supply                  | Power Supply for Core                                                                                                           |

| 4, 11, 20, 27, 54, 61, 70,<br>77                                                      | VDDQ          | Supply                  | Power Supply for Output Buffers                                                                                                 |

| 14, 17, 40, 66, 67, 90                                                                | VSS           | Ground                  | Ground for Core                                                                                                                 |

| 5, 10, 21, 26, 55, 60, 71,<br>76                                                      | VSSQ          | Ground                  | Ground for Output Buffers                                                                                                       |

#### **OPERATING MODE**

#### (1) Synchronous Input Truth Table

| OPERATION                     | WE | ADV | CE       | BW | Addr. Used | CKE | ZZ | I/O <sup>(5)</sup> |

|-------------------------------|----|-----|----------|----|------------|-----|----|--------------------|

| Read (begin burst)            | Н  | L   | Select   | Х  | External   | L   | L  | Output             |

| Read (continue burst)         | Х  | Н   | Х        | Х  | Internal   | L   | L  | Output             |

| Write (begin burst)           | L  | L   | Select   | L  | External   | L   | L  | Input              |

| Write (continue burst)        | Х  | Н   | Х        | L  | Internal   | L   | L  | Input              |

| NOP/Write Abort (begin burst) | L  | L   | Select   | Н  | Х          | L   | L  | Hi-Z               |

| Write Abort (continue burst)  | Χ  | Н   | Х        | Н  | Internal   | L   | L  | Hi-Z               |

| Deselected                    | Х  | L   | Deselect | Х  | Х          | L   | L  | Hi-Z               |

| Deselect Continue (Note 2)    | Х  | Н   | Х        | Х  | Х          | L   | L  | Hi-Z               |

| Ignore Clock Edge (Note 3)    | Х  | Х   | Х        | Х  | Х          | Н   | L  | Previous value     |

| Snooze                        | Х  | Х   | X        | Х  | Х          | Х   | Н  | Hi-Z               |

Notes: 1. H means logical High and L means logical Low. X means Don't care.

- 2. A Deselect Continue cycle can only be entered if a Deselect cycle is executed before it.

- 3. When the Ignore Clock Edge command is asserted during a Read operation, the output data for the previous cycle still appear on the I/O pins. When the command is asserted during a Write operation, the I/O pins remain at Hi-Z and the Write operation is not executed.

- 4. All synchronous Inputs must exhibit adequate setup and hold times either side of the rising edge of the CLK pin.

- 5. The data output appears in the same cycle as that in which the Read command is asserted. Data input is triggered on the rising edge of CLK in the next following the one in which the Write command is asserted.

- 6. ZZ input is asynchronous, but is included is this table.

#### (2) Write Enable Truth Table

| OPERATION | WE | BW1 | BW2 | I/O1 to I/O9 | I/O10 to I/O18 |

|-----------|----|-----|-----|--------------|----------------|

| Read      | Н  | Х   | Х   | Output       | Output         |

|           | L  | L   | L   | Input        | Input          |

| Write     | L  | L   | Н   | Input        | Hi-Z           |

| vviile    | L  | Н   | L   | Hi-Z         | Input          |

|           | L  | Н   | Н   | Hi-Z         | Hi-Z           |

Notes: 1. H means logical High and L means logical Low. X means Don't care.

#### (3) Asynchronous Inputs Truth Table

| OPERATION           | ŌĒ | ZZ | I/O       |

|---------------------|----|----|-----------|

| Read                | L  | L  | Dout      |

| Neau                | Н  | L  | Hi-Z      |

| Write               | X  | L  | Din, Hi-Z |

| Stop clock (Note 2) | Н  | L  | Hi-Z      |

| Stop Glock (Note 2) | L  | L  | Low-Z     |

| Snooze (Note 3)     | X  | Н  | Hi-Z      |

Notes: 1. H means logical High and L means logical Low. X means Don't care.

- 2. The Stop CLK Mode achieves Low-Power Standby by stopping the input clock.

- 3. The Snooze Mode achieves Low-Power Standby by asserting the ZZ pin.

- 4. The cycle immediately prior to a Snooze brought about by the ZZ pin must be a Read Mode or Deselect Mode cycle.

- 5. Memory data is retained during Snooze Mode cycles.

#### (4) Burst Sequence

| MODE PIN | BURST OPERATION         |

|----------|-------------------------|

| L        | Linear burst order      |

| H or NC  | Interleaved burst order |

## a) Linear Burst Sequence (MODE input = V<sub>SS</sub>)

Bit Order :  $A_{18}$ ----- $A_1$   $A_0$

| 1st Address<br>(external) | 2nd Address<br>(internal) | 3rd Address<br>(internal) | 4th Address<br>(internal) |

|---------------------------|---------------------------|---------------------------|---------------------------|

| XX XX00                   | XX XX01                   | XX XX10                   | XX XX11                   |

| XX XX01                   | XX XX10                   | XX XX11                   | XX XX00                   |

| XX XX10                   | XX XX11                   | XX XX00                   | XX XX01                   |

| XX XX11                   | XX XX00                   | XX XX01                   | XX XX10                   |

## b) Interleaved Burst Sequence (MODE input = V<sub>DD</sub> or NC)

Bit Order: A<sub>18</sub>-----A<sub>1</sub> A<sub>0</sub>

| 1st Address<br>(external) | 2nd Address<br>(internal) | 3rd Address<br>(internal) | 4th Address<br>(internal) |

|---------------------------|---------------------------|---------------------------|---------------------------|

| XX XX00                   | XX XX01                   | XX XX10                   | XX XX11                   |

| XX XX01                   | XX XX00                   | XX XX11                   | XX XX10                   |

| XX XX10                   | XX XX11                   | XX XX00                   | XX XX01                   |

| XX XX11                   | XX XX10                   | XX XX01                   | XX XX00                   |

# **DEVICE OPERATION**

#### (1) Read Operation

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌE | CKE | I/O | OPERATION               |

|-------|---------|----|----|-----|----|----|-----|-----|-------------------------|

| n     | A0      | Н  | Х  | L   | L  | Χ  | L   | Х   | Address & control valid |

| n + 1 | X       | Х  | Х  | Х   | Х  | L  | L   | Q0  | Read out A0             |

Notes: 1. H means logical High and L means logical Low. X means Don't care. Q is data output.

#### (2) Burst Read Operation

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌĒ | CKE | I/O    | OPERATION               |

|-------|---------|----|----|-----|----|----|-----|--------|-------------------------|

| n     | A0      | Н  | Х  | L   | L  | Χ  | L   | Χ      | Address & control valid |

| n + 1 | Х       | Х  | Х  | Н   | Х  | L  | L   | Q0     | Read out A0             |

| n + 2 | Х       | Х  | Х  | Н   | Χ  | L  | L   | Q0 + 1 | Read out A0 + 1         |

| n + 3 | Х       | Х  | Х  | Н   | Х  | L  | L   | Q0 + 2 | Read out A0 + 2         |

| n + 4 | Х       | X  | X  | Η   | X  | L  | L   | Q0 + 3 | Read out A0 + 3         |

| n + 5 | A1      | Н  | Х  | L   | L  | L  | L   | Q0     | Read out A0             |

| n + 6 | Х       | Х  | Х  | Н   | Х  | L  | L   | Q1     | Read out A1             |

| n + 7 | A2      | Н  | Х  | L   | L  | L  | L   | Q1 + 1 | Read out A1 + 1         |

Notes: 1. H means logical High and L means logical Low. X means Don't care. Q is data output.

## (3) Write Operation

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌE | CKE | I/O | OPERATION               |

|-------|---------|----|----|-----|----|----|-----|-----|-------------------------|

| n     | A0      | L  | L  | L   | L  | Х  | L   | Х   | Address & control valid |

| n + 1 | Х       | Х  | Х  | Х   | Х  | Х  | L   | D0  | Write to A0             |

Notes: 1. H means logical High and L means logical Low. X means Don't care. D is data input.

#### (4) Burst Write Operation

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌE | CKE | I/O    | OPERATION               |  |

|-------|---------|----|----|-----|----|----|-----|--------|-------------------------|--|

| n     | A0      | L  | L  | L   | L  | Χ  | L   | Х      | Address & control valid |  |

| n + 1 | Х       | Х  | L  | Н   | Χ  | Χ  | L   | D0     | Write A0                |  |

| n + 2 | Х       | X  | L  | Н   | X  | X  | L   | D0 + 1 | Write A0 + 1            |  |

| n + 3 | Х       | Х  | L  | Н   | Х  | Х  | L   | D0 + 2 | Write A0 + 2            |  |

| n + 4 | Х       | X  | L  | Н   | X  | X  | L   | D0 + 3 | Write A0 + 3            |  |

| n + 5 | A1      | L  | L  | L   | L  | X  | L   | D0     | Write A0                |  |

| n + 6 | Х       | Х  | L  | Н   | Х  | Х  | L   | D1     | Write A1                |  |

| n + 7 | A2      | L  | L  | L   | L  | Χ  | L   | D1 + 1 | Write A1 + 1            |  |

Notes: 1. H means logical High and L means logical Low. X means Don't care. D is data input.

## (5) Read Operation with Clock Enable

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌE | CKE | I/O | OPERATION               |  |

|-------|---------|----|----|-----|----|----|-----|-----|-------------------------|--|

| n     | A0      | Н  | Χ  | L   | L  | Χ  | L   | Χ   | Address & control valid |  |

| n + 1 | Х       | Х  | Х  | Х   | Χ  | Х  | Н   | Х   | Ignore cycle            |  |

| n + 2 | A1      | Н  | Х  | L   | L  | L  | L   | Q0  | A0 read out             |  |

| n + 3 | Х       | Х  | Х  | Х   | Х  | L  | Н   | Q0  | Ignore clock            |  |

| n + 4 | Х       | Х  | Χ  | Χ   | Χ  | L  | Н   | Q0  | Ignore clock            |  |

| n + 5 | A2      | Н  | X  | L   | L  | L  | L   | Q1  | Read out A1             |  |

| n + 6 | A3      | Н  | Х  | L   | L  | L  | L   | Q2  | Read out A2             |  |

| n + 7 | A4      | Н  | Х  | L   | L  | L  | L   | Q3  | Read out A3             |  |

Notes: 1. H means logical High and L means logical Low. X means Don't care. Q is data output.

## (6) Write Operation with Clock Enable

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌĒ | CKE | I/O | OPERATION               |  |

|-------|---------|----|----|-----|----|----|-----|-----|-------------------------|--|

| n     | A0      | L  | L  | L   | L  | Χ  | L   | Χ   | Address & control valid |  |

| n + 1 | Х       | Х  | X  | Х   | X  | Х  | Н   | Х   | Ignore clock            |  |

| n + 2 | A1      | L  | L  | L   | L  | Х  | L   | D0  | Write A0                |  |

| n + 3 | Х       | Х  | Х  | Х   | Х  | Х  | Н   | Х   | Ignore clock            |  |

| n + 4 | Х       | X  | X  | Х   | X  | Х  | Н   | Χ   | Ignore clock            |  |

| n + 5 | A2      | L  | L  | L   | L  | Х  | L   | D1  | Write A1                |  |

| n + 6 | A3      | L  | L  | L   | L  | Х  | L   | D2  | Write A2                |  |

| n + 7 | Х       | Х  | Х  | Х   | Х  | Х  | L   | D3  | Write A3                |  |

Notes: 1. H means logical High and L means logical Low. X means Don't care. D is data input.

## (7) Read Operation with Chip Enable

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌE | CKE | I/O | OPERATION               |

|-------|---------|----|----|-----|----|----|-----|-----|-------------------------|

| n     | A0      | Н  | Х  | L   | L  | Χ  | L   | Х   | Address & control valid |

| n + 1 | Х       | Х  | Х  | L   | Н  | L  | L   | Q0  | Read A0                 |

| n + 2 | A1      | Н  | Х  | L   | L  | Х  | L   | Z   | Deselect                |

| n + 3 | Х       | Х  | Х  | L   | Н  | L  | L   | Q1  | Read A1                 |

| n + 4 | Х       | X  | Х  | L   | Н  | Х  | L   | Z   | Deselect                |

| n + 5 | A2      | Н  | Х  | L   | L  | Х  | L   | Z   | Deselect                |

| n + 6 | Х       | Х  | Х  | L   | Н  | L  | L   | Q2  | Read A2                 |

| n + 7 | Х       | Х  | Х  | L   | Н  | Х  | L   | Z   | Deselect                |

Notes: 1. H means logical High and L means logical Low. X means Don't care. Q is data output. Z means Hi-Z.

## (8) Write Operation with Chip Enable

| CYCLE | ADDRESS | WE | BW | ADV | CE | ŌĒ | CKE | I/O | OPERATION               |

|-------|---------|----|----|-----|----|----|-----|-----|-------------------------|

| n     | A0      | L  | L  | L   | L  | Χ  | L   | Х   | Address & control valid |

| n + 1 | Х       | Х  | Х  | L   | Н  | Х  | L   | D0  | Write A0                |

| n + 2 | A1      | L  | L  | L   | L  | Х  | L   | Z   | Deselect                |

| n + 3 | Х       | Х  | Х  | L   | Н  | Х  | L   | D1  | Write A1                |

| n + 4 | Х       | X  | Х  | L   | Н  | Х  | L   | Z   | Deselect                |

| n + 5 | A2      | L  | L  | L   | L  | Х  | L   | Z   | Deselect                |

| n + 6 | Х       | Х  | Х  | L   | Н  | Х  | L   | D2  | Write A2                |

| n + 7 | Х       | Х  | Х  | L   | Н  | Х  | L   | Z   | Deselect                |

Notes: 1. H means logical High and L means logical Low. X means Don't care. D is data input. Z means Hi-Z.

## **MAXIMUM RATINGS**

| SYMBOL              | RATING                             | VALUE                                           | UNIT |

|---------------------|------------------------------------|-------------------------------------------------|------|

| $V_{DD}$            | Power Supply Voltage               | -0.5 to 4.6                                     | V    |

| $V_{\text{DDQ}}$    | Output Buffer Power Supply Voltage | -0.5 to V <sub>DD</sub> + 0.5 (≤ 4.6 V max)     | V    |

| V <sub>IN</sub>     | Input Terminal Voltage             | −0.5* to 4.6                                    | V    |

| V <sub>I/O</sub>    | Input/Output Terminal Voltage      | -0.5* to V <sub>DDQ</sub> + 0.5** (≤ 4.6 V max) | V    |

| P <sub>D</sub>      | Power Dissipation                  | 1.5                                             | W    |

| T <sub>solder</sub> | Soldering Temperature (10s)        | 260                                             | °C   |

| T <sub>stg</sub>    | Storage Temperature                | -65 to 150                                      | °C   |

| T <sub>opr</sub>    | Operating Temperature              | –10 to 85                                       | °C   |

<sup>\*:</sup> -1.0 V with a pulse width of 20% of  $t_{KC}$  min (3 ns max)

# **DC RECOMMENDED OPERATING CONDITIONS** (Ta = 0° to 70°C)

| SYMBOL           | PARAMETER                              | MIN                   | TYP.     | MAX                     | UNIT |

|------------------|----------------------------------------|-----------------------|----------|-------------------------|------|

| $V_{DD}$         | Power Supply Voltage                   | 3.135                 | 3.3      | 3.465                   | V    |

| $V_{DDQ}$        | Output Buffer Power Supply Voltage     | 3.135                 | 3.3      | 3.465                   | V    |

| V <sub>IH</sub>  | Input High Voltage                     | 2.0                   | _        | V <sub>DD</sub> + 0.3** | V    |

| V <sub>IH1</sub> | Input High Voltage for MODE pin        | V <sub>DD</sub> – 0.3 | $V_{DD}$ | V <sub>DD</sub> + 0.3   | V    |

| V <sub>IL</sub>  | Input Low Voltage                      | -0.3*                 | _        | 0.8                     | V    |

| V <sub>IL1</sub> | Input Low Voltage for MODE and NU pins | -0.3                  | 0.0      | 0.3                     | V    |

<sup>\*:</sup> -0.7 V with a pulse width of 20% of  $t_{KC}$  min (3 ns max)

Note: The NU pin must be low or not connected.

You must not apply a voltage of more than 0.8 V to the NU.

<sup>\*\*:</sup> V<sub>DDQ</sub> + 1.0 V with a pulse width of 20% of t<sub>KC</sub> min (3 ns max)

<sup>\*\*:</sup>  $V_{DDQ}$  + 0.7 V with a pulse width of 20% of  $t_{KC}$  min (3 ns max)

# $\underline{DC\ CHARACTERISTICS}$ (Ta = 0° to 70°C, $V_{DD} = V_{DDQ} = 3.3\ V \pm 5\ \%)$

| SYMBOL            | PARAMETER                        | TEST CONDITIONS                                                                                                                                                                                    | MIN                    | TYP. | MAX | UNIT |

|-------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|------|

| I <sub>IL</sub>   | Input Leakage<br>Current         | V <sub>IN</sub> = 0 to V <sub>DD</sub>                                                                                                                                                             | -1                     | _    | 1   | μΑ   |

| I <sub>NU</sub>   | Input Current<br>(NU pin)        | V <sub>IN</sub> = 0 to 0.3 V                                                                                                                                                                       | -1                     | _    | 1   | μА   |

| I <sub>LO</sub>   | Output Leakage<br>Current        | Device Deselected or Output Deselected, V <sub>OUT</sub> = 0 to V <sub>DDQ</sub>                                                                                                                   | -1                     | _    | 1   | μА   |

| V                 | Output High Voltage              | I <sub>OH</sub> = -8 mA                                                                                                                                                                            | 2.4                    | _    | _   | V    |

| V <sub>OH</sub>   | Output High Voltage              | $I_{OH} = -100 \mu A$                                                                                                                                                                              | V <sub>DDQ</sub> - 0.2 | _    | _   | V    |

|                   | Output Law Valtage               | I <sub>OL</sub> = 8 mA                                                                                                                                                                             | _                      | _    | 0.4 | V    |

| V <sub>OL</sub>   | Output Low Voltage               | I <sub>OL</sub> = 100 μA                                                                                                                                                                           | _                      | _    | 0.2 | V    |

| I <sub>DDO1</sub> | Operating Current                | $\begin{split} I_{OUT} &= 0 \text{ mA}, \\ \text{All Inputs} &= V_{DD} - 0.2 \text{ V}/0.2 \text{ V} \\ \text{Clock} &\geq t_{KC} \text{ Minimum} \end{split}$                                     | _                      | _    | 240 | mA   |

| I <sub>DDO2</sub> | Operating Current (idle)         | Device Deselected $\begin{split} I_{OUT} &= 0 \text{ mA}, \\ All \text{ Inputs} &= V_{DD} - 0.2 \text{ V}/0.2 \text{ V} \\ Clock &\geq t_{KC} \text{ Minimum} \end{split}$                         | _                      |      | 110 | mA   |

| I <sub>DDS1</sub> | Standby Current (TTL level)      | Clock = V <sub>SS</sub><br>All Inputs = V <sub>IH</sub> or V <sub>IL</sub>                                                                                                                         | _                      | _    | 60  | mA   |

| I <sub>DDS2</sub> | Standby Current<br>(MOS level)   | Clock = V <sub>SS</sub><br>All Inputs = V <sub>DD</sub> - 0.2 V or 0.2 V                                                                                                                           | _                      | _    | 10  | mA   |

| I <sub>DDS3</sub> | Standby Current<br>(Snooze Mode) | $\begin{split} ZZ &\geq V_{DD} - 0.2 \text{ V} \\ \text{All Inputs} &= V_{DD} - 0.2 \text{ V or } 0.2 \text{ V} \\ \text{Clock} &\geq t_{KC} \text{ Minimum} \end{split}$                          | _                      | _    | 10  | mA   |

| I <sub>DDS4</sub> | Standby Current (CKE Mode)       | $\label{eq:continuity} \begin{array}{ll} \overline{CKE} & \geq V_{IH} \\ & \text{All Inputs} = V_{DD} - 0.2 \text{ V or } 0.2 \text{ V} \\ & \text{Clock} \geq t_{KC} \text{ Minimum} \end{array}$ | _                      | _    | 10  | mA   |

Note: Operating Current ( $I_{DDO1}$ ) is specified with 50% Read cycles and 50% Write cycles.

# $\underline{\text{CAPACITANCE}} \text{ (Ta = 25°C, f = 1 .0 MHz)}$

| SYMBOL           | PARAMETER                | TEST CONDITIONS        | MAX | UNIT |

|------------------|--------------------------|------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance        | $V_{IN} = GND$         | 5   | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance | V <sub>I/O</sub> = GND | 7   | pF   |

| C <sub>NU</sub>  | Input Capacitance of NU  | V <sub>IN</sub> = GND  | 10  | pF   |

Note: This parameter is periodically sampled and is not 100% tested.

# <u>AC CHARACTERISTICS</u> (Ta = 0° to 70°C, $V_{DD} = V_{DDQ} = 3.3 \text{ V} \pm 5 \text{ \%}$ )

| SYMBOL            | PARAMETER                   | MIN | MAX              | UNIT |

|-------------------|-----------------------------|-----|------------------|------|

| t <sub>KC</sub>   | CLK Cycle Time              | 12  | _                |      |

| t <sub>KH</sub>   | CLK High Pulse Width        | 4   | _                |      |

| t <sub>KL</sub>   | CLK Low Pulse Width         | 4   | _                |      |

| t <sub>KQV</sub>  | CLK High to Output Valid    | _   | 9                |      |

| t <sub>KQX</sub>  | CLK High to Output Invalid  | 3   | _                |      |

| <sup>t</sup> KQLZ | CLK High to Output Low-Z    | 4   | _                |      |

| <sup>t</sup> KQHZ | CLK High to Output High-Z   | _   | 5                |      |

| t <sub>GQV</sub>  | OE Low to Output Valid      | _   | 5                |      |

| t <sub>GQLZ</sub> | OE Low to Output Low-Z      | 0   | _                |      |

| tgQHZ             | OE High to Output High-Z    | _   | 5                |      |

| t <sub>AS</sub>   | Address Setup Time from CLK | 2   | _                |      |

| t <sub>DS</sub>   | Data Setup Time from CLK    | 1.5 | _                |      |

| t <sub>WS</sub>   | WE Setup Time from CLK      | 2   | _                | ns   |

| tces              | CE Setup Time from CLK      | 2   | _                |      |

| t <sub>ADVS</sub> | ADV Setup Time from CLK     | 2   | _                |      |

| t <sub>BWS</sub>  | BW Setup Time from CLK      | 2   | _                |      |

| tckes             | CKE Setup Time from CLK     | 2   | _                |      |

| t <sub>AH</sub>   | Address Hold Time from CLK  | 0.5 | _                |      |

| t <sub>DH</sub>   | Data Hold Time from CLK     | 0.5 | _                |      |

| t <sub>WH</sub>   | WE Hold Time from CLK       | 0.5 | _                |      |

| t <sub>CEH</sub>  | CE Hold Time from CLK       | 0.5 | _                |      |

| t <sub>ADVH</sub> | ADV Hold Time from CLK      | 0.5 | _                |      |

| t <sub>BWH</sub>  | BW Hold Time from CLK       | 0.5 | _                |      |

| t <sub>CKEH</sub> | CKE Hold Time from CLK      | 0.5 | _                |      |

| t <sub>ZZ</sub>   | ZZ High to Input Ignored    | 0   | 2t <sub>KC</sub> |      |

| tzzr              | ZZ Low to Input Sampled     | 0   | 2t <sub>KC</sub> |      |

| tzzhz             | ZZ High to Output High-Z    | 0   | 2t <sub>KC</sub> |      |

| tzzlz             | ZZ Low to Output Low-Z      | 0   | _                |      |

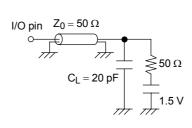

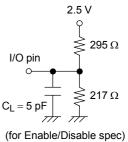

# **AC TEST CONDITIONS**

| PARAMETER                                    | TEST CONDITION              |

|----------------------------------------------|-----------------------------|

| Input Pulse Level                            | 3.0 V/ 0.0 V                |

| Input Pulse Rise and Fall Time               | 1 V/ns (20%/80%)            |

| Input Timing Measurement<br>Reference Level  | 1.5 V                       |

| Output Timing Measurement<br>Reference Level | 1.5 V                       |

| Output Load                                  | As shown in Fig.1 and Fig.2 |

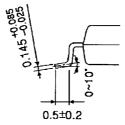

Fig.1:AC test load

Fig.2:AC test load

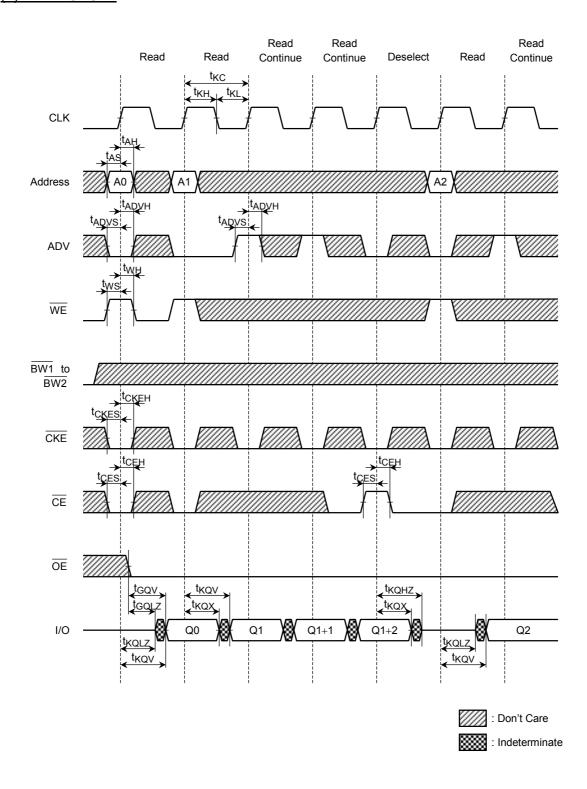

## **TIMING DIAGRAMS**

**TOSHIBA**

## (1) READ CYCLE

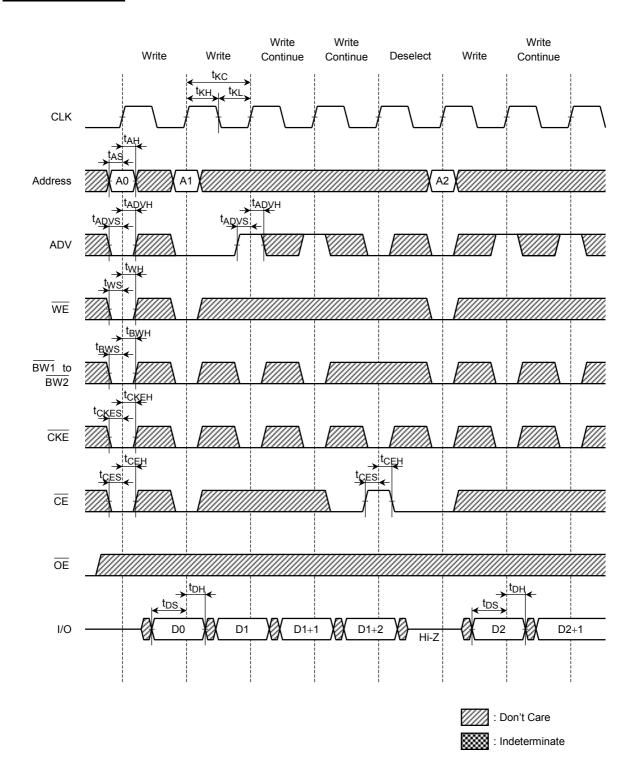

# (2) WRITE CYCLE

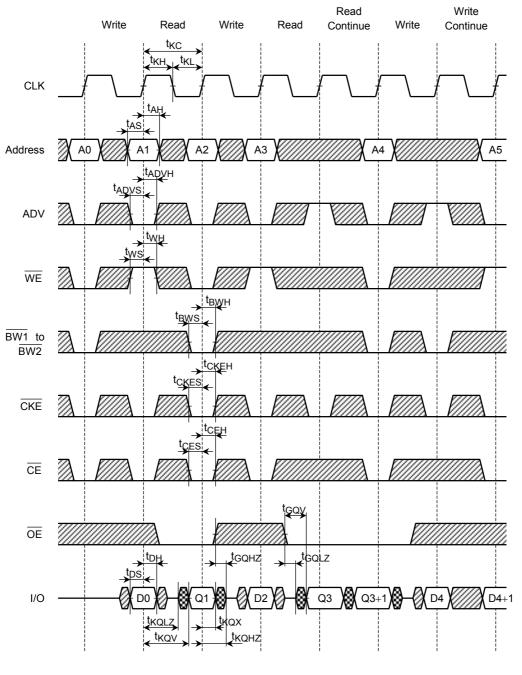

## (3) WRITE/READ CYCLE

: Don't Care

: Indeterminate

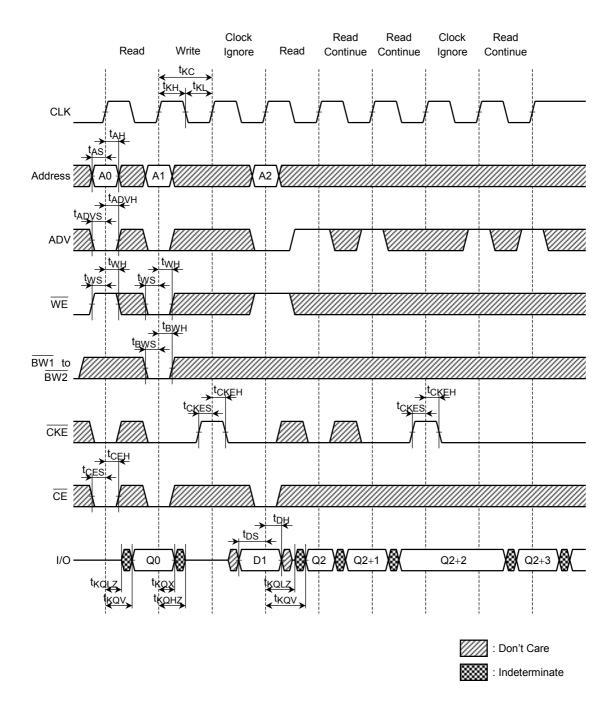

# (4) CLOCK IGNORE CYCLE

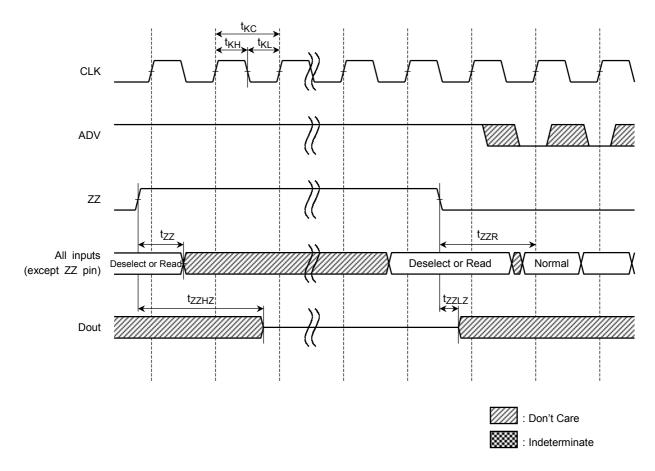

# (5) SNOOZE CYCLE

Notes: 1. The cycle immediately prior to a Snooze brought about by the ZZ pin must be a Read cycle or Deselect cycle.

2. Memory data is retained during Snooze cycles.

- Notes: 1. Do not apply opposite data polarity to the I/O pins when they are in the output state.

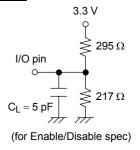

- 2. Output enable and output disable times are specified as follows using the output load shown in Fig.1.

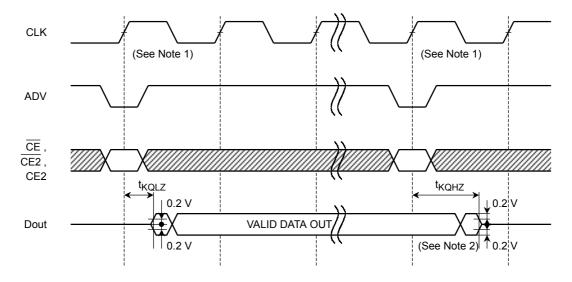

#### (A) tkqlz, tkqhz

- Notes: 1. Input states are defined in the Synchronous Input Truth Table.

- 2. When the device is deselected, the output goes into a high impedance state in the present clock cycle regardless of  $\overline{\text{OE}}$  .

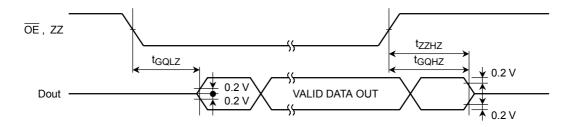

#### (B) tgqlz, tgqhz, tzzhz

# **V<sub>DDQ</sub>** = 2.5 V Interface specification

# **DC RECOMMENDED OPERATING CONDITIONS** (Ta = 0° to 70°C)

| SYMBOL           | PARAMETER                                       | MIN                   | TYP.     | MAX                       | UNIT |

|------------------|-------------------------------------------------|-----------------------|----------|---------------------------|------|

| $V_{DD}$         | Power Supply Voltage                            | 3.135                 | 3.3      | 3.465                     | V    |

| $V_{DDQ}$        | Output Buffer Power Supply Voltage              | 2.375                 | 2.5      | 2.9                       | V    |

| V                | Input High Voltage for Address and Control pins | 1.7                   | _        | V <sub>DD</sub> + 0.3**   | V    |

| V <sub>IH</sub>  | Input High Voltage for I/O pins                 | 1.7                   | _        | V <sub>DDQ</sub> + 0.3*** | V    |

| V <sub>IH1</sub> | Input High Voltage for MODE pin                 | V <sub>DD</sub> – 0.3 | $V_{DD}$ | V <sub>DD</sub> + 0.3     | V    |

| V <sub>IL</sub>  | Input Low Voltage                               | -0.3*                 | _        | 0.7                       | V    |

| V <sub>IL1</sub> | Input Low Voltage for MODE and NU pins          | -0.3                  | 0.0      | 0.3                       | V    |

<sup>\*: -0.7</sup> V with a pulse width of 20% of t<sub>KC</sub> min (3 ns max)

Note: The NU pin must be low or not connected.

You must not apply a voltage of more than 0.8 V to the NU.

## DC CHARACTERISTICS (Ta = 0° to 70°C, $V_{DD}$ = 3.3 V ± 5 %, $V_{DDQ}$ = 2.375 V to 2.9 V)

| SYMBOL            | PARAMETER                        | TEST CONDITIONS                                                                                                                                                                                              | MIN                    | TYP. | MAX | UNIT |

|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|------|

| I <sub>IL</sub>   | Input Leakage<br>Current         | V <sub>IN</sub> = 0 to V <sub>DD</sub>                                                                                                                                                                       | -1                     | _    | 1   | μΑ   |

| I <sub>NU</sub>   | Input Current<br>(NU pin)        | V <sub>IN</sub> = 0 to 0.3 V                                                                                                                                                                                 | -1                     |      | 1   | μА   |

| I <sub>LO</sub>   | Output Leakage<br>Current        | Device Deselected or Output Deselected, $V_{OUT} = 0$ to $V_{DDQ}$                                                                                                                                           | -1                     | l    | 1   | μА   |

| V <sub>OH</sub>   | Output High Voltage              | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                                     | 1.7                    |      |     | V    |

|                   |                                  | $I_{OH} = -100 \mu A$                                                                                                                                                                                        | V <sub>DDQ</sub> - 0.2 | _    | _   |      |

| V <sub>OL</sub>   | Output Low Voltage               | I <sub>OL</sub> = 2 mA                                                                                                                                                                                       | _                      |      | 0.7 | V    |

|                   |                                  | $I_{OL} = 100 \mu A$                                                                                                                                                                                         | _                      |      | 0.2 |      |

| I <sub>DDO1</sub> | Operating Current                | $\begin{split} I_{OUT} &= 0 \text{ mA}, \\ \text{All Inputs} &= V_{DD} - 0.2 \text{ V}/0.2 \text{ V} \\ \text{Clock} &\geq t_{KC} \text{ Minimum} \end{split}$                                               |                        | _    | 240 | mA   |

| I <sub>DDO2</sub> | Operating Current (idle)         | Device Deselected $\begin{split} I_{OUT} &= 0 \text{ mA}, \\ All \text{ Inputs} &= V_{DD} - 0.2 \text{ V}/0.2 \text{ V} \\ Clock &\geq t_{KC} \text{ Minimum} \end{split}$                                   |                        | _    | 110 | mA   |

| I <sub>DDS2</sub> | Standby Current<br>(MOS level)   | Clock = V <sub>SS</sub><br>All Inputs = V <sub>DD</sub> - 0.2 V or 0.2 V                                                                                                                                     | _                      | _    | 10  | mA   |

| I <sub>DDS3</sub> | Standby Current<br>(Snooze Mode) | $\begin{split} ZZ &\geq V_{DD} - 0.2 \text{ V} \\ \text{All Inputs} &= V_{DD} - 0.2 \text{ V or } 0.2 \text{ V} \\ \text{Clock} &\geq t_{KC} \text{ Minimum} \end{split}$                                    | _                      | _    | 10  | mA   |

| I <sub>DDS4</sub> | Standby Current (CKE Mode)       | $\label{eq:cke} \begin{array}{ll} \overline{\text{CKE}} & \geq \text{V}_{IH} \\ \text{All Inputs} = \text{V}_{DD} - 0.2 \text{ V or } 0.2 \text{ V} \\ \text{Clock} \geq t_{KC} \text{ Minimum} \end{array}$ | _                      | _    | 10  | mA   |

Note: Operating Current (I<sub>DDO1</sub>) is specified with 50% Read cycles and 50% Write cycles.

<sup>\*\*:</sup>  $V_{DD}$  + 0.7 V with a pulse width of 20% of  $t_{KC}$  min (3 ns max)

<sup>\*\*\*:</sup>  $V_{DDQ}$  + 0.7 V with a pulse width of 20% of  $t_{KC}$  min (3 ns max)

# <u>AC CHARACTERISTICS</u> (Ta = 0° to 70°C, $V_{DD}$ = 3.3 V $\pm$ 5 %, $V_{DDQ}$ = 2.375 V to 2.9 V)

| SYMBOL            | PARAMETER                   | MIN | MAX              | UNIT |

|-------------------|-----------------------------|-----|------------------|------|

| t <sub>KC</sub>   | CLK Cycle Time              | 12  | _                |      |

| t <sub>KH</sub>   | CLK High Pulse Width        | 4   | _                |      |

| t <sub>KL</sub>   | CLK Low Pulse Width         | 4   | _                |      |

| t <sub>KQV</sub>  | CLK High to Output Valid    | _   | 9                |      |

| t <sub>KQX</sub>  | CLK High to Output Invalid  | 3   | _                |      |

| t <sub>KQLZ</sub> | CLK High to Output Low-Z    | 4   | _                |      |

| t <sub>KQHZ</sub> | CLK High to Output High-Z   | _   | 5                |      |

| t <sub>GQV</sub>  | OE Low to Output Valid      | _   | 5                |      |

| t <sub>GQLZ</sub> | OE Low to Output Low-Z      | 0   | _                |      |

| t <sub>GQHZ</sub> | OE High to Output High-Z    | _   | 5                |      |

| t <sub>AS</sub>   | Address Setup Time from CLK | 2   | _                |      |

| t <sub>DS</sub>   | Data Setup Time from CLK    | 1.5 | _<br>_           |      |

| t <sub>WS</sub>   | WE Setup Time from CLK      |     |                  |      |

| t <sub>CES</sub>  | CE Setup Time from CLK      | 2   | _                |      |

| t <sub>ADVS</sub> | ADV Setup Time from CLK     | 2   | _                | ns   |

| t <sub>BWS</sub>  | BW Setup Time from CLK      | 2   | _                |      |

| t <sub>CKES</sub> | CKE Setup Time from CLK     | 2   | _                |      |

| t <sub>AH</sub>   | Address Hold Time from CLK  | 0.5 | _                |      |

| t <sub>DH</sub>   | Data Hold Time from CLK     | 0.5 | _                |      |

| t <sub>WH</sub>   | WE Hold Time from CLK       | 0.5 | _                |      |

| t <sub>CEH</sub>  | CE Hold Time from CLK       | 0.5 | _                |      |

| t <sub>ADVH</sub> | ADV Hold Time from CLK      | 0.5 | _                |      |

| t <sub>BWH</sub>  | BW Hold Time from CLK       | 0.5 | _                |      |

| t <sub>CKEH</sub> | CKE Hold Time from CLK      | 0.5 |                  |      |

| t <sub>ZZ</sub>   | ZZ High to Input Ignored    | 0   | 2t <sub>KC</sub> |      |

| t <sub>ZZR</sub>  | ZZ Low to Input Sampled     | 0   | 2t <sub>KC</sub> |      |

| t <sub>ZZHZ</sub> | ZZ High to Output High-Z    | 0   | 2t <sub>KC</sub> |      |

| t <sub>ZZLZ</sub> | ZZ Low to Output Low-Z      | 0   |                  |      |

# **AC TEST CONDITIONS**

| PARAMETER                                    | TEST CONDITION              |  |  |

|----------------------------------------------|-----------------------------|--|--|

| Input Pulse Level                            | 2.3 V/ 0.0 V                |  |  |

| Input Pulse Rise and Fall Time               | 1 V/ns (20%/80%)            |  |  |

| Input Timing Measurement<br>Reference Level  | 1.15 V                      |  |  |

| Output Timing Measurement<br>Reference Level | 1.15 V                      |  |  |

| Output Load                                  | As shown in Fig.1 and Fig.2 |  |  |

Fig.1:AC test load

I/O pin  $Z_0 = 50 \Omega$  I/O  $C_L = 20 \text{ pF}$   $C_L = 1.15 \text{ V}$  (for

Fig.2:AC test load

## **PACKAGE DIMENSIONS**

Weight: 0.56 g (typ)

## RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.