# TMC2243 CMOS FIR Filter 10 x 10 Bit. 20 MHz

#### **Features**

- 20 MHz data input and computation rate

- 10 x 10 bit multiplication with 23-bit extended precision sum of products (overflow, plus 16 output and 6 guard bits)

- Up to 3 zero and 3 non-zero stages per device

- Two's complement arithmetic

- 16-bit Sum-In and Sum-Out ports for cascading

- Internal 1/2 LSB rounding

- · All inputs and outputs are registered

- One coefficient update per clock cycle

- Low power consumption CMOS process

- Single +5V supply

Available in 68-pin ceramic pin grid array and 69-pin plastic PGA packages

## **Applications**

- · FIR filters

- Adaptive filters

- Multi-bit correlation

- · One and two dimension video filtering

- Radar signal processors

- · One and two dimension convolution

- Arithmetic element for systolic array processors

## **Description**

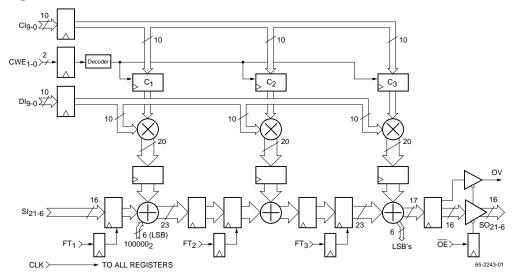

The TMC2243 is a video speed three stage 10 x 10 bit FIR (Finite Impulse Response) filter integrated circuit composed of three registered multiplier-adders concatenated into a one-dimensional systolic array. Utilizing two's complement representation, the TMC2243 accepts one 10-bit data point, updates one 10-bit coefficient, and produces one 16-bit rounded, filtered output point every 50 nanoseconds.

The TMC2243 has features which facilitate longer FIR filters: a 16-bit SUM-In port and user programmable pipeline registers. Enabling these registers allows the insertion of a zero-coefficient stage before each regular filter stage for up to six stages per TMC2243. Larger FIR filters can be built by

cascading Sum-In and Sum-Out.

Coefficients are stored in 3 registers and are addressed via the 2-bit Write Enable control, allowing one coefficient to be changed per clock cycle. All Data, Sum-In, Sum-Out and instruction inputs are registered on the rising edge of clock.

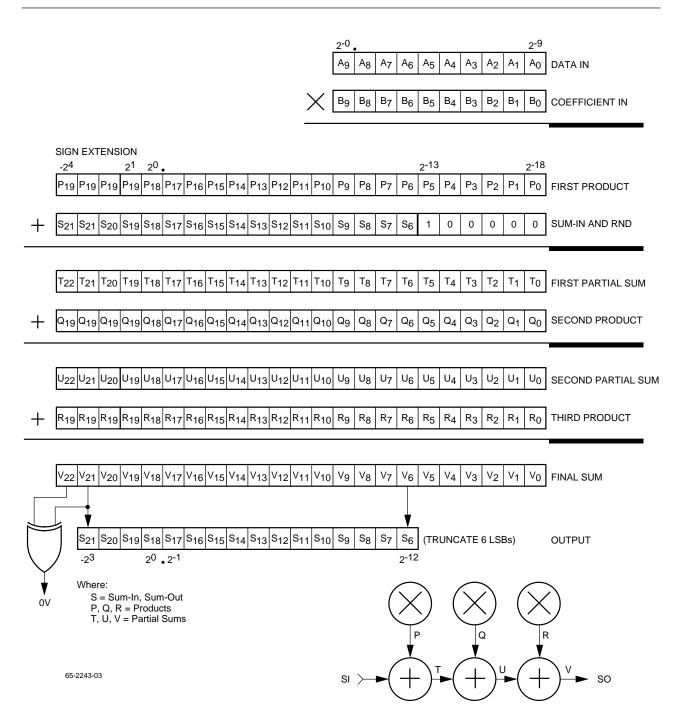

The 16 bits below the MSB of the 23-bit internal summation path are available at the SUM-In and Sum-Out ports. Six bits of cumulative word growth are provided internally. Data Overflow is indicated by an output flag.

# **Block Diagram**

# **Functional Description**

#### **General Information**

The TMC2243 consists of three identical arithmetic cells, each of which contains a 10 x 10 two's complement multiplier and a 23-bit adder. Each cell receives the current data (DI) from the Data input register, multiplies it by a locally stored Coefficient (CI<sub>i</sub>), and adds it to the Sum  $SI_{(i-1)}$  received from the previous cell. The result,

$$SI_i = DI \times CI_i + SI_{(i-1)},$$

then goes to the next cell via two serial pipeline registers. When only one pipeline register is enabled, stages (i-l) and i are sequential. When both registers are enabled, there is a stage with a zero coefficient between them.

The input arithmetic cell receives  $SI_{(i-1)}$  via the 16-bit Sum-In port (registered when  $FT_1 = LOW$ ), filling the six lower bits with 100 000 (1/2 LSB) for internal rounding. The output cell outputs 16 of the MSBs (V<sub>21</sub> through V<sub>6</sub>) of  $SO_i$  through a register to the Sum-Out port. The Overflow flag is set when the final output exceeds 16 bits and resets with the output of the next nonoverflowing result. Sum-Out and the Overflow Flag can be forced to high-impedance with the Output Enable control. See Figure 1.

The two-bit Write Enable control specifies the loading of the three coefficient registers (one per arithmetic cell) with data appearing at the Coefficient Input port.

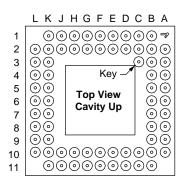

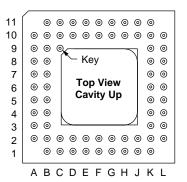

## **Pin Assignments**

## 68 Pin Grid Array – G8 Package 69 Pin Plastic Pin Grid Array – H8 Package

| Pin        | Name             | Pin | Name             | Pin | Name             | Pin | Name             |

|------------|------------------|-----|------------------|-----|------------------|-----|------------------|

| A2         | S06              | В9  | SO20             | F10 | SI11             | K4  | CI2              |

| А3         | S07              | B10 | OV               | F11 | SI <sub>10</sub> | K5  | CI4              |

| A4         | S09              | B11 | GND              | G1  | DI6              | K6  | VDD              |

| <b>A</b> 5 | S011             | C1  | FT <sub>0</sub>  | G2  | DI7              | K7  | CI7              |

| A6         | S013             | C2  | OE               | G10 | SI <sub>13</sub> | K8  | Cl9              |

| A7         | S015             | C10 | VDD              | G11 | SI12             | К9  | SI <sub>20</sub> |

| 8A         | S017             | C11 | VDD              | H1  | DI4              | K10 | GND              |

| A9         | S019             | D1  | FT2              | H2  | DI5              | K11 | SI18             |

| A10        | S0 <sub>21</sub> | D2  | FT1              | H10 | SI <sub>15</sub> | L2  | DI <sub>0</sub>  |

| B1         | VDD              | D10 | SI7              | H11 | SI <sub>14</sub> | L3  | CI <sub>1</sub>  |

| B2         | GND              | D11 | SI <sub>6</sub>  | J1  | DI <sub>2</sub>  | L4  | CI3              |

| В3         | S08              | E1  | CWE <sub>1</sub> | J2  | DI3              | L5  | CI5              |

| B4         | S010             | E2  | CWE0             | J10 | SI17             | L6  | CI6              |

| B5         | S012             | E10 | SI9              | J11 | SI16             | L7  | CI8              |

| B6         | S014             | E11 | SI8              | K1  | GND              | L8  | SI21             |

| B7         | S016             | F1  | DI8              | K2  | DI1              | L9  | SI19             |

| B8         | S018             | F2  | DI9              | К3  | CI0              | L10 | CLK              |

**Note:** Pin C3 is a mechanical orientation pin on the H8 package at manufacturer's option.

65-2243-02

| Pin Name           | Pin Number                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power              | 1                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DD</sub>    | B1, K6, C10, C11                                                                        | Supply Voltage. The TMC2243 operates from a single +5V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND                | B2, K1, K10, B11                                                                        | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Inputs             |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DI9-0              | F2, F1, G2, G1,<br>H2, H1, J2, J1,<br>K2, L2                                            | <b>Data Input.</b> Dlg through Dl <sub>0</sub> is the 10-bit registered Data Input; Dlg is the MSB (sign bit) and Dl <sub>0</sub> is the LSB. Data is in two's complement representation, and is clocked into the data register on each rising edge of clock. See Figure 1.                                                                                                                                                                                                                                                                             |

| Sl <sub>21-6</sub> | L8, K9, L9, K11,<br>J10, J11, H10,<br>H11, G10, G11,<br>F10, F11, E10,<br>E11, D10, D11 | <b>Sum Input.</b> SI <sub>21</sub> through SI <sub>6</sub> is the 16-bit Sum-In port. SI <sub>21</sub> is the MSB (sign bit). Sum-In is truncated to bit SI <sub>6</sub> (plus the 1/2 LSB rounding bit in SI <sub>5</sub> ) and is in two's complement representation. See Figure 1. The Sum-In port is registered, on the rising edge of clock, only when FT <sub>1</sub> =LOW. Unique input setup requirements must be observed when operating in the feedthrough mode (FT <sub>1</sub> = HIGH) See text.                                            |

| Cl9-0              | K8, L7, K7, L6,<br>L5, K5, L4, K4,<br>L3, K3                                            | Coefficient Input. Cl9 through Cl <sub>0</sub> is the 10-bit registered Coefficient Input; Clg is the MSB (sign bit) and Cl <sub>0</sub> is the LSB. Each coefficient and its write enable address (CWE <sub>1-3</sub> ) are registered on the same clock. The coefficient is then latched into the indicated register (C <sub>1-3</sub> ) at the rising edge of the next clock. The contents of this bus are ignored if a coefficient register is not selected (CWE = 00). The format of Cl <sub>9-0</sub> is identical to that of Dl <sub>9-0</sub> . |

| Outputs            |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SO <sub>21-6</sub> | A10, B9, A9, B8,<br>A8, B7, A7, B6,<br>A6, B5, A5, B4,<br>A4, B3, A3, A2                | <b>Sum Output.</b> SO <sub>21</sub> through SO <sub>6</sub> is the three-state 16-bit registered Sum-Out port; SO <sub>21</sub> is the MSB (sign bit). For maximum precision, the internal products and accumulations are 23 bits but Sum-Out is internally truncated to 16 bits, and excludes the overflow bit and the 6 LSBs. The format is identical to that of SI <sub>21-6</sub> . See Figure 1.                                                                                                                                                   |

| Clock              |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLK                | L10                                                                                     | <b>Master Clock.</b> The TMC2243 has a single clock input. The rising edge of CLK strobes all enabled registers. All timing specifications are referenced to the rising edge of clock.                                                                                                                                                                                                                                                                                                                                                                  |

| Controls           |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CWE <sub>1-0</sub> | E1, E2                                                                                  | Coefficient Write Enable. The two bits of the registered Coefficient Write Enable control indicate which of the coefficient registers is to receive a new coefficient at the beginning of the next clock cycle.                                                                                                                                                                                                                                                                                                                                         |

|                    |                                                                                         | CWE <sub>1-0</sub> Coefficient Register Selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    |                                                                                         | 0 0 Holds all coefficients unchanged. 0 1 C <sub>1</sub> 1 0 C <sub>2</sub> 1 1 C <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FT <sub>3-1</sub>  | D1, D2, C1                                                                              | <b>Feedthrough.</b> These registered Feed Through controls select clocked ( $FT_i = LOW$ ) or feedthrough ( $FT_i = HIGH$ ) operation for each of the pipeline registers. Setting $FT_i = LOW$ inserts a zero coefficient stage, or additional register, before the ith non-zero stage.                                                                                                                                                                                                                                                                 |

| ŌĒ                 | C2                                                                                      | Output Enable. Output Enable is a registered three-state enable control which forces the Sum-Out port and Overflow to the high-impedance state when HIGH. These outputs are enabled when $\overline{\text{OE}}$ is LOW.                                                                                                                                                                                                                                                                                                                                 |

| Flags              | ,                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OV                 | B10                                                                                     | <b>Overflow.</b> The Overflow Flag is a registered three-state output which goes HIGH whenever the summation result exceeds 16 bits and is reset to LOW on the next nonoverflowing result.                                                                                                                                                                                                                                                                                                                                                              |

Figure 1. Data Formats and Internal Busing

Because the Sum-In and Sum-Out are truncated by 6 bits relative to the external accumulation pipeline, the TMC2243 rounds internally by adding  $2^{-13}$  to each emerging sum of

products, effecting half-LSB rounding relative to the output format. The chip internally utilizes all lower-order bits, to  $2^{-18}$ .

# **Basic Operation**

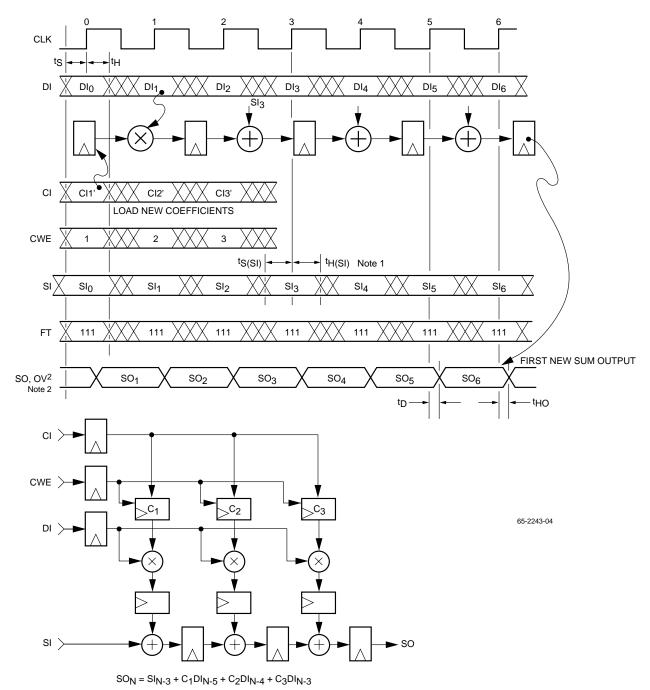

- 1. Setup and Hold requirements for the Sum Input are similar to the other registered inputs when  $FT_1 = LOW$ . See text.

- 2. Sum Out and Overflow timing are shown with  $\overline{OE} = LOW$ .

Figure 2. Timing Diagram Demonstrating Basic Operation with FT<sub>1-3</sub> = HIGH (no zero stages)

The basic equation describing the function of the TMC2243 operating in a fixed state is:

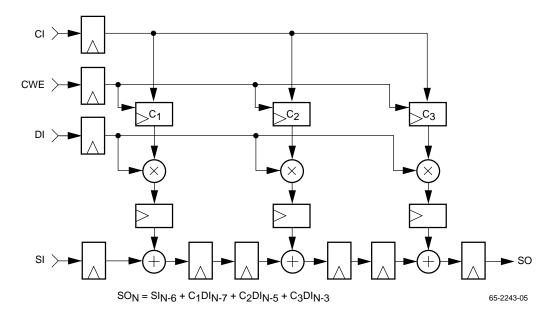

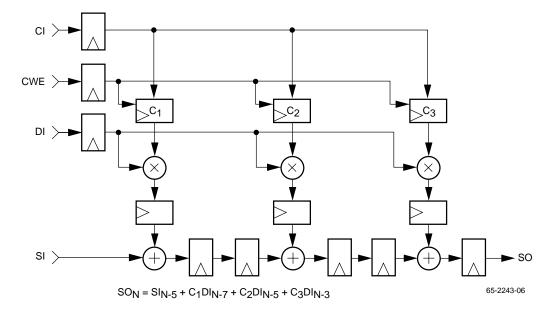

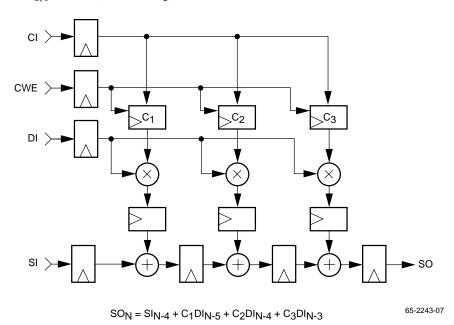

$$\begin{split} SO(N) &= SI(N-6+FT1+FT2+FT3) \\ &+ C_1 \times DI(N-7+FT2+FT3) \\ &+ C_2 \times DI(N-5+FT3) \\ &+ C_3 \times DI(N-3) \end{split}$$

Careful observation of the clock delays shown is basic to construction of a filter algorithm. The operating sequence for the common application with FT1-3 = HIGH (no zero stages) is shown in Figure 2. The simplified block diagram demonstrates the clock stages in this configuration. When FT1 = HIGH, the input feedthrough register is bypassed, and care must be taken to observe the setup requirements on the input of the first adder. Due to the absence of the input register buffer, note that the adder operates on data stable just prior to the arrival of the next clock, and not that setup at the rising edge of the current clock. When FT1 = LOW the input register latches the input data, and the Sum Input follows

setup and hold requirements similar to the other registered inputs of the TMC2243. When  $FT_1 = HIGH$ ,  $t_S(SI)$  is guaranteed to allow 20MHz pipelined operation, assuming that input setup is observed, including cascaded operation. See the AC Characteristics table and Figure 9 in the Applications Discussion section.

Figure 3 shows the effects of the feedthrough registers on filter operation, with two different configurations. The inputs are those presented at the corresponding rising edge of clock, excepting the delayed setup requirements of the Sum Input when  $FT_1 = HIGH$ . The outputs are those available up to and including the corresponding edge of clock. Applications utilizing the TMC2243's ability to modify coefficients dynamically are demonstrated in Figure 4, showing the operation of a typical adaptive filter. Note that the Sum Output will be zero in the first few clock cycles of all examples only if the Coefficient Registers are initialized to zero beforehand.

| Cycle | SI(A) FT <sub>1</sub> = LOW | SI(B) FT <sub>1</sub> = HIGH | DI              | CI               | CWE | SO                                                                                    |

|-------|-----------------------------|------------------------------|-----------------|------------------|-----|---------------------------------------------------------------------------------------|

| 1     | 0                           | 0                            | 0               | K0               | 01  | X                                                                                     |

| 2     | 0                           | 0                            | 0               | K1               | 10  | X                                                                                     |

| 3     | 0                           | 0                            | 0               | K2               | 11  | X                                                                                     |

| 4     | SI <sub>0</sub>             | 0                            | DI <sub>0</sub> | 0                | 00  | X                                                                                     |

| 5     | SI <sub>1</sub>             | SI <sub>0</sub>              | DI <sub>1</sub> | 0                | 00  | 0                                                                                     |

| 6     | SI <sub>2</sub>             | SI <sub>1</sub>              | D1 <sub>2</sub> | 0                | 00  | 0                                                                                     |

| 7     | SI <sub>3</sub>             | SI <sub>2</sub>              | DI <sub>3</sub> | 0                | 00  | $DI_0K_2$                                                                             |

| 8     | SI <sub>4</sub>             | SI <sub>3</sub>              | DI <sub>4</sub> | K <sub>0</sub> ' | 01  | DI <sub>1</sub> K <sub>2</sub>                                                        |

| 9     | SI <sub>5</sub>             | SI <sub>4</sub>              | DI <sub>5</sub> | 0                | 00  | $DI_0K_1 + DI_2K_2$                                                                   |

| 10    | SI <sub>6</sub>             | SI <sub>5</sub>              | DI <sub>6</sub> | K <sub>1</sub> ' | 10  | $SI_0 + DI_1K_1 + DI_3K_2$                                                            |

| 11    | SI7                         | SI <sub>6</sub>              | DI <sub>7</sub> | 0                | 00  | $SI_1 + DI_0K_0 + DI_2K_1 + DI_4K_2$                                                  |

| 12    | SI8                         | SI <sub>7</sub>              | DI <sub>8</sub> | K <sub>2</sub> ' | 11  | $SI_2 + DI_1K_0 + DI_3K_1 + DI_5K_2$                                                  |

| 13    | SI9                         | SI <sub>8</sub>              | DI <sub>9</sub> | 0                | 00  | $SI_3 + DI_2K_0 + DI_4K_1 + DI_6K_2$                                                  |

| 14    | 0                           | SI <sub>9</sub>              | 0               | 0                | 00  | $SI_4 + DI_3K_0 + DI_5K_1 + DI_7K_2$                                                  |

| 15    | 0                           | 0                            | 0               | 0                | 00  | $SI_5 + DI_4K_0 + DI_6K_1 + DI_8K_2$                                                  |

| 16    | 0                           | 0                            | 0               | 0                | 00  | $SI_6 + DI_5K_0' + DI_7K_1' + DI_9K_2'$                                               |

| 17    | 0                           | 0                            | 0               | 0                | 00  | SI <sub>7</sub> + DI <sub>6</sub> K <sub>0</sub> ' + DI <sub>8</sub> K <sub>1</sub> ' |

| 18    | 0                           | 0                            | 0               | 0                | 00  | SI <sub>8</sub> + DI <sub>7</sub> K <sub>0</sub> ' + DI <sub>9</sub> K <sub>1</sub> ' |

| 19    | 0                           | 0                            | 0               | 0                | 00  | SI <sub>9</sub> + DI <sub>8</sub> K <sub>0</sub> ′                                    |

| 20    | 0                           | 0                            | 0               | 0                | 00  | Dl <sub>9</sub> K <sub>0</sub> ′                                                      |

| 21    | 0                           | 0                            | 0               | 0                | 00  | 0                                                                                     |

Figure 3. Impulse Response Filter Operation Sequence with FT2,3 = LOW

SI(A) is the sequence of Sum Input data with  $FT_{1-3} = LOW$  (three zero stages).

SI(B) is the sequence of Sum Input data with  $FT_1 = HIGH$  and  $FT_{2,3} = LOW$  (two zero stages).

| Cycle | SI               | DI               | CI             | CWE | so                                                                                                                 |

|-------|------------------|------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------|

| 0     | SI <sub>0</sub>  | DI <sub>0</sub>  | A <sub>1</sub> | 01  | X                                                                                                                  |

| 1     | SI <sub>1</sub>  | DI <sub>1</sub>  | A <sub>2</sub> | 10  | X                                                                                                                  |

| 2     | SI <sub>2</sub>  | DI <sub>2</sub>  | A <sub>3</sub> | 11  | X                                                                                                                  |

| 3     | SI <sub>3</sub>  | DI <sub>3</sub>  | B <sub>1</sub> | 01  | X                                                                                                                  |

| 4     | SI <sub>4</sub>  | DI <sub>4</sub>  | B <sub>2</sub> | 10  | X                                                                                                                  |

| 5     | SI <sub>5</sub>  | DI <sub>5</sub>  | В3             | 11  | X                                                                                                                  |

| 6     | SI <sub>6</sub>  | DI <sub>6</sub>  | C <sub>1</sub> | 01  | SI <sub>2</sub> + A <sub>1</sub> DI <sub>1</sub> + A <sub>2</sub> DI <sub>2</sub> + A <sub>3</sub> DI <sub>3</sub> |

| 7     | SI <sub>7</sub>  | DI <sub>7</sub>  | C <sub>2</sub> | 10  | SI <sub>3</sub> + A <sub>1</sub> DI <sub>2</sub> + A <sub>2</sub> DI <sub>3</sub> + A <sub>3</sub> DI <sub>4</sub> |

| 8     | SI <sub>8</sub>  | DI <sub>8</sub>  | C <sub>3</sub> | 11  | SI <sub>4</sub> + A <sub>1</sub> DI <sub>3</sub> + A <sub>2</sub> DI <sub>4</sub> + A <sub>3</sub> DI <sub>5</sub> |

| 9     | SI <sub>9</sub>  | DI <sub>9</sub>  |                | 00  | SI <sub>5</sub> + B <sub>1</sub> DI <sub>4</sub> + B <sub>2</sub> DI <sub>5</sub> + B <sub>3</sub> DI <sub>6</sub> |

| 10    | SI <sub>10</sub> | DI <sub>10</sub> |                | 00  | SI <sub>6</sub> + B <sub>1</sub> DI <sub>5</sub> + B <sub>2</sub> DI <sub>6</sub> + B <sub>3</sub> DI <sub>7</sub> |

| 11    | SI <sub>11</sub> | DI <sub>11</sub> |                | 00  | $SI_7 + B_1DI_6 + B_2DI_7 + B_3DI_8$                                                                               |

| 12    | SI <sub>12</sub> | DI <sub>12</sub> |                | 00  | $SI_8 + C_1DI_7 + C_2DI_8 + C_3DI_9$                                                                               |

| 13    | SI <sub>13</sub> | DI <sub>13</sub> |                | 00  | $SI_9 + C_1DI_8 + C_2DI_9 + C_3DI_{10}$                                                                            |

Figure 4. Typical Adaptive Filter Operation Sequence

with  $FT_1 = LOW$  and  $FT_{2, 3} = HIGH$  (one zero stage)

# **Equivalent Circuits and Transition Levels**

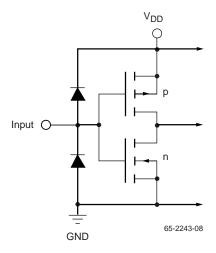

Figure 5. Equivalent Input Circuit

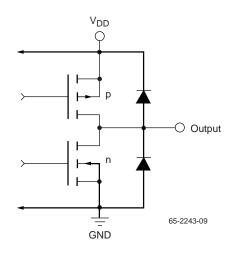

Figure 6. Equivalent Output Circuit

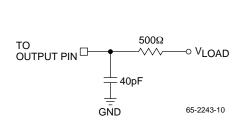

Figure 7. Test Load

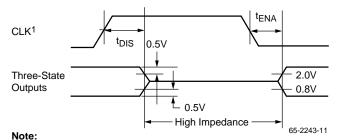

1. Assumes  $\overline{OE}$  has gone LOW, within the Input Setup requirements.

Figure 8. Transition Levels for Three-State Measurements

# Absolute Maximum Ratings (beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min  | Max       | Unit |

|----------------------------------------------------------------|------|-----------|------|

| Supply Voltage                                                 | -0.5 | 7.0       | V    |

| Input Voltage                                                  | -0.5 | VDD + 0.5 | V    |

| Output Applied Voltage <sup>2</sup>                            | 0.5  | VDD + 0.5 | V    |

| Output Forced Current <sup>3,4</sup>                           | -1.0 | 6.0       | mA   |

| Short circuit duration (single output in HIGH state to ground) |      | 1         | sec  |

| Operating, Case Temperature                                    | -60  | 130       | °C   |

| Operating, Junction Temperature                                |      | 175       | °C   |

| Storage Temperature                                            | -65  | 150       | °C   |

| Lead Soldering Temperature (10 seconds)                        |      | 300       | °C   |

- 1. Absolute maximum ratings are limiting values applied individually while all parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range, and measured with respect to GND.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

# **Operating Conditions**

|        |                                     |                                               |      | Te      | mperat | ure Rar | nge    |      |       |

|--------|-------------------------------------|-----------------------------------------------|------|---------|--------|---------|--------|------|-------|

|        |                                     |                                               |      | Standar | d      | E       | xtende | d    |       |

| Param  | eter                                | Test Conditions                               | Min  | Nom     | Max    | Min     | Nom    | Max  | Units |

| VDD    | Supply Voltage                      |                                               | 4.75 | 5.0     | 5.25   | 4.5     | 5.0    | 5.5  | V     |

| VIL    | Input Voltage, Logic LOW            |                                               | 2.0  |         |        | 2.0     |        |      | V     |

| VIH    | Input Voltage, Logic HIGH           |                                               |      |         | 0.8    |         |        | 0.8  | V     |

| loL    | Output Current, Logic LOW           |                                               |      |         | 4.0    |         |        | 4.0  | mA    |

| Іон    | Output Current, Logic HIGH          |                                               |      |         | -2.0   |         |        | -2.0 | mA    |

| tCY    | Cycle Time                          | V <sub>DD</sub> = Min                         | 50   |         |        | 50      |        |      | ns    |

| tpwL   | Clock Pulse Width LOW               | V <sub>DD</sub> = Min                         | 20   |         |        | 20      |        |      | ns    |

| tPWH   | Clock Pulse Width HIGH              | V <sub>DD</sub> = Min                         | 20   |         |        | 20      |        |      | ns    |

| ts     | Input Setup Time                    |                                               | 15   |         |        | 20      |        |      | ns    |

| ts(SI) | Input Setup Time                    | Sl <sub>21-6,</sub> FT <sub>1</sub> =<br>HIGH | 25   |         |        | 28      |        |      | ns    |

|        |                                     | FT <sub>1</sub> = LOW                         | 18   |         |        | 20      |        |      | ns    |

| tH     | Input Hold Time                     |                                               | 2    |         |        | 3       |        |      | ns    |

| tH(SI) | Input Hold Time, SI <sub>21-6</sub> |                                               | 5    |         |        | 5       |        |      | ns    |

| TA     | Ambient Temperature, Still Air      |                                               | 0    |         | 70     |         |        |      | °C    |

| TC     | Case Temperature                    |                                               |      |         |        | -55     |        | 125  | °C    |

# **DC** Characteristics<sup>1</sup>

|                |                                             |                                                                    | Temp |      | ure Rar | nge  |       |

|----------------|---------------------------------------------|--------------------------------------------------------------------|------|------|---------|------|-------|

|                |                                             |                                                                    | Stan | dard | Exte    | nded |       |

| Param          | eter                                        | Test Conditions                                                    | Min  | Max  | Min     | Max  | Units |

| IDDQ           | Supply Current, Quiescent                   | V <sub>DD</sub> = Max, V <sub>IN</sub> = OV, <del>OE</del> = HIGH  |      | 15   |         | 15   | mA    |

| IDDU           | Supply Current, Unloaded                    | V <sub>DD</sub> = Max, <del>OE</del> = HIGH                        |      |      |         |      |       |

|                |                                             | f = 20MHz                                                          |      | 90   |         | 90   | mA    |

|                |                                             | f = 10MHz                                                          |      | 48   |         | 48   | mA    |

| ΠL             | Input Current, Logic LOW                    | V <sub>DD</sub> = Max, V <sub>IN</sub> = OV                        | -75  | 75   | -75     | 75   | μΑ    |

| lн             | Input Current, Logic HIGH                   | V <sub>DD</sub> = Max, V <sub>IN</sub> = V <sub>DD</sub>           | -75  | 75   | -75     | 75   | μΑ    |

| VOL            | Output Voltage, Logic LOW                   | V <sub>DD</sub> = Min, I <sub>OL</sub> = Max                       |      | 0.4  |         | 0.4  | V     |

| Vон            | Output Voltage, Logic HIGH                  | V <sub>DD</sub> = Min. I <sub>OH</sub> = Max                       | 2.4  |      | 2.4     |      | V     |

| lozL           | Hi-Z Output Leakage Current,<br>Output LOW  | V <sub>DD</sub> = Max, V <sub>IN</sub> = OV                        | -40  | 40   | -40     | 40   | μА    |

| lozh           | Hi-Z Output Leakage Current,<br>Output HIGH | $V_{DD} = Max, V_{IN} = V_{DD}$                                    | -40  | 40   | -40     | 40   | μА    |

| los            | Short-Circuit Output Current                | VDD = Max, Output HIGH, one pin to ground, one second duration max |      | -150 |         | -150 | mA    |

| Cı             | Input Capacitance                           | T <sub>A</sub> = 25°C, f = 1MHz                                    |      | 10   |         | 10   | pF    |

| C <sub>0</sub> | Input Capacitance                           | T <sub>A</sub> = 25°C, f = 1MHz                                    |      | 10   |         | 10   | pF    |

<sup>1.</sup> Actual test conditions may vary from those shown, but guarantee operation as specified.

### **AC Characteristics**

|       |                                                |                                                 | Temperature Range |                 | nge |      |       |

|-------|------------------------------------------------|-------------------------------------------------|-------------------|-----------------|-----|------|-------|

|       |                                                |                                                 | Stan              | Standard Extend |     | nded |       |

| Paran | neter                                          | Test Conditions                                 | Min               | Max             | Min | Max  | Units |

| tD    | Output Delay                                   | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 40pF |                   | 30              |     | 30   | ns    |

| tDC   | Output Delay, Cascaded                         | VDD = Min, CLOAD = 10pF                         |                   | 20              |     | 20   | ns    |

| tHO   | Output Hold Time                               | V <sub>DD</sub> = Max, C <sub>LOAD</sub> = 40pF | 5                 |                 | 5   |      | ns    |

| tENA  | Three-State Output, Enable Delay <sup>1</sup>  | VDD = Min, CLOAD = 40pF                         |                   | 20              |     | 25   | ns    |

| tDIS  | Three-State Output, Disable Delay <sup>1</sup> | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 40pF |                   | 15              |     | 20   | ns    |

#### Note:

1. All transitions are measured at a 1.5V level except for t<sub>DIS</sub> and t<sub>ENA</sub>.

## **Application Discussion**

## **Loading and Updating of Coefficients**

Because of the TMC2243's internal architecture, its impulse response is  $C_3$ ,  $C_2$ ,  $C_1$ , where  $C_3$  is the rightmost coefficient and  $C_1$  is the leftmost. However, for glitchless performance, coefficients must be updated from left to right:  $C_1$  then  $C_2$  then  $C_3$ .

For example, consider an adaptive filter whose first set of coefficients is  $A_i$ , second set is  $B_i$  and third set is  $C_i$  (Figure 4). First, the TMC2243 is initialized with  $A_i$ . If these are loaded in numerical (left to right) sequence, two of the first three data points can be loaded with them, as shown in Figure 4. Immediately after the third coefficient is loaded, the first coefficient of the next set can be loaded, if desired, along with the third data point.

**Table 1. Impulse Response**

| FT <sub>3-1</sub> |                | Response       |                |                |                |   |  |

|-------------------|----------------|----------------|----------------|----------------|----------------|---|--|

| 000               | C <sub>3</sub> | 0              | C <sub>2</sub> | 0              | C <sub>1</sub> | 0 |  |

| 001               | C <sub>3</sub> | 0              | C <sub>2</sub> | 0              | C <sub>1</sub> |   |  |

| 010               | C <sub>3</sub> | 0              | C <sub>2</sub> | C <sub>1</sub> | 0              |   |  |

| 011               | C <sub>3</sub> | 0              | C <sub>2</sub> | C <sub>1</sub> |                |   |  |

| 100               | C <sub>3</sub> | C <sub>2</sub> | 0              | C <sub>1</sub> | 0              |   |  |

| 101               | C <sub>3</sub> | C <sub>2</sub> | 0              | C <sub>1</sub> |                |   |  |

| 110               | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | 0              |                |   |  |

| 111               | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> |                |                |   |  |

#### Notes:

- 1. C<sub>3</sub> is she rightmost coefficient, C<sub>1</sub> is the leftmost

- FT<sub>1</sub> is relevant only it SUMIN is used. When multiple chips are cascaded, FT<sub>1</sub> LOW places a zero stage between their concatenated impulse responses.

### **Building Longer Filters**

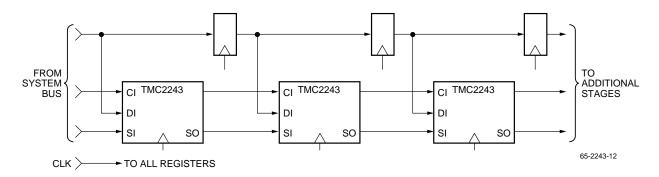

To build a filter of more than three non-zero stages, merely concatenate a series of TMC2243s. The coefficient inputs may be connected to the data bus, a separate common coefficient bus, or separate buses, depending on system architecture, memory and bus resources, and coefficient updating requirements. The data inputs are connected to a common bus. If the first feedthrough register is used (and a zero stage is not desired there), an external register should be inserted in the data input path for proper timing (Figure 9).

The 16-bit Sum-Out port of each TMC2243 is connected to the Sum-In port of the next TMC2243 in the chain; the filter output is the Sum-Out port of the last TMC2243. Since the 6 LSBs of each TMC2243's accumulation pipeline are not output, each TMC2243 incorporates a rounding increment of 1 into the sixth bit, to minimize bias.

When TMC2243s are cascaded in this fashion, the minimum permissible clock period is the sum of the output delay and the Sum-In port's input setup time. When the Input Registers are enabled (that is,  $FT_1 = LOW$ ), full 20MHz performance can be obtained.

All data and coefficient inputs and outputs are two's complement representation, whose relative scaling is presented in the Data Formats table, Figure 1. Although the data values are shown in fractional format, the user can arbitrarily rescale them, as long as consistency is maintained.

Figure 9. Basic Diagram for Stacking the TMC2243 for High–Speed Operation (no zero tap desired between each TMC2243, all FT<sub>1</sub> = LOW)

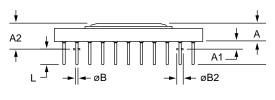

## **Mechanical Dimensions**

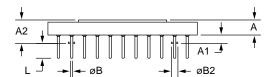

## 68 Lead PGA Package

|        | Inc    | hes   | Millin |       |       |

|--------|--------|-------|--------|-------|-------|

| Symbol | Min.   | Max.  | Min.   | Max.  | Notes |

| A      | .080   | .125  | 2.03   | 3.18  |       |

| A1     | .040   | .060  | 1.02   | 1.52  |       |

| A2     | .115   | .190  | 2.92   | 4.83  |       |

| øΒ     | .017   | .020  | 0.43   | 0.51  |       |

| øB2    | .050 I | NOM.  | 1.27   | NOM.  |       |

| D      | 1.140  | 1.180 | 28.96  | 29.97 |       |

| D1     | 1.000  | BSC   | 25.40  | BSC   |       |

| е      | .100   | BSC   | 2.54   | BSC   |       |

| L      | .120   | .140  | 3.05   | 3.56  |       |

| М      | 1      | 1     | 11     |       | 2     |

| N      | 6      | 8     | 6      | 8     | 3     |

| Р      | .003   | _     | .076   | _     |       |

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Dimension "M" defines matrix size.

- 3. Dimension "N" defines the maximum possible number of pins.

- 4. Controlling dimension: inch.

- 5. Optional index pin.

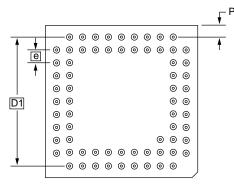

# **Mechanical Dimensions** (continued)

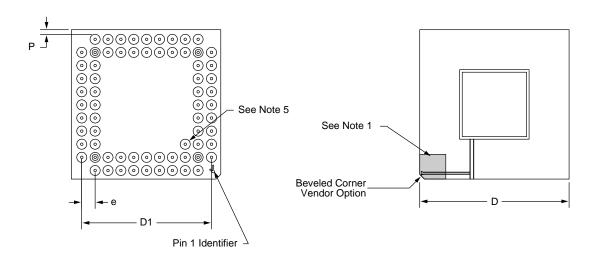

## 69 Lead PGA Package

| Cumbal | Inc    | hes   | Millin | Notes |       |

|--------|--------|-------|--------|-------|-------|

| Symbol | Min.   | Max.  | Min.   | Max.  | Notes |

| А      | .080   | .160  | 2.03   | 4.06  |       |

| A1     | .040   | .060  | 1.01   | 1.53  |       |

| A2     | .125   | .215  | 3.17   | 5.46  |       |

| øΒ     | .016   | .020  | 0.40   | 0.51  | 2     |

| øB2    | .050 l | NOM.  | 1.27   | NOM.  | 2     |

| D      | 1.140  | 1.180 | 28.96  | 29.97 | SQ    |

| D1     | 1.000  | BSC   | 25.40  | BSC   |       |

| е      | .100   | BSC   | 2.54   | BSC   |       |

| L      | .110   | .145  | 2.79   | 3.68  |       |

| М      | 1      | 1     | 11     |       | 3     |

| N      | 6      | 8     | 68     |       | 4     |

| Р      | .003   | _     | .076   | _     |       |

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Pin diameter excludes solder dip finish.

- 3. Dimension "M" defines matrix size.

- 4. Dimension "N" defines the maximum possible number of pins.

- 5. Orientation pin is at supplier's option.

- 6. Controlling dimension: inch.

# **Ordering Information**

| Product Number | Product Number Temperature Range           |             | Package                       | Package Marking |

|----------------|--------------------------------------------|-------------|-------------------------------|-----------------|

| TMC2243G8C     | STD- $T_A = 0^{\circ}C$ to $70^{\circ}C$   | Commercial  | 68 Pin Grid Array             | 2243G8C         |

| TMC2243G8V     | EXT-TC = $55^{\circ}$ C to $125^{\circ}$ C | MIL-STD-883 | 68 Pin Grid Array             | 2243G8V         |

| TMC2243H8C     | STD- $T_A = 0^{\circ}C$ to $70^{\circ}C$   | Commercial  | 69 Pin Plastic Pin Grid Array | 2243H8C         |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com