# T66H0004A

### 80 output LCD Segment/Common Driver IC

# **DESCRIPTION**

The T66H0004A is an LCD driver LSI which is fabricated by low power CMOS high voltage process technology. In segment driver mode, it can be interfaced in 1-bit serial or 4-bit parallel method by the controller. In common driver mode, dual type mode is applicable. And in segment mode application, the power down function reduces power consumption.

### **FEATURES**

- Power supply voltage:+5V±10%,+3V±10%

- Supply voltage for display:6 to  $28V(V_{DD}-V_{EE})$

- 4 bit parallel/1 bit serial data processing (in segment mode)

- Single mode operation/dual mode operation (in common mode)

- Power down function (in segment mode)

- Applicable LCD duty: 1/64 1/256

- High voltage CMOS process

- Bare die , QFP or TQFP available

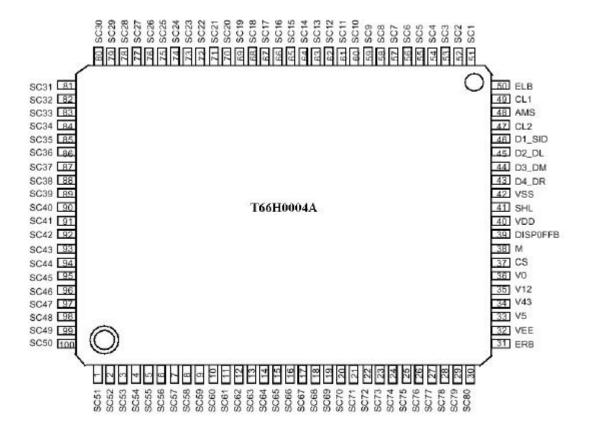

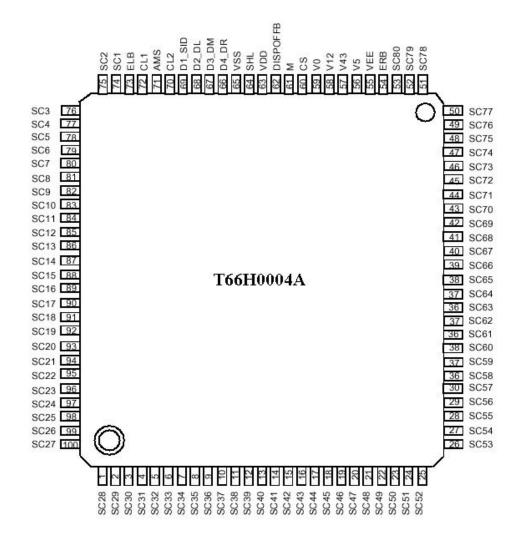

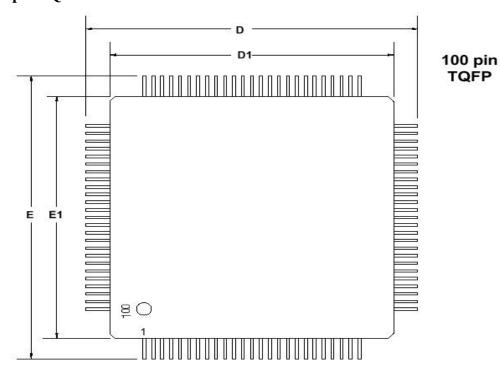

### PACKAGE INFORMATION

QFP 100QFP PACKAGE

## TQFP 100QFP PACKAGE

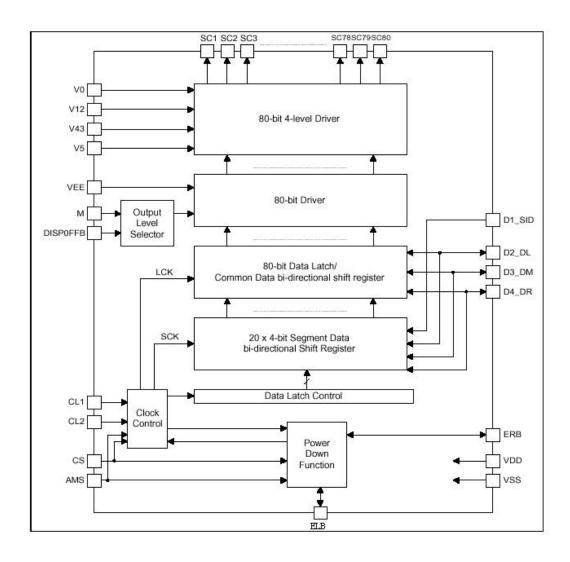

# **BLOCK DIAGRAM**

# **BLOCK DESCRIPTION**

| Name                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                 | COM/SEG |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Clock control                                                            | Generates latch clock(LCK), shift clock(SCK) and control clock timing according to the input of CL1, CL2 and control inputs(CS, AMS). In common driver accolication mode, this block generates the shift clock(LCK) for the common data Bi-directional shift register.                                                                                                                                                   | COM/SEG |

| Data latch control                                                       | Determines the direction of segment data shift, and input data of each Bi-<br>directional shift register. In 4-bit segment data parallel transfer mode, data<br>is shifted by 4-bit unit. In common driver application mode, data is<br>transferred to the common data shift register directly, which disables this<br>block.                                                                                            | SEG     |

| Power down<br>function                                                   | Controls the clock enable state of the current driver according to the input value of enable pin(ELB or ERB). If enable input value is "Low", every clock of the current driver is enabled and the clock control block works. But if enable input is "High", current driver is disabled and the input data value has no effect on the output level. So power consumption can be lowered.                                 | SEG     |

| Output level selector                                                    | Controls the output voltage level according to the input control pin (M and DISPOFFB) (refer to PIN DESCRIPTION).                                                                                                                                                                                                                                                                                                        | COM/SEG |

| 20x4-bit<br>segment data<br>Bi-directional<br>shift register             | Stores output data value by shifting the input values. In 1-bit serial interface mode application, all 80 shift clocks(SCK) are needed to store all the display data. But in 4-bit parallel transfer mode application, only 20 clocks are needed. In common driver application mode, this block does not work.                                                                                                           | SEG     |

| 80-bit data<br>latch/common<br>data Bi-<br>directional<br>shift register | In segment driver application mode, the data from the 20x4-bit segment data shift register are latched for segment driver output. In single-type common driver application,1-bit input data(from DL or DR pin) is shifted and latched by the direction according to the SHL signal input. In dual-type common application mode,80-bit registers are divided by two blocks and controlled independently(refer to NOTE 3). | COM/SEG |

| 80-bit level<br>shifter                                                  | Voltage level shifter block for high voltage part. The inputs of this block are of logical voltage level and the outputs of this block are at high voltage level value. These values are input in to the driver.                                                                                                                                                                                                         | SEG     |

| 80-bit 4-level<br>driver                                                 | Selects the output voltage level according to M and latched data value. If the data value is "High" the driver output is at selected voltage level(V0 or V5), and in the reverse case the driver output value is at the non-selected level (V12 or V43). In segment driver application mode, non-selected output value is V2 or V3. And when in common driver application, this value becomes V1 or V4.                  | SEG     |

# PIN DESCRIPTION

| Pin               | I/O | Name                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Interface  |

|-------------------|-----|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| VDD               |     |                                       | Logical "High" input port(+5V±10%,+3V±10%)                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| Vss               |     | Power supply                          | 0V(GND)                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power      |

| VEE               |     |                                       | Logical "Low" for high voltage part                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

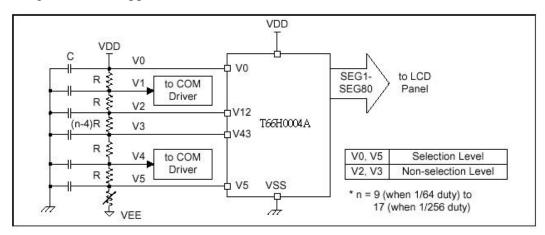

| V0,V12,<br>V43,V5 | Ι   | LCD driver<br>output voltage<br>level | Bias supply voltage input to drive the LCD. Bias voltage divided by the resistance is usually used as a supply voltage source (refer to NOTE 2).                                                                                                                                                                                                                                                                                                              | Power      |

| SC1-SC80          | 0   | LCD driver<br>output                  | Display data output pin which corresponds to the respective latch contents. One of V0,V12,V34 and V5 is selected as a display driving voltage source according to the combination of the latch data level and M signal(refer to NOTE 1).                                                                                                                                                                                                                      | LCD        |

| CL2               | I   | Data shift<br>clock                   | Clock pulse input for the bi-directional shift register.  -In segment driver application mode, the data is shifted to 20x4-bit segment data shift  The clock pulse, which was input when the enable bit(ELB/ERB) is in not active condition, is invalid.  -In common driver application mode, the data is shifted to 80-bit common data bi-directional shift register by the CL1 clock.  Hence, this clock pin is not used (Open or connect this pin to VDD). | Controller |

| М                 | I   | AC signal for LCD driver output       | Alternate signal input pin for LCD driving.  Normal frame inversion signal is input in to this pin.                                                                                                                                                                                                                                                                                                                                                           | Controller |

| CL1               | Ι   | Data latch<br>clock                   | -In segment driver application mode, this signal is used for latching the shift register contents at the falling edge of this clock pulse.  CL1 pulse "High" level initializes power-down function block.  -In common driver application mode, CL1 is used as a shifting clock of common output data.                                                                                                                                                         | Controller |

| DISPOFFB          | I   | Display OFF<br>control                | Control input pin to fix the driver output(SC1-SC80) to V0 level, during "Low" value input. LCD becomes non-selected by V0 level output from every output of segment drivers and every output of common drivers.                                                                                                                                                                                                                                              | Controller |

| CS                | I   | COM/SEG<br>mode control               | When CS="Low",T66H0004A is used as an 80-bit segment driveer.  When CS="High",T66H0004A is set to an 80-bit common driver.                                                                                                                                                                                                                                                                                                                                    | VDD/VSS    |

| AMS               | Ι   | Application mode select               | According to the input value of the AMS and the CS pin, application mode of T66H0004A is differs as shown below.                                                                                                                                                                                                                                                                                                                                              |            |

# Preliminary T66H0004A

|                                      |       |                                                                                  | CS AMS Application mode COM/SEG  0 0 4-bit parallel interface mode  0 1 1-bit serial interface mode  1 0 Single type application mod  1 1 Dual type application mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------|-------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1_SID,<br>D2_DL,<br>D3_DM,<br>D4_DR | I/O   | Display data<br>input/serial<br>input<br>data/left,right<br>data input<br>output | In segment driver application mode, these pins are used as 4-bit data input pin (when 4-bit parallel interface mode: AMS="Low"), or D1_SID is used as serial data input pin and other pins are not used(connect these to VDD)(when 1-bit serial interface mode: AMS="High") -In common driver application mode, the data is shifted from D2_DL(D4_DR) to D4_DR (D2_DL), when in single type interface mode (AMS="Low"). In dual-type application case, the data are shifted from D2_DL and D3_DM(D4_DR and D3_DM) to D4_DR(D2_DL). In each case the direction of the data shift and the connection of data pins are determined by SHL input(refer to NOTE3,NOTE4). |

| SHL                                  | Input | Shift direction control                                                          | When SHL="Low",data is shifted from left to right. When SHL"High",the direction is reversed.(refer to NOTE3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ELB,ERB                              | I/O   | Enable data input/output                                                         | -In segment driver application mode, the internal operation is enabled only when enable input (ELB or ERB) is "Low" (power down function). When several drivers are serially connected, the enable state of each driver is shifted according to the SHL input. Connect these pins as below.  Segment Driver ELB ERB L Output (open Input (VSS) H Input (VSS) Output (open) -In common driver application mode, power down function is not used. Open these pins.                                                                                                                                                                                                   |

| 1.012 1. Output Level Control |                     |                         |          |             |  |  |  |  |  |

|-------------------------------|---------------------|-------------------------|----------|-------------|--|--|--|--|--|

| M                             | Latched data        | Latched data DISPOFFB - |          | I(SC1-SC80) |  |  |  |  |  |

| 171                           | Latched data DISPOF | DISTOFFD                | SEG Mode | COM Mode    |  |  |  |  |  |

| L                             | L                   | Н                       | V12(V2)  | V12(V1)     |  |  |  |  |  |

| L                             | H                   | Н                       | V0       | V5          |  |  |  |  |  |

| Н                             | L                   | Н                       | V43(V3)  | V43(V4)     |  |  |  |  |  |

| Н                             | Н                   | Н                       | V5       | V0          |  |  |  |  |  |

| X                             | X                   | L                       | V0       | V0          |  |  |  |  |  |

**NOTE 1. Output Level Control**

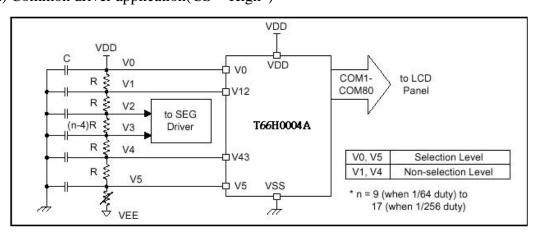

#### **NOTE 2. LCD Driving Voltage Application Circuit**

(1) Segment driver application(CS="Low")

(2) Common driver application(CS="High")

## **NOTE 3. Data Shift Direction according to Control Signals**

(1) When CS="Low" (Segment driver application)

| AMS | SHL                         | Application mode           | Data Direction                          | Input Pin                   |

|-----|-----------------------------|----------------------------|-----------------------------------------|-----------------------------|

| L   | L                           | 4-Bit Parallel             | S S S S S S S S S S S S S S S S S S S   | D1_SID,<br>D2_DL,<br>D3_DM, |

| Н   | Н                           | Data Transfer<br>Mode(SEG) | S S S S S S S S S S S S S S S S S S S   | D4_DR                       |

| Н   | L                           | 1-Bit Serial               | S S S S S C C C C C C C C C C C C C C C | D1_SID                      |

| H - | Data Transfer Mode (SEG)  H |                            | S S S S S S S S S S S S S S S S S S S   | טוב_טוט                     |

# Preliminary T66H0004A

(2) When CS="High"(

| AMS | SHL    | Application                        | Data Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input Pin       |

|-----|--------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| L   | L<br>H | Single-type Application Mode (COM) | Shift Direction  S S S S C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D2_DL D4_DR     |

| Н   | L      | 1-Bit Serial<br>Data Transfer      | Shift Direction   (D2_DL)   (D3_DM)   (D4_DR)   (D | D2_DL,<br>D3_DM |

| п   | Н      | Mode (SEG)                         | S S S C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D4_DR,<br>D3_DM |

### **NOTE 4. Usage of Data Pins**

| COM/SEG     | Application mode                         | SHL |              | Data interface pin |                |             |  |

|-------------|------------------------------------------|-----|--------------|--------------------|----------------|-------------|--|

| (CS pin)    | (AMS pin)                                |     | D1_SID       | D2_DL              | D3_DM          | D4_DR       |  |

| SEG         | 4-bit parallel interface mode(AMS="Low") | X   | D1(input)    | D2(input2)         | D3(input3)     | D4(input4)  |  |

| (CS="Low")  | 1-bit serial interface mode (AMS="High") | X   | X SID(input) |                    | Connect to VDD |             |  |

|             | Single-type application                  | L   | Onan         | DL(input)          | Onan           | DR(output)  |  |

| COM         | mode(AMS="Low")                          | Н   | Open         | DL(output)         | Open           | DR(input)   |  |

| (CS="High") | Dual-type application                    | L   | Open         | DL(input1)         | DM(input2)     | DR(output2) |  |

|             | mode (AMS="high")                        | Н   | Open         | DL(output2)        | DM(input2)     | DR(input1)  |  |

#### **MAXIMUM ABSOLUTE LIMIT**

| Characteristic        | Symbol | Value        | Unit |

|-----------------------|--------|--------------|------|

| Power supply voltage  | VDD    | -0.3 to +7.0 |      |

| Driver supply voltage | Vlcd   | 0 to +30     | V    |

| Input voltage         | Vin    | -0.3 to      | ·    |

| Input voltage         | VIII   | VDD+0.3      |      |

| Operating temperature | Topr   | -30 to +85   |      |

| Storage temperature   | Tstg   | -55 to +150  |      |

<sup>\*</sup>NOTE: Voltage greater than above may do damage to the circuit.

## **ELECTRICAL CHARACTERISTICS**

#### DC CHARACTERISTICS

#### (1) Segment Driver Application

(Vss = 0V, Ta = -30 to +85)

| Characteristic              | Symbol          | Test Condition                 |                               | Min.              | Тур. | Max.                            | Unit |

|-----------------------------|-----------------|--------------------------------|-------------------------------|-------------------|------|---------------------------------|------|

| Operating Voltage           | $V_{DD}$        | -                              | 2.7                           | -                 | 5.5  |                                 |      |

| 1                           | $V_{LCD}$       | $V_{IN} = V_{DD} - V_{EF}$     |                               | 6                 | -    | 28                              | V    |

| Input voltage (1)           | $V_{IH}$        | -                              |                               | $0.8V_{ m DD}$    | -    | $V_{ m DD}$                     | · V  |

|                             | $V_{IL}$        | 1                              |                               | 0                 | -    | $0.2 V_{\scriptscriptstyle DD}$ |      |

| Output voltage (2)          | $V_{OH}$        | $I_{OH} = -0.4 \text{mA}$      |                               | $V_{\rm DD}$ -0.4 | -    | -                               | V    |

|                             | $V_{OL}$        | $I_{OL} = 0.4 \text{mA}$       |                               | -                 | -    | 0.4                             |      |

| Input leakage current 1 (1) | $I_{\rm IL1}$   | $V_{IN} = V_{DD}$ to $Vs$      | s                             | -10               | -    | 10                              | ,, A |

| Input leakage current 2 (3) | $I_{\rm IL2}$   | $V_{IN} = V_{DD}$ to $V_{EI}$  | $V_{IN} = V_{DD}$ to $V_{EE}$ |                   | -    | 25                              | uA   |

| On resistance (4)           | R <sub>on</sub> | $I_{ON} = 100uA$               |                               | 1                 | 2    | 4                               | K    |

|                             | $I_{STBY}$      | F <sub>CL1</sub> =32 KHz M=Vss | Vss pin                       | -                 | ı    | 100                             | uA   |

| Supply current (5)          |                 |                                | $V_{DD} = 5V$                 | -                 | -    | 5                               |      |

| 2 app 3 amount (c)          | $I_{DD}$        | $F_{CL1} = 32KHz$              |                               | -                 | -    | 2                               | mA   |

|                             | $I_{\rm EE}$    | $F_{M} = 80Hz$                 | $V_{\rm DD} = 5V$             | -                 | -    | 500                             | uA   |

#### **NOTES:**

- 1. Applied to Cl1,CL2,ELB,ERB,D1\_SID-D4\_DR,SHL,DISPOFFB,M,CS,AMS pin

- 2. ELB,ERB pin

- 3. V0,V12,V43,V5 pin

4.

$$V_{LCD} = V_{DD} - V_{EE}$$

,  $V0 = V_{DD} = 5V$ ,  $V5 = V_{EE} = -23V$

$$V12 = V_{\rm DD} \ -2/n(V_{\rm LCD}), V43 = V_{\rm EE} \ +2/n(V_{\rm LCD}), n = 17(1/256 \ duty, 1/17 \ bias)$$

5. V0=

$$V_{DD}$$

,V12=1.71V( $V_{DD}$ =5V) or -0.06V( $V_{DD}$ =3V)

$$V43\text{=-}19.71V(V_{DD}\text{=-}5V) \text{ or } -19.94V(V_{DD}\text{=-}3V), V5\text{=-}V_{EE}\text{=-}23V, no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface mode} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit parallel interface} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) \text{ 4-bit pa$$

$$Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, DISPOFFB = V_{DD}, M = Vss, display \ data \ pattern = 0000 \\ Istby: V_{DD} = 5V, f_{CL2} = 5.12 \\ MHz, SHL = Vss, display \ data \ d$$

$$I_{DD}$$

:  $V_{DD}$  =3V, $f_{CL2}$ =4MHz,display data pattern=0101

$$V_{\mathrm{DD}} = 5 \mathrm{V}$$

,  $f_{\mathrm{CL2}} = 5.12 \mathrm{MHz}$ , display data pattern=0101

$$I_{\text{EE}}$$

:  $V_{\text{DD}}$ =5V, $f_{\text{CL}2}$ =5.12MHz,display data pattern=0101, $V_{\text{EE}}$  pin

## **ELECTRICAL CHARACTERISTICS**

#### (2) Common Driver Application

(Vss = 0V, Ta = -30 to +85)

| Characteristic              | Symbol                            | Test Condition                                  | n                        | Min.                 | Тур. | Max.         | Unit |

|-----------------------------|-----------------------------------|-------------------------------------------------|--------------------------|----------------------|------|--------------|------|

| Operating Voltage           | $V_{DD}$                          | -                                               |                          | 2.7                  | -    | 5.5          |      |

| Operating voltage           | $V_{LCD}$                         | $V_{\rm IN} = V_{\rm DD} - V_{\rm EI}$          | 3                        | 6                    | -    | 28           | V    |

| Innut valtage (1)           | $V_{IH}$                          | -                                               |                          | $0.8 V_{DD}$         | -    | $V_{ m DD}$  | ·    |

| Input voltage (1)           | $V_{\scriptscriptstyle \rm I\!L}$ | -                                               |                          | 0                    | ı    | $0.2 V_{DD}$ |      |

| Output voltage (3)          | $V_{OH}$                          | $I_{OH} = -0.4 \text{mA}$                       |                          | V <sub>DD</sub> -0.4 | -    | -            | V    |

| Output voltage (3)          | $V_{OL}$                          | $I_{OL} = 0.4 \text{mA}$                        |                          | -                    | -    | 0.4          | v    |

| Input leakage current 1 (1) | $I_{IL1}$                         | $V_{IN} = V_{DD}$ to $V_{S}$                    | $V_{IN} = V_{DD}$ to Vss |                      | ı    | 10           |      |

| Input leakage current 2 (2) | $I_{IL2}$                         | $V_{IN}=0$ $V_{DD}=5V(PUI)$                     | LL UP)                   | -50                  | -125 | -250         | uA   |

| Input leakage current 3 (4) | $I_{IL3}$                         | $V_{\rm IN} = V_{\rm DD}$ to $V_{\rm P}$        | EΕ                       | -25                  | ı    | 25           |      |

| On resistance (5)           | $R_{ON}$                          | $I_{ON} = 100uA$                                | $I_{ON} = 100uA$         |                      | 2    | 4            | K    |

|                             | $I_{\scriptscriptstyle STRY}$     | $F_{CL}=32KHz$                                  | Vss pin                  | -                    | -    | 100          |      |

| Cumply augment(6)           | T I                               | $F_{CLI}=32KHz$                                 | $V_{DD} = 5V$            | -                    | -    | 200          |      |

| Supply current(6)           | $I_{DD}$                          | $F_{\text{CL1}}$ =32KHz<br>$F_{\text{M}}$ =80Hz | $V_{DD} = 3V$            | -                    | -    | 120          |      |

|                             |                                   | I'M-0011Z                                       | $V_{DD} = 5V$            | -                    | -    | 150          |      |

#### **NOTES:**

- 1. Applied to CL1,D2\_DL(SHL=LOW),D4\_DR(SHL=HIGH),SHL,DISPOFFB,M,CS,AMS pin

- 2. Pull-up input pins:CL2,D1\_SID,D3\_DM(AMS=HIGH),ELB(SHL=LOW),ERB(SHL=HIGH)

- 3. D2\_DL(SHL=HIGH),D4\_DR(SHL=LOW) pin

- 4. V0,V12,V43,V5 pin

- 5.  $V_{LCD} = V_{DD} V_{EE}$ ,  $V0 = V_{DD} = 5V$ ,  $V5 = V_{EE} = -23V$

$$V12 = V_{DD} - 1/n(V_{LCD}), V43 = V_{EE} + 1/n(V_{LCD}), n = 17(1/256 \text{ duty}, 1/17 \text{ bias})$$

6.  $V0=V_{DD},V12=3.35V(V_{DD}=5V) \text{ or } 1.47V(V_{DD}=3V),$

$$V43 = -21.35 V(V_{\rm DD} = 5 V) \text{ or } -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, \text{no-load condition} \\ (1/256 \text{ duty}, 1/17 \text{ bias}) = -21.47 V(V_{\rm DD} = 3 V), V5 = V_{\rm EE} = -23 V, V5 = V_{\rm EE$$

Single-type mode operation: AMS = Vss, SHL = Vss, DISPOFFB =  $V_{\rm DD}$

D1\_SID=D3\_DM=VDD,D4\_DR=OPEN,ELB+ERB+OPEN,

$I_{STBY}$ :  $V_{DD} = 5V, M = Vss, D2_DL = Vss$

$I_{DD}$ :  $f_{M}$ =80Hz,D2\_DL=  $V_{DD}$

$V_{\rm DD}$  =3V,display data pattern=10000000 ...,01000000 ...,00100000 ...,000100000 ...

$V_{\rm DD}$  =5V.displat data pattern=10000000 ...,01000000 ...,00100000 ...,00010000 ...,...

$I_{EE}$ :  $f_M$ =80Hz,D2\_DL= $V_{DD}$

Taiwan Memory Technology, Inc. reserves the right to change products or specifications without notic Publication Date: FEB., 2001

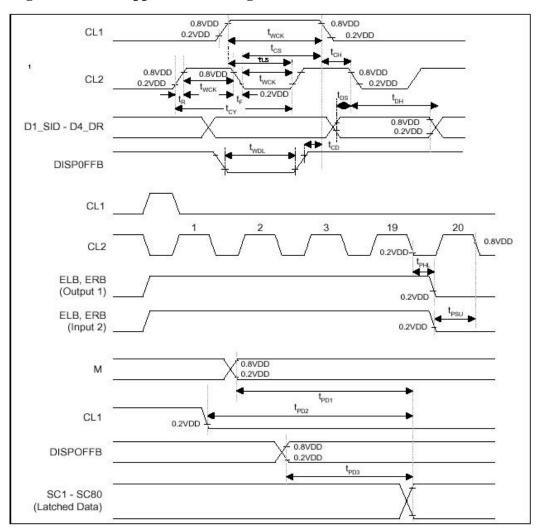

# **AC CHARACTERRISTICS**

## (1) Segment Driver Application

(Vss = 0V, Ta = -30 to +85)

| Characteristic                               | G                            | The A. Constitution   | (1) V | DD=5V | ±10% | (2) VI | DD=3V | ±10% | TT . *4 |

|----------------------------------------------|------------------------------|-----------------------|-------|-------|------|--------|-------|------|---------|

| Characteristic                               | Symbol                       | <b>Test Condition</b> | Min.  | Тур.  | Max. | Min.   | Тур.  | Max. | Unit    |

| Clock cycle time                             | tcy                          | Duty=50%              | 125   | -     | -    | 250    | -     | -    |         |

| Clock pulse width                            | twck                         | -                     | 45    | -     | -    | 95     | -     | -    |         |

| Clock rise/fall time                         | $t_{\rm R}/t_{\rm F}$        | -                     | -     | -     | -    | -      | -     | 30   |         |

| Data set-up time                             | $t_{ m DS}$                  | -                     | 30    | -     | -    | 65     | -     | -    |         |

| Data hold time                               | $t_{\mathrm{DH}}$            | -                     | 30    | -     | -    | 65     | -     | -    |         |

| Clock set-up time                            | tcs                          | -                     | 80    | -     | -    | 120    | -     | -    | ns      |

| Clock hold time                              | tch                          | -                     | 80    | -     | -    | 120    | -     | -    |         |

| Propagation delay                            | 4.1.1                        | ELB Output            |       |       | 60   |        |       | 125  |         |

| time                                         | tphl                         | ERB Output            | -     | -     | 60   | -      | -     | 125  |         |

| ELD EDD set un time                          | 4                            | ELB Input             | 30    |       |      | 65     |       |      |         |

| ELB,ERB set-up time                          | tpsu                         | ERB Input             | 30    | 30    | _    | 65     | _     | _    |         |

| DISPOFFB low pulse width                     | $t_{\scriptscriptstyle WDL}$ | -                     | 1.2   | -     | -    | 1.2    | -     | -    | us      |

| DISPOFFB clear time                          | tcd                          | -                     | 100   | -     | -    | 100    | -     |      | ns      |

| M-OUT propagation delay time                 | tpd1                         |                       | ı     | ı     | 1.0  | ı      | ı     | 1.2  |         |

| CL1-OUT<br>propagation delay<br>time         | tpd2                         | CL=15pF               | 1     | ı     | 1.0  | ı      | ı     | 1.2  | us      |

| DISPOFFB-OUT propagation delay time          | tpd3                         |                       | -     | -     | 1.0  | -      | -     | 1.2  |         |

| Latch pulse rise to<br>Shift clock rise time | $t_{LS}$                     |                       | 80    | -     | -    | 120    | -     | -    | ns      |

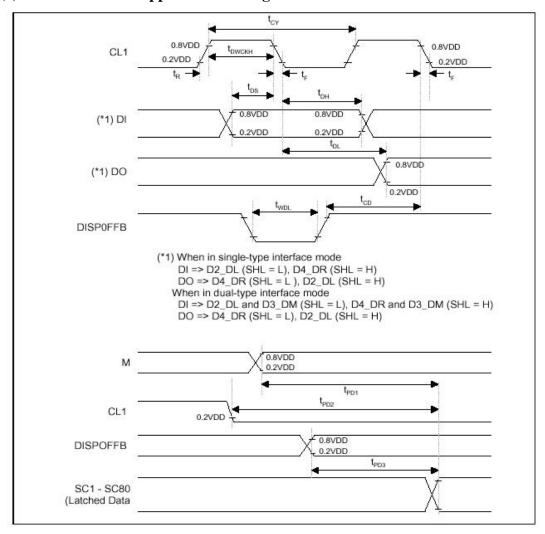

# **AC CHARACTERISTICS**

### (2) Common Driver Application

(Vss = 0V, Ta=-30 to +85)

| Clara and a state                    | Gl1    | To a Condition        | (1) V | DD=5V | ±10% | (2) VI | DD=3V | ±10% | TI . *4 |

|--------------------------------------|--------|-----------------------|-------|-------|------|--------|-------|------|---------|

| Characteristic                       | Symbol | <b>Test Condition</b> | Min.  | Тур.  | Max. | Min.   | Тур.  | Max. | Unit    |

| Clock cycle time                     | tcy    | Duty=50%              | 250   | ı     | -    | 500    | -     | -    |         |

| Clock pulse width                    | twck   | -                     | 45    | -     | -    | 95     | -     | -    |         |

| Clock rise/fall time                 | tR/tF  | -                     | -     | -     | 50   | -      | -     | 50   | ns      |

| Data set-up time                     | tDS    | -                     | 30    | -     | -    | 65     | -     | -    |         |

| Data hold time                       | tDH    | -                     | 30    | -     | -    | 65     | -     | -    |         |

| DISPOFFB low pulse width             | twdl   | -                     | 1.2   | ı     | -    | 1.2    | -     | -    | us      |

| DISPOFFB clear time                  | tcd    | -                     | 100   | -     | -    | 100    | -     |      | ns      |

| Output delay time                    | tdl    |                       | -     | 1     | 200  | -      | -     | 250  |         |

| M-OUT propagation delay time         | tpd1   |                       | 1     | 1     | 1.0  | 1      | 1     | 1.2  |         |

| CL1-OUT<br>propagation delay<br>time | tpd2   | CL=15pF               |       | 1     | 1.0  | 1      | ı     | 1.2  | us      |

| DISPOFFB-OUT propagation delay time  | tpd3   |                       | -     | -     | 1.0  | -      | -     | 1.2  |         |

# **AC CHARACTERISTICS**

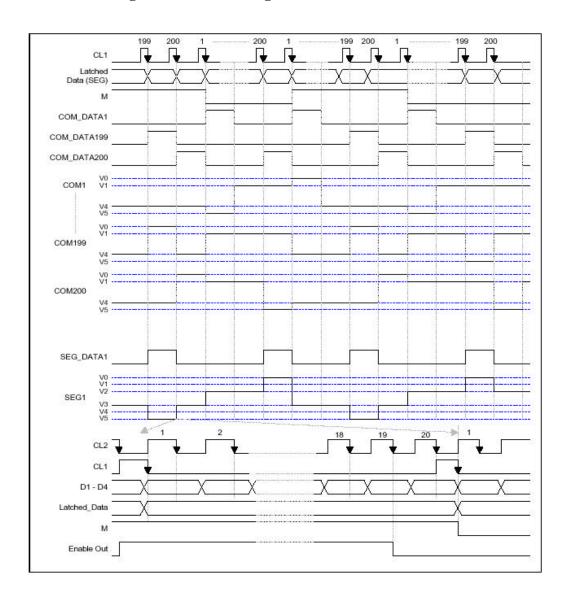

### (3) Segment Driver Application Timing

## **AC CHARACTERISTICS**

#### (4) Common Driver Application Timing

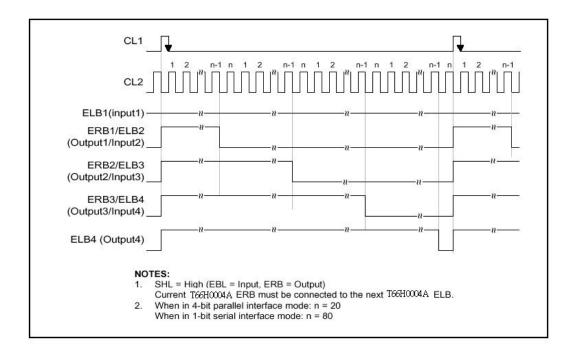

# **POWER DOWN FUNCTION**

In the case of cascade connection of segment mode drivers, T66H0004A has a "power down function" In order to reducd the power consumption.

| SHL | <b>Enable input</b> | Enable output | Current driver status                      | The other drivers status |

|-----|---------------------|---------------|--------------------------------------------|--------------------------|

| L   | ERB                 | ELB           | While ERB="Low",current driver is enabled. | Disabled                 |

| Н   | ELB                 | ERB           | While ELB="Low",current driver is enabled  | Disabled                 |

<sup>\*</sup> In the case of common driver application, power down function dose not work.

# **OPERATION TIMING DIAGRAM**

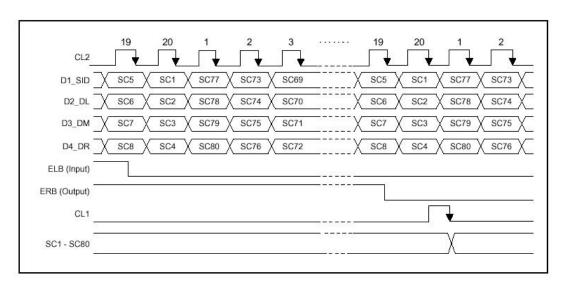

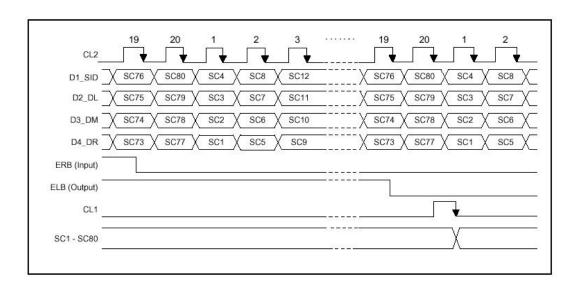

#### (1) 4-bit Parallel Mode Interface Segment Driver

• When SHL ="Low"

● When SHL="High"

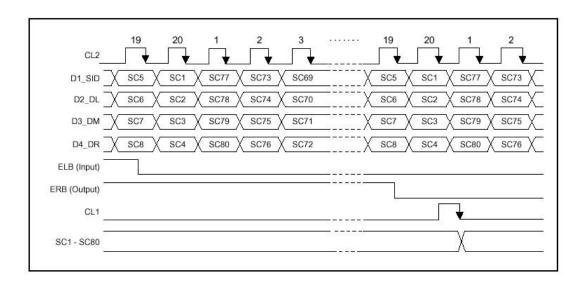

#### (2) 1-bit Serial Mode Interface Segment Driver

• When SHL="Low"

#### • When SHL="High"

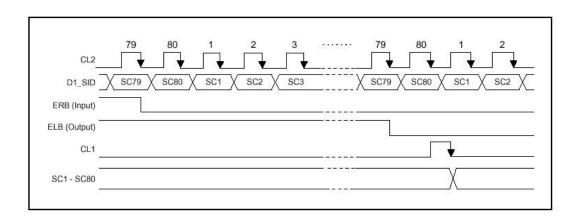

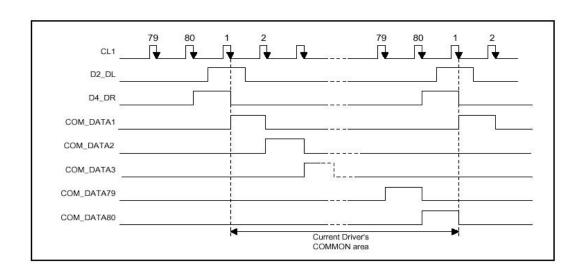

#### (3) Single-type Interface Mode Common Driver

• When SHL="Low"

• When SHL="High"

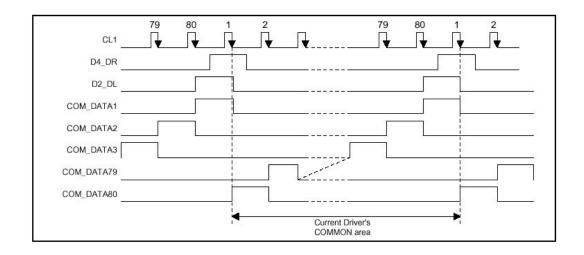

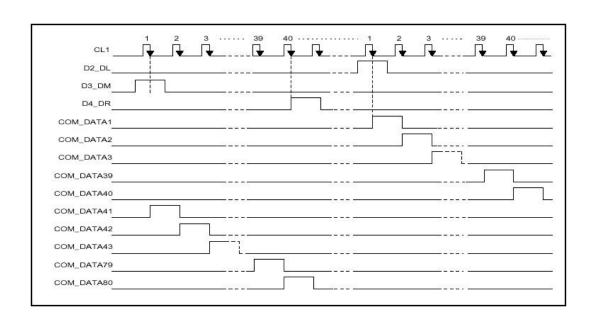

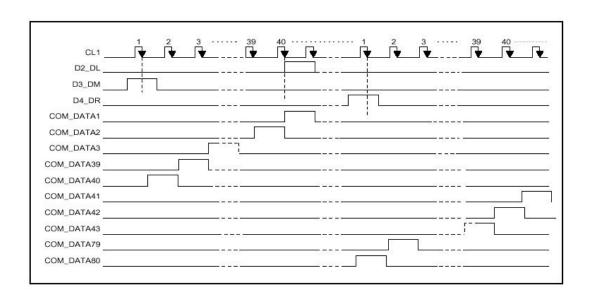

### (4) DUAL-type Interface Mode Common Driver

• When SHL="Low"

• When SHL="High"

### (5) Common/Segment driver Timing(1/200 DUTY)

# APPLICATION INFORMATION

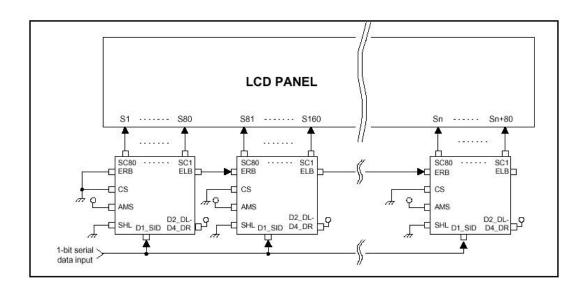

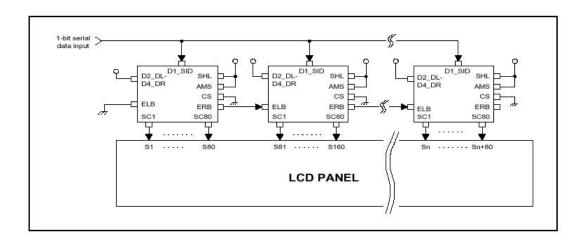

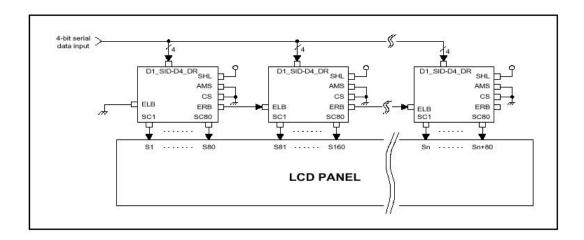

#### 1-bit Serial Interface Mode(80 output Segment Driver)

(a) Lower View (SHL = L, AMS = H)

#### (b)Upper View(SHL = H, AMS = H)

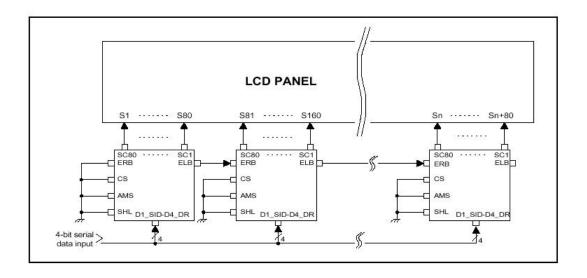

#### 4-bit Parallel Interface Mode(80 output Segment Driver)

(a) Lower View(SHL = L, AMS = L)

(b) Upper View (SHL = H, AMS = L)

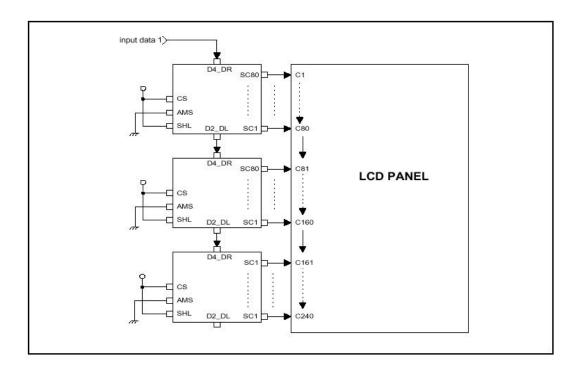

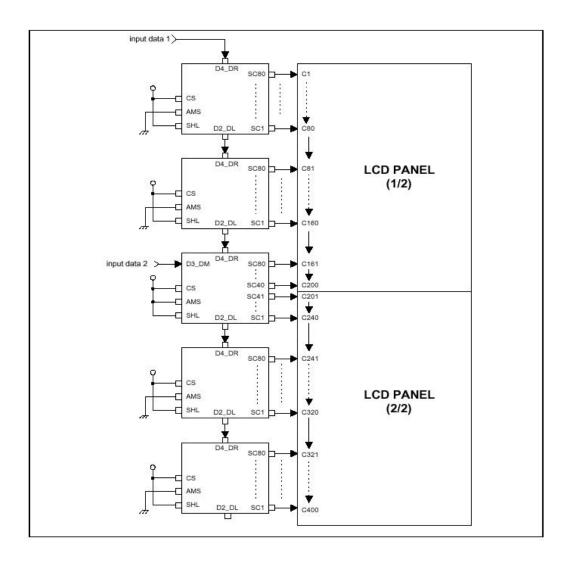

### **Single-type Interface Mode (80 output Common Driver)**

#### **Dual-type Interface Mode (40 output Common Driver)**

**NOTE:** Using this application mode (dual-type common mode), the duty ratio can be reduced to half. In case, 1/200 duty can be used to drive the 400 common LCD panel.

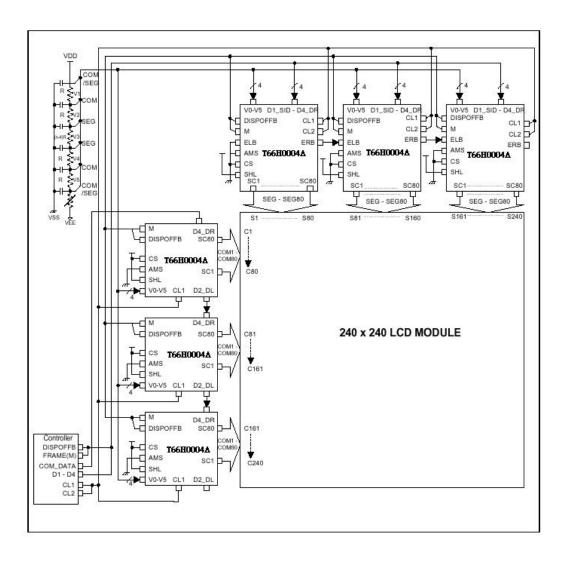

## APPLICATION CIRCUIT EXAMPLE

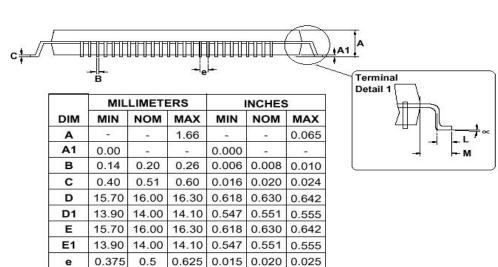

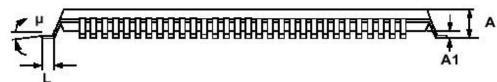

# PACKAGE DIMENSION (Unit:mm)

### 100 pin TQFP

0.51

1.00 BSC

0.70

12°

0.012

L

M

0.30

0.020

0.039 BSC

0.028

12°

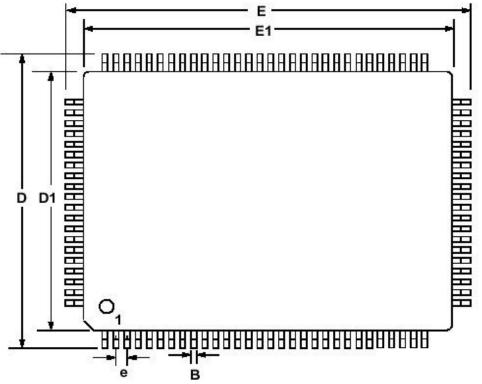

100 pin QFP

|     | INCHES |        | MILLIMETERS |        |

|-----|--------|--------|-------------|--------|

| DIM | MIN    | MAX    | MIN         | MAX    |

| Α   |        | 0.134  |             | 3.400  |

| A1  | 0.010  | 0.014  | 0.250       | 0.350  |

| В   | 0.009  | 0.015  | 0.220       | 0.380  |

| D   | 0.667  | 0.687  | 16.950      | 17.450 |

| D1  | 0.547  | 0.555  | 13.900      | 14.100 |

| E   | 0.904  | 0.923  | 22.950      | 23.450 |

| E1  | 0.783  | 0.791  | 19.900      | 20.100 |

| e*  | 0.022  | 0.030  | 0.550       | 0.750  |

| μ   | 0.000° | 7.000° | 0.000°      | 7.000° |

| L   | 0.018  | 0.030  | 0.450       | 0.750  |

<sup>\*</sup> Nominal pin pitch is 0.65 mm