### INTEGRATED CIRCUIT **TOSHIBA**

TECHNICAL DATA

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT TC58A040 F SILICON GATE CMOS

## 4 MBIT (4 M × 1 BITS) CMOS AUDIO NAND E<sup>2</sup>PROM

TENTATIVE DATA

#### **DESCRIPTION**

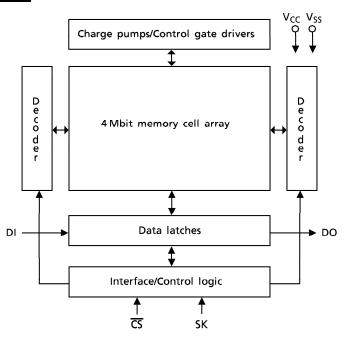

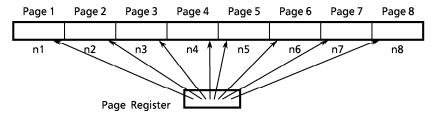

The TC58A040 is a 5-volt 4 Mbit NAND Electrically Erasable and Programmable Read Only Memory (NAND EEPROM) organized as 256 bits × 128 pages × 128 blocks.

The device has a 256-bit static register which allows the program and read data to be transferred between the register and the memory cell array in 256-bit increments. The Erase operation is implemented in a single block unit (4 kbytes).

The TC58A040 is suitable for digital recording systems such as digital answering machines and personal digital recorders.

#### **FEATURES**

Organization

Memory cell array  $4 M \times 1$ Page Buffer 256 bits Page size 256 bits Block size 4 kbytes

Mode

Read, Auto Program Auto Block Erase, Status Read

Mode control

Serial input/output Command control

- Power supply  $V_{CC} = 5 V \pm 10\%$

- Access time

Cell array-Register  $25 \mu s$ Serial Read Cycle  $250 \, \mathrm{ns}$

Operating current

Read (500 ns cycle) 5 mA typ Write 15 mA typ Erase 10 mA typ Standby 50 μA

Package

TC58A040F: SOP28-P-450

(Weight: 0.81 g typ)

#### PIN ASSIGNMENT (TOP VIEW)

|     |   |    | $\smile$ |    |                    |

|-----|---|----|----------|----|--------------------|

| GND |   | 1  |          | 28 | $\square$ $v_{cc}$ |

| NC  | П | 2  |          | 27 | ∣пс                |

| NC  |   | 3  |          | 26 | □ис                |

| cs  |   | 4  |          | 25 | □ис                |

| SK  |   | 5  |          | 24 | □ис                |

| DI  |   | 6  |          | 23 | □ис                |

| DO  |   | 7  |          | 22 | □ис                |

| NC  |   | 8  |          | 21 | □ис                |

| NC  |   | 9  |          | 20 | ∣ис                |

| NC  |   | 10 |          | 19 | □ис                |

| NC  |   | 11 |          | 18 | □ис                |

| NC  |   | 12 |          | 17 | □ис                |

| NC  |   | 13 |          | 16 | ∣ис                |

| NC  |   | 14 |          | 15 | □ис                |

|     |   |    |          |    | j                  |

#### PIN NAMES

| DO                               | Serial Data Output |

|----------------------------------|--------------------|

| DI                               | Serial Data Input  |

| SK                               | Serial Clock       |

| <u>cs</u>                        | Chip Select        |

| NC                               | No Connection      |

| V <sub>CC</sub> /V <sub>SS</sub> | Power Supply       |

The products described in this document are strategic products subject to COCOM regulations. They should not be exported without authorization from the appropriate governmental authorities (as of

1996 - 08 - 19 TOSHIBA CORPORATION

TC58A040F-1

(1)

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others. These TOSHIBA products are intended for use in general commercial applications (office equipment, communication equipment, measuring equipment, domestic appliances, etc.), please make sure that you consult with us before you use these TOSHIBA products in equipment which requires extraordinarily high quality and/or reliability, and in equipment which may involve life threatening or critical application, including but not limited to such uses as atomic energy control, airplane or spaceship instrumentation, traffic signals, medical instrumentation, combustion control, all types of safety devices, etc. TOSHIBA cannot accept and hereby disclaims liability or any damage which may occur in case the TOSHIBA products are used in such equipment or applications without prior consultation with TOSHIBA.

TC58A040 F

TECHNICAL DATA

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | RATING                       | VALUE                          | UNIT |

|---------------------|------------------------------|--------------------------------|------|

| V <sub>CC</sub>     | Power Supply                 | - 0.6 to 7.0                   | V    |

| V <sub>IN</sub>     | Input Voltage                | - 0.6 to 7.0                   | V    |

| V <sub>I/O</sub>    | Input/Output Voltage         | - 0.6 V to Vcc + 0.5 V (≦ 7 V) | V    |

| P <sub>D</sub>      | Power Dissipation            | 0.5                            | w    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                            | °C   |

| T <sub>STG</sub>    | Storage Temperature          | – 55 to 150                    | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | 0 to 70                        | °C   |

### <u>CAPACITANCE</u> \*(Ta = $25^{\circ}$ C, f = 1 MHz)

| SYMBOL           | PARAMETER | CONDITION              | MIN | TYP | MAX | UNIT |

|------------------|-----------|------------------------|-----|-----|-----|------|

| C <sub>IN</sub>  | Input     | V <sub>IN</sub> = 0 V  | -   | 5   | 10  | РF   |

| C <sub>OUT</sub> | Output    | V <sub>OUT</sub> = 0 V | _   | 5   | 10  | РF   |

<sup>\*</sup> This parameter is periodically sampled and is not tested for every component.

| TC58A040F-2         |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

# INTEGRATED CIRCUIT **TOSHIBA**

TECHNICAL DATA

TC58A040 F

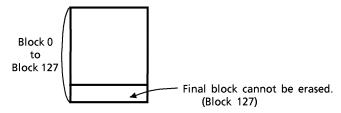

#### **VALID BLOCKS**

(1) The number of valid blocks in the range Block 0 to Block 126 (2) is:

| SYMBOL           | PARAMETER              | MIN | TYP | MAX     | UNIT  |

|------------------|------------------------|-----|-----|---------|-------|

| N <sub>VP1</sub> | Number of Valid blocks | 117 | TBD | 127 (2) | Block |

Note 1: The TC58A040 occasionally contains unusable blocks. Refer to Application Note (8) toward the end of this document.

Note 2: Block 127 is guaranteed to be good.

### DC RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PARAMETER                | MIN    | TYP | MAX                   | UNIT |

|-----------------|--------------------------|--------|-----|-----------------------|------|

| V <sub>CC</sub> | Power Supply             | 4.5    | 5.0 | 5.5                   | V    |

| V <sub>IH</sub> | High Level Input Voltage | 2.2    | _   | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IL</sub> | Low Level Input Voltage  | - 0.3* | -   | 0.8                   | V    |

<sup>\* - 2</sup> V (pulse width  $\leq$  20 ns)

### DC CHARACTERISTICS (Ta = $0^{\circ}$ to $70^{\circ}$ C, $V_{CC} = 5 \text{ V} \pm 10\%$ )

| SYMBOL            | PARAMETER                      | CONDITION                         | MIN | TYP | MAX  | UNIT |

|-------------------|--------------------------------|-----------------------------------|-----|-----|------|------|

| I <sub>IL</sub>   | Input Leakage Current          | $V_{IN} = 0 V \text{ to } V_{CC}$ | _   | _   | ± 10 | μΑ   |

| I <sub>LO</sub>   | Output Leakage Current         | $V_{OUT} = 0.4 V$ to $V_{CC}$     | _   | _   | ± 10 | μA   |

| I <sub>CCO1</sub> | Operating Current (Read Cycle) | t <sub>cycle</sub> = 250 ns       | -   | 5   | 20   | mA   |

| I <sub>CCO2</sub> | Operating Current (Read Cycle) | $t_{cycle} = 1 \mu s$             | _   | _   | 10   | mA   |

| I <sub>CCO3</sub> | Operating Current (Program)    | -                                 | -   | 15  | 60   | mA   |

| I <sub>CCO4</sub> | Operating Current (Erase)      | -                                 | _   | 10  | 40   | mA   |

| I <sub>CCS1</sub> | Standby Current                | CE = VIH                          | -   | _   | 500  | μΑ   |

| I <sub>CCS2</sub> | Standby Current                | $\overline{CE} = V_{CC} - 0.2 V$  | -   | _   | 50   | μΑ   |

| V <sub>OH</sub>   | High Level Output Voltage      | I <sub>OH</sub> = - 400 μA        | 2.4 | -   | -    | ٧    |

| V <sub>OL</sub>   | Low Level Output Voltage       | I <sub>OL</sub> = 2.1 mA          | _   | -   | 0.4  | V    |

| TC58A040F-3         |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CODDODATION |

TOSHIBA

TECHNICAL DATA

TC58A040 F

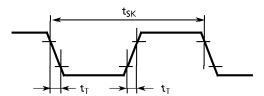

## <u>AC CHARACTERISTICS AND OPERATING CONDITIONS</u> (Ta = $0^{\circ}$ to $70^{\circ}$ C, $V_{CC}$ = $5 \text{ V} \pm 10\%$ )

| SYMBOL            | PARAMETER               | CONDITIONS                                      | MIN   | MAX | UNIT |

|-------------------|-------------------------|-------------------------------------------------|-------|-----|------|

| t <sub>SK</sub>   | Serial Clock Cycle Time |                                                 | 250 * | -   | ns   |

| t <sub>SKH</sub>  | SK High Time            |                                                 | 120   | -   | ns   |

| t <sub>SKL</sub>  | SK Low Time             |                                                 | 120   | -   | ns   |

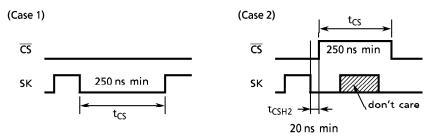

| t <sub>CS</sub>   | CS High Time            |                                                 | 250   | -   | ns   |

| t <sub>CSS</sub>  | CS Set-Up Time          | Relative to SK Rising Edge                      | 100   | -   | ns   |

| t <sub>DIS</sub>  | DI Set-Up Time          | Relative to SK Rising Edge                      | 50    | -   | ns   |

| t <sub>CSH1</sub> | CS Hold Time            | t <sub>CSH1</sub> : Relative to DO Rising Edge  | 0     | -   | ns   |

| t <sub>CSH2</sub> | CS Hold Time            | t <sub>CSH2</sub> : Relative to SK Falling Edge | 20    | -   | ns   |

| t <sub>DIH</sub>  | DI Hold Time            | Relative to SK Rising Edge                      | 20    | -   | ns   |

| t <sub>DF</sub>   | CS to DO in High Z      |                                                 | _     | 100 | ns   |

| t <sub>DH</sub>   | DO Hold Time            | Relative to SK Falling Edge                     | 0     | -   | ns   |

| t <sub>PD</sub>   | Output Delay            | Relative to SK Falling Edge                     | _     | 100 | ns   |

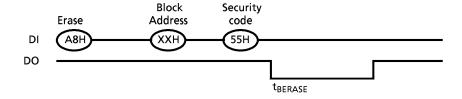

| t <sub>SADD</sub> | Set Address Time        |                                                 | _     | 200 | μs   |

| t <sub>R</sub>    | Page Read Transfer Time |                                                 | _     | 25  | μς   |

| t <sub>SKB</sub>  | SK to DO (Busy)         | Relative to SK Falling Edge                     | _     | 200 | ns   |

<sup>\*</sup>  $t_T$  (transition time) = 5 ns

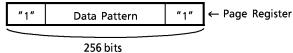

## <u>PROGRAMMING AND ERASING CHARACTERISTICS</u> (Ta = $0^{\circ}$ to $70^{\circ}$ C, $V_{CC}$ = $5 \text{ V} \pm 10\%$ )

| SYMBOL              | PARAMETER                                        | MIN | TYP         | MAX  | UNIT   |

|---------------------|--------------------------------------------------|-----|-------------|------|--------|

| t <sub>PROG</sub>   | Programming Time                                 | -   | 300 to 1000 | 2000 | μS     |

| t <sub>BERASE</sub> | Block Erasing Time                               | -   | 7           | 100  | ms     |

| N <sub>W/E</sub>    | Number of Write/Erase Cycles                     | -   | -           | 105  | Cycles |

| N <sub>PP</sub> *   | Number of Programming Cycles on Same Master Page | _   | _           | 50   | Cycles |

\*: Refer to the Partial Page Write operation.

| TC58A040F-4         |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

### **TOSHIBA**

TECHNICAL DATA

TC58A040 F

#### PIN DESCRIPTIONS

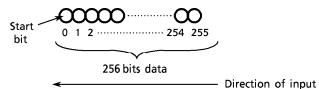

#### Serial Data Input: DI

The DI pin is used for inputting in commands and data. Commands and data are latched on the rising edge of SK.

#### Serial Data Output: DO

The DO pin is used for outputting status and data. Data is available tpD after the falling edge of SK. DO indicates the internal state except during data output. A low level indicates that the device is busy. A high level indicates that the device is ready.

#### Chip Select: CS

This signal enables the device. When this signal is high, the device ignores SK. This signal can be tied to ground when there is only one Audio-NAND device. The  $\overline{\text{CS}}$  pin may be pulled high to reset the device.

#### Serial Clock: SK

This signal controls serial data input and output. Commands and data are latched on the rising edge of SK. Data is output on the falling edge of SK.

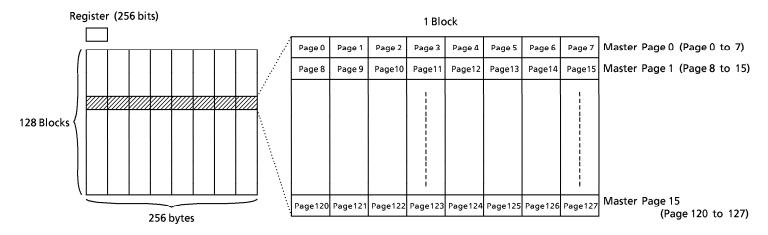

#### **ORGANIZATION**

The TC58A040F is a 4 Mbit device organized as 128 blocks of 16 master pages. A master page is further segmented into 8 pages as shown in the following figure. The Write and Read operations are executed on a page basis and Erase is executed on a block basis.

1 page = 256 bits

1 master page = 8 pages = 256 bytes

1 block = 16 master pages = 128 pages = 4096 bytes

A page is the unit of reading and programming.

A block is the unit of erasure.

A master page is divided into 8 pages. These 8 pages are controlled by a common word line.

| TC58A040F-5         |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

### **TOSHIBA**

TECHNICAL DATA

TC58A040 F

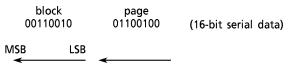

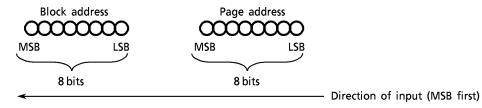

#### ADDRESS ASSIGNMENT

The address is acquired through the DI pin using 16 consecutive clock cycles. The first 8 bits are the block address. The last 8 bits are the page address.

|               | DECIMAL  | BINARY               |

|---------------|----------|----------------------|

| Block address | 0 to 126 | 00000000 to 01111110 |

| Page address  | 0 to 127 | 00000000 to 01111111 |

example: Page 100 in block 50

#### WRITE-ONCE BLOCK

The TC58A040 has 128 blocks (blocks 0 to 127). The final block (block 127) has been set aside as a read-only block. Once data is written, this block cannot be erased. This block needs a special command for reading and writing. Block 127 may be used for storing system configuration information that cannot be lost.

#### **COMMAND TABLE**

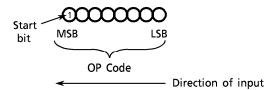

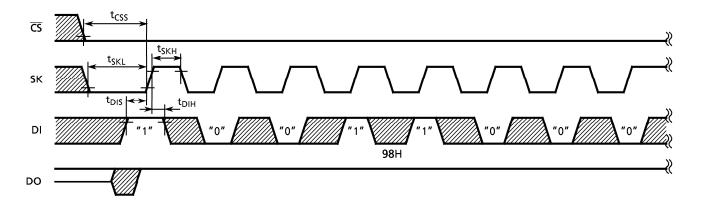

There are 12 commands in the TC58A040 command set. All operations are controlled by these commands, shown in the following table.

| INSTRUCTION      | START BIT | OPCODE | RESERVED | HEX COMMAND |

|------------------|-----------|--------|----------|-------------|

| Get Status       | 1         | 0000   | 000      | 80H         |

| Set Address      | 1         | 0001   | 000      | 88H         |

| Increment        | 1         | 0010   | 000      | 90H         |

| Read             | 1         | 0011   | 000      | 98H         |

| Write            | 1         | 0100   | 000      | A0H         |

| Erase            | 1         | 0101   | 000      | A8H         |

| Data Shift In    | 1         | 0110   | 000      | вон         |

| Data Shift Out   | 1         | 0111   | 000      | в8Н         |

| Write Enable     | 1         | 1100   | 000      | E0H         |

| Write Disable    | 1         | 1101   | 000      | E8H         |

| Write Last Block | 1         | 1110   | 000      | F0H         |

| Read Last Block  | 1         | 1010   | 000      | D0H         |

| TC58A040F6          |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

### **TOSHIBA**

TECHNICAL DATA

TC58A040 F

#### **COMMANDS**

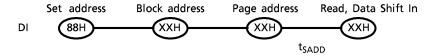

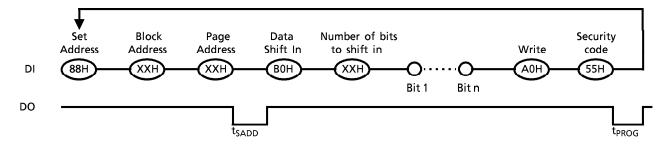

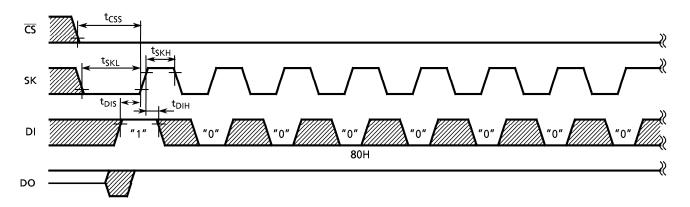

#### Set Address

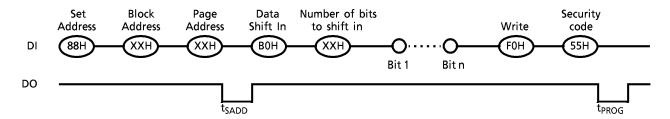

The Set Address command defines which block and page of the memory an operation will operate on. The Set Address command is followed by two bytes, the first indicating the block number and the second indicating the page number. The Set Address command is usually followed by a Read or a Data Shift In command. Between the page address byte and the next command there is a delay of tSADD.

The address that is selected remains the active address until a new Set Address or Increment command is given.

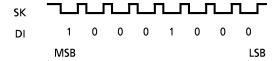

Example: If inputting the 88H command, the MSB must be input first.

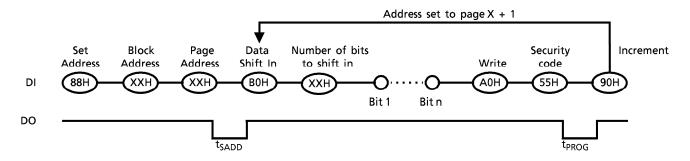

#### **Increment**

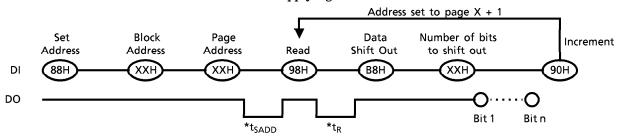

The Increment command automatically increments the page address.

When the last page in a block is selected, if the Increment command is input, the address is set to 00H (Page 0) in the next block.

However, if the last page in the last block (Block 126) is selected, the Increment command will set the address to 00H (page 0) in the same block (Block 126).

#### Read

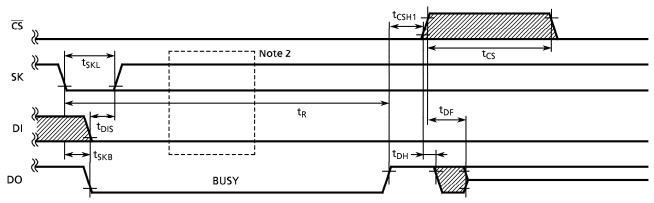

The Read command transfers data from the selected page of the memory array into the on-chip buffer (256-bit shift register). The Read command is usually followed by a Data Shift Out command. There is a delay of  $t_R$  between the Read command and the Data Shift Out command as the data is transferred from the memory array to the on-chip buffer.

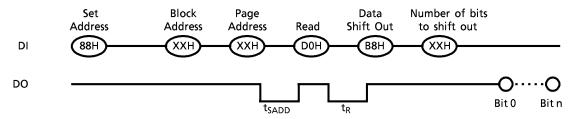

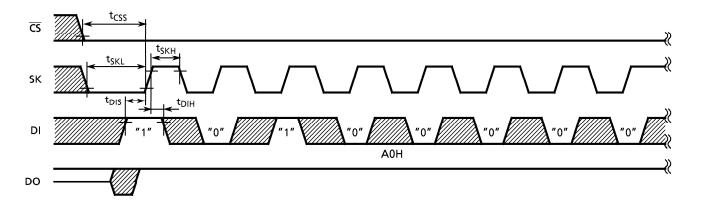

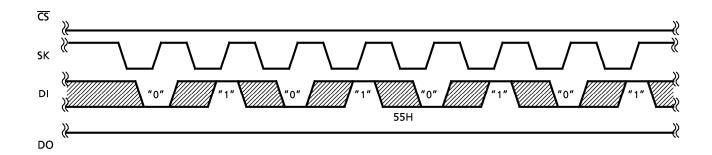

#### **Write**

The Write command programs data from the on-chip buffer into the selected page of the memory array. A security code (55H) follows the Write command to ensure against accidental writes. Get Status may be used to ensure that the operation was successful. The Write command will be ignored if Write Disable has been set.

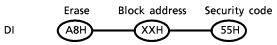

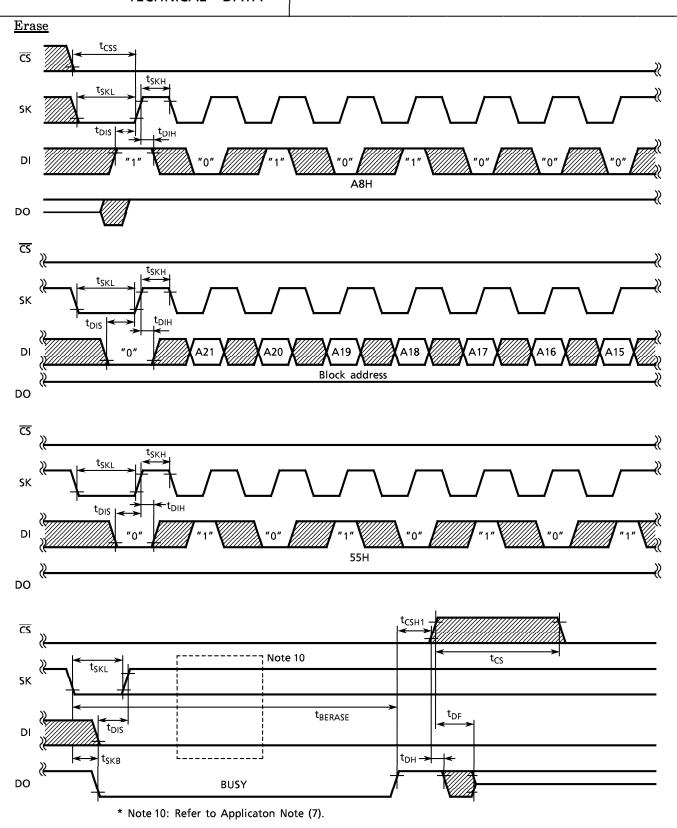

#### **Erase**

The Erase command erases a selected block. The Erase command is followed by the block address. A security code (55H) follows the block address to ensure against accidental erasure. The Get Status command may be used to verify that the operation was successful. The Erase command will be ignored if Write Disable has been set.

| TC58A040F-7         |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

## **TOSHIBA**

TECHNICAL DATA

TC58A040 F

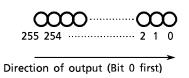

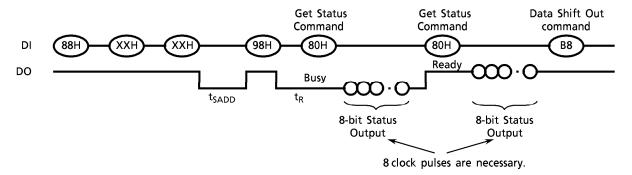

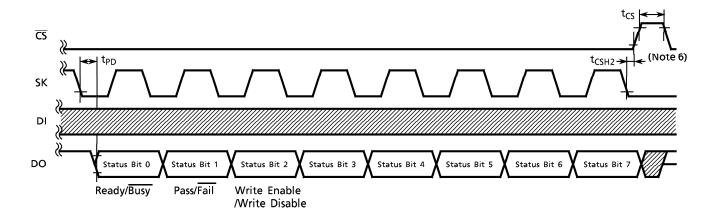

#### Get Status

The Get Status command is used to output the status of the TC58A040. The eight status bits are defined as follows.

| BIT     | STATUS                     | OUTPUT                               |

|---------|----------------------------|--------------------------------------|

| 0 (LSB) | Ready/Busy                 | Ready: "1" Busy: "0"                 |

| 1       | Pass/Fail                  | Pass: "1" Fail: "0"                  |

| 2       | Write Enable/Write Disable | Write Enable: "1" Write Disable: "0" |

| 3       | Not Used                   | Unknown "1" or "0"                   |

| 4       | Not Used                   | Unknown "1" or "0"                   |

| 5       | Not Used                   | Unknown "1" or "0"                   |

| 6       | Not Used                   | Unknown "1" or "0"                   |

| 7 (MSB) | Not Used                   | Unknown "1" or "0"                   |

The status is output LSB first.

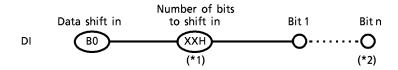

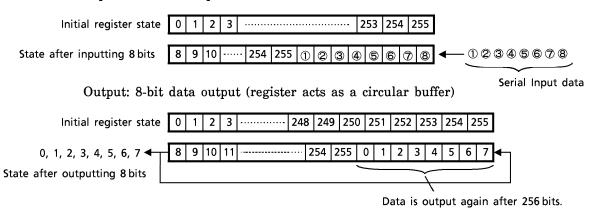

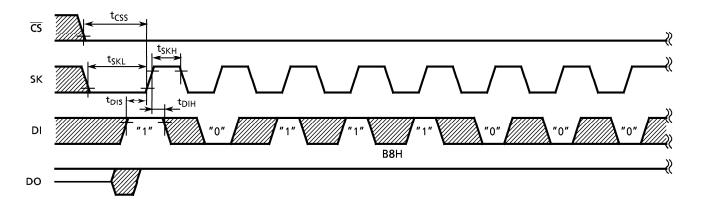

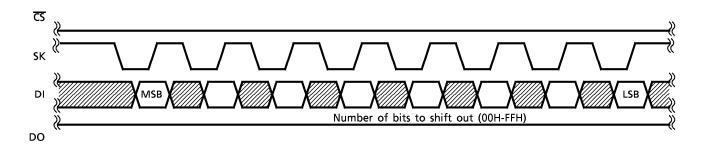

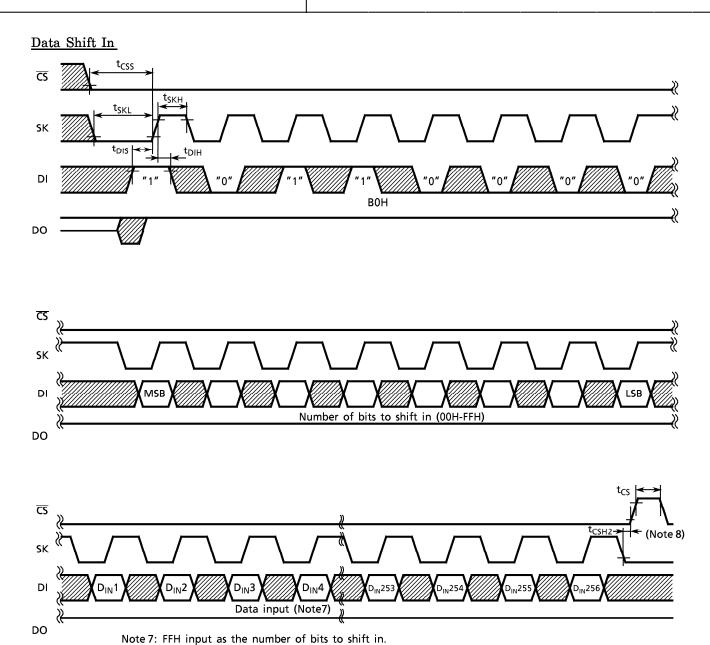

#### Data Shift In

The Data Shift In command is used to shift data into the on-chip buffer. The number of bits sent into the buffer is determined by an 8-bit argument following the command. The Data Shift In command is usually used prior to the Write command.

The value of (\*1) is 1 less than the actual number of bits to be shifted in (\*2).

#### Example:

| Number of bits (*2)          | n = 256        | n = 128        | n = 1          |

|------------------------------|----------------|----------------|----------------|

| Number of bits argument (*1) | FFH = 11111111 | 7FH = 01111111 | 00H = 00000000 |

### TOSHIBA

TECHNICAL DATA

TC58A040 F

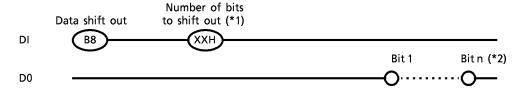

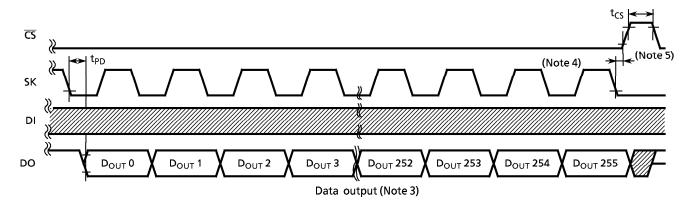

#### Data Shift Out

The data Shift Out command is used to shift data out of the on-chip buffer. The number of bits sent out of the buffer is determined by an 8-bit argument following the command. The Data Shift Out command is usually used after a Read command.

The value of (\*1) is 1 less than the actual number of bits to be shifted out (\*2).

#### Example:

| Number of bits (*2)          | n = 256        | n = 128        | n = 1          |

|------------------------------|----------------|----------------|----------------|

| Number of bits argument (*1) | FFH = 11111111 | 7FH = 01111111 | 00H = 00000000 |

#### Write Disable

The Write Disable command is used to prevent inadvertent writing or erasure. Once this command has been executed, no subsequent Write or Erase commands will be accepted. The Status Read operation (Get Status command) can be used to determine whether the device is in the Write Enable or Disable state.

#### Write Enable

The Write Enable command is used to cancel Write Disable mode.

#### Read Last Block

The Read Last Block command is used to read the contents of the final block (Block 127). The Set Address command and 2 address bytes are required to set the page address. The block address is automatically set to 127, so the first address byte is ignored.

#### Write Last Block

The Write Last Block command is used to program into the selected page in the final block (Block 127). Once data is written into the last block, it cannot be erased. A security code (55H) follows the Write Last Block command to ensure against accidental writes.

TECHNICAL DATA

TC58A040 F

#### **DEVICE OPERATION**

#### Input/Output operation

The TC58A040 has separate input and output pins. Address, command and input data are input as serial data through DI. Status data and output data are output as serial data through DO. Input and output operations are as follows.

#### (1) Address input

(2) Command input

(3) Data input

(4) Data output

(5) Status data output

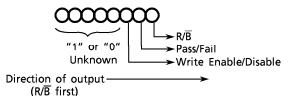

#### Register operation

The TC58A040 has a 256-bit shift register on the chip. This register is used to transfer data to and from the memory cell array. The register operation is as follows:

Input: 8-bit data input (new data shifts out oldest data)

TC58A040F-10 1996-08-19 TOSHIBA CORPORATION

TOSHIBA

TECHNICAL DATA

TC58A040 F

#### Read Operation

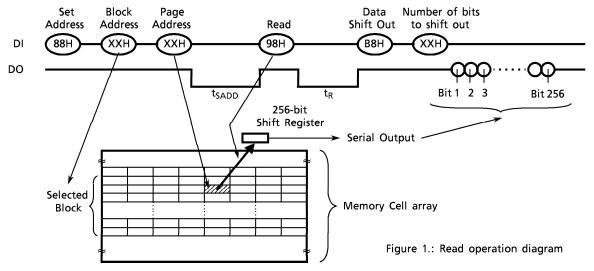

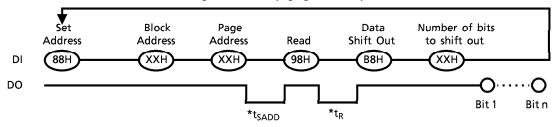

The Read operation transfers data to the register from the memory cell array and outputs data synchronized to SK. This operation is shown in Figure 1.

The read operation is executed page by page. When reading from two or more consecutive pages, two methods are possible:

#### · Read Mode (1)

The set address command is input for every page read cycle.

#### · Read Mode (2)

The Increment command is used instead of applying the Set Address command.

\* D0 becomes low and is held low during the Busy state. The device state (Busy or Ready) can be output by executing the Status Read operation.

> TC58A040F-11 1996-08-19 TOSHIBA CORPORATION

TOSHIBA

TECHNICAL DATA

#### Status Read Operation

This operation outputs the device's internal state by using the Get Status command.

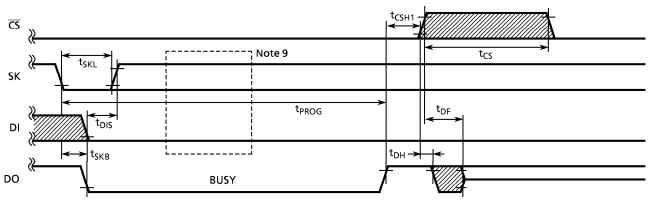

#### Write Operation

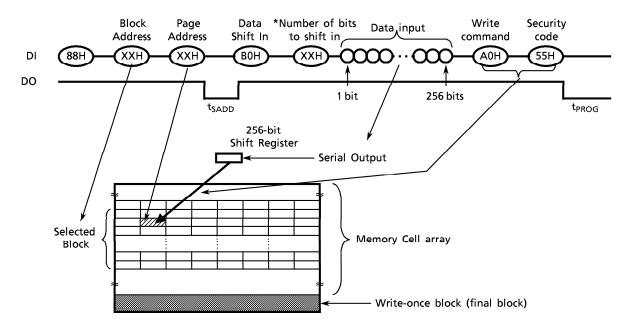

The Write operation inputs data into the on-chip data register, and transfers the data from the register into the selected page in the memory array. This operation is shown in Figure 2.

Figure 2. Write operation diagram

### **TOSHIBA**

TECHNICAL DATA

TC58A040 F

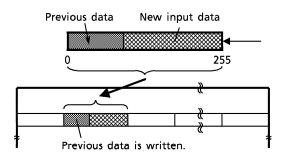

\* Number of bits to shift in: 256 (#FFH) should be input.

If the number of bits to shift in is less than 256 (#FFH), previous data will be written into the memory array.

The Write operation is executed page by page. When writing two or more consecutive pages, two methods are possible:

#### · Write Mode (1)

The Set Address command is input for every Page Write operation.

#### · Write Mode (2)

The Increment command is used instead of applying the Set Address command.

### TOSHIBA

TECHNICAL DATA

TC58A040 F

#### · Partial Page Write operation

The TC58A040 allows a master page to be divided into a maximum of 50 segments with each page segment written individually as follows:

Npp = n1 + n2 + n3 + n4 + n5 + n6 + n7 + n8 = 50

- \* n1 to n8: Number of partial programs in a page

- \* Npp : Number of partial programs in a master page

The input data for unprogrammed or previously programmed page segments must be "1".

#### Erase Operation

The Erase operation is executed block by block. The Erase operation sequence is shown below.

# INTEGRATED CIRCUIT **TOSHIBA**

TECHNICAL DATA

TC58A040 F

#### Read and Write operation for the final block (write-once block)

The final block (Block 127) has been set aside as a read-only block. Hence, the final block needs special commands for the Read and Write operations.

#### Read Last Block

The block address is ignored.

#### Write Last Block

The block address is ignored.

TC58A040 F

TECHNICAL DATA

Note: The above 4 timing diagrams are contiguous.

| TC58A040F-16        |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

TOSHIBA

TECHNICAL DATA

#### Read

\* Note 2: Refer to Application Note (7).

Note: The above 2 timing diagrams are contiguous.

**TOSHIBA**

TECHNICAL DATA

#### Data Shift Out

Note 3: FFH input as the number of bits to shift out.

Note 4: Refer to Application Note (6).

Note 5: Refer to Application Note (9).

Note: The above 3 timing diagrams are contiguous.

TC58A040F-18 1996-08-19 TOSHIBA CORPORATION TOSHIBA TECHNICAL DATA

#### Status Read

Note 6: Refer to Application Note (9).

Note: The above 2 timing diagrams are contiguous.

TC58A040F—19 1996 - 08 - 19 TOSHIBA CORPORATION

## INTEGRATED CIRCUIT **TOSHIBA**

TC58A040 F

TECHNICAL DATA

Note: The above 3 timing diagrams are contiguous.

Note 8: Refer to Application Note (9).

TC58A040F-20 1996 - 08 - 19

TOSHIBA CORPORATION

**TOSHIBA**

TECHNICAL DATA

#### Write

\* Note 9: Refer to Application Note (7).

Note: The above 3 timing diagrams are contiguous.

| TC58A040F-21        |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

**TOSHIBA**

TECHNICAL DATA

Note: The above 4 timing diagrams are contiguous.

| TC58A040F-22        |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

### **TOSHIBA**

TECHNICAL DATA

TC58A040 F

#### APPLICATION NOTES AND COMMENTS

#### (1) Prohibition of unspecified commands

The 12 operation commands are listed in the command table. Commands other than these specified commands are prohibited. Stored data may be corrupted if an unspecified command is entered during the command cycle.

#### (2) Interruption by $\overline{CS}$ going high

During the period when the TC58A040 is reading a page from the array ( $t_R$ ), writing a page to the array ( $t_{ROG}$ ), or erasing a block ( $t_{BERASE}$ ) or setting address ( $t_{SADD}$ ), the operation will complete regardless of the state of  $\overline{CS}$ . When the  $\overline{CS}$  pin go high during busy, the DO pin is in high impedance.

#### (3) Device reset

The TC58A040 is reset whenever  $\overline{\text{CS}}$  changes from low to high. The command register will be cleared at this point. The data register will continue to hold whatever data is in the register. To clear the data register, 32 bytes of "00H" data must be input.  $\overline{\text{CS}}$  does not affect operations as described in Application Note (2) above.

#### (4) Write disable at power-up

On power-up, the TC58A040 is set to Write Disable mode. This prevents any spurious writes to the device. To enable write operations, the Write Enable (E0H) command must be given.

#### (5) Prohibition of extra clocks

If an unexpected clock pulse is induced on the SK terminal by noise, the device may malfunction. Also, the device has no reset command. Therefore, noise must be controlled.

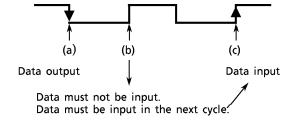

#### (6) Prohibition of data output and data input in the same cycle

Input and output operations in one cycle is prohibited. The following diagram shows an example.

#### (7) Busy state signal

When the device is in the Busy state (when the TC58A040 reads a page from the array (t<sub>R</sub>), writes a page to the array (t<sub>PROG</sub>), erases a block (t<sub>BERASE</sub>), or decodes an address (t<sub>SADD</sub>), the DO pin outputs a low level (Busy status). During this period operations, other than Status Read, are prohibited. If SK is clocked during this period, other than during a Status Read operation, the DI pin must be kept low. If SK is held high or low, the DI pin = "don't care".

| TC58A040F-23        |

|---------------------|

| 1996 - 08 - 19      |

| TOSHIBA CORPORATION |

### **TOSHIBA**

TECHNICAL DATA

TC58A040 F

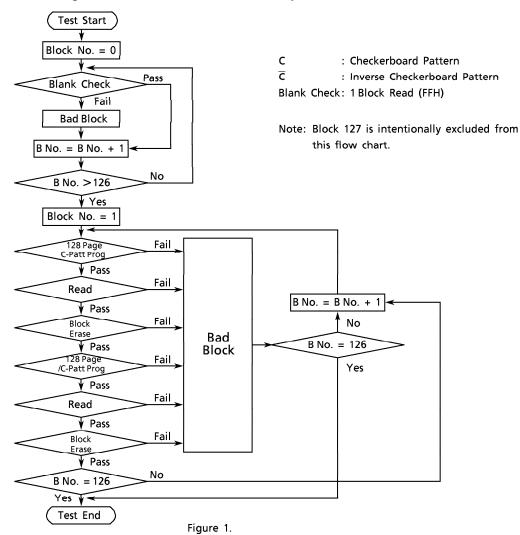

#### (8) Identification of bad blocks

The TC58A040 may contain unusable blocks. Bad blocks must be identified by user software during initial operation. The figure below describes how to identify bad blocks.

#### (9) End-of-operation signal

When a Data Shift Out, Data Shift In, or Status Read operation finishes, the  $\overline{\text{CS}}$  pin must go high or SK must stay low for at least 250 ns. This must occur before subsequent commands are input, such as Increment, Write Enable, or Write Disable.

#### **INTEGRATED** CIRCUIT **TOSHIBA**

TECHNICAL DATA TC58A040 F

#### (10) Error in Program or Erase operation (failure of at Status Read)

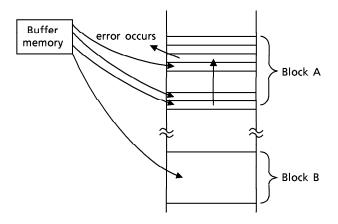

The device may fail during a Program or Erase operation due, for example, to the Write/Erase cycle limits being exceeded. The following system architecture will ensure high system reliability if a failure occurs:

#### **Program**

If an error occurs in Block A, try to reprogram the data into another block, Block B, by loading from an external buffer. Then, prevent further system accesses to Block A (by creating a "bad block" table or some other appropriate scheme).

#### **Erase**

When the error occurs after an Erase operation, prevent future accesses to this bad block (again by creating a table within the system or some other appropriate scheme).

# INTEGRATED CIRCUIT **TOSHIBA**

TECHNICAL DATA

TC58A040 F

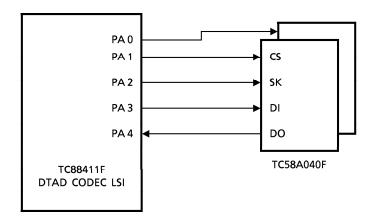

#### **SYSTEM CONCEPTS**

TC58A040 is a 4 Mbit NAND E2PROM designed to provide the most cost effective solution for digital audio recording applications. For digital audio storage, the TC58A040 has been matched with DTAD CODEC LSI TC88411F. Applications that can benefit from this combination include digital answering machines and personal digital recorders. Customers can quickly bring to market systems capable of recording up to 15 minutes of audio on a single 4 Mbit device. Multiple TC58A040s can be used to extend the recording time.

### **DATA TRANSFER RATE**

The data transfer rate of the TC58A040 is as follows:

|                                     | DATA TRANSFER RATE |               | TOTAL TIME     |         |

|-------------------------------------|--------------------|---------------|----------------|---------|

|                                     | PAGE               | BLOCK         | PAGE           | BLOCK   |

| Read                                | 0.85 Mbits/s       | 2.60 Mbits/s  | 301 <i>μ</i> s | 12.6 ms |

| Write (t <sub>PROG</sub> : 400 μs)  | 377.6 kbits/s      | 538.3 kbits/s | 678 μs         | 60.9 ms |

| Erase (t <sub>ERASE</sub> : 7.0 ms) | _                  | _             | -              | 7.0 ms  |

TC58A040 F

#### **DEVICE PHYSICS**

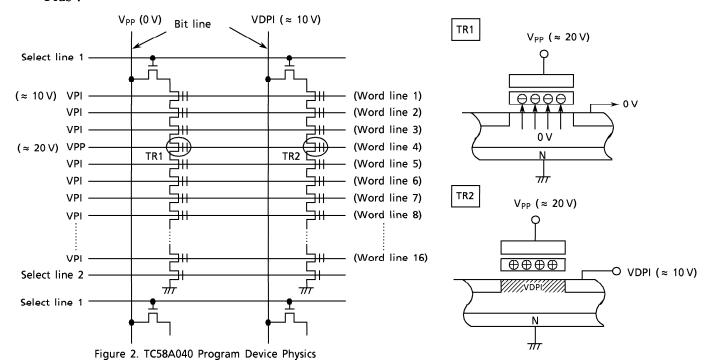

#### Program Operation

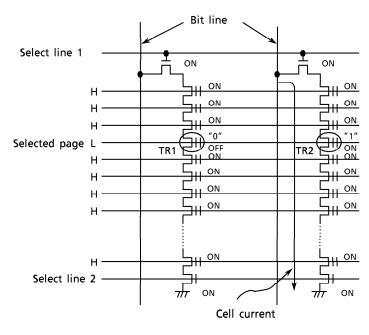

Figure 2 shows the NAND memory cell level details of the programming mechanism. The Program operation is used to write "0" data into an erased memory cell ("1" data cell) using a tunneling mechanism. An example Program operation to program "0" data into TR1 and "1" data into TR2 is as follows:

- (1) A high level is applied to Select line 1 and a low level is applied to Select line 2 so that the device is connected to the Bit line and disconnected from the ground line.

- (2) Vpp (to 20 V) is applied to the selected word line and an inhibit voltage of VPI (≈ 10 V) is applied to the unselected word lines.

- (3) 0 volts is applied to the bit line tied to cell transistor TR1 and the inhibit voltage VDP1 ( $\approx 10 \text{ V}$ ) is applied to the bit line tied to TR2.

- (4) Vpp is applied between the control gate and the channel in TR1, as shown in Figure 2, which causes electrons to be injected from the channel to the floating gate by a tunneling.

- (5) The injected electrons are captured in the floating gate (surrounded by an oxide layer) and will remain, even after power is cut off, until they are removed by an Erase operation.

- (6) Although 20 volts is applied to the control gate of TR2, the voltage difference between the control gate and the channel is only 10 V because the voltage of the channel is 10 V. Therefore, tunneling does not take place (i.e. the electron is not injected into the floating gate.)

- (7) Tunneling does not take place in the unselected pages because of the 10 V (VPI) applied to the unselected word lines which makes the voltage difference between the control gate and channel only 10 volts.

Thus, the floating gate of the "0" cell is charged to "Minus" and that of the "1" cell is charged to "Plus".

TC58A040F-27 1996-08-19 TOSHIBA CORPORATION

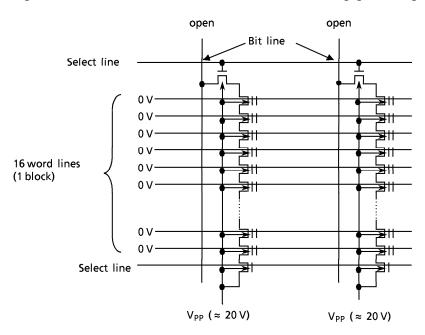

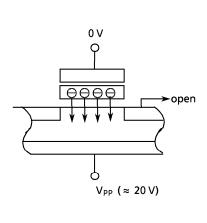

#### **Erase Operation**

Figure 3 shows the NAND memory cell level details of the Erase mechanism. The Erase operation is used to turn the "0" (programmed) cells back to "1" in a block. The captured electrons are pulled out from the floating gate to the substrate by a tunneling.

Zero volts is applied to the control gate and Vpp (to 20 V) is applied to the substrate so that a 20-volt potential is created and the electrons in the floating gate are pulled out by the tunneling.

Figure 3. TC58A040 Erase Device Physics

#### Read operation

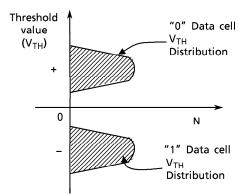

After programing the state of the memory cell is either "0" (minus charge on the floating gate) or "1" (plus charge on the floating gate). Each state is indicated by a "threshold voltage (Vth)" which is a characterization parameter of the MOS transistor as shown in Figure 4. The threshold voltage of a transistor with data "0" is distributed in the "plus" region while a transistor with data "1" is distributed in the "minus" region. The distribution band depends on transistor fluctuations.

Figure 4. V<sub>TH</sub> Distribution for "0" and "1" data cells

TECHNICAL DATA

Figure 5 shows memory cell level details of the Read operation.

- (1) A high voltage is applied to Select lines 1 and 2 in the block which includes the selected page, so that the 16 NAND memory cells are connected to the Bit line and ground.

- (2) Zero volts is applied to the control gates of the selected page and a high level voltage is applied to the control gates of the unselected pages.

- (3) In Figure 5, transistor TR2 with data "1" turns on, transistor TR1 with data "0" turns off, and all other unselected transistors turn on.

- (4) The precharged bit line tied to TR2 is discharged through TR2 as cell current flows to ground, while the precharged bit line tied to TR1 remains high level because current does not flow.

The sense amplifiers tied to the bit lines thus sense the voltage levels as "1" and "0" respectively.

Figure 5. TC58A040 Read Device Physics

TC58A040 F

TECHNICAL DATA

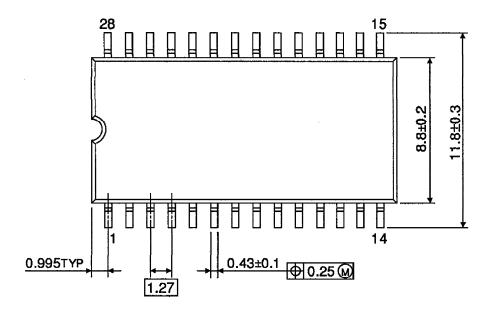

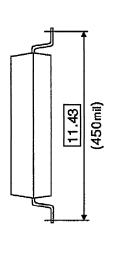

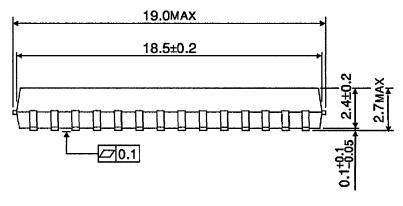

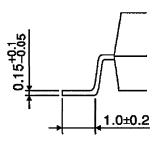

#### **PACKAGE DIMENSIONS**

• Plastic SOP

SOP28-P-450

UNITS: mm

| TC58A040F-30*       |  |  |  |

|---------------------|--|--|--|

| 1996 - 08 - 19      |  |  |  |

| TOSHIBA CORROBATION |  |  |  |