# TTIA0110G 10 Gbits/s Transimpedance Amplifier

#### **Features**

- 10 GHz bandwidth

- 1 k $\Omega$  transimpedance (single-ended)

- $\blacksquare$  Complementary 50  $\Omega$  outputs can be ac or dc coupled

- Equivalent input noise current 1.5 µArms

- Group delay ±15 ps

- dc output offset control

- Single –5.2 V power supply

- Power dissipation 0.8 W

- Die size: 1.600 mm x 1.225 mm

- Low pulse-width distortion

- Maximum input current 1.25 mA average

### **Applications**

- SONET/SDH OC-192/STM-64 receivers

- SONET/SDH OC-192/STM-64 test equipment

- Digital video transmission

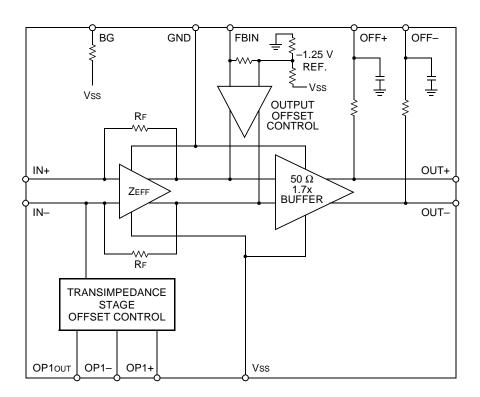

5-9408.a(F)

Figure 1. Functional Block Diagram

#### **Functional Description**

The Agere Systems Inc. TTIA0110G is a high-speed, wide dynamic range transimpedance amplifier. A typical application is a low-noise, high-speed lightwave receiver when combined with an APD or PIN photodetector. The targeted transmission system is OC-192/STM-64.

The amplifier consists of a differential transimpedance stage followed by an output buffer which provides complementary 50  $\Omega$  outputs. A wide dynamic range of linear operation is achieved by combining a low-noise input stage with an output buffer capable of providing a single-ended output swing of 800 mVp-p. Large output swings provide linear operation up to 360  $\mu A$  average input current. The offset between the two outputs is user adjustable and is controlled by the dc voltage at the FBIN pin.

The TTIA0110G contains two offset control circuits. The transimpedance stage offset control removes the average current from the input. This causes the average voltage of the differential outputs of the transimpedance stage to be equal. A second offset control

immediately following the transimpedance stage is available to the user. A single pin, FBIN, allows the user to apply a voltage to produce an offset between the two outputs of the TIA. FBIN nominally operates at around -1.25 V, has an input impedance of 10 k $\Omega$ , and has an inverting gain of 2 to the positive data output, OUT+, when the outputs are dc-coupled to 50  $\Omega$  loads. When the outputs are ac-coupled, there is an inverting gain of 4 from FBIN to OUT+. Differential gains are twice these values. Two 10  $k\Omega$  resistors are provided on the die to sense the average voltage of the two data outputs. One resistor is connected between OFF+ and OUT+, and the other is connected between OFF- and OUT-. An external op amp can be used to close the loop between the sensing points, OFF+ and OFF-, and FBIN (see Figure 5 and Figure 6).

Amplifier operation is from a single –5.2 V power supply. The TTIA0110G is available in die form.

#### Pin Information

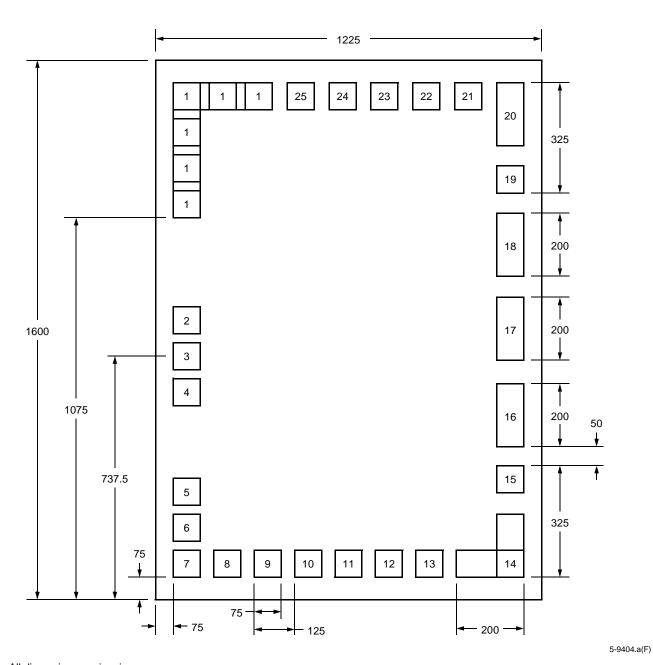

2

**Table 1. Pad Descriptions**

| Pad              | Symbol | Name/Function                                                                                                  |  |  |

|------------------|--------|----------------------------------------------------------------------------------------------------------------|--|--|

| 1                | IN+    | Complementary Input. This node must be ac-bypassed to ground.                                                  |  |  |

| 2, 4, 15, 17, 19 | GND    | <b>Ground.</b> Pads are connected to the back side of the die through substrate vias. The                      |  |  |

|                  |        | back side of the die must be electrically connected to ground.                                                 |  |  |

| 3                | IN-    | Amplifier Input. Connect to detector anode, current should enter this node.                                    |  |  |

| 5, 6, 7, 8, 12,  | DNC    | Do Not Connect. Internal test point or reserved future use.                                                    |  |  |

| 13, 25           |        |                                                                                                                |  |  |

| 9                | ОР1оит | Transimpedance Stage Offset Control Output.                                                                    |  |  |

| 10               | OP1-   | Transimpedance Stage Offset Control Inverting Input.                                                           |  |  |

| 11               | OP1+   | Transimpedance Stage Offset Control Noninverting Input.                                                        |  |  |

| 14, 20           | Vss    | Supply Voltage. –5.2 Vdc nominal.                                                                              |  |  |

| 16               | OUT-   | Inverted Data Output. Produces low-level output for current entering IN                                        |  |  |

| 18               | OUT+   | Noninverted Data Output. Produces high-level output for current entering IN                                    |  |  |

| 21               | OFF-   | Offset Senses average voltage of OUT- pin.                                                                     |  |  |

| 22               | OFF+   | Offset +. Senses average voltage of OUT+ pin.                                                                  |  |  |

| 23               | FBIN   | Feedback In. Apply external voltage to produce offset between OUT- and OUT+.                                   |  |  |

| 24               | BG     | <b>Band Gap Reference.</b> Connection for external –2.5 Vdc voltage reference (typical use is an Si band gap). |  |  |

Draft Copy Agere Systems Inc.

# Pin Information (continued)

Note: All dimensions are in microns.

Figure 2. Die Pad Configuration

Agere Systems Inc. Draft Copy 3

### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

Table 2. Absolute Maximum Ratings<sup>1</sup>

| Parameter                            | Symbol | Min | Max           | Unit |

|--------------------------------------|--------|-----|---------------|------|

| Supply Voltage (reference to ground) | Vss    | _   | <i>–</i> 5.75 | V    |

| Input Voltage                        | Vin    | GND | Vss           | V    |

| Power Dissipation                    | PD     | _   | 0.85          | W    |

| Storage Temperature Range            | Tstg   | -40 | 125           | °C   |

| Operating Temperature Range          | TA     | 0   | 100           | °C   |

<sup>1.</sup> Long term reliability is not guaranteed in a non-hermetic environment.

### **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Agere employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used in the defined model. No industry-wide standard has been adopted for the CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes.

**Table 3. Handling Precautions**

| Device    | Voltage |  |  |

|-----------|---------|--|--|

| TTIA0110G | TBD     |  |  |

### **Die Attachment**

The TTIA0110G die must be used in a hermetic environment. The die should be attached with conductive epoxy. If solder is required, an 80 Au/20 Sn solder preform can be used. Using a solder preform eliminates the need for flux. Preforms typically melt at 280 °C, but should be soaked at 305 °C for five to eight seconds. Once the preform melts, a die scrub motion should be used to ensure a good contact. Do not use a vacuum tool to pick-up the die. This may result in damage to air bridges on the die surface. Use a collet for die pick-up to avoid air bridge damage. The TTIA0110G die is 4 mils thick.

4 **Draft Copy** Agere Systems Inc.

## **Recommended Operating Conditions**

**Table 4. Recommended Operating Conditions**

| Parameter             | Symbol | Min   | Max          | Unit |

|-----------------------|--------|-------|--------------|------|

| Power Supply Voltage  | Vss    | -4.75 | <b>-</b> 5.5 | V    |

| Operating Temperature | TA     | 0     | 70           | °C   |

#### **Electrical Characteristics**

TA = 25 °C, Vss = -5.2 V, and RLOAD =  $50~\Omega$ , dc coupled. Bit rate = 9,953.28 Mbits/s NRZ and data pattern =  $2^{31}-1$  PRBS, unless otherwise indicated. Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements.

**Table 5. Electrical Characteristics**

| Symbol | Parameter                          | Conditions <sup>1</sup> | Min | Тур | Max | Unit  |

|--------|------------------------------------|-------------------------|-----|-----|-----|-------|

| Zeff   | Small Signal Transimpedance        | Single Ended            | _   | 1   | _   | kΩ    |

|        | Equivalent Input Noise Current     | f = 8 GHz               | _   | 1.5 | _   | μArms |

|        | Input Current for Linear Operation | <del>-</del>            | _   | 360 | _   | μAavg |

| V±OUT  | Output Voltage                     | Single Ended            | _   | 800 | _   | mVp-p |

| f3dB   | Small Signal Bandwidth             | <del>-</del>            | _   | 10  | _   | GHz   |

|        | Group Delay                        | 50 MHz to 7 GHz         | _   | ±15 | _   | ps    |

| S22    | Output Return Loss                 | Over f3dB Bandwidth     | _   | 12  | _   | dB    |

| Iss    | Power Supply Current               | Vss = −5.2 V            | _   | 155 |     | mA    |

<sup>1.</sup> CDET = 0.2 pF, LDET = 1.0 nH, RDET = 10  $\Omega$ .

Agere Systems Inc. Draft Copy 5

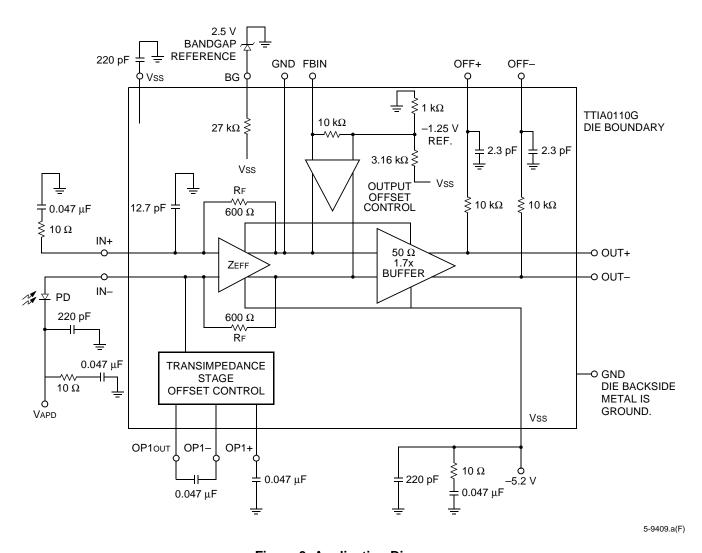

## **Application Information**

6

The ground pads on the die are connected to the back side of the die through substrate vias. The back side of the die is metallized with gold and must be electrically connected to ground. It is not necessary to wire bond to the ground pads of the die.

Figure 3. Application Diagram

# **Applications Information** (continued)

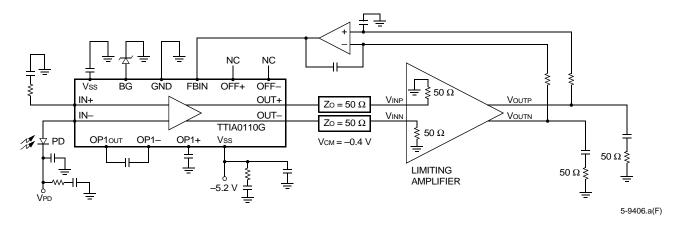

## **Typical Application Circuits**

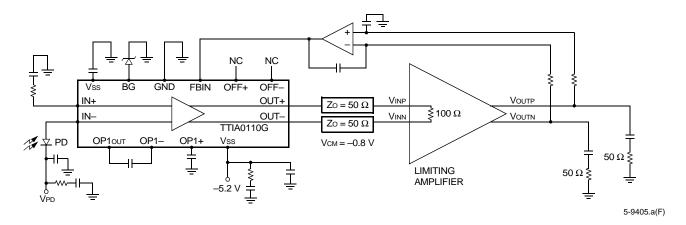

Figure 4. dc-Coupled to Limiting Amplifier

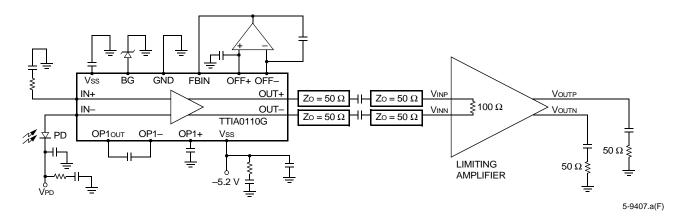

Figure 5. dc-Coupled to Limiting Amplifier

Figure 6. ac-Coupled to Limiting Amplifier

Agere Systems Inc. Draft Copy 7

#### Chip Visual Inspection Criteria

The chips will be visually free of the following defects, at 100x:

- Scratches in the metallization (including air-bridges) that leave less than 50% of the original width undisturbed and distort the outline of the metal feature.

- Voids or missing metallization that leave less than 50% of the original width undisturbed.

- Extra metals that bridge adjacent same layer metal feature. This includes bond pads damaged from probing.

- Crack or chip out that extends into the active area of the device.

- Damaged air-bridges that have been distorted or torn off.

- Particles on the surface of the chip that are large enough to bridge between bond pads.

- Stains larger than the size of a bond pad.

- Lifted or blistered metallization.

- Missing nitride that occurs over or under an active feature.

- Defects to bond pad area:

- Stains larger than 25% of bond pads.

- Extra nitride on the bond pad that reduces the open area by more than 25%.

- Probe damage that removes more than 25% of the bond pad.

- Probe damage that causes cracks in the surrounding nitride of substrate.

#### Ordering Information

| Device Code | Package | Comcode   |  |  |

|-------------|---------|-----------|--|--|

| TTIA0110G51 | Die     | 108559071 |  |  |

For additional information, contact your Agere Systems Account Manager or the following: INTERNET: http://www.agere.com

E-MAIL: docmaster@micro.lucent.com

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 N. AMERICA: 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA: Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC

Tel. (86) 21 50471212, FAX (86) 21 50472266

JAPAN: Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 Data Requests: DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot)

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

FUROPF: