**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC90A11F

# MULTI SYSTEM 3DIM. DNR IC (FOR VCR)

TC90A11F is the digital video signal processor, which reduces the noise on the playback video signal of VCR, with the external video memory IC (2Mbit FIFO type). This IC is available for NTSC, PAL, etc. in world wide area.

### **FEATURES**

- Built-in 2 channels A/D converters.

(for Luma & for Chroma)

- Built-in 2 channels D/A converters. A channel can be selected the output signal, Luma (Y) or Y/C mix. The other is for chroma output signal.

Weight: 1.1g (Typ.)

- Multi system, NTSC (3.58MHz, 4.43MHz), PAL and NTSC on PAL. (applying YNR only at SECAM)

- Built-in the clock generaters.

at NTSC :  $\times 4$  PLL of fsc (chroma subcarrier frequency)

at PAL : VCXO circuit locked the color burst.

- Built-in the digital H-PLL circuit and the digital V-PLL circuit.

- 3 kinds of NR system, Frame comb (NTSC only), Field comb, Line comb (for Trick mode).

- Applicable 2Mbit memory IC : μPD42280 (NEC), MSM518221

- Built-in the digital CTI (color detail enhancer)

- I<sup>2</sup>C control

<u>961001EBA1</u>

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

<sup>■</sup> TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade control laws.

**TOSHIBA**

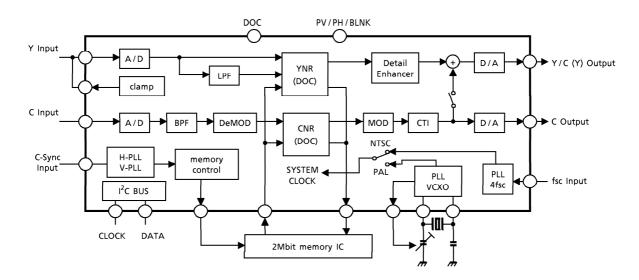

# **BLOCK DIAGRAM**

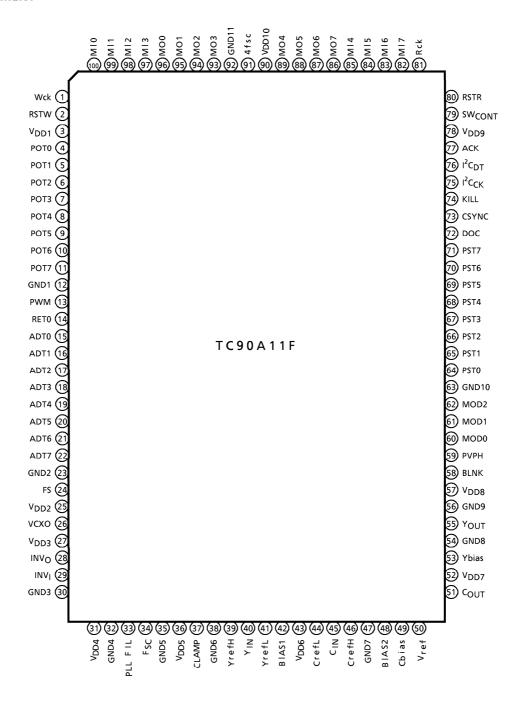

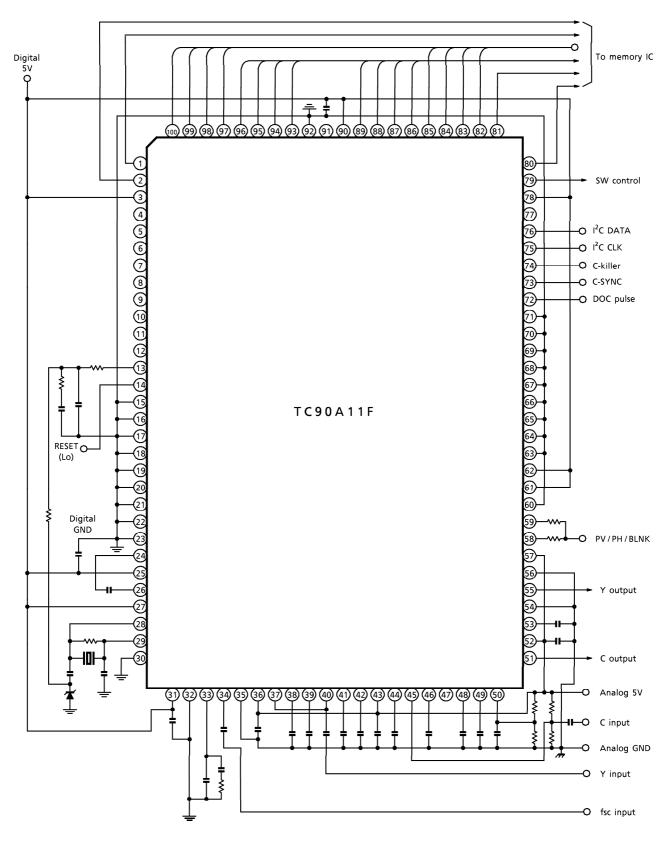

#### **PIN ASSIGNMENT**

# PIN DESCRIPTION

| PIN<br>No. | NAME             | 1/0    | FUNCTION                    | REMARKS                                                    |  |  |

|------------|------------------|--------|-----------------------------|------------------------------------------------------------|--|--|

| 1          | Wck              | Output | Writing clock to memory IC  | High level>2.4V, low level<0.6V                            |  |  |

| 2          | RSTW             | Output | Write reset pulse to memory | High level>2.4V, low level<0.6V                            |  |  |

| 3          | V <sub>DD1</sub> | _      | Digital voltage supply (5V) | _                                                          |  |  |

| 4          | POT0             | Output |                             |                                                            |  |  |

| 5          | POT1             | Output |                             |                                                            |  |  |

| 6          | POT2             | Output |                             |                                                            |  |  |

| 7          | РОТ3             | Output | Outrot of took or or its o  | Output high level>2.4V,                                    |  |  |

| 8          | POT4             | Output | Output of test monitor      | Output low level < 0.6V                                    |  |  |

| 9          | POT5             | Output |                             |                                                            |  |  |

| 10         | РОТ6             | Output |                             |                                                            |  |  |

| 11         | POT7             | Output |                             |                                                            |  |  |

| 12         | GND1             | _      | Digital GND                 | _                                                          |  |  |

| 13         | PWM              | Output | VCXO control output         | High level>2.4V, low level<0.6V                            |  |  |

| 14         | RETO             | Input  | Reset pin of internal logic | _                                                          |  |  |

| 15         | ADT0             | Input  |                             |                                                            |  |  |

| 16         | ADT1             | Input  |                             |                                                            |  |  |

| 17         | ADT2             | Input  |                             |                                                            |  |  |

| 18         | ADT3             | Input  | Dulas is most fan tastis n  | Threshold of high level < 2.4V                             |  |  |

| 19         | ADT4             | Input  | Pulse input for testing     | Threshold of low level>0.8V                                |  |  |

| 20         | ADT5             | Input  |                             |                                                            |  |  |

| 21         | ADT6             | Input  |                             |                                                            |  |  |

| 22         | ADT7             | Input  |                             |                                                            |  |  |

| 23         | GND2             | _      | Digital GND                 | _                                                          |  |  |

| 24         | FS               | Input  | Clock input (for VCXO)      | Internal DC BIAS, minimum input level<1V <sub>p-p</sub>    |  |  |

| 25         | V <sub>DD2</sub> | _      | Digital GND                 |                                                            |  |  |

| 26         | VCXO             | Output | Buffer output of VCXO       | Threshold (high)<2.4V, Threshold (low)>0.6V                |  |  |

| 27         | V <sub>DD3</sub> | _      | Voltage supply of VCXO      | _                                                          |  |  |

| 28         | INVO             | Output | Inverter output of VCXO     | _                                                          |  |  |

| 29         | INVi             | Input  | Inverter input of VCXO      | _                                                          |  |  |

| 30         | GND3             | _      | GND of VCXO                 | _                                                          |  |  |

| 31         | V <sub>DD4</sub> | _      | Voltage supply of ×4 PLL    | Recommend digital voltage supply (5V)                      |  |  |

| 32         | GND4             | _      | GND of ×4 PLL               | Recommend digital GND                                      |  |  |

| 33         | PLL FIL          | _      | Loop filter of ×4 PLL       | _                                                          |  |  |

| 34         | F <sub>SC</sub>  | Input  | Fsc input for ×4 PLL        | Internal DC BIAS,<br>minimum input level<1V <sub>p-p</sub> |  |  |

| 35         | GND5             | _      | GND of AD converter         | Recommend analog GND                                       |  |  |

| 36         | V <sub>DD5</sub> | _      | Voltage supply of AD conv.  | Recommend analog voltage supply (5V)                       |  |  |

| 37         | CLAMP            | Output |                             | 3/10×V <sub>DD</sub> (5V)                                  |  |  |

| 38         | GND6             | _      | GND of AD converter         | Recommend analog GND                                       |  |  |

| 39         | YrefH            | _      | High level REF. for Y-ADC   | _                                                          |  |  |

| 40         | Y <sub>IN</sub>  | Input  | Y (Luma) input              | Typ. input: 1.6V <sub>p-p</sub> , signal CLAMP by pin 37   |  |  |

| PIN<br>No. | NAME                           | 1/0    | FUNCTION                                | REMARKS                                                                    |  |  |

|------------|--------------------------------|--------|-----------------------------------------|----------------------------------------------------------------------------|--|--|

| 41         | YrefL                          | _      | Low level REF. for Y-ADC                | _                                                                          |  |  |

| 42         | BIAS1                          |        | BIAS of AD converter                    | Common to Y-ADC and C-ADC                                                  |  |  |

| 43         | V <sub>DD6</sub>               | _      | Voltage supply of AD conv.              | Recommend analog voltage supply (5V)                                       |  |  |

| 44         | CrefL                          | _      | Low level REF. for C-ADC                | _                                                                          |  |  |

| 45         | C <sub>IN</sub>                | Input  | C (Chroma) input                        | External BIAS : 1/2 V <sub>DD</sub> ,<br>Typ. input : 1.14V <sub>p-p</sub> |  |  |

| 46         | CrefH                          | _      | High level REF. for C-ADC               | <del>-</del>                                                               |  |  |

| 47         | GND7                           | _      | GND of AD converter                     | Recommend analog GND                                                       |  |  |

| 48         | BIAS2                          | _      | BIAS of DA converter                    | _                                                                          |  |  |

| 49         | Cbias                          | _      | BIAS of C-DAC                           | _                                                                          |  |  |

| 50         | V <sub>ref</sub>               | _      | Reference voltage of DAC                | _                                                                          |  |  |

| 51         | C <sub>OUT</sub>               | Output | C (Chroma) output                       | ON/OFF (fix to V <sub>DD</sub> ) controlled by BUS data                    |  |  |

| 52         | V <sub>DD7</sub>               | _      | Voltage supply of DA conv.              | Recommend analog voltage supply (5V)                                       |  |  |

| 53         | Ybias                          | _      | BIAS of Y-DAC                           | _                                                                          |  |  |

| 54         | GND8                           | _      | GND of DA converter                     | Recommend analog GND                                                       |  |  |

| 55         | Yout                           | Output | Y (Luma) or Y/C output                  | ON/OFF (fix to V <sub>DD</sub> ),<br>Y/C mix ON/OFF controlled by BUS      |  |  |

| 56         | GND9                           |        | Digital GND                             | _                                                                          |  |  |

| 57         | $V_{DD8}$                      |        | Digital voltage supply (5V)             | _                                                                          |  |  |

| 58         | BLNK                           | Input  | Chroma mute (ON/OFF by BUS)             | VTH: 1/6 V <sub>DD</sub> , Lo = mute ON (for OSD character)                |  |  |

| 59         | PVPH                           | Input  | Chroma mute (ON/OFF by BUS)             | VTH: 1/2 V <sub>DD</sub> , Hi = mute ON (for SYNC period)                  |  |  |

| 60         | MOD0                           | Input  |                                         |                                                                            |  |  |

| 61         | MOD1                           | Input  | Test mode select                        | _                                                                          |  |  |

| 62         | MOD2                           | Input  |                                         |                                                                            |  |  |

| 63         | GND10                          | _      | Digital GND                             | _                                                                          |  |  |

| 64         | PST0                           | Input  |                                         |                                                                            |  |  |

| 65         | PST1                           | Input  |                                         |                                                                            |  |  |

| 66         | PST2                           | Input  |                                         |                                                                            |  |  |

| 67         | PST3                           | Input  | Test signal input                       | Threshold of high level < 2.4V                                             |  |  |

| 68         | PST4                           | Input  |                                         | Threshold of low level >0.8V                                               |  |  |

| 69         | PST5                           | Input  |                                         |                                                                            |  |  |

| 70         | PST6                           | Input  |                                         |                                                                            |  |  |

| 71         | PST7                           | Input  |                                         |                                                                            |  |  |

| 72         | DOC                            | Input  | DOC pulse input                         | <0.8V→DOC ON, >2.4V→OFF                                                    |  |  |

| 73         | CSYNC                          | Input  | C-SYNC input                            | VTH: <2.4V/>0.8V, hysteresis: 0.4V                                         |  |  |

| 74         | KILL                           | Input  | Color killer                            | >2.4V→killer ON, <0.8V→OFF                                                 |  |  |

| 75         | I <sup>2</sup> C <sub>CK</sub> | Input  | Click input of I <sup>2</sup> C BUS     | VTH: <2.4V/>0.8V, hysteresis: 0.4V                                         |  |  |

| 76         | I <sup>2</sup> C <sub>DT</sub> | Input  | Data input of I <sup>2</sup> C BUS      | _                                                                          |  |  |

| 77         | ACK                            | Output | Acknowledge output I <sup>2</sup> C BUS | High level>2.4V, low level<0.6V                                            |  |  |

| 78         | V <sub>DD9</sub>               | _      | Digital voltage supply (5V)             |                                                                            |  |  |

| 79         | SWCONT                         |        | BUS decode output                       | High level>2.4V, low level<0.6V                                            |  |  |

| 80         | RSTR                           | Output | Read reset pulse to memory              | High level>2.4V, low level<0.6V                                            |  |  |

| PIN<br>No. | NAME              | 1/0    | FUNCTION                    | REMARKS                                       |  |  |

|------------|-------------------|--------|-----------------------------|-----------------------------------------------|--|--|

| 81         | Rck               | Output | Reading clock to memory IC  | High level>2.4V, low level<0.6V               |  |  |

| 82         | MI7               | Input  |                             |                                               |  |  |

| 83         | MI6               | Input  | Data input from moment IC   | Threshold of high level < 2.4V                |  |  |

| 84         | MI5               | Input  | Data input from memory IC   | Threshold of low level>0.8V                   |  |  |

| 85         | MI4               | Input  |                             |                                               |  |  |

| 86         | MO7               | Output |                             |                                               |  |  |

| 87         | MO6               | Output | Data cutnut to moment IC    | Output high level>2.4V, Output low level<0.6V |  |  |

| 88         | MO5               | Output | Data output to memory IC    |                                               |  |  |

| 89         | MO4               | Output |                             |                                               |  |  |

| 90         | V <sub>DD10</sub> | _      | Digital voltage supply (5V) | _                                             |  |  |

| 91         | 4fsc              | Output | System clock monitor        | High level>2.4V, low level<0.6V               |  |  |

| 92         | GND11             | _      | Digital GND                 | _                                             |  |  |

| 93         | MO3               | Output |                             |                                               |  |  |

| 94         | MO2               | Output | Data autnut ta mamanu IC    | Output high level>2.4V,                       |  |  |

| 95         | MO1               | Output | Data output to memory IC    | Output low level < 0.6V                       |  |  |

| 96         | MO0               | Output |                             |                                               |  |  |

| 97         | MI3               | Input  |                             |                                               |  |  |

| 98         | MI2               | Input  | Data input from memory IC   | Threshold of high level < 2.4V                |  |  |

| 99         | MI1               | Input  | Data input from memory ic   | Threshold of low level>0.8V                   |  |  |

| 100        | MIO               | Input  |                             |                                               |  |  |

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL                | RATING                   | UNIT     |

|-----------------------|-----------------------|--------------------------|----------|

|                       |                       |                          |          |

| Supply Voltage        | $V_{DD}$              | <b>-</b> 0.3∼ + 6.0      | V        |

| Input Voltage         | VIN                   | $-0.3 \sim V_{DD} + 0.3$ | <b>\</b> |

| Power Dissipation     | P <sub>D</sub> (Note) | 1.75                     | W        |

| Operating Temperature | T <sub>opr</sub>      | <b>- 10∼75</b>           | °C       |

| Storage Temperature   | T <sub>stg</sub>      | <b>- 40∼125</b>          | °C       |

(Note)  $Ta = 25^{\circ}C$

**TOSHIBA**

# **ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS (Ta =  $-10\sim75^{\circ}$ C,  $V_{DD} = 4.75\sim5.25V$ )

| CHARACTERISTIC         | PIN              | SYMBOL           | TEST<br>CONDITION         | MIN.                     | TYP. | MAX.                     | UNIT |  |

|------------------------|------------------|------------------|---------------------------|--------------------------|------|--------------------------|------|--|

| Supply Current         | _                | I <sub>DD</sub>  | _                         | _                        | _    | 165                      | mΑ   |  |

|                        | (*A)             | V <sub>IH1</sub> | _                         | 2.4                      | _    | _                        |      |  |

| Threshold of High      | (*B)             | V <sub>IH2</sub> | _                         | 2.4                      | _    | _                        |      |  |

| Level                  | (*C)             | V <sub>IH3</sub> | _                         | 4.0                      | _    | _                        | V    |  |

| Level                  | 59 (PV/PH)       | V <sub>IH4</sub> | _                         | 1/2V <sub>DD</sub> + 0.3 | _    | _                        |      |  |

|                        | 58 (BLNK)        | V <sub>IH5</sub> | _                         | 1/6V <sub>DD</sub> + 0.2 |      | _                        |      |  |

|                        | (*A)             | V <sub>IL1</sub> | _                         |                          | _    | 0.8                      | 0.8  |  |

|                        | (*B)             | V <sub>IL2</sub> | _                         |                          |      | 0.8                      |      |  |

| Threshold of Low Level | (*C)             | V <sub>IL3</sub> |                           |                          | _    | 1.0                      | V    |  |

|                        | 59 (PV/PH)       | V <sub>IL4</sub> | _                         |                          | _    | 1/2V <sub>DD</sub> – 0.3 |      |  |

|                        | 58 (BLNK)        | V <sub>IL5</sub> | _                         |                          | _    | 1/6V <sub>DD</sub> - 0.2 |      |  |

| Input Current (High)   | (*A), (*B), (*C) | l <sub>IH1</sub> | _                         | <b>– 10</b>              | _    | + 10                     | μΑ   |  |

| Input Current (Low)    | (*A), (*B), (*C) | l <sub>IH2</sub> | _                         | <b>– 10</b>              | _    | + 10                     | μΑ   |  |

| Output High Level      | _                | Voн              | I <sub>OH</sub><br>= -4mA | 2.4                      | _    | _                        | V    |  |

| Output Low Level       | _                | VOL              | I <sub>OL</sub> = 4mA     | _                        | _    | 0.6                      | V    |  |

| Hysteresis Level       | _                | V <sub>HS</sub>  | _                         | _                        | 0.4  | _                        | V    |  |

<sup>(\*</sup>A) 15 – 22, 64, 72, 74, 82, 85, 97, 100

<sup>(\*</sup>B) 73, 75

<sup>(\*</sup>C) 14, 60 – 62

# AC CHARACTERISTICS (Ta = $25^{\circ}$ C, $V_{DD} = 5V$ )

| CHARACTERISTIC                              | SYMBOL             | TEST CONDITION                                   | MIN.                 | TYP.        | MAX.                 | UNIT             |  |

|---------------------------------------------|--------------------|--------------------------------------------------|----------------------|-------------|----------------------|------------------|--|

| Input Level (Y)                             | Yin                | White 100% at pin 40                             | _                    | 1.6         | 2.0                  | V <sub>p-p</sub> |  |

| Input Level (C)                             | Cin                | 100 IRE Chroma at pin 45                         | _                    | 1.15        | 2.0                  | V <sub>p-p</sub> |  |

| Fsc (Pin 34) Input Level                    | Lsc                | Sine wave at pin 34                              | 0.3                  | 1.0         | 2.0                  | V <sub>p-p</sub> |  |

| Operation Frequency<br>Range                | Fsc                | 1.0V <sub>p-p</sub> sine wave at pin 34          | 3.47                 | 3.58 / 4.43 | 4.58                 | MHz              |  |

| FS (Pin 24) Input Level                     | Lfs                | _                                                | 1.0                  | _           | _                    | V                |  |

| Input Range of AD<br>Conv.                  | AD IN              | Pin 40, pin 45                                   | 3/10 V <sub>DD</sub> | _           | 7/10 V <sub>DD</sub> | ٧                |  |

| Output Signal Level at<br>Pin 55            | Yout               | Yin = $1.6V_{p-p}$<br>$V_{ref} = 2.5V (pin 50)$  | _                    | 2.0         | _                    | V <sub>p-p</sub> |  |

| Output Chroma Level<br>at Pin 55 & Pin 51   | C <sub>out</sub>   | Cin = $1.15V_{p-p}$<br>$V_{ref} = 2.5V (pin 50)$ | _                    | 1.43        | _                    | V <sub>p-p</sub> |  |

| Output Impedance                            | Zo                 | <del>-</del>                                     | 200                  | 350         | 700                  | Ω                |  |

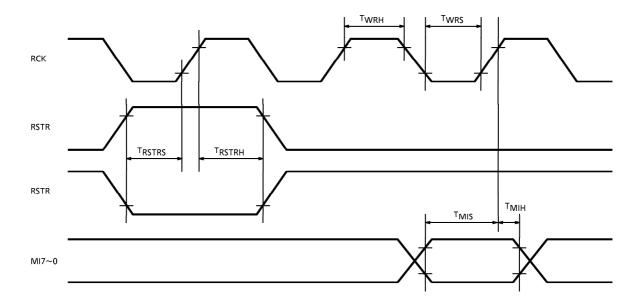

| Set Up Period to Read<br>the Data of Memory | TMIS               | _                                                | 25                   | _           | _                    | ns               |  |

| Hold Period to Read the Data of Memory      | ТМІН               | _                                                | 3                    | _           | _                    | ns               |  |

|                                             | TWRH               |                                                  | 20                   | _           | _                    |                  |  |

| Clock Pulse Width to                        | TWRL               | lood impodones , 15-5                            | 20                   | _           | _                    | ns               |  |

| Memory IC                                   | TwwH               | Load impedance : 15pF                            | 20                   |             | _                    | 115              |  |

|                                             | TWWL               |                                                  | 20                   | _           | _                    |                  |  |

|                                             | TRSTRS             |                                                  | 15                   | _           | _                    |                  |  |

|                                             | TRSTRH             |                                                  | 10                   | _           | _                    |                  |  |

| Pulse Timing to                             | T <sub>RSTWS</sub> |                                                  | 15                   |             | _                    | ns               |  |

| Memory IC                                   | T <sub>RSTWH</sub> | _                                                | 10                   |             | _                    | 113              |  |

|                                             | TMOS               |                                                  | 15                   |             | _                    |                  |  |

|                                             | Тмон               |                                                  | 10                   | _           | _                    |                  |  |

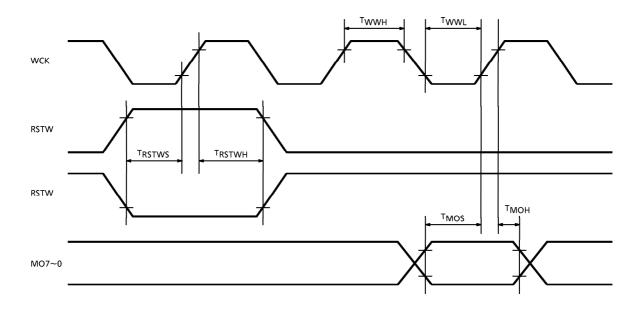

# **TIMING CHART**

#### **I<sup>2</sup>C-BUS OUTLINE**

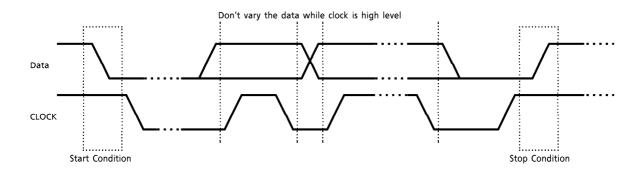

The I<sup>2</sup>C-BUS has two wires, serial data (SDA) and serial clock (SCL) which carry information between the IC's are connected to the bus line. The bus is considered to be busy after the "Start Condition". The bus is considered to be free again after the "Stop Condition".

A HIGH to LOW transition of the SDA line while SCL is HIGH, defines a Start Condition.

A LOW to HIGH transition of the SDA line while SCL is HIGH, defines a Stop Condition.

Every bytes put on the SDA line must be 8bit long. Each byte has to be followed by acknowledge bit. Each SDA and SCL has to be pulled up the voltage supply via a resistor.

DON'T ...... Don't vary the data while clock is high level at data transmission.

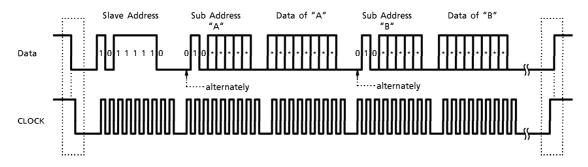

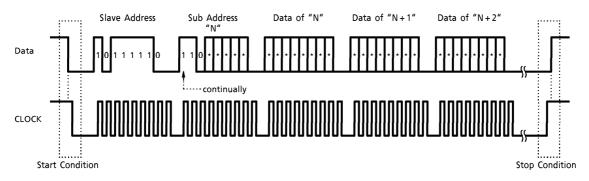

This IC adopts the sub address format. Send the sub address and the data alternately after the slave address. If the first bit of the sub address which is sent first is changed to "1", some data can be sent continually. (Refer to follow)

#### INPUT SUB ADD. AND DATA ALTERNATELY

#### INPUT DATA CONTINUALLY AFTER SUB ADD.

# **CONTENTS OF BUS LINE CONTROL**

Table of I<sup>2</sup>C BUS control Slave address = (101111110)

| SUB ADD.  | D <sub>7</sub>             | D <sub>6</sub>   | D <sub>5</sub>  | D <sub>4</sub>   | D <sub>3</sub>                 | D <sub>2</sub>          | D <sub>1</sub> | D <sub>0</sub>   |  |

|-----------|----------------------------|------------------|-----------------|------------------|--------------------------------|-------------------------|----------------|------------------|--|

| 40        | K factor of                | YNR              |                 |                  | Limiter level of YNR           |                         |                |                  |  |

| 41        | K factor of                |                  |                 |                  | Limiter level of CNR           |                         |                |                  |  |

| 42        | Offset of Y                | motion de        | tector for Y    | NR               | Slope of Y det. for YNR 0 (Nor |                         |                | 0 (None)         |  |

| 43        | Offset of Y                | motion de        | tector for C    | NR               | Slope of Y<br>CNR              | det. for                | 0 (None)       | 0 (None)         |  |

| 44        | Offset of C                | motion de        | tector for C    | NR               | Slope of C<br>CNR              | det. for                | 0 (None)       | 0 (None)         |  |

| 45        | Y motion of                | det. referend    | e level for     | cross color      | Chroma ref                     | ference leve            | I for cross c  | olor             |  |

| 46        | Motion de                  | tector OFF (     | still)          | Y-mot.<br>wide   | 0 (TEST)                       | NR OFF                  | 0 (TEST)       | 443NTSC          |  |

| 47        | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | 0 (TEST)       | Mod. OFF         |  |

| 48        | Delay of ch                | roma mute        | for BLNK p      | ulse             |                                | C-Mute<br>OFF           | Y/C<br>DELAY   | 0 (TEST)         |  |

| 49        | 0 (TEST)                   | 0 (TEST)         | Timing adj      | ustment of       | the delayed                    | signal from             | memory         |                  |  |

| 4A        | PAL                        | Timing adj       | ustment bet     | ween video       | signal and                     | C-sync                  |                |                  |  |

| 4B        | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | 1 (TEST)       | 0 (TEST)         |  |

| 4C        | 0 (TEST)                   | 0 (TEST) 0 (TEST |                 | 0 (TEST)         | 0 (TEST) 0 (Fix)               |                         | Memory IC      | Field /<br>frame |  |

| 4D        | 0 (TEST)                   | SW<br>Control    | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (Fix)                 | 0 (TEST)       | 0 (TEST)         |  |

| 4E        | 0 (Fix)                    | 0 (TEST)         | 0 (TEST)        | 0 (Fix)          | 0 (TEST)                       | 0 (TEST)                | 0 (TEST)       | 0 (TEST)         |  |

| 4F        | Y-DOC                      | C-DOC            | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | BPF OFF        | 0 (TEST)         |  |

| 50        | 0 (TEST)                   | 1 (Fix)          | Stand<br>non St | lard /<br>andard | SW CLK VCXO OFF                |                         | PLL OFF        | 1 (Fix)          |  |

| 51        | 50Hz /<br>60Hz             | 4.43 / 3.58      | line NR         | V mask po        | sition for br                  | st PLL                  | 0 (TEST)       | 1<br>(TEST CLR)  |  |

| 52        | Burst gate                 | position for     | VCXO            |                  |                                |                         |                | 1 (Fix)          |  |

| 53        | C-NC ON                    | Limiter leve     | el of C-NC      | Y-DAC ON         | C-DAC ON                       | PV / PH<br>OFF          | 0 (TEST)       | 0 (TEST)         |  |

| 54        | Delay of Y                 | signal           | Delay of C      | signal           | 0 (Fix)                        | 1 (Fix)                 | DeMod.<br>OFF  | Y/C<br>Mix/Sep   |  |

| 55        | 0 (TEST)                   | 0 (TEST)         | 0 (Fix)         | 0 (Fix)          | 0 (Fix)                        | PAL/NTSC                | 0 (TEST)       | 0 (TEST)         |  |

| 56        | Y detail enhanced<br>level |                  | C-enh.<br>det.  | C-enh. 0 (Fix)   |                                | C detail enhanced level |                | 0 (TEST)         |  |

| 57 (TEST) | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | 0 (TEST)       | 0 (TEST)         |  |

| 58 (TEST) | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | 0 (None)       | 0 (None)         |  |

| 59 (TEST) | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (None)                | 0 (TEST)       | 0 (TEST)         |  |

| 5A (TEST) | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (None)         | 0 (None)                       | 0 (None)                | 0 (None)       | 0 (TEST)         |  |

| 5B (TEST) | 0 (TEST)                   | 0 (None)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (None)                | 0 (TEST)       | 0 (TEST)         |  |

| 5C (TEST) | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | 0 (TEST)       | 0 (TEST)         |  |

| 5D (TEST) | 0 (TEST)                   | 0 (TEST)         | 0 (TEST)        | 0 (TEST)         | 0 (TEST)                       | 0 (TEST)                | 0 (TEST)       | 0 (TEST)         |  |

#### **DETAIL EXPLANATION OF BUS CONTROL**

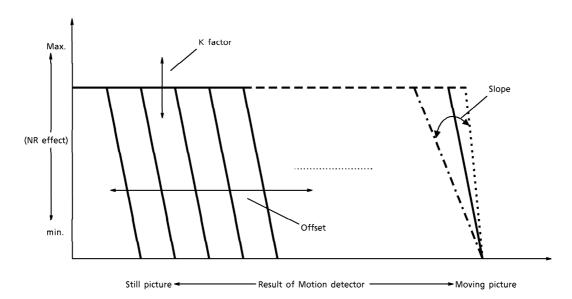

- 1. Motion detector function and the setting of BUS bit

- Motion detectors decide the picture (part) is near the moving or the still by detecting the differential level between the input signal and the delayed signal (a frame or a field).

- The NR circuit receives the result of motion detectors and makes the "K factor" reduce to "0" (NR OFF) at the parts of the moving picture.

- The middle range of "K factor" have 5 steps from the setting value to "0", and the offset value, which is the starting point to reduce the "K factor", and slope is programmable by I<sup>2</sup>C BUS control.

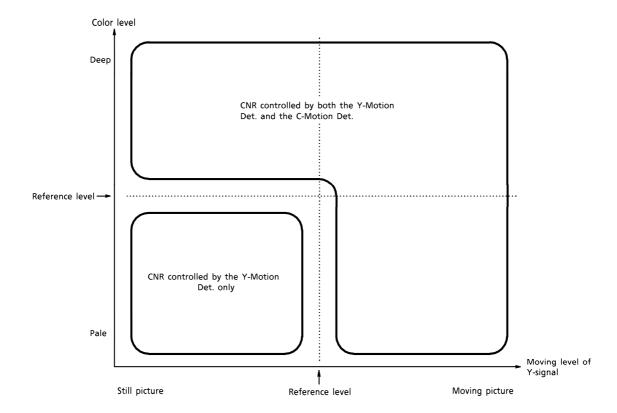

- YNR is controlled by the Y-motion detector only, and CNR is controlled by both the Y-motion detector and the C-motion detector. But in case of that the color level is small and the motion of Y-signal is small, CNR is controlled by only the Y-motion detector to decrease the cross color component.

#### BUS control data

- ① K factor of YNR (Sub address 40H; D7~D4)

- K factor can be changed by 14 steps from 0 to maximum. K factor of YNR increases in proportion to the setting data of these bits.

- ② Limiting level of YNR (Sub address 40H; D<sub>3</sub>~D<sub>0</sub>)

- The limiting level can be changed by 16 steps from 0 to maximum. Limiting level of YNR increases in proportion to the setting data of these bits.

- ③ K factor of CNR (Sub address 41H; D<sub>7</sub>~D<sub>4</sub>)

- K factor can be changed by 14 steps from 0 to maximum. K factor of CNR increases in proportion to the setting data of these bits.

- 4 Limiting level of CNR (Sub address 41H;  $D_3 \sim D_0$ )

- The limiting level can be changed by 16 steps from 0 to maximum. Limiting level of CNR increases in proportion to the setting data of these bits.

- ⑤ Offset of Y motion detector for YNR (Sub address 42H; D7~D4)

- This data can be changed by 16 steps from 0 to maximum. When the data is smaller, the motion detector make the K factor of YNR reduce more near the still picture, so, YNR effect is smaller. Conversely when the data is bigger, K factor doesn't decrease more near the moving picture, so, the afterimage comes into view on the moving picture.

© Slope of Y motion detector for YNR (Sub address 42H; D3, D2)

This data can be changed by 3 steps.

```

"00" = steep slope, "01" = middle, "10" = gentle slope

```

⑦ Offset of Y motion detector for CNR (Sub address 43H; D<sub>7</sub>~D<sub>4</sub>)

This data can be changed by 16 steps from 0 to maximum. When the data is smaller, the motion detector make the K factor of CNR reduce more near the still picture, so, CNR effect is smaller. Conversely when the data is bigger, K factor doesn't decrease more near the moving picture, so, the color blur increases on the moving picture.

Slope of Y motion detector for CNR (Sub address 43H; D<sub>3</sub>, D<sub>2</sub>)

This data can be changed by 3 steps.

```

"00" = steep slope, "01" = middle, "10" = gentle slope

```

Offset of C motion detector for CNR (Sub address 44H; D7~D4)

This data can be changed by 16 steps from 0 to maximum. When the data is smaller, the motion detector make the K factor of CNR reduce more near the still picture, so, CNR effect is smaller. Conversely when the data is bigger, K factor doesn't decrease more near the moving picture, so, the afterimage comes into view on the moving picture.

® Slope of C motion detector for CNR (Sub address 44H; D<sub>3</sub>, D<sub>2</sub>)

This data can be changed by 3 steps.

```

"00" = steep slope, "01" = middle, "10" = gentle slope

```

① Reference level of Y motion detector for cross color (Sub address 45H; D7~D4)

This data can be changed by 16 steps. When the data is bigger, the countermeasure effect of the cross color works more near the moving picture.

Reference level of Y motion detector for cross color (Sub address 45H; D3~D0)

This data can be changed by 16 steps. When the data is bigger, the countermeasure effect of the cross color works to the bigger color signal level.

③ ON/OFF of Y motion detector for YNR (Sub address 46H; D7)

Y motion detector for YNR is forced OFF at "1". (YNR is always ON.)

(4) ON/OFF of Y motion detector for CNR (Sub address 46H; D<sub>6</sub>)

Y motion detector for CNR is forced OFF at "1". (CNR is controlled by only C motion detector.)

(5) ON/OFF of C motion detector for CNR (Sub address 46H; D5)

C motion detector for CNR is forced OFF at "1". (CNR is controlled by only Y motion detector.)

(Sub address 46H; D<sub>4</sub>)

The moving picture parts widen for ±2 cycle of clock at "1".

① The moving picture parts to black (Sub address 46H; D3) ...... (Test mode)

The moving picture parts is replaced to black by the result of motion detector at "1".

Y motion detector result (Sub Address 4F<sub>H</sub>; D<sub>5</sub>) = "1"

C motion detector result (Sub Address  $4F_H$ ;  $D_5$ ) = "1"

This function is only for the evaluation. Don't use this function for the other aim,

18 YNR and CNR OFF (Sub address 46H; D2)

The result of all motion detectors is replaced to the moving picture at "1". (YNR and CNR is always OFF.)

2. The setting of BUS for the television standards

| SUB<br>ADD | DATA           | CONTROL<br>ITEM | "0"     | "1"     | NTSC | 443NTSC | PAL | SECAM | S-VHS<br>(NTSC) |

|------------|----------------|-----------------|---------|---------|------|---------|-----|-------|-----------------|

| 46         | D <sub>0</sub> | 443NTSC         | 358NTSC | 443NTSC | 0    | 1       | 0   | 1     | 0               |

| 47         | D <sub>0</sub> | De-mod OFF      | NORMAL  | OFF     | 0    | 0       | 0   | 1     | 0               |

| 4A         | D <sub>7</sub> | PAL             | NTSC    | PAL     | 0    | 0       | 1   | 0     | 0               |

| 4F         | D <sub>1</sub> | BPF OFF         | NORMAL  | THROUGH | 0    | 0       | 0   | 1     | 0               |

| 50         | D <sub>3</sub> | SW CLK in       | FS      | Fsc     | 1    | 1       | 0   | 1     | 1               |

| 50         | D <sub>2</sub> | VCXO OFF        | ACT     | STOP    | 1    | 1       | 0   | 1     | 1               |

| 50         | D <sub>1</sub> | PLL OFF         | ACT     | STOP    | 0    | 0       | 1   | 0     | 0               |

| 51         | D <sub>7</sub> | 50 / 60         | 60Hz    | 50Hz    | 0    | 0       | 1   | 1     | 0               |

| 51         | D <sub>6</sub> | 4.43 / 3.58     | 3.58MHz | 4.43MHz | 0    | 1       | 1   | 1     | 0               |

| 53         | D <sub>3</sub> | C-DAC ON        | OFF     | ON      | 0    | 0       | 0   | 0     | 1               |

| 54         | D <sub>1</sub> | Mod OFF         | NORMAL  | OFF     | 0    | 0       | 0   | 1     | 0               |

| 54         | D <sub>0</sub> | Y/C mix OFF     | Y-ONLY  | YC-MIX  | 1    | 1       | 1   | 1     | 0               |

| 55         | D <sub>2</sub> | PAL / NTSC      | PAL     | NTSC    | _    | 1       | 0   | _     | _               |

① 443NTSC (Sub address 46H; D<sub>0</sub>)

VCO frequency of the 4fsc PLL is changed by this bit.

0 : fsc = 3.58MHz, 1 : fsc = 4.43MHz

② De-modulation OFF (Sub address 47H; D<sub>0</sub>)

The chroma demodulator is ON/OFF by this bit. Select OFF at only SECAM mode.

0: ON, 1: OFF

3 PAL (Sub address 4AH; D7)

The chroma modulating and de-modulating system is selected by this bit.

0: NTSC, 1: PAL

BPF OFF (Sub address 4FH; D<sub>1</sub>)

The chroma BPF is ON/OFF by this bit. Select OFF at only SECAM mode.

0: ON, 1: OFF

⑤ Switch of the clock input (Sub address 50H; D<sub>3</sub>)

The clock input terminal is selected by this bit.

0 : pin 24 (for VCXO), 1 : OFF : pin 34 (for 4fsc PLL)

6 VCXO OFF (Sub address 50H; D2)

The VCXO driver of the burst PLL is ON/OFF by this bit.

0: ON, 1: OFF

⑦ PLL OFF (Sub address 50H; D<sub>1</sub>)

The 4fsc PLL is ON/OFF by this bit.

0: ON, 1: OFF

8 50Hz/60Hz (Sub address 51H; D<sub>7</sub>)

This bit is for selection of the field frequency.

0:60Hz, 1:50Hz

9 4.43MHz/3.58MHz (Sub address 51H; D<sub>6</sub>)

This bit is for selection of the system clock frequency by fsc.

0 : fsc = 3.58MHz, 1 : fsc = 4.43MHz

(1) C-DAC ON (Sub address 53H; D<sub>3</sub>)

Chroma output (at Pin 51) is ON/OFF by this bit.

0: OFF, 1: ON

① Modulation OFF (Sub address 54H; D<sub>1</sub>)

The chroma modulator is ON/OFF by this bit. Select OFF at only SECAM mode.

0: ON, 1: OFF

12 Y/C mix OFF (Sub address 54H; D<sub>0</sub>)

This bit is for selection of the output signal at Pin 55, composite video (Y/C) or Luma only (Y).

0 : Y/C mix, 1 : Y only

(3) PAL/NTSC (Sub address 55H; D<sub>2</sub>)

This bit is for selection of the detection system of burst PLL, NTSC or PAL. When you will only use the burst PLL at NTSC signal, set this bit "1".

0 : PAL, 1 : NTSC

(Sub address 4DH; D6)

This bit is for the external SW control. Pin 79 (SW<sub>CONT</sub>) is the decoding terminal of this bit.

0 : Low, 1 : High

(Note) When the bit of "Y-DAC ON" (Sub add 53H; d4) is "1", the Y-DAC output terminal (Pin 55) is fixed "Hi" (near the V<sub>DD</sub> level).

- 3. The adjustment of the internal logic timing by BUS data

- ① Delay of chroma mute for BLNK pulse (Sub address 48H; D7~D3)

The color component of the output signal at Pin 51 (Cout) or/and Pin 55 (Yout) is OFF during Pin 74 (BLNK) is low. This color mute timing can be shifted by the data of these bits.

② Timing adjustment of the delayed signal from the memory IC (Sub address 49H;  $D_5 \sim D_0$ )

These bits are for the timing adjustment between the input signal and the delayed signal from the external memory IC. Normally, these bits are set as follows for each NR mode.

③ Timing adjustment of the video signal and the C-sync (Sub address 49H; D5~D0)

To save the bits data for the memory IC, the NR effect is OFF except the picture parts of the video signal. This timing is made from the C-sync (Pin 73), and the horizontal position can be sifted by these bus bits data.

So, set the data for these bits to meet the timing between the action period of WCK (Pin 1) and the picture parts of internal video signal, that is  $1\mu$ s later than the signal of Yin (Pin 40).

④ V mask position for burst PLL (Sub address 51H; D<sub>4</sub>~D<sub>2</sub>)

The detector of the burst PLL stops during the Vertical Blanking period. This period can be selected by bus data. But, normally select the longest period  $(D_4 = 0, D_3 = 1)$ .

```

Front of V mask period : "D_4 = 0"; early, "D_4 = 1"; late End of V mask period : "(D_3, D_2) = (0, 0)"; early "(D_3, D_2) = (0, 1)"; center "(D_3, D_2) = (1, x)"; late

```

⑤ Burst gate position for VCXO (Sub address 52H; D7~D1)

The gate pulse of burst PLL is made from C-sync, so you have to adjust the timing of this pulse to the internal burst position, that is 500ns later than the signal of Cin (Pin 45). This gate pulse can be observed at Pin 13 (PWM) under the test mode as follows.

Test mode for the observation of the burst gate pulse

```

Sub Address 4BH; D_1 = 0

Sub Address 4EH; D_6 = 1

Sub Address 4EH; D_3 = 1

Sub Address 55H; D_1 = 1

```

© Delay of Y signal (Sub address 54H;  $D_7$ ,  $D_6$ ) (Note) Fix 0 at "Y/C Delay" = 1 (C delay mode) Delay of C signal (Sub address 54H;  $D_5$ ,  $D_4$ ) (Note) Fix 0 at "Y/C Delay" = 0 (Y delay mode)

These bits are for the adjustment of Y/C timing at output. First, select the Y delay or C delay by the bit of "Y, C Delay" (Sub Address 48H;  $D_1$ ).

#### 4. The others

1 Color mute control

The terminal who make the chroma output OFF is as follows.

- BLNK (Pin 58); Mute the color where is the characters at OSD super impose mode.

- PVPH (Pin 59); Mute the color where is vertical blanking period, because the color is not here.

- KILL (Pin 74); Make the color OFF when the input signal is the B/W signal.

The functions of BLNK (Pin 58) and PVPH (Pin 59) can be made OFF by bus control as follows.

- C-Mute OFF (Sub Address 48H; D<sub>2</sub>) = 1→BLNK (Pin 58) is ignored.

- PV/PH OFF (Sub Address 53H; D<sub>2</sub>) = 1→PVPH (Pin 59) is ignored.

- 2 Memory IC (Sub address 4CH; D<sub>1</sub>)

```

0: \mu PD42280 (by NEC), 1: MSM518221 (by OKI)

```

- 3 Field / frame (Sub address 4CH; D<sub>0</sub>)

- 0 : Frame NR (NTSC only), 1 : Field NR

- 4 Standard / non standard (Sub address 50H; D5, D4)

The video signal from the PC and the TV game etc. is different from the television standard. This IC detects the input signal is the standard or not, and usually makes the NR effect OFF automatically. But the manual select is available by bus control.

```

D<sub>5</sub>; 0: Automatic, 1: BUS control (D<sub>4</sub>)

```

D4; 0: Standard, 1: Non-standard

(Note) On the trick mode of VCR, the input signal may be regarded as the non-standard because the number of lines in a field is different from on normal play back. If you need the (line) NR effect on the trick mode, you select the standard fix mode by bus.

⑤ Line NR (Sub address 51H; D<sub>5</sub>)

The line NR mode is usually used on the trick mode of VCR, because the field correlation is small in this case. This IC doesn't have the internal line memory, so the external memory is used on the line NR mode, too.

```

0 : Frame / Field NR, 1 : Line NR

```

6 Drop-out compensation

This IC have the function that replace the input signal by the delayed signal during low level at Pin 72 (DOC). But this function can not be used at the field/frame NR mode, because the delayed signal is noting at the sync parts. So you can use this function at the line NR mode only.

- Y-DOC (Sub Address 4FH; D7) = 1 .... Y signal component is replace by DOC pulse at Pin 72.

- C-DOC (Sub Address 4FH; D<sub>6</sub>) = 1 .... C signal component is replace by DOC pulse at Pin 72.

7 Chroma noise cancel

```

C-N.C. ON (Sub Address 53H; D<sub>7</sub>)

0: OFF, 1: ON

```

• Limiter level of C-N.C. (Sub Address 53H; D<sub>6</sub>, D<sub>5</sub>)

```

00 : 2, 10 : 4, 01 : 8, 11 : 16

```

® Y detail enhanced level (Sub address 56H; D7, D6)

```

00 : 0 (OFF), 01 : 0.25, 10 : 0.5, 11 : 1.0

```

9 C detail enhancer (Sub address 56H; D<sub>5</sub>, D<sub>3</sub>, D<sub>2</sub>, D<sub>1</sub>)

This function is the enhancement of chroma signal level near the edge of Y signal.

```

D<sub>5</sub> ; Edge detecting level ...... 0 : Low, 1 : High

```

ullet D<sub>3</sub>, D<sub>2</sub>; Enhancement level of the chroma detail

```

00 : 0.5, 01 : 1.0, 10 : 1.5, 11 : 2.0

```

D<sub>1</sub> ; C detail enhancer OFF

0 : ON, 1 : OFF

#### **DESIGNING FILTER CIRCUIT**

a) Input low-pass filter

This low-pass filter is used to limit the frequency bandwidth of the input signal to below a half of the clock frequency. If the input signal contains a high frequency component and this input filter is not, it may interfere with clock frequency inside the IC, generating a frequency component that can be removed by an output filter. (Reflected distortion)

b) Output low-pass filter

This filter is used to remove clock frequency components (including harmonics) in the IC's output signal, as well as remove the reflected distortion at input.

#### **CAUTION**

This device is electrostatic sensitive device, so care must be taken in handling and storage to prevent deterioration or damage by means of shorting electrically all pins with use of aluminum foil or conductive mat.

Even in assembled on board, it is necessary to protect against surge or inductive noise from input, output and power supply line.

### **APPLICATION CIRCUIT**

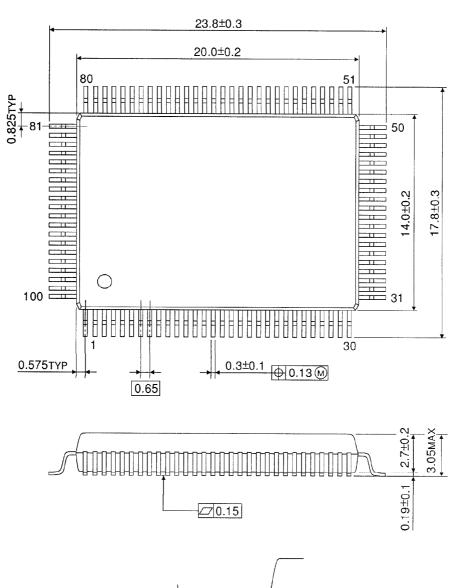

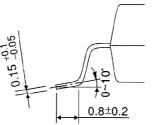

# OUTLINE DRAWING OFP100-P-1420-0.65A

Unit: mm

Weight: 1.1g (Typ.)