# RISC/CISC ASIC PRODUCT GUIDE

# The Dawn of the "Computer -on-Silicon" Age

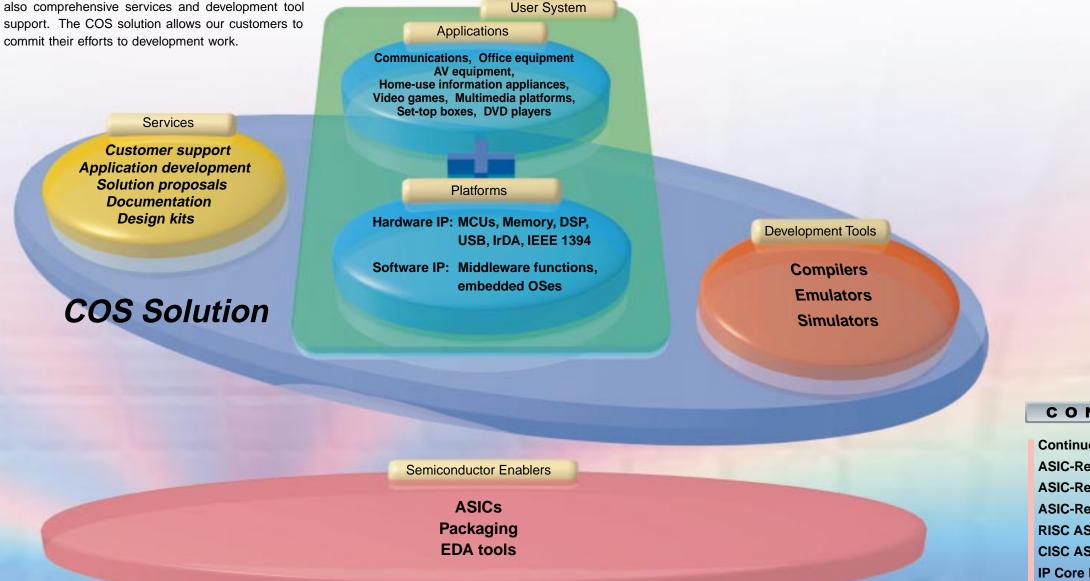

Specialized microcontrollers are increasingly used to control devices of all kinds such as automobiles, home and office appliances, handheld equipment, etc. With this trend getting into high gear, application software is customized more often than ever before to fit specific needs of target systems.

Toshiba offers a computer-on-silicon (COS) solution to help its customers improve the time-to-market for their new processor-based systems. The combination of Toshiba's world-class computer and silicon technologies provides its customers with a total solution - a partnership with Toshiba brings you not only the

performance of our hardware and software IP, but also comprehensive services and development tool support. The COS solution allows our customers to

To meet diverse customer needs, Toshiba provides a broad range of Reduced Instruction Set Computer (RISC) and Complex Instruction Set Computer (CISC) processors. Our RISC and CISC processors are available either as ASIC-ready cores or as standard products. Toshiba's ASIC core portfolio includes a gallery of 32- and 64-bit TX families of RISC cores as well as Toshiba's proprietary 16-bit CISC processor families such as TLCS-900/H and TLCS900/L1. Also included among ASIC-ready cores are a variety of hardware and software IP cores targeted for consumer, computer, and communications applications. All these cores give you great flexibility in the design of advanced multimedia products.

Gateway to the COS Age – RISC/CISC ASICs from Toshiba.

ASIC-Re ASIC-Re ASIC-Re **RISC AS** CISC AS **IP** Core Hardwa Develop **Test Me** Software Software Toshiba Packagi Toshiba

# CONTENTS

| ous Evolution of Toshiba's MPU Cores     | 4  |

|------------------------------------------|----|

| ady RISC Cores TX Sytem RISC TX39 Family | 5  |

| ady RISC Cores TX Sytem RISC TX19 Family | 6  |

| ady CISC Cores 900 Family                | 7  |

| IC                                       | 8  |

| IC                                       | 9  |

| Lines                                    | 10 |

| e/Software Co-verification Environment   | 11 |

| ment Flow                                | 12 |

| hodologies                               | 13 |

| Development Tools for RISC ASICs         | 14 |

| e Development Tools for CSIC ASICs       | 16 |

| ASIC Road Map                            | 17 |

| ng                                       | 18 |

| Documents                                | 19 |

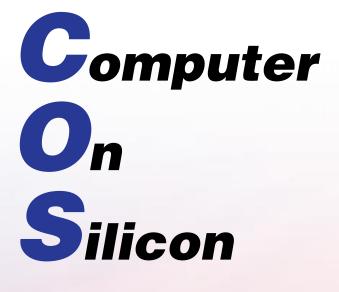

# Continuous Evolution of Toshiba's MPU Cores

The following road map shows a whole suite of Toshiba's ASIC-ready MPU cores. Toshiba offers a broad and varied range of RISC and CISC options to suit your unique needs, including applications, power dissipation, and performance requirements. Encompassing Toshiba's MPU core offerings are the **TLCS-900** CISC family and the **TX19**, **TX39**, **TX49**, and the next-generation RISC families.

# **ASIC-Ready RISC Cores**

The **TX39** family is a high-performance 32-bit microprocessor for embedded applications developed by Toshiba based on the MIPS R3000A architecture. The **TX39** family can be used as a foundation for embedded array or cell-based ASIC designs.

# **Microprocessor Core**

- R3000A architecture

- High-performance: TX39/H: 74 MIPS (at 70 MHz operation) TX39/H2 (in development): 105 MIPS (at 100 MHz operation)

- based on Dhrystone 2.1 VAX-11/780 benchmarking

- Built-in cache memory Separate instruction and data caches

- Non-blocking load function Avoids performance degradation by executing the next instruction while the data cache is being refilled.

- DSP function One-cycle Multiply-Accumulate (MAC) supporting 32-bit x 32-bit multiply-add operations

# Low Power

- Multiple power saving modes of operation, including Reduced-Frequency (RF), Doze, Halt modes, etc.

- The PLL oscillation can be halted externally (standby mode)

# Functions for Embedded Applications

Improved code density and performance Branch-likely instructions Hardware interlock

\* R3000A is a trademark of MIPS Technologies, Inc.

# TX39 Family ASSP Products

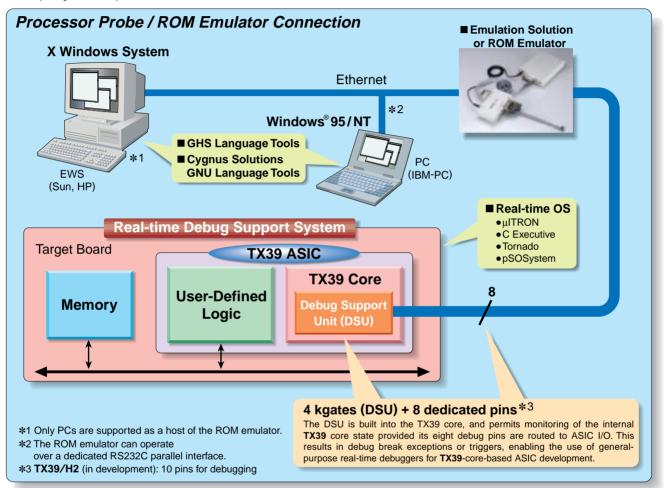

# Development Tool Support

- C/C++ compiler, assemblers/linkers

- External real-time debug system support Provides for real-time debug with caches enabled.

- Support of various real-time OSes

- Standard board applicable to evaluation and user application

# ASIC Support

- Proven EDA environment with RTL Verilog models

- Peripherals add-ons provided as megacells

- MPU core availability:

- GR39WAD: TX39/H core (TC220)

- PTX3904A: Functionally-equivalent to TMPR3904A (TC220)

- PTX39WAD: TX39/H2 core (TC240, in development)

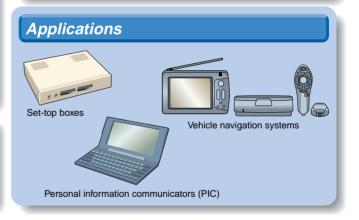

| Product Number                                                 | Applications                                                                 | Clock<br>Frequency | Voltage                   | Package         |

|----------------------------------------------------------------|------------------------------------------------------------------------------|--------------------|---------------------------|-----------------|

| TMPR3901AF-70                                                  | Standard MPU                                                                 | 70 MHz             | 3.3 V                     | QFP160          |

| TMPR3903AF                                                     | Vehicle navigation systems                                                   |                    | 3.3 V                     | QFP208          |

| TMPR3904AF-66*                                                 | IPR3904AF-66* Peripherals added to the standard MPU                          |                    | 3.3 V                     | QFP208          |

| TMPR3907F                                                      | TMPR3907F         Peripherals and a PCI controller added to the standard MPU |                    | 3.3 V                     | QFP208          |

| TMPR3912AU/XB Personal information communicators (PIC)         |                                                                              | 92 MHz             | 3.3 V                     | LQFP208/FBGA217 |

| TMPR3922AU/XB         Personal information communicators (PIC) |                                                                              | 129/148* MHz       | I/O: 3.3 V<br>Core: 2.7 V | LQFP208/FBGA217 |

\*: In Development

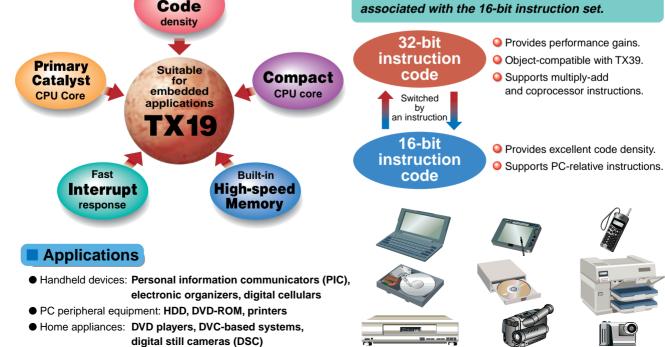

# **ASIC-Ready RISC Cores**

The **TX19** family is an extremely compact, high-performance 32-bit microprocessor developed by Toshiba based on the MIPS R3000A architecture. The **TX19** family added support for MIPS16<sup>™</sup> Application-Specific Extension (ASE), a highly efficient code compression mechanism, to the **TX39** family. Toshiba has been introducing application-specific standard products (ASSPs) in stages that integrate the **TX19** processor core and various peripheral building blocks on the same chip. In addition, the **TX19** processor core can be used in ASIC designs for high-performance embedded systems.

### **Microprocessor Core**

- R3000A architecture

- High-performance: 42 MIPS (at 40 MHz operation) based on Dhrystone 2.1 VAX-11/780 benchmarking

- Built-in cache memory and high-speed data RAM

- Non-blocking load function Avoids performance degradation by executing the next instruction while the data cache is being refilled.

- DSP function Fast Multiply-Accumulate (MAC) supporting 32-bit x 32-bit multiply-add operations

# Functions for Embedded Applications

- Compatible with MIPS16<sup>™</sup> ASE

- Real-time performance

Minimizes an interrupt response time

(e.g. through one-clock-access RAM)

Instruction/data cache locking function

\* R3000A and MIPS16 are trademarks of MIPS Technologies, Inc.

# ASIC Support

- Implemented with the TC240 technology process

- Requires a very small die area

- Upgrading development tools

# Low Power

- Optimized design implemented using a low-power cell library

- Power saving modes

Clock gearing function (Reduced-Frequency mode)

Various standby modes

Improved

Intermixing 16-and 32-bit instructions provides all the performance benefits of an embedded 32-bit microprocessor while offering reduced code size associated with the 16-bit instruction set.

# **ASIC-Ready CISC Cores**

160 ns (at 25 MHz)

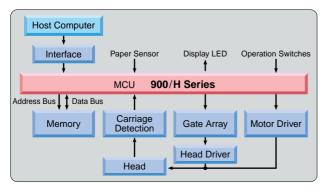

# 900 Family

The **900** family is a high-performance 16-bit microcontroller (MCU) with high C code efficiency. The **900** family offers a wide range of features to fit a variety of requirements for different products ranging from office equipment such as printers and facsimiles to high-end consumer electronic products like digital still cameras (DSC) and DVC-based systems to portable equipment that mandates low power dissipation. To significantly reduce the time and expense of controller design, a wide range of powerful and consistent development tools are available from Toshiba and several third-party development tool vendors.

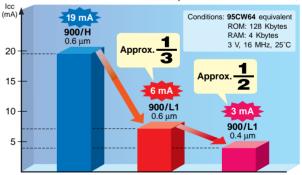

The 900 family contains two product series: high-performance 900/H and low-power, low-noise 900 /L1.

# Suitable for high-end office equipment

### High-Performance CISC Core

- Minimum instruction execution time:

- 32-bit ALU

- 4-bit barrel shifter

### **Compact Core**

Reduced die size due to a very lean set of instructions selected for embedded applications

# Suitable for applications with low-power and low-noise requirements

### Low Power (900/L1)

### **Tentative Specifications**

- Operating voltage range: 1.8 to 5.5 V

- Minimum instruction execution time:

- 250 ns (at 16 MHz, Vcc ≥ 2.7 V)

- 400 ns (at 10 MHz, Vcc ≥ 1.8 V)

- Low power dissipation: 3.0 mA typical

(16 MHz, 3.0V, NORMAL mode)

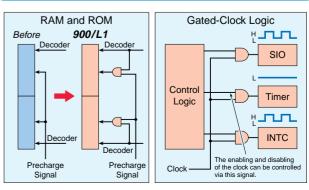

- Clock gearing function: (fc, fc/2, fc/4, fc8, fc/16)

- Dual clock function

- Three standby modes

- Low-power design techniques (e.g. gated clocks)

### Reduction of Power Dissipation

(Relative to Toshiba's previous microcontrollers)

Examples of Low-Power Design Techniques

# Applications Printers

CD-ROM drives

Electronic musical instruments

Digital-video-cassette-based systems

# Serial Printer Block Diagram

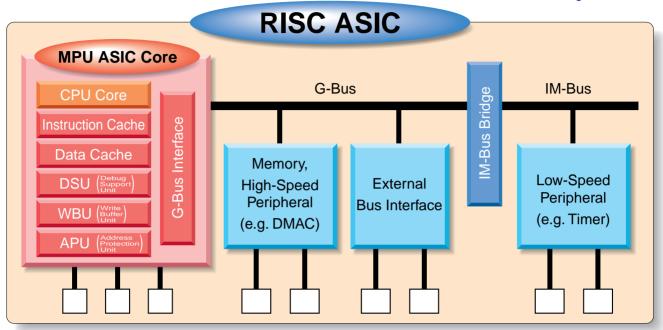

# **RISC ASIC**

# **RISC ASIC Configurations**

- The RISC ASIC allows designers to integrate a TX System RISC megacell (or system CPU) with peripheral IP cores and/or user-defined logic on one chip.

- The integral G-bus directly connects system components together, such as a DMA controller acting as a bus master, a memory controller, a interrupt controller, etc. The specification of G-bus is provided to users of a TX System RISC megacell.

- Low-speed peripherals like a timer and a UART block are connected through IM-Bus via a bridging logic.

- Currently, the TX System RISC megacells are available in two versions: GR39WAD which integrates a TX39 CPU core with a Address Protection Unit (APU), Write Buffer Unit (WBU), and a Debug Support Unit (DSU) and PTX3904A which is functionally equivalent to TX3904A. The high-performance megacell, PTX39WAD, is in development using the TC240 technology.

- The TX39-based ASIC chip requires a package with at least 160 pins.

## Application Example

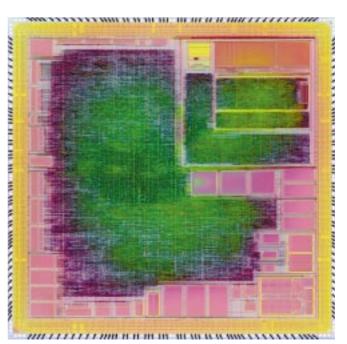

Digital BS Receiver *MPEG-2 Decoder IC:* TC81220F

Toshiba's **TC81220F** integrates a **TX39** core, a MPEG-2 video decoder, a MPEG-1/2 audio decoder, a programmable transport processor, standard peripherals, a memory controller, etc.

Photo of the TC81220F

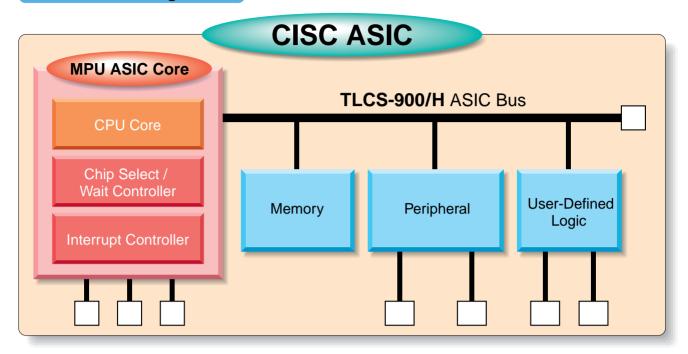

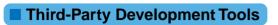

# **CISC ASIC**

# **CISC ASIC Configurations**

- The CISC ASIC offers a megacell, SMC95C001, which integrates a 900/H core with such built-in functions as a chip-select/wait controller and an interrupt controller. The SMC95C001 is functionally equivalent to Toshiba's standard product TMP95C001.

- The TLCS-900/H Bus, which is the standard bus specification for all 900/H products, connects the 900/H core with memories (RAMs, ROMs, etc.), peripheral I/O functions, and user-defined logic.

- The TLCS-900/H Bus is routed off-chip, so the same emulator can be used to test both the standard TMP95C001 product and 900/H core-based ASICs.

## Application Example

Toshiba used its CISC ASIC solution to integrate a **900/H** core with ROM, RAM, standard peripherals, and A/D converters to build a communications IC. This IC is fabricated using the **TC222C** technology. While the I/O interfaces with 3 V, the core operates at 2 V, reducing power dissipation.

Communications IC Implemented as a CISC-Processor-Core-Based ASIC

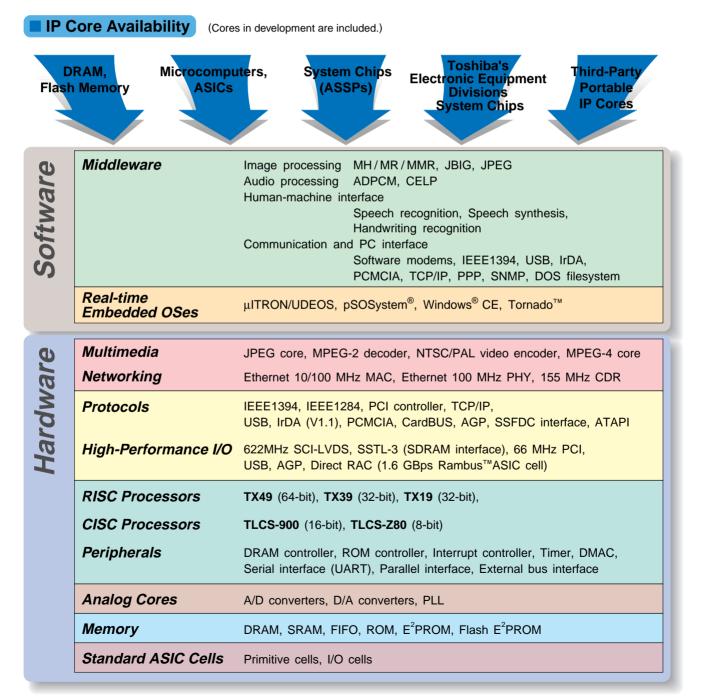

# **IP Core Lines**

A broad range of high-density, high-performance IP cores is an essential element for the success of advanced ASIC designs for all consumer, communications, and data processing applications.

- For true systems-on-a-chip, the supporting ASIC silicon technologies cover a full spectrum of application requirements with a wide range of power, density, and speed solutions.

- IP core offerings meet the requirements of system chips. Hardware IP libraries include cores that implement RISC and CISC processors as well as multimedia, network, and protocol functions. Software (or synthesizable) IP libraries include cores that implement middleware functions such as JPEG, speech processing, and fax modem as well as real-time embedded operating systems and software drivers.

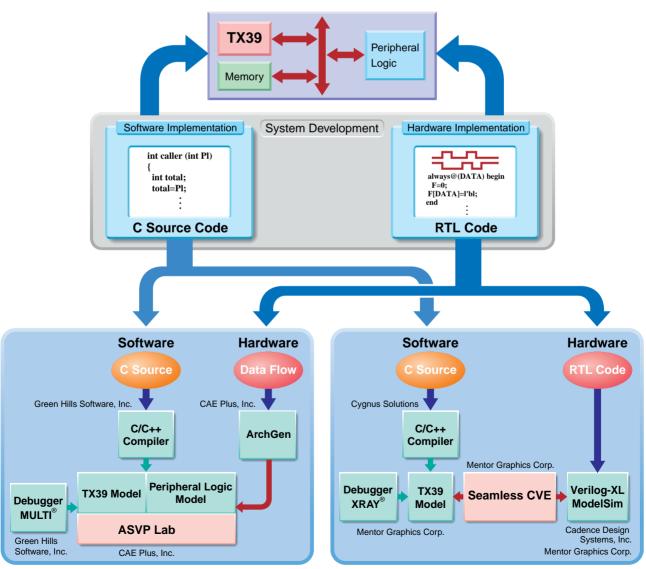

# Hardware/Software Co-verification Environment

### **Seamless Co-verification Flow**

The traditional approach to the development of system chips with an embedded CPU core is usually a series of sequential and independent steps. This means system development is fragmented into task-oriented specialties like hardware and software designs. Detailed analysis of interactions between hardware and software is only possible after hardware prototyping. While software errors are relatively easy to fix, errors in hardware can cause significant delays if design rework is needed. Today's increasingly complex designs and shortened design cycles make the traditional approach unsuitable.

The hardware/software co-verification environment addresses the problems of the traditional design cycle by linking software and hardware verification together. Toshiba supports ASVP Lab from CAE Plus and Seamless CVE from Mentor Graphics by offering the C model of the TX39 core. ASVP Lab provides all-C model hardware and software debugging by assembling ArchGen C models of user-defined logic and the TX39 C model into a high-speed virtual prototype. Seamless CVE delivers high-performance system verification environment by combining embedded software development tools with behavioral and logic simulation.

Co-verification Using the CAE Plus Tools

Co-verification Using the Mentor Graphics Tools

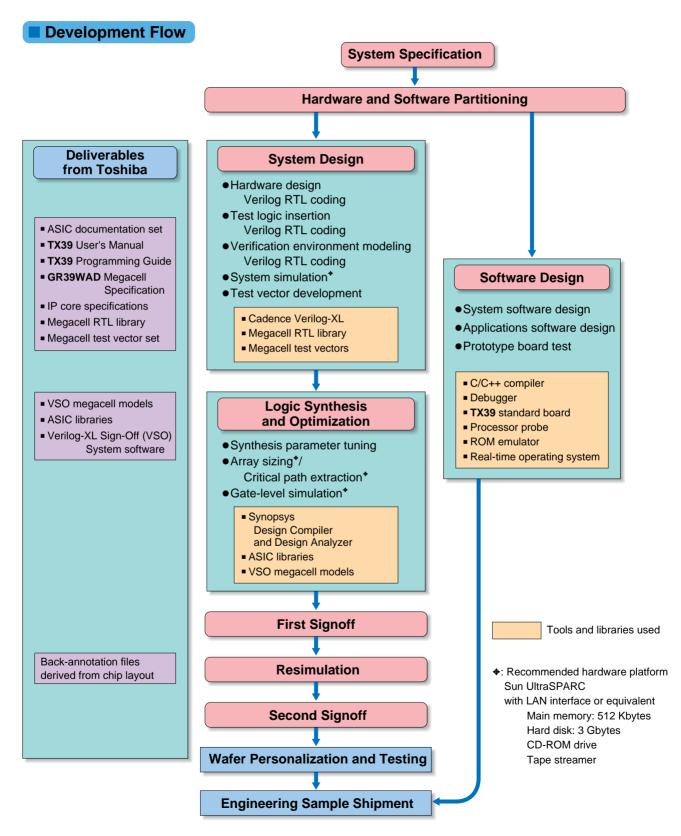

# **Development Flow**

The following flowchart shows a typical process for developing an ASIC with an integrated **TX39** family RISC processor core, **GR39WAD**. For support of EDA tools not shown in the flowchart, please contact your local Toshiba customer support group.

# **Test Methodologies**

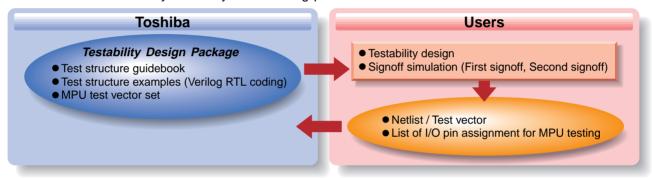

There are two issues for testing of a chip with embedded blocks such as an MPU core. One is testing of the block itself. In the case of a large, complex block like an MPU core, it is necessary to test the block separately from the rest of the chip. The figure below shows a direct access approach where the MPU core is isolated from the user-defined logic by providing an access collar around it. All inputs and outputs of the MPU core are made directly accessible and observable for testing by connecting multiplexers to package pin test points. A test vector set for the stand-alone test of an embedded core is provided by Toshiba.

### Testability Design Flow

- Test structures need to be designed as part of the user-defined logic.

- Test structure examples coded at RTL are provided by Toshiba.

- An automated test synthesis system is being planned.

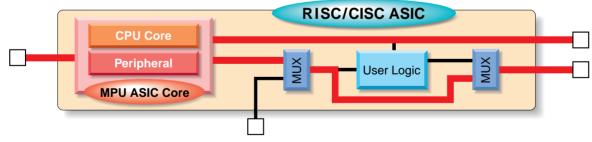

### Isolating the MPU Core

### **Stand-alone Testing of the MPU**

The MPU core is isolated from the rest of the design during testing. Test vectors for the MPU core are provided by Toshiba and multiplexed through a set of I/O pins. The flow of data while the MPU core is tested is shown by the bold paths below.

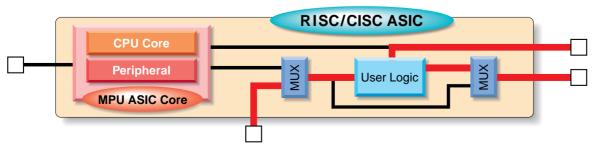

### Testing of the User-Defined Logic

The user-defined logic is isolated from the MPU core for testing purposes. Test vectors for the user-defined logic are created by the designer, and internal signals are routed as necessary to ASIC I/O pins to improve testability. The flow of data while the user-defined logic is tested is shown by bold paths below.

# Software Development Tools for RISC ASICs

## Software Development Environment

Exactly the same suite of tools are supported for the software development of RISC

ASICs as for standard **TX family** products. To significantly reduce the time and expense of processorbased design, a wide range of powerful and consistent development tools, including compilers, debuggers, real-time operating systems, and processor probes, are available from Toshiba and several third-party development tool vendors.

# Third-Party Development Tools for TX39

# TX39

| Vendor                     | ΤοοΙ                      | Product Name                                  |

|----------------------------|---------------------------|-----------------------------------------------|

| Green Hills Software, Inc. | Language Tool<br>Debugger | C/C++ CROSS MIPS COMPILER<br>MULTI®           |

| Integrated Systems, Inc.   | Real-time OS              | pSOSystem <sup>®</sup>                        |

| Wind River Systems, Inc.   | Real-time OS              | Tornado™                                      |

| DENSAN Systems, Inc.       | Evaluation Board          | DVE-R3904/20<br>DVE-R3900/20A<br>DVE-R3900/20 |

| Cygnus Solutions           | Language Tool<br>Debugger | GNU Pro <sup>™</sup> Tool kit<br>GDB          |

| Hewlett-Packard Company    | Processor Probe           | HPE3492B                                      |

### TX19 (Under Development)

| Vendor                     | ΤοοΙ                      | Product Name                                    |

|----------------------------|---------------------------|-------------------------------------------------|

| Green Hills Software, Inc. | Language Tool<br>Debugger | C/C++ CROSS MIPS COMPILER<br>MULTI <sup>®</sup> |

| Integrated Systems, Inc.   | Real-time OS              | pSOSystem <sup>®</sup>                          |

| Cygnus Solutions           | Language Tool<br>Debugger | GNU Pro <sup>™</sup> Tool kit<br>GDB            |

| Hewlett-Packard Company    | Processor Probe           | HP Distributed Emulation System                 |

| Yokogawa Digital Computer  | In-circuit Emulator       | IDB Analyzer                                    |

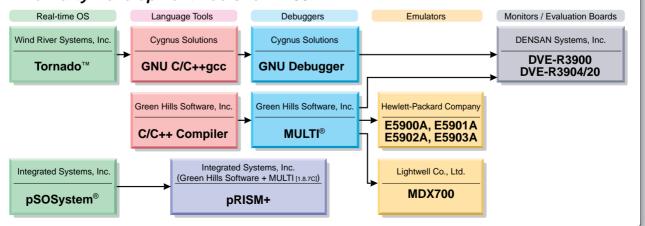

# Software Development Tools for CSIC ASICs

# Software Development Environment

# Toshiba's Software Development System

# **TLCS-900/H**

| Supported MCU<br>Product | Embedded<br>Software Controller | Language Tool         | Test Tool |                    |          |

|--------------------------|---------------------------------|-----------------------|-----------|--------------------|----------|

| TMP95C001F               | Real-time OS                    | Assembler C Compiler  | Debugger  | Real-time Emulator |          |

|                          | Redi-time 00                    | Assembler, C Compiler | Debuggei  | model 25           | model 15 |

Note: For details, please consult the *Microcomputer DEVEOPMENT SYSTEM GUIDE* brochure.

# Third-Party Software Development Tools

### **TLCS-900/H**

| Vendor                    | ΤοοΙ                                                               | Product Name                   |

|---------------------------|--------------------------------------------------------------------|--------------------------------|

| IAR Systems AB            | Assembler<br>C Compiler<br>Simulator Debugger<br>Emulator Debugger | Development kit<br>C-SPY/S 900 |

| GAIO TECHNOLOGY Co., Ltd. | C Compiler<br>ICE Debugger                                         | XASS-V Series                  |

| Yokogawa Digital Computer | In-circuit Emulator                                                | ADViCE                         |

\* Company names and product names may be trademarks or registered trademarks by their respective companies.

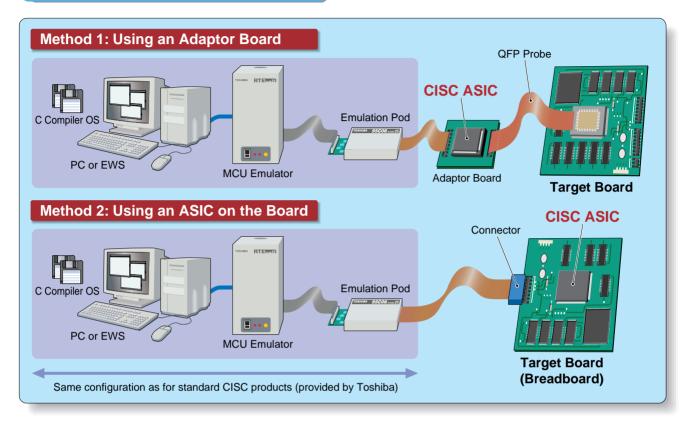

# **Toshiba ASIC Road Map**

# Toshiba ASIC Trend

In keeping with our overriding commitment to meeting customers' present and future needs, Toshiba continuously pursues new goals in the exploration of both silicon technologies and design techniques. For true system-scale integrations, ASIC silicon technologies must cover a full spectrum of application requirements with a broad range of power, density and speed solutions, complete with support of core functions and high-performance I/O.

# **Embedded Array Product Lines**

| Product Family      |                                      | I/O: 3<br>Core: |         | I/O: Mixed 3.3/5 V<br>Core: 3.3 V |         |  |

|---------------------|--------------------------------------|-----------------|---------|-----------------------------------|---------|--|

|                     |                                      | TC220E          | TC200E  | TC223E                            | TC203E  |  |

|                     | Process                              | 0.3 μm          | 0.4 μm  | 0.3 μm                            | 0.4 μm  |  |

| Delay               | Fanout = 1                           | 0.07 ns         | 0.11 ns | 0.07 ns                           | 0.11 ns |  |

| Time*               | Fanout = 2<br>+ typical interconnect | 0.15 ns         | 0.19 ns | 0.15 ns                           | 0.19 ns |  |

| Usable Random Gates |                                      | 1.9 M           | 704 k   | 193 k                             | 694 k   |  |

| I/O                 | Wirebond                             | 512             | 512     | 504                               | 504     |  |

| Pads                | ТАВ                                  | 768             | 776     | 768                               | 768     |  |

| Power Dissipation** |                                      | 0.65 μW         | 1.14 μW | 0.65 μW                           | 1.14 μW |  |

| Masterslices        |                                      | 38              | 39      | 40                                | 38      |  |

# **Cell-Based IC Product Lines**

| Product Family                             |                     | I/O: 3<br>Core: |         | I/O: Mixed 3.3/5 V<br>Core: 3.3 V |         |  |  |

|--------------------------------------------|---------------------|-----------------|---------|-----------------------------------|---------|--|--|

|                                            | ,                   | TC220C          | TC200C  | TC223C                            | TC203C  |  |  |

|                                            | Process             | 0.3 μm          | 0.4 μm  | 0.3 μm                            | 0.4 μm  |  |  |

| Delay                                      | Fanout = 1          | 0.06 ns         | 0.10 ns | 0.06 ns                           | 0.10 ns |  |  |

| Time* Fanout = 2<br>+ typical interconnect |                     | 0.14 ns         | 0.17 ns | 0.14 ns                           | 0.17 ns |  |  |

| Usable Random Gates                        |                     | 2.1 M           | 729 k   | 2.1 M                             | 718 k   |  |  |

| I/O Wirebond                               |                     | 512             | 512     | 504                               | 504     |  |  |

| Pads                                       | ТАВ                 | 768             | 768     | 768                               | 768     |  |  |

| Power<br>Dissi-                            | ND2 (Fanout = 1)    | 0.41 μW         | 0.91 μW | 0.41 μW                           | 0.91 μW |  |  |

| pation*                                    | * ND2R (Fanout = 1) | 0.24 μW         | 0.48 μW | 0.24 μW                           | 0.48 μW |  |  |

| Masterslices                               |                     | 40              | 39      | 40                                | 38      |  |  |

★: High-drive 2-input NAND gate ★★:  $\mu$ W/gate/MHz (3.3 or 5 V), 2-input NAND, fanout = 1

★: High-drive 2-input NAND gate ★★: μW/gate/MHz (2, 3.3, or 5 V), ND2: 2-input NAND, NR2R: Low-power 2-input NAND

Note: The above tables give only the product families supporting embedded RISC and CISC cores.

# **TC240 Family Product Summary**

| Process Technology                           |                                   | 0.25 μm                       |        |        |                                |           |        |        |

|----------------------------------------------|-----------------------------------|-------------------------------|--------|--------|--------------------------------|-----------|--------|--------|

| F                                            | Tocess Technology                 |                               |        | HC2MOS | Si-gate five lay               | /er metal |        |        |

| Series                                       |                                   | Embedded Arrays Cell-Based IC |        |        |                                |           |        |        |

| Maximum Us                                   | sable Gates* (with four metals)   | 8.8 Mgates 10.2 Mgates        |        |        |                                |           |        |        |

| Cell Name**                                  |                                   | GND2X1                        | GND2X2 | GND2X4 | CND2XL                         | CND2X1    | CND2X2 | CND2X4 |

| Delay Time (ps)                              | Fanout = 1                        | 77                            | 68     | 61     | 87                             | 70        | 55     | 54     |

| Delay Time (p3)                              | Fanout = 1 + typical interconnect | 141                           | 101    | 79     | 218                            | 118       | 83     | 68     |

| Power Dissipation ( $\mu$ W/MHz, Fanout = 1) |                                   | 0.156                         | 0.270  | 0.487  | 0.107                          | 0.170     | 0.296  | 0.563  |

|                                              | Operating Voltage                 |                               |        | I      | Core: 2.5 V<br>/O: 2.5 V/3.3 V |           |        |        |

★: Depends on design configurations.

★★: □ND2X1: 2-input NAND gate. X1 drive

□ND2X4: 2-input NAND gate. X4 drive

# Packaging

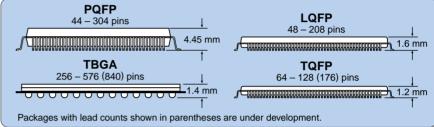

### High-Density Packages

BGAs provide the highest I/O-to-body-size ratio, with solder balls formed on the bottom in an area array format and a ball pitch of 1.27 or 0.8 mm. In spite of increased ball pitches, BGAs result in smaller footprints than PQFPs. The photo at right shows an FBGA and a TBGA, in contrast to PQFPs with the same lead counts. Formally known as chip scale packages (CSPs), the fine-pitch BGA (FBGA) is generally defined as having a package body size no larger than 1.2 times the die size. Tape BGA (TBGA) packages support ultra-high pin count applications. TBGAs combine the fine die pad pitch interconnect advantages of TAB with the assembly ease of

BGAs. The center balls of the TBGA is depopulated to allow room for the facedown TAB bonded and encapsulated die.

# 144 Pins 304 Pins FBGA PQFP 0.8 mm-pitch 0.5 mm-pitch 0.9 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000

### Thin and Light Packages

LQFP and TQFP packages provide a thin, lightweight surface mount solution to system miniaturization. The package height is 1.4 mm (seating height = 1.6mm) for the LQFP lines and 1.0 mm (seating height = 1.2 mm) for the ultra thin

(seating height = 1.2 mm) for the ultra-thin TQFP lines. Also, TBGAs support both the low-profile and ultra-high-pin-count requirements. With their excellent heat dissipation, low profile, and low cost, TBGAs can handle a wide variety of applications.

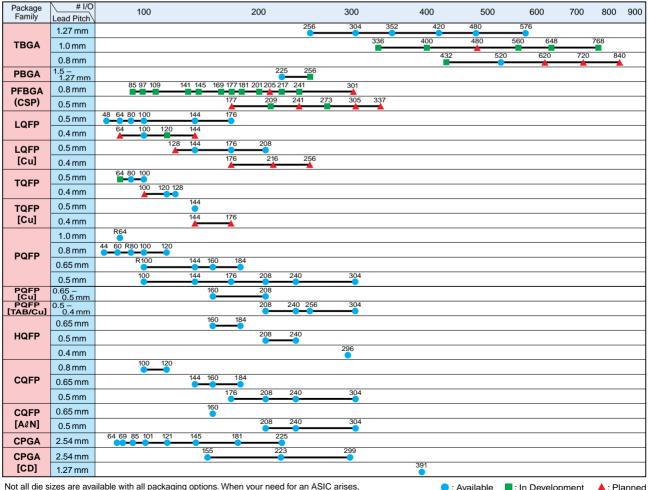

### Lead Count Chart

Not all die sizes are available with all packaging options. When your need for an ASIC arises, please contact the nearest ASIC service group.

# **Toshiba Documents**

### Brochures

- CMOS ASICs Product Guide

- ASIC Packaging

- 32-Bit TX System RISC TX19 Family

- 32-Bit TX System RISC TX39 Family

- 64-Bit TX System RISC TX49 Family

- Microcomputers Product Guide

- Microcomputer Development System Guide

### TX39

- 32-Bit RISC Microprocessor TLCS-R3900 Family (Architecture TMPR3901F)

- 32-Bit TX System RISC TX39 Family User's Manual (Hardware)

- 32-Bit TX System RISC TX39 ASIC Design Guide

### **TX19**

• 32-Bit TX System RISC TX19 User's Manual (Architecture)

### **TX49**

• 64-Bit RISC Microprocessor TX49 User's Manual

### TLCS-900/H and TLCS-900/L1

- 16-Bit Microcontroller TLCS-900/H Series User's Manual (1)

- Development System Manual (ASSEMBLER)

- Development System Manual (C COMPILER)

- Microcomputer Development System Real-time OS (User's Manual)

- 16-Bit Microcontroller TLCS-900/H, TLCS-900/L APPLICATION NOTE

### Design Handbooks

- User's manuals for various EDA tools

- CMOS ASIC Design Manual

- Design-for-Test Handbook

- ASIC Packaging

### **OVERSEAS SUBSIDIARIES AND AFFILIATES**

Headquarters-Irvine, CA 9775 Toledo Way, Irvine, CA 92618, U.S.A. Tel: (949)455-2000 Fax: (949)859-3963

**Boulder, CO** 3100 Arapahoe Avenue, Ste. 500, Boulder, CO 80303, U.S.A. Tel: (303)442-3801 Fax: (303)442-7216

Boynton Beach, FL(Orlando) 11924 W. Forest Hill Blvd., Ste. 22-337, Boynton Beach, FL 33414, U.S.A. Tel: (561)374-6193 Fax: (561)374-6194

Deerfield, IL(Chicago) One Pkwy., North, Suite 500, Deerfield, IL 60015-2547, U.S.A. Tel: (847)945-1500 Fax: (847)945-1044

Duluth, GA(Atlanta) 3700 Crestwood Parkway, Ste. 460, Duluth, GA 30096, U.S.A. Tel: (770)931-3363 Fax: (770)931-7602

Edison, NJ 2035 Lincoln Hwy. Ste. #3000, Edison NJ 08817, U.S.A. Tel: (732)248-8070 Fax: (732)248-8030

Orange County, CA 2 Venture Plaza, #500 Irvine, CA 92618, U.S.A. Tel: (949)453-0224 Fax: (949)453-0125

Portland, OR 1700 NW 167th Place, #240, Beaverton, OR 97006, U.S.A. Tel: (503)629-0818 Fax: (503)629-0827

### Richardson, TX(Dallas)

777 East Campbell Rd., Suite 650, Richardson, TX 75081, U.S.A. Tel: (972)480-0470 Fax: (972)235-4114

San Jose Engineering Center, CA 1060 Rincon Circle, San Jose, CA 95131, U.S.A. Tel: (408)526-2400 Fax:(408)526-2410

#### Wakefield, MA(Boston)

401 Edgewater Place, Suite #360, Wakefield, MA 01880-6229, U.S.A. Tel: (781)224-0074 Fax: (781)224-1095

#### **Toshiba Electronics Europe GmbH**

Düsseldorf Head Office Hansaallee 181, D-40549 Düsseldorf Germany Tel: (0211)5296-0 Fax: (0211)5296-400

München Office

Büro München Hofmannstrasse 52,

D-81378, München, Germany

Tel: (089)748595-0

Fax: (089)748595-42

### Toshiba Electronics France SARL Immeuble Robert Schumann 3 Rue de Rome,

F-93561, Rosny-Sous-Bois, Cedex, France Tel: (1)48-12-48-12 Fax: (1)48-94-51-15

### Toshiba Electronics Italiana S.R.L.

Centro Direzionale Colleoni Palazzo Perseo Ingr. 2-Piano 6, Via Paracelso n.12, 1-20041 Agrate Brianza Milan, Italy Tel: (039)68701 Fax:(039)6870205

#### Toshiba Electronics España, S.A.

Parque Empresarial San Fernando Edificio Europa, 1<sup>a</sup> Planta, ES-28831 Madrid, Spain Tel: (91)660-6700 Fax:(91)660-6799

#### Toshiba Electronics(UK) Limited

Riverside Way, Camberley Surrey, GU15 3YA, U.K. Tel: (01276)69-4600 Fax: (01276)69-4800

# Toshiba Electronics Scandinavia AB

Gustavslundsvägen 12, 2nd Floor S-161 15 Bromma, Sweden Tel: (08)704-0900 Fax: (08)80-8459

# Toshiba Electronics Asia (Singapore) Pte. Ltd.

#### Singapore Head Office

438B Alexandra Road, #06-08/12 Alexandra Technopark, Singapore 119968 Tel: (278)5252 Fax: (271)5155, (270)6056

#### **Bangkok Office**

135 Moo 5 Bangkadi Industrial Park, Tivanon Rd., Bangkadi Amphur Muang Pathumthani, Bangkok, 12000, Thailand Tel: (02)501-1635 Fax: (02)501-1638

# Toshiba Electronics Trading (Malaysia)Sdn. Bhd.

#### Kuala Lumpur Head Office

Suite W1203, Wisma Consplant, No.2, Jalan SS 16/4, Subang Jaya, 47500 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: (3)731-6311 Fax: (3)731-6307

#### Penang Office

Suite 13-1, 13th Floor, Menard Penang Garden, 42-A, Jalan Sultan Ahmad Shah, 100 50 Penang, Malaysia Tel: 4-226-8523 Fax: 4-226-8515 Toshiba Electronics Philippines, Inc.

26th Floor, Citibank Tower, Valero Street, Makati, Manila, Philippines Tel: (02)750-5510 Fax: (02)750-5511

#### Toshiba Electronics Asia, Ltd.

#### Hong Kong Head Office

Level 11, Top Glory Insurance Building, Grand Century Place, No.193, Prince Edward Road West, Mong Kok, Kowloon, Hong Kong Tel: 2375-6111 Fax: 2375-0969

#### **Beijing Office**

Rm 714, Beijing Fortune Building, No.5 Dong San Huan Bei-Lu, Chao Yang District, Beijing, 100004, China Tel: (010)6590-8795 Fax: (010)6590-8791

#### Chengdu Office

Unit F, 18th Floor, New Times Plaza, 42 Wenwu Road, Xinhua Avenue, Chengdu, 610017, China Tel: (028)675-1773 Fax: (028)675-1065

#### Shenzhen Office

Rm 3010-3012, Office Tower Shun Hing Square, Di Wang Commercial Centre, 333 ShenNan East Road, Shenzhen, 518008, China Tel: (0755)246-1582 Fax: (0755)246-1581

#### **Toshiba Electronics Korea Corporation**

#### Seoul Head Office

14/F, KEC B/D, 257-7 Yangjae-Dong, Seocho-ku, Seoul, Korea Tel: (02)589-4334 Fax: (02)589-4302

#### Kumi Office

6/F, Ssangyong Investment Securities B/D, 56 Songjung-Dong, Kumi City Kyeongbuk, Korea Tel: (82)546-456-7613 Fax: (82)546-456-7617

# Toshiba Technology Development (Shanghai) Co., Ltd.

23F, Shanghai Senmao International Building, 101 Yin Cheng East Road, Pudong New Area, Shanghai, 200120, China Tel: (021)6841-0666 Fax: (021)6841-5002

# Tsurong Xiamen Xiangyu Trading Co., Ltd.

8N, Xiamen SEZ Bonded Goods Market Building, Xiamen, Fujian, 361006, China Tel: (0592)562-3798 Fax: (0592)562-3799

# Toshiba Electronics Taiwan Corporation

#### **Taipei Head Office**

17F, Union Enterprise Plaza Bldg. 109 Min Sheng East Rd., Section 3, 0446 Taipei, Taiwan R.O.C. Tel: (02)514-9988 Fax: (02)514-7892

#### Kaohsiung Office

16F-A, Chung-Cheng Bldg., Chung-Cheng 3Rd., 80027, Kaohsiung, Taiwan R.O.C. Tel: (07)222-0826 Fax: (07)223-0046

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document may include products subject to the foreign exchange and foreign trade laws.

### TOSHIBA CORPORATION

Electronic Devices Sales & Marketing Group 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 105-8001, Japan Tel: (03)3457-3405 Fax: (03)5444-9431