# **TOSHIBA**

# 0.25 µm CMOS ASIC TC240 Families

**NEW PRODUCT GUIDE**

# System ASIC Solution TC240 Family

Fabricated on an advanced 0.25-micron process, the TC240 family provides unique capabilities for systems-on-a-chip. The "unified cell architecture" created for the TC240 family allows you to mix gate-array-based logic and cell-based functions in the same design, providing an optimal balance of chip cost, silicon performance, and development time. The TC240 family offers a gallery of cores compliant with Virtual Socket Interface (VSI). In addition, the TC240 family allows you to create a logic design and later port it to a merged DRAM-on-logic process.

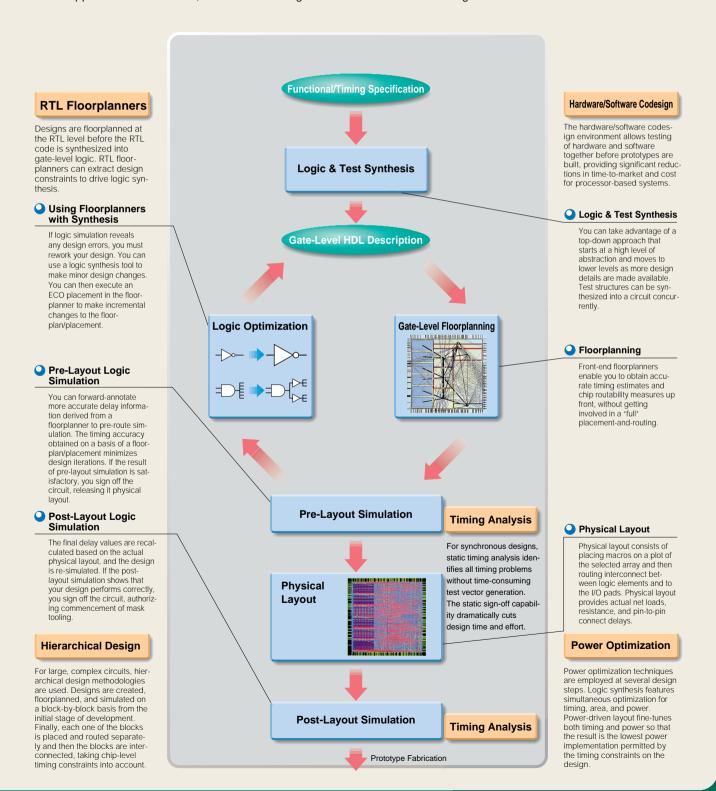

Toshiba makes available to you all tools needed for multi-million-gate designs. Encompassing Toshiba's adaptable EDA highlights are static-timing-analysis sign-off and hierarchical designs methodologies. Compliers and debuggers are being totally revamped for microprocessor-based designs.

The TC240 package offerings include a wide range of solutions for every system application, including high-pin-count, high-performance, and high-density packages.

For true system-scale integration, the TC240 family covers a full spectrum of application requirements with a broad range of power, density, and speed solutions, complete with core function and high-performance I/O support.

# ■ Key Features

# 0.25-Micron, 5-Metal Layer Process

The TC240 family is fabricated on a 0.25-micron five-layer stacked-via metal CMOS process, with the world's narrowest line pitch and shallow trench isolation. This new process yields 10 million-plus maximum usable gates — an approximately 3 times gate density improvement compared to the previous generation technology.

# Ultra-Fast Speed

The TC240 family features the use of salicide on the gate to reduce parasitic resistance and capacitance. Coupled with an effective channel length of 0.18 micron, this gives rise to a 20 percent speed improvement over the previous generation technology.

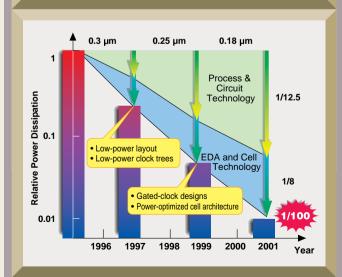

# Low Power Dissipation

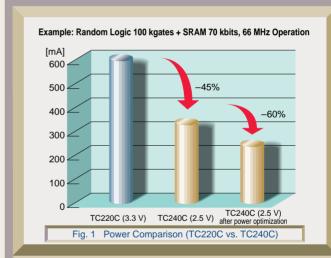

The TC240 family is optimized for low 2.5 V, a de facto industry standard with a quarter-micron technology, reducing power dissipation by 45 percent compared to the existing 3.3-V products. Unique circuit optimization techniques employed during both logic synthesis and physical layout can deliver up to 60 percent reduction in power dissipation (Fig. 1). For best results, four or more drive-strength variations of macrocells are available, allowing the optimal tuning of performance and power. While tailored to run at 2.5 V, the TC240 family gives you a flexibility with your system interface design by offering an optional 3.3-V I/O interfacing.

# High I/O Counts

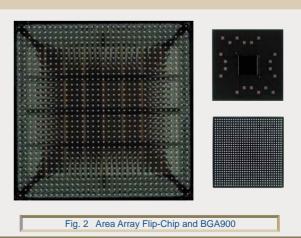

A migration from peripheral leads to an area array format is necessary to achieve reasonable package sizes and silicon/package electrical performance requirements for system chips. With the TC240 family, four of the five metal layers are used for interconnects; the fifth (or the uppermost) is reserved for full-area bonding pad array for flip-chip interconnects. Designs with over 500 I/Os can be captured on a small die (Fig. 2). Flip-chip BGAs are also offered for easy attachment to a circuit board.

# Product Summary

| Process Technology                        |                               | $0.25~\mu \mathrm{m}$ HC $^2$ MOS Si-gate five layer metal |        |        |                |        |        |        |

|-------------------------------------------|-------------------------------|------------------------------------------------------------|--------|--------|----------------|--------|--------|--------|

| Series                                    |                               | Gate Arrays & Embedded Arrays                              |        |        | Cell-Based ICs |        |        |        |

| Maximum Usable Gates*1 (with four metals) |                               | 10 Mgates                                                  |        |        | 12 Mgates      |        |        |        |

| Delay<br>Time<br>(ps)                     | Cell Name*2                   | GND2X1                                                     | GND2X2 | GND2X4 | CND2XL         | CND2X1 | CND2X2 | CND2X4 |

|                                           | Fanout=1                      | 77                                                         | 68     | 61     | 87             | 70     | 55     | 54     |

|                                           | Fanout=1+Typical Interconnect | 141                                                        | 101    | 79     | 218            | 118    | 83     | 68     |

| Power Dissipation (µW/MHz, Fanout=1)      |                               | 0.156                                                      | 0.270  | 0.487  | 0.107          | 0.170  | 0.296  | 0.563  |

| Operating Voltage                         |                               | Core: 2.5 V<br>I/Os: 2.5 V/3.3 V                           |        |        |                |        |        |        |

- \*1 Depends on design configurations.

- \*2 ND2 X 1:2-input NAND gate, 1x drive

- □ND2 X 2:2-input NAND gate, 2x drive

- □ND2 X 4:2-input NAND gate, 4x drive

- □ND2 X L:2-input NAND gate, 1/2x drive

# ■ Unified Cell Architecture

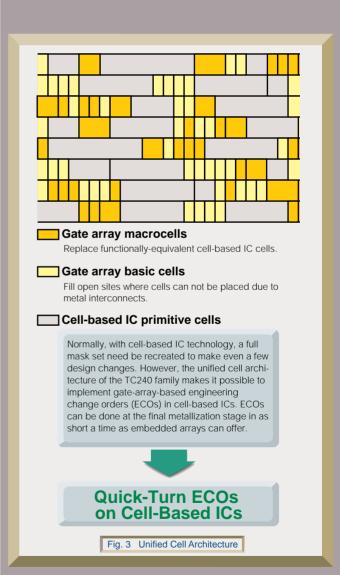

Recently, with the markedly increasing levels of integration, specialized large functions such as embedded cores have become indispensable. Thus cell-based ICs have come to command a larger proportion of ASIC business.

However, the move to the quarter-micron generation brings with it not only greater chip densities and higher speed but higher costs and longer turnaround times, mostly due to photomask creation. This equates to greater risks as well. Furthermore, even with the advancement of EDA technologies, designing multi-million-gate designs require several synthesis-layout iterations. Each iteration can be time-consuming and costly. Even when you want to implement only small design changes, a full mask set need be recreated with the cell-based IC technology.

To eliminate this bottleneck, Toshiba created a "unified cell architecture" for embedded arrays. This new architecture uses the same cell height and routing grid structure for gate arrays as it does for cell-based ICs. This enables the designer to mix gate-array-based logic with cell-based functions in the same chip. Implemented in the unified cell architecture, small cells like 2-input NAND gates do not exhibit noticeable differences between gate arrays and cell-based ICs in terms of size and electrical characteristics. In addition, gate array cells can fill all open sites after cores are placed. This creates a block of uncommitted cells fabricated in gate array technology within cell-based ICs. Consequently, the designer can create a bug fix with gate array lead times and costs, because only the metal interconnect masks need be redefined.

Toshiba has teamed with In-Chip Systems, Inc. (Los Altos, Calif.) to offer the new NXT gate array cell architecture. The NXT architecture features low power dissipation and a dramatically increased percentage of routable cells per mm2.

# ■ Toshiba EDA Environment

To make it easier to take full advantage of Toshiba's world-class silicon capabilities, we have gone to extraordinary lengths to make the Toshiba EDA environment a flexible, adaptable environment. Now the "static sign-off" or the ability to sign off on synchronous designs based on static timing analysis allows you to ensure exhaustive timing coverage while using timing simulation to execute a more focused functional verification. For mega-plus-gate designs, hierarchical design methodologies including RTL floorplanning are essential. Also among Toshiba's adaptable EDA highlights are power optimization at several stages of design, <100-ps skew clock tree synthesis, timing-driven layout, and so on

For system ASICs with an on-chip microprocessor, compilers, debuggers, and emulators are being improved. In April 1997, Toshiba created the Computer on Silicon (COS) business unit to focus on service and software issues for system ASICs. Toshiba also provides middleware products to ease development of video, audio, communication, and other applications. In addition, Toshiba is working on hardware/software codesign tools.

# ■ TC240 Boosts Systems-on-a-Chip Integration

# Increasing Need for System Chips

The race is on among electronics manufacturers to roll out multimedia products that capture and present information in a combination of text, graphics, video, animation, and sound. Multimedia chips demand ever increasing levels of performance, versatility, and functionality. At the same time, markets are expanding for such portable products as palmtop PCs, personal digital assistants (PDAs), digital still cameras, digital camcorders, automobile navigation systems, and cellular phones. This trend is creating a demand for longer battery life and increased mobility.

The high-density and lower-power features of the TC240 family are essential elements for the success of advanced designs for system ASICs.

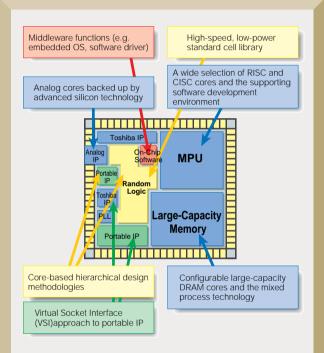

# A Gallery of Cores

Typical system chips integrate a wide variety of functions. To meet the challenges of system chips, ASIC core libraries must include a whole suite of core functions such as microprocessor cores, large-capacity memory cores, and many hardware intellectual-property (IP) functions. In addition, system chips may also require soft (or synthe-sizable) IP cores that implement embedded OSes, middleware functions, and software drivers.

Access to a wide range of advanced system building blocks and the supporting infrastructure are the key to the success of system ASICs. An abbreviated list of cores in development for implementation in the TC240 family include:

- TX System RISC processor cores (MIPS RISC cores)

- Toshiba-original CISC controller cores

- Media compression/decompression cores

- Network/communication cores

- Protocol controller cores

- Analog cores

- DRAM cores

- I/O interface cores

# Low Power Technology

The benefits of high integration can only be appreciated if power dissipation is reduced. The need for power reduction is increasingly acute as portable products become more commonplace. Power minimization is of utmost importance since customers of these products rank long battery life at the top of their feature preferences. Power dissipation problems also arise due to the ever increasing complexity of ASIC designs. Power-hungry chips may weight down ASIC and system designs because of overheating issues.

In October 1995, Toshiba launched the 100x Power Savings Project. The roadmap seeks to reduce power dissipation to one-hundredth within this century. The project consists of two working parties, one putting an emphasis on finer- and lower-power processes and advanced circuit architectures, and the other on more efficient EDA tools and new design optimization techniques.

#### Toshiba America **Electronic Components, Inc.**

#### Headquarters-Irvine, CA

9775 Toledo Way, Irvine CA 92718, U.S.A

Tel: (714)455-2000 Fax: (714)859-3963

#### Altamonte Springs, FL(Orland)

600 S. North Lake Blvd., Suite 250, Altamonte Springs, FL 32701, U.S.A. Tel: (407)332-0966 Fax: (407)339-3777

#### Deerfield, IL(Chicago)

One Pkwy., North, Suite 500, Deerfield, IL 60015-2547, U.S.A. Tel: (847)945-1500 Fax: (847)945-1044

#### Denver CO

8400 E, Prentice Englewood, CO 80111, U.S.A. Tel: (303)220-9848 Fax: (303)220-9856

#### Edison, NJ

2035 Lincoln Hwy. Ste. #3000, Edison NJ 08817, U.S.A.

Tel: (908)248-8070 Fax: (908)248-8030

#### Irvine, CA

2 Venture Plaza, Suite 500, Irvine, CA 92718 U.S.A.

Tel: (714)453-0224 Fax: (714)453-0125

#### Microelectronics Center-Sunnyvale, CA

1220 Midas Way, Sunnyvale, CA 94088-3509, U.S.A.

Tel: (408)739-0560 Fax: (408)746-0577

#### Norcross, GA(Atlanta)

655 Engineering Dr. #160, Norcross, GA 30092 U.S.A.

Tel: (404)368-0203 Fax: (404)368-0075

#### Richardson, TX(Dallas)

777 East Campbell Rd., Suite 650, Richardson, TX 75081 U.S.A.

Tel: (214)480-0470 Fax: (214)235-4114

#### Wakefield, MA(Boston)

401 Edgewater Place, Suite #360, Wakefield, Essex, MA 01880-6229, U.S.A. Tel: (617)224-0074 Fax:(617)224-1095

## San Jose Engineering Center, CA

1060 Rincon Circle, San Jose CA 95131, U.S.A.

Tel: (408)456-8900 Fax: (408)456-8910

#### **Toshiba Electronics Europe GmbH**

#### Düsseldorf Head Office

Hansaallee 181, D-40549 Düsseldorf Germany

Tel: (0211)5296-0 Fax: (0211)5296-400

#### Stuttgart Office

Buro Stuttgart, Eltinger Str. 61, D-71229 Leonberg, Germany Tel: (07152)6045-0 Fax: (07152)6045-45

#### München Office

Büro München Hofmannstrasse 52, D-81378, München, Germany Tel: (089)748595-0 Fax: (089)748595-42

#### **Berlin Office**

Buro Berlin, Alt-Moabit 96B. D-10559, Berlin, Germany Tel: (030)-3999000 Fax: (030)-3999017

#### **Toshiba Electronics France SARL**

Immeuble Robert Schumann 3 Rue de Rome. F-93561, Rosny-Sous-Bois, Cedex, France Tel: (1)48-12-48-12 Fax: (1)48-94-51-15

#### Toshiba Electronics Italiana S.R.L.

Centro Direzionale Colleoni Palazzo Perseo Ingr. 2-Piano 6, Via Paracelso n.12, 1-20041 Agrate Brianza Milan, Italy Tel: (039)68701 Fax:(039)6870205

#### Toshiba Electronics España, S.A.

Parque Empresarial San Fernando Edificio Europa, 1<sup>a</sup> Planta, ES-28831 Madrid, Spain Tel: (91)660-6700 Fax:(91)660-6799

#### Toshiba Electronics(UK) Limited

Riverside Way, Camberley Surrey, GU15 3YA, U.K.

Tel: (01276)69-4600 Fax: (01276)69-4800

#### Toshiba Electronics Scandinavia AB

Gustavslundsvägen 12, 2nd Floor S-161 15 Bromma, Sweden Tel: (08)704-0900 Fax: (08)80-8459

#### **Toshiba Electronics Asia** (Singapore) Pte. Ltd.

# Singapore Head Office

460 Alexandra Rd., #21-00 PSA Bldg., Singapore 0511 Tel: (278)5252 Fax: (271)5155, (270)6056

#### **Bangkok Office**

135 Moo 5 Bangkadi Industrial Park, Tivanon Rd., Bangkadi Amphur Muang Pathumthani 12000, Thailand

Tel: (2)501-1635 Fax: (2)501-1638

#### **Toshiba Electronics Trading** (Malaysia)Sdn. Bhd.

# Kuala Lumpur Head Office

Suite W1203, Wisma Consplant, No.2, Jalan SS 16/4, Subang Jaya, 47500 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: (3)731-6311 Fax: (3)731-6307

#### Penang Office

Suite 13-1, 13th Floor, Menard Penang Garden, 42-A. Jalan Sultan Ahmad Shah. 100 50 Penang, Malaysia Tel: 4-226-8523 Fax: 4-226-8515

#### Toshiba Electronics Asia, Ltd.

#### Hong Kong Head Office

Level 11, Top Glory Insurance Building, Grand Century Place. No.193, Prince Edward Road West, Mong Kok, Kowloon, Hong Kong Tel: 2375-6111 Fax: 2375-0969

#### Seoul Branch

14/F. KEC B/D. 257-7 Yangiae-dong. Seocho-ku, Seoul, Korea Tel: (02)589-4334 Fax: (02)589-4302

#### Seoul Branch, Gumi Office

6/F. Ssangvong Investment Securities B/D. 56 Songjung-Dong, Gumi City Kveonghuk Korea Tel: (0645)456-7613-6 Fax: (0546)456-7617

# Shenzhen Office

Rm 3010-3012, Shun Hing Square, Di Wang Commercial Centre. 333 Shennan Road East, Shenzhen, China, 518008 Tel: (0755)246-1582 Fax: (0755)246-1581

#### Shanghai Office

RM2612 26F, Rui Jin Bldg., 205 Mao Ming South Rd., Shanghai, China Tel: (021)64723077 Fax:(021)64727028

#### Tsurong Xiamen Xiangyu Trading Co., Ltd.

8N, Xiamen Sez Bonded Goods Market Building, Xiamen, Fujian, China Tel: (0592)562-3798 Fax:(0592)562-3799

#### **Beijing Office**

Rm 714, Beijing Fortune Building, No.5 Dong San Huan Bei-Lu, Chao Yang District, Beijing, China, 10004 Tel:(010)6595-8795 Fax: (010)6591-9346

#### **Toshiba Electronics Taiwan Corporation**

#### **Taipei Head Office**

17F, Union Enterprise Plaza Bldg. 109 Min Sheng East Rd., Section 3, 0446 Taipei, Taiwan R O C

Tel: (02)514-9988 Fax: (02)514-7892

## **Kaohsiung Office**

16F-A, Chung-Cheng Bldg., Chung-Cheng 3Rd., 80027, Kaohsiung, Taiwan R.O.C. Tel: (07)222-0826 Fax: (07)223-0046

#### **Toshiba Display Devices** (Thailand) Co., Ltd.

142 Moo 5, Bangkadi Industrial Park Tivanon Rd., Pathumthani 12000, Thailand Tel: (2)501-1200 Fax: (2)501-1209

The information contained herein is subject to change without notice

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook

In Touch with Tomorrow TOSHIBA

# TOSHIBA CORPORATION

**International Operations-Electronic Components** 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 105-01, Japan Tel:(03)3457-3495 Fax: (03)5444-9431

The products described in this document may include products subject to foreign exchange and foreign trade control laws