# SHT32E22 32×8 LCD Driver

## **Description**

The SHT32E22 is a 32×8 pattern LCD driver. It uses internal stored RAM data to display the digital numbers. It can communicate with external controller via 3-line interface. Three

system commands can be used to set the different functions of SHT32E22 and three data commands are used to access to internal RAM. SHT32E22 also provides power down and LCD display off features.

#### **Features**

- \* Provides internal voltage generator and VLCD pin for adjusting LCD operating voltage.

- \* Three lines serial data interface.

- \* Provides on-chip RC oscillator, or external oscillator input as system clock source.

- \* 32 segments output.

- \* 8 commons output.

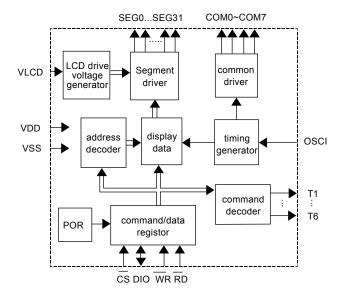

## **Block Diagram**

1

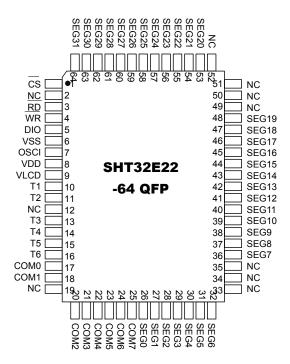

## Pin Assignment

Pin Description

| Pin Name | I/O          | Description                                                                                                                                                                                                                    |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD      | power supply | Positive power supply                                                                                                                                                                                                          |

| VSS      | power supply | Negative power supply, ground                                                                                                                                                                                                  |

| CS       | I            | Chip select input with pull-high resistor, active low. The $\overline{\text{CS}}$ pin should be set to high level after one command excuted, and excuting a new command $\overline{\text{CS}}$ pin should returns to low level |

| WR       | I            | Write control input with pull-high resistor, active low.                                                                                                                                                                       |

| RD       | I            | Read control input with pull-high resistor, active low.                                                                                                                                                                        |

| Pin Name   | I/O | Description                                                                                                                                             |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIO        | I/O | Serial data in/out with pull-high resistor.                                                                                                             |

| OSCI       | I   | If external 32KHz clock source is used as system clock, then pin OSCI is connected, if built-in RC oscillator is used, and then pins OSCI is left open. |

| VLCD       | I   | LCD power input, this voltage should be less than or equal to VDD                                                                                       |

| T1~T6      | О   | Testing only                                                                                                                                            |

| SEG0~SEG31 | О   | Output pin for LCD segment driving                                                                                                                      |

| COM0~COM7  | О   | Output pin for LCD common driving                                                                                                                       |

# Absolute Maximum Ratings

| Supply Voltage0.3V ~5.5V                                 | Storage Temperature50°C ~125°C  |

|----------------------------------------------------------|---------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V~V <sub>DD</sub> +0.3V | Operating Temperature40°C ~85°C |

## **D.C.**Characteristics

Ta=25°C

|                  |                            |                 | Test Conditions          |      | _    |      |      |

|------------------|----------------------------|-----------------|--------------------------|------|------|------|------|

| Symbol           | Parameter                  | V <sub>DD</sub> | Conditions               | Min. | Тур. | Max. | Unit |

| $V_{DD}$         | Operating Voltage          | -               | _                        | 2.4  | -    | 5.2  | V    |

| I <sub>DD1</sub> | Operating Current          | 3V              | No load or LCD ON        | _    | 80   | 210  | μA   |

| 1טטי             | Operating Current          |                 | On-chip RC oscillator    | _    | 135  | 415  | μΑ   |

| I <sub>DD2</sub> | Operating Current          | 3V              | No load or LCD OFF       | _    | 8    | 30   | μΑ   |

| 'DD2             | Operating Current          | 5V              | On-chip RC oscillator    | _    | 20   | 55   | μΑ   |

| 1                | Standby Current            | 3V              | No load, Power down mode | _    | 1    | 8    | μΑ   |

| I <sub>STB</sub> | Standby Current            | 5V              | No load, Power down mode | _    | 2    | 16   | μΑ   |

| VII              | Input Law Valtage          | 3V              | DIO, WR, CS, RD          | 0    | _    | 0.6  | V    |

| VIL              | Input Low Voltage          | 5V              | DIO, WK, CS, RD          | 0    | _    | 1.0  | V    |

| VIH              | Land Alliah Mallana        |                 | DIO, WR, CS, RD          | 2.4  | _    | 3    | V    |

| VIH              | Input High Voltage         | 5V              | DIO, WK, CS, KD          | 4.0  | _    | 5    | V    |

| la               | DIO                        | 3V              | V <sub>OL</sub> =0.3V    | 200  | 450  | _    | μΑ   |

| I <sub>OL1</sub> | DIO                        | 5V              | V <sub>OL</sub> =0.5V    | 250  | 500  | _    | μΑ   |

| I <sub>OH1</sub> | DIO                        | 3V              | V <sub>OH</sub> =2.7V    | -200 | -450 | _    | μΑ   |

| IOH1             |                            | 5V              | V <sub>OH</sub> =4.5V    | -250 | -500 | _    | μA   |

| I <sub>OL2</sub> | LCD Common Sink Current    | 3V              | V <sub>OL</sub> =0.3V    | 15   | 40   | _    | μΑ   |

| 'OL2             | LCD Common Sink Current    |                 | V <sub>OL</sub> =0.5V    | 100  | 200  | _    | μΑ   |

| I <sub>OH2</sub> | LCD Common Source Current  | 3V              | V <sub>OH</sub> =2.7V    | -15  | -30  | _    | μΑ   |

| IOH2             | ECD Common Source Current  |                 | V <sub>OH</sub> =4.5V    | 45   | -90  | _    | μΑ   |

| I <sub>OL3</sub> | LCD Sogmont Sink Current   | 3V              | V <sub>OL</sub> =0.3V    | 15   | 30   | _    | μΑ   |

| OL3              | LCD Segment Sink Current   |                 | V <sub>OL</sub> =0.5V    | 70   | 150  | _    | μΑ   |

| I <sub>OH3</sub> | LCD Segment Source Current | 3V              | V <sub>OH</sub> =2.7V    | -6   | -13  | _    | μΑ   |

| •ОН3             | LOD Segment Source Current | 5V              | V <sub>OH</sub> =4.5V    | 20   | -40  | _    | μΑ   |

| R <sub>PH</sub>  | Pull high Pecistor         | 3V              | DIO, WR, CS, RD          |      | 200  |      | kΩ   |

| TYPH             | Pull-high Resistor         |                 | DIO, WK, CO, KD          | _    | 100  | _    | kΩ   |

## **A.C.Characteristics**

Ta=25 ℃

| Cl I                            | Parameter V <sub>1</sub>                                                                       |       | Test Conditions            | Min. | Тур. |      |      |

|---------------------------------|------------------------------------------------------------------------------------------------|-------|----------------------------|------|------|------|------|

| Symbol                          |                                                                                                |       | Conditions                 |      |      | Max. | Unit |

| f                               | System Closk                                                                                   | 3V    | On ahin DC agaillatar      | 25   | 32   | 36   | kHz  |

| f <sub>SYS1</sub>               | System Clock                                                                                   | 5V    | On-chip RC oscillator      | 25   | 32   | 36   | kHz  |

| f                               | System Cleak                                                                                   | 3V    | Evitama el ala els accurac | -    | 32   | -    | kHz  |

| f <sub>SYS2</sub>               | System Clock                                                                                   | 5V    | External clock source      | _    | 32   | -    | kHz  |

| f                               | Optical DIO Objects (IMP of in)                                                                | 3V    | Duta                       | _    | _    | 150  | kHz  |

| f <sub>CLK1</sub>               | Serial DIO Clock (WR pin)                                                                      | 5V    | Duty cycle 50%             | _    | _    | 300  | kHz  |

|                                 |                                                                                                | 3V    | D / 1/                     | _    | -    | 75   | kHz  |

| f <sub>CLK2</sub>               | Serial DIO Clock (RD pin)                                                                      |       | Duty cycle 50%             | _    | _    | 150  | kHz  |

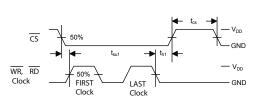

| t <sub>CS</sub>                 | Serial Interface Reset Pulse Width (Figure 3)                                                  | _     | <del>CS</del>              | -    | 250  | -    | ns   |

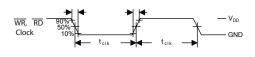

|                                 | WR, RD Input Pulse Width (Figure 1)                                                            | 3V 5V | Write mode                 | 3.34 | -    | -    |      |

|                                 |                                                                                                |       | Read mode                  | 6.67 | -    | -    | μs   |

| t <sub>CLK</sub>                |                                                                                                |       | Write mode                 | 1.67 | -    | -    |      |

|                                 |                                                                                                |       | Read mode                  | 3.34 | -    | -    | μS   |

|                                 | Rise/Fall Time Serial Data Clock Width                                                         | 3V    |                            |      | 400  |      |      |

| t <sub>r</sub> , t <sub>f</sub> | (Figure 1)                                                                                     | 5V    | _                          | _    | 120  | _    | ns   |

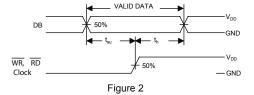

| 4                               | Setup Time for DATA to WR, RD Clock                                                            | 3V    |                            |      | 100  |      |      |

| t <sub>su</sub>                 | Width (Figure 2)                                                                               | 5V    | _                          | _    | 120  | _    | ns   |

| t <sub>h</sub>                  | Hold Time for DATA to WR, RD, Clock                                                            | 3V    | _                          | _    | 120  | _    | 20   |

| чn                              | Width (Figure 2)                                                                               | 5V    | _                          |      | 120  |      | ns   |

| t <sub>su1</sub>                | Setup Time for $\overline{\text{CS}}$ to $\overline{\text{WR}}$ , $\overline{\text{RD}}$ Clock | 3V    | _                          | _    | 100  | _    | ns   |

| *SUT                            | Width (Figure 3)                                                                               |       |                            |      | 100  |      | 113  |

| t <sub>h1</sub>                 | Hold Time for $\overline{\text{CS}}$ to $\overline{\text{WR}}$ , $\overline{\text{RD}}$ Clock  | 3V    | _                          | _    | 100  | _    | ns   |

| *111                            | Width (Figure 3)                                                                               |       |                            |      | 100  |      | 110  |

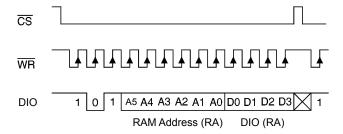

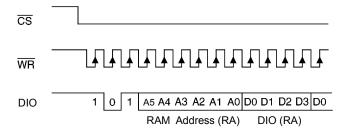

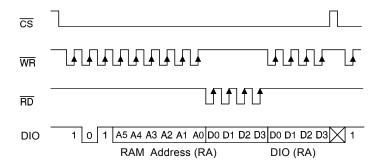

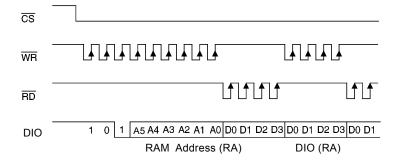

Figure 1

Figure 3

11th June'03

## Functional Description

### Command/Data register

☐ There are two registers within the chip. They are Command and Data registers.

The Command register is a 9-bit shift register. It receives the command bits c8,  $c7 \sim c0$  from the DIO bus on the rising edge of  $\overline{WR}$ . The Data register contains 4 bits,  $d3 \sim d0$ , It is also a 4-bit shift register, receiving serial bit from DIO bus on the rising edge of  $\overline{RD}$ .

#### Command Decoder

After Command register receiving the completed serial shift in data, Command Decoder will decode this data. And then this decoded data will control the whole chip operation.

## Display Data memory

The bit map of 32x8 internal RAM is as fallowing table.

|      |    | seg0 | seg1 | seg2 | <br>seg29 | seg30 | seg31 |

|------|----|------|------|------|-----------|-------|-------|

| Bit  | 0  |      |      |      |           |       |       |

|      | 1  |      |      |      |           |       |       |

|      | 2  |      |      |      |           |       |       |

|      | 3  |      |      |      |           |       |       |

| Bit' | 0' |      |      |      |           |       |       |

|      | 1' |      |      |      |           |       |       |

|      | 2' |      |      |      |           |       |       |

|      | 3' |      |      |      |           |       |       |

The internal RAM is organized 64 by 4. It contains 64 address and 4 bits data. The address and data are loaded into the chip through DIO bus while write command is executed. And then they are stored in the internal registers for RAM access, respectively. After data are written into the internal RAM, this 4-bit data are directly mapped into the LCD display panel. In addition to write command operation, the chip also accept READ and READ-MODIFY-WRITE commands.

The following is the mapping table between RAM data and contents of LCD driver.

|         | seg0 | seg1 | seg2 | <br>seg29 | seg30 | seg31 |       |

|---------|------|------|------|-----------|-------|-------|-------|

| COM0    |      |      |      |           |       |       | Bit0  |

| COM1    |      |      |      |           |       |       | Bit1  |

| COM2    |      |      |      |           |       |       | Bit2  |

| СОМЗ    |      |      |      |           |       |       | Bit3  |

| Address | 0    | 2    | 4    | <br>58    | 60    | 62    |       |

| COM4    |      |      |      |           |       |       | Bit0' |

| COM5    |      |      |      |           |       |       | Bit1' |

| COM6    |      |      |      |           |       |       | Bit2' |

| COM7    |      |      |      |           |       |       | Bit3' |

| Address | 1    | 3    | 5    | 59        | 61    | 63    |       |

#### Address counter

The address counter is resided in the chip. It receives the address via DIO bus while RAM access command is operated. The initial address can be set by the external controller, and also be auto increased by one in the auto increment mode.

#### Address decoder

After processed by address counter, this address is shift to the address decoder to be decoded again. And then give rise to a real address that used to addressing the internal RAM.

## Timing Generator

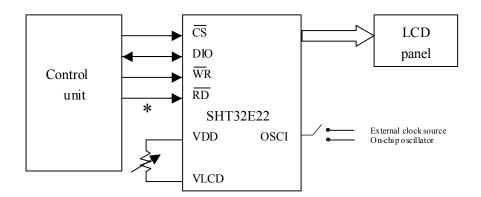

The SHT32E22 accepts one of two different clock sources as system clock. When external clock source is chosen, pin OSCI is served as input. The built-in RC oscillator is default chosen after power on.

#### Common counter

This counter is also resided in the internal chip. It is used as the timing control for output Common signal.

## Segment and Common

Through combining 32 segments and 8 commons, the chip can be used to drive off-chip LCD panel. And the voltage level of segments and commons is decided by VLCD voltage .

## Commands

SHT32E22 provides 3 system commands and 3 data access commands.

Through these commands, the external controller can communicate with SHT32E22 and display the desired data on the LCD panel.

#### Commands table:

| Command                | Code                    | Function                                |

|------------------------|-------------------------|-----------------------------------------|

| System clock selection | 10000011axxx            | Select one clock source for clock       |

|                        |                         | a: 0: built-in RC oscillator            |

|                        |                         | 1: external clock source                |

|                        |                         |                                         |

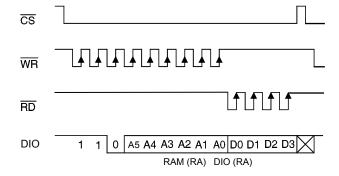

| Data read              | 110A5A4A3A2A1A0D0D1D2D3 | Data read from internal RAM             |

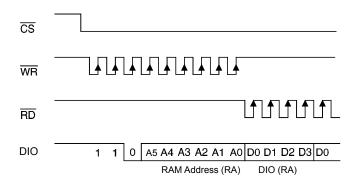

| Data write             | 101A5A4A3A2A1A0D0D1D2D3 | Data write from internal RAM            |

| Read-Modify-Write      | 101A5A4A3A2A1A0D0D1D2D3 | Data write after read from internal RAM |

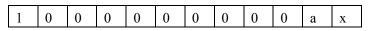

| System Enable/Disable  | 1000000000ax            | 1: Enable system oscillator             |

|                        |                         |                                         |

|                        |                         | 0: Disable both system oscillator and   |

|                        |                         | LCD display                             |

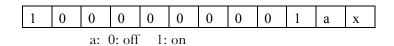

| LCD on/off             | 1000000001 ax           | Turn LCD display on or off              |

Note: x: don't care

A5~A0: Address of internal RAM for LCD display D3~D0: Data of internal RAM for LCD display

#### Auto increment mode

The SHT32E22 provides the auto increment mode for internal RAM access. In this mode, the address will be auto increased by one after the current address location has been accessed. The starting address will be set in the command byte first.

## Command description:

System clock selection:

|   |    |    |        |        |            |     |   |     |    |    | i  |

|---|----|----|--------|--------|------------|-----|---|-----|----|----|----|

| 1 | 0  | 0  | $\sim$ | $\sim$ | $^{\circ}$ | 1   | 1 | _   |    |    | i  |

|   | () | () | ()     | ()     | ()         | I I |   | l a | X  | X  | X  |

| - | 0  | 0  | V      | 0      | 0          | -   | - | ч   | 21 | 71 | 21 |

This command chooses one of two clock sources as system clock.

a: 0: built-in 32KHz RC oscillator 1: external 32KHz clock source

## Data read

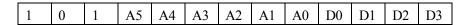

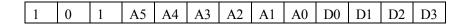

| 1   1   0   A5   A4   A3   A2   A1   A0   D0   D1   D2   D3 |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

The data stored in the internal RAM can be read out through DIO bus at specified address. After data been read out, the address will be auto increased by one in the auto increment mode.

The relations between A5~A0 and address are as follows:

| A5 | A4 | A3 | A2 | Al | A0 | address |

|----|----|----|----|----|----|---------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0       |

| 0  | 0  | 0  | 0  | 0  | 1  | 1       |

| 0  | 0  | 0  | 0  | 1  | 0  | 2       |

|    |    |    |    |    |    |         |

|    |    |    |    |    |    |         |

|    |    |    |    |    |    |         |

| 1  | 1  | 1  | 1  | 1  | 0  | 62      |

| 1  | 1  | 1  | 1  | 1  | 1  | 63      |

Auto increment mode

## Data write

Through data bus DIO, Data can be written into the internal RAM at address A5~A0. After data has been written, the address will be auto increased by one from the starting address in the auto increment mode.

#### Auto increment mode

## Read-Modify-Write

The data will be read out first according the specified address, and then the next 4 bits consecutive data will be written into the same address at next 4 cycles. If the auto increment mode is chosen, the next Read-Modify-Write command address will be increased by one automatically.

#### Auto increment mode

## System Enable / Disable:

a: 0: Disable both system oscillator and LCD display1: Enable system oscillator

After power on, both system and LCD display are default off. And this command can be used to switch the system on or off. When system is switch on, the LCD display can be set by LCD on/off command. Besides, if the system is turn off, the power consumption of the chip can be reduced dramatically.

## LCD on/off:

LCD display is turned on/off, the display is preset off after power on.

## Application diagram:

Control unit (Controller) with SHT32E22 application architecture:

Note: RD pin can be selected depending on the requirement of control unit.