# **ATM Traffic Shaper**

# (Generator/Receiver)

# SHAP3

| Title:       | ATM Traffic Shaper SHAP3 |  |  |  |

|--------------|--------------------------|--|--|--|

| Version:     | 2.0                      |  |  |  |

| Last update: | 14. November 1996        |  |  |  |

| Originator:  | M. Guth, T. Lux          |  |  |  |

| <b>Purpose:</b>  | Specify Shaper implementation  |

|------------------|--------------------------------|

| <b>Keywords:</b> | ATM, UPC, Shaping, Measurement |

#### Features

- Shaping on a per class basis

- Supports 32 classes

- Single or Dual Leaky Bucket Shaping function

- Allows control of PCR, SCR, MBS and CDV traffic parameters

- Allows 32 output rates per class per LB

- Select different parameter sets by HW or SW

- Up to 2M cells/class

- Uses low cost 60/70 ns Dynamic RAM

- Utopia level 1 and SAI compatible interfaces

- Output can be halted while arriving cells are stored

- Supports 53 and 56 byte cell size

- Cell size conversion 53 ↔ 56 bytes

- Cell drop and insert via microprocessor interface

- Repeated cell sequence transmission at specified rate

- 24 bit time stamp for cell arrival timing

| Draft | Approval | Date       | Reason for change |

|-------|----------|------------|-------------------|

| 1.0   |          | 31.08.1995 | Design Tape-out   |

| 1.1   |          | 08.03.1996 | Testing of device |

| 2.0   |          | 14.11.1996 |                   |

Nov-96 Page 1 of 55

# **Table of Contents**

| 1 General description              | 5  |

|------------------------------------|----|

| 2 ATM ports                        | 6  |

| 2.1 Input port                     |    |

| 2.1.1 Cell alignment               |    |

| 2.1.2 Utopia input port signals    |    |

| 2.1.3 Idle cells                   |    |

| 2.1.4 HEC check                    | 8  |

| 2.1.5 Cell format                  | 8  |

| 2.1.6 Time stamp                   | 9  |

| 2.1.7 Input status                 | 9  |

| 2.2 Output port                    | 10 |

| 2.2.1 Utopia output port signals   | 10 |

| 2.2.2 Idle cell production         | 11 |

| 2.2.3 Output cell format           | 11 |

| 2.2.4 Idle cell format             |    |

| 2.2.5 Circular mode                | 12 |

| 3 Shaping function                 | 12 |

| 3.1 Rate parameters                |    |

| 3.2 Special rates                  |    |

| 3.2.1 Full data stream             |    |

| 3.2.2 Stop data stream             |    |

| 3.3 Single Leaky Bucket            |    |

| 3.3.1 Rate control                 |    |

| 3.3.2 Examples                     |    |

| 3.4 Dual Leaky Bucket              |    |

| 3.4.1 Rate control                 |    |

| 3.4.2 Examples                     |    |

| 3.5 Cell Delay Variation.          |    |

| 4 Multiple classes                 | 10 |

| 4.1 Priorities setting             |    |

| 4.1.1 Static priority              |    |

| 4.1.1 State priority               |    |

| 4.1.3 Mixed priorities             |    |

| 4.2 Queue output conflicts         |    |

|                                    |    |

| 5 Class data                       |    |

| 5.1 Queue control RAM              |    |

| 5.1.1 Queue base address           |    |

| 5.1.2 Queue size                   |    |

| 5.1.3 CLP-level                    |    |

| 5.1.5 Queue level                  |    |

| 5.1.6 Queue status bits            |    |

| 5.1.7 Read/Write queue control RAM |    |

| 5.2 Read/Write Shaping settings    |    |

| 5.2.1 Write parameter or level RAM |    |

| 5.2.2 Read parameter or level RAM  |    |

| 5.2.3 Read/write static RAM        |    |

|                                    |    |

| 6 CLP bit handling                 |    |

| 7 Class assignment                 |    |

| 7.1 Header mask                    |    |

| 7.2 Lookup table                   |    |

| 7.3 General memory access          | 25 |

| 8 Class Rate Adaptation            | 25 |

| 8.1 Leaky Bucket select register   |    |

| 8.2 Parameter set select           | 26 |

| 8.3 Software rate control          |    |

|------------------------------------|----|

| 8.4 Hardware rate control          |    |

| 8.5 Parameter curves               |    |

| 8.5.1 Asymmetric change (ABR)      | 29 |

| 9 Local cells transfer             | 30 |

| 9.1 CPU cell handling              |    |

| 9.2 DMA cell handling              |    |

| 9.3 Read cell from data stream     |    |

| 9.4 Insert cell in data stream     | 31 |

| 9.5 Cell interface transfer format | 31 |

| 10 Traffic receiver & generator    |    |

| 10.1 Traffic receiver              |    |

| 10.2 Traffic generator             |    |

| 11 External memory                 | 34 |

| 11.1 Dynamic memory                |    |

| 11.1.1 Memory type                 |    |

| 11.1.2 Refresh rate                |    |

| 11.1.3 Configurations              |    |

| 11.2 Static memory                 |    |

| 12 Register summary                | 37 |

| 12.1 Dedicated registers           |    |

| 12.2 All purpose data registers    | 41 |

| 13 Signal description              | 44 |

| 13.1 ATM input port                | 44 |

| 13.2 ATM output port               |    |

| 13.3 Dynamic memory interface      |    |

| 13.4 Static memory interface       |    |

| 13.5 Microprocessor interface      |    |

| 13.6 Parameter select              |    |

| 13.7 System signals                | 46 |

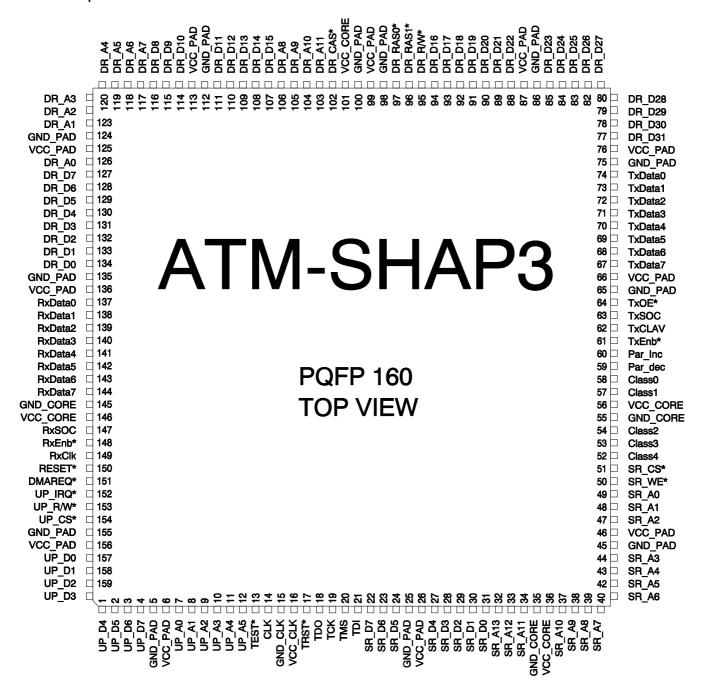

| 14 Pin assignment                  | 46 |

| 15 Timing diagrams                 | 49 |

| 16 Electrical Characteristics      | 52 |

| 16.1 Absolute Maximum Ratings      | 52 |

| 16.2 DC Characteristics            | 53 |

| 17 Thermal data                    | 53 |

| 18 Package                         | 54 |

| 18.1 Top view                      |    |

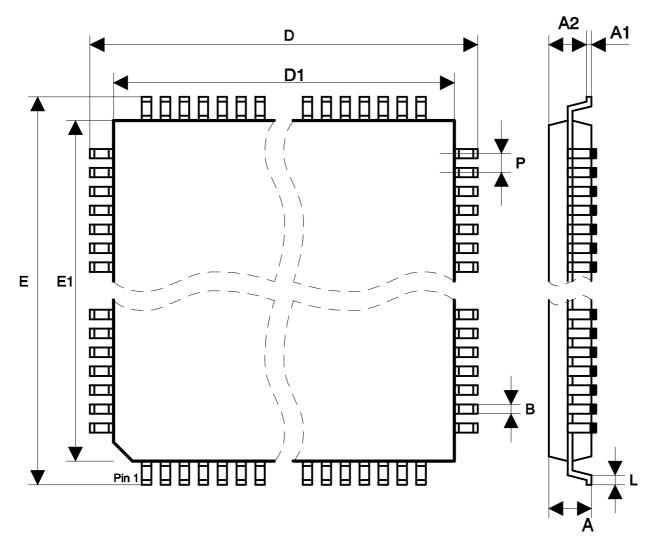

| 18.2 Mechanical data               | 55 |

# **Table of Figures**

| Figure 1-1: Block diagram of the SHAP3                              | 5  |

|---------------------------------------------------------------------|----|

| Figure 1-2: Class selection                                         | 6  |

| Figure 2-1: 53 Byte cell format                                     | 8  |

| Figure 2-2: 53 Byte + 3 routing tag bytes cell format               | 9  |

| Figure 2-3: 56 Byte cell format                                     | 9  |

| Figure 2-4: Stopping cell output for 53 byte cells                  | 11 |

| Figure 2-5: Stopping cell output for 56 Byte cells                  | 11 |

| Figure 3-1: Single Leaky Bucket with CDV of zero cell times         | 15 |

| Figure 3-2: Single Leaky Bucket with a CDV of three cell times      | 15 |

| Figure 3-3: Single Leaky Bucket with a CDV of two cell times        | 15 |

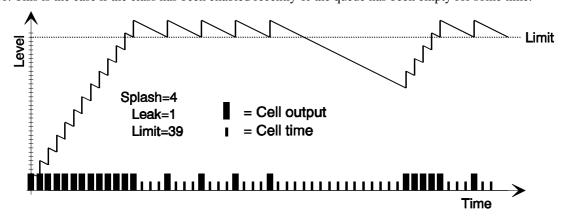

| Figure 3-4: Typical level behaviour                                 | 16 |

| Figure 3-5: Single Leaky Bucket with burst                          | 17 |

| Figure 3-6: Dual Leaky Bucket without CDV                           | 18 |

| Figure 3-7: Dual Leaky Bucket with CDV                              | 18 |

| Figure 4-1: Cell output without CDV                                 | 20 |

| Figure 4-2: Cell output with CDV of one                             | 20 |

| Figure 7-1: Header extraction mask                                  | 24 |

| Figure 8-1: Par_inc, Par_dec signal timing                          | 28 |

| Figure 8-2: Linear rate change                                      | 29 |

| Figure 8-3: Logarithmic rate change                                 | 29 |

| Figure 8-4: Pi-Curve rate change                                    | 29 |

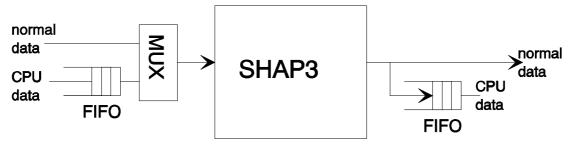

| Figure 9-1: Faster access to SHAP3 data                             | 30 |

| Figure 9-2: All purpose data register format 53 bytes               | 32 |

| Figure 9-3: All purpose data register format 53 bytes + routing tag | 32 |

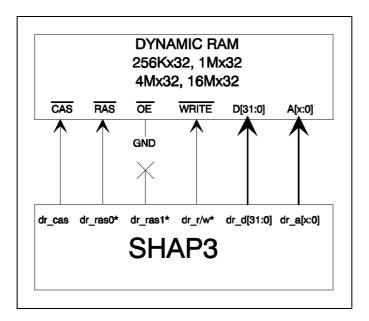

| Figure 11-1: Memory configuration with one bank                     | 36 |

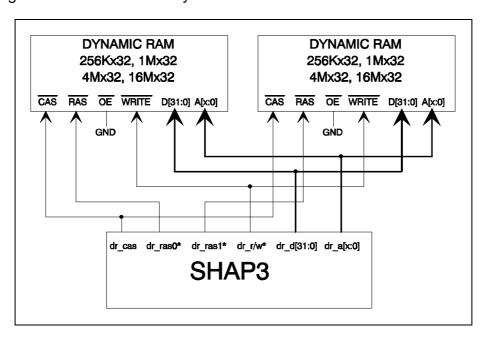

| Figure 11-2: Memory configuration with two banks                    | 36 |

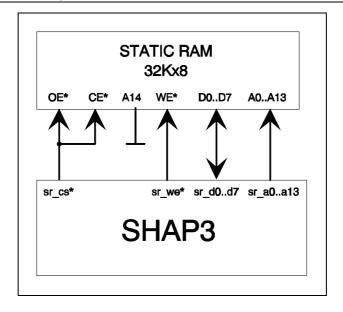

| Figure 11-3: Static RAM connected to SHAP3                          | 37 |

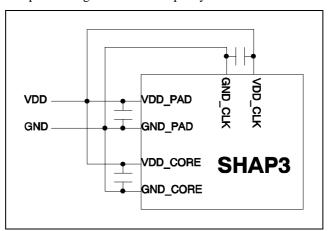

| Figure 14-1: Connecting Power and Ground                            | 49 |

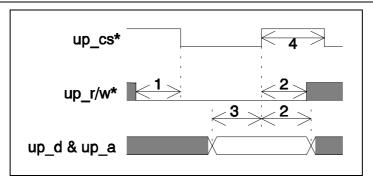

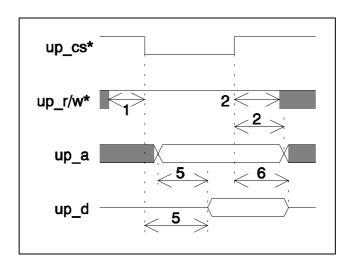

| Figure 15-2: Microprocessor write timing                            | 50 |

| Figure 15-3: Microprocessor read timing                             | 50 |

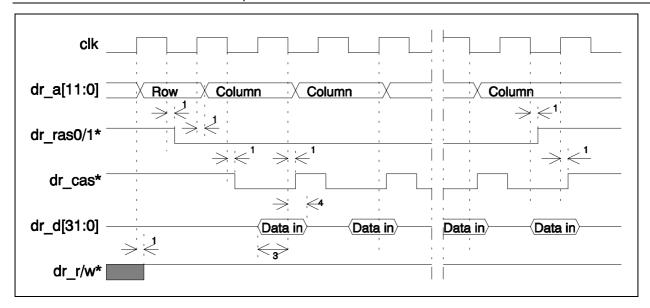

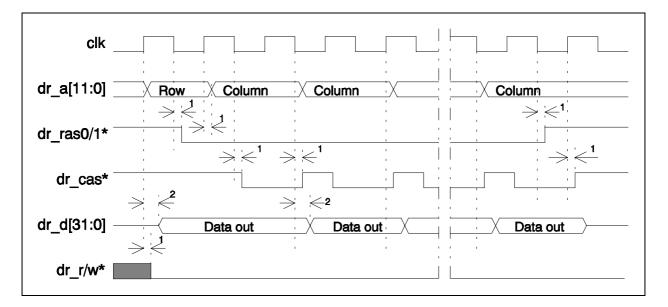

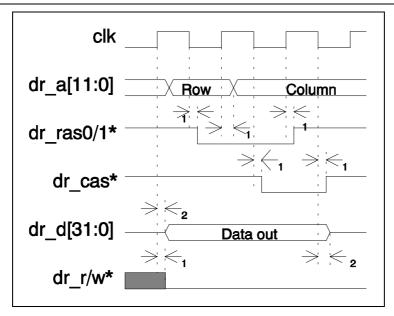

| Figure 15-4: Timing diagram read cell of the DRAM                   | 51 |

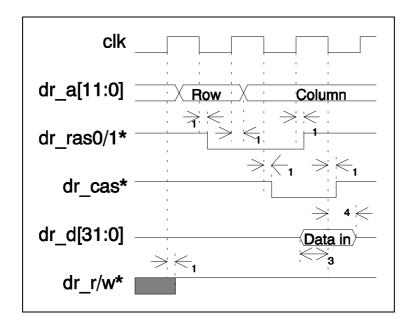

| Figure 15-5: Timing diagram write cell of the DRAM                  | 51 |

| Figure 15-6: Microprocessor DRAM write access                       | 52 |

| Figure 15-7: Microprocessor DRAM read access                        | 52 |

| Figure 18-1: SHAP3 package top view                                 | 54 |

| Figure 18-2: Mechanical drawing                                     | 55 |

Page 4 of 55 Nov-96

## 1 General description

The idea of traffic shaping in ATM is well known. However there are numerous ways to perform traffic shaping. This document describes how traffic shaping is done by the ATecoM SHAP3 device.

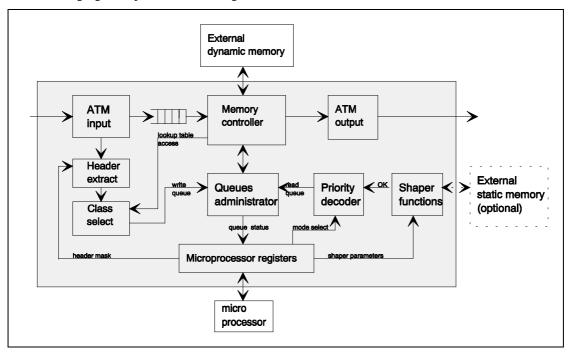

The following figure depicts the block diagram of the SHAP3:

Figure 1-1: Block diagram of the SHAP3

The SHAP3 is a device which allows an incoming ATM cell stream to be output with a pre-defined rate. To do so the cell stream is split into 32 traffic classes. For each class the following parameters can be set:

- Peak Cell Rate output (PCR)

- Sustainable Cell Rate output (SCR)

- Maximum Burst size at PCR output (MBS)

- CLP bit handling

- Amount of memory used by the class

- Priority within the classes

The output rate is controlled according to one of two Shaper functions both based on the Leaky Bucket algorithm namely the Single Leaky Bucket and the Dual Leaky Bucket.

The SHAP3 operates using a number of classes. Up to 16 bits of the arriving cell header are extracted and presented to a lookup table in the main memory. From the table is extracted the class to which the cell belongs. The cells of each class are stored in a queue which is also held in the external memory.

Nov-96 Page 5 of 55

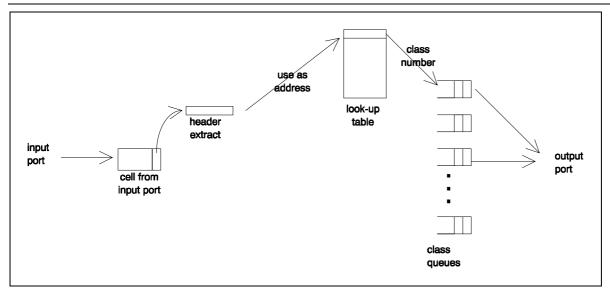

Figure 1-2: Class selection

Arriving cells are stored until the queue is full. If a queue is full and more cells arrive they are discarded. A counter keeps track of the number of discarded cells. Each class has a Shaper function assigned to it. The Shaper function determines when a cell is allowed to leave the queue. However the system has several queues thus it can happen that multiple Shaper functions signal that a cell should be output. If multiple request to output a cell are made, a priority function decides which request is honoured. The device supports static priorities as well as round robin priorities.

To support flow control the device allows the rate at which data is output to be changed under hardware or software control (see chapter 8 Class Rate Adaptation).

Beside shaping an ATM stream passing through the device, it is also possible to start or terminate a stream at the device. This allows the SHAP3 to be used as Traffic enerator, Traffic analyser or low speed AAL0.

## 2 ATM ports

The SHAP3 support the SAI- and the Utopia interface. The input port is decoupled from the rest of the chip through a four cell FIFO. Cells will first be completely stored in the FIFO before they are handled by the device. The output of the SHAP3 can be stopped in which case new arriving cells are stored in the queues. The SHAP3 can work with a 53 or 56 byte cell stream. In the 56 byte mode the first 3 bytes may be used for a routing tag. It is also possible to convert 56 byte cells to 53 byte cells.

# 2.1 Input port

The input port of the SHAP3 has the following properties:

- can work on a continuous or discontinuous cell stream

- can be enabled or disabled

- · can check or ignore an incoming HEC

- can pass or remove incoming idle cells

- can work on 53 or 56 byte cells

- can insert a three byte time stamp at the end of the cell when running in 53 byte cell mode

- can convert from 56 to 53 byte cell format

Bit 0 of the *IOC register* enables or disables the input port.

- If bit 0 of the *IOC register* is cleared all incoming cells are discarded.

- If bit 0 of the *IOC register* is set the input port is enabled.

The input port of the device is decoupled through a four cell FIFO. The FIFO is used for clock de-coupling only and not for rate adaptation.

Page 6 of 55 Nov-96

## 2.1.1 Cell alignment

In ATM two different cell streams are possible:

- systems where a continuous cell stream is present and all space between cells containing valid data is filled with idle cells.

- systems with a discontinuous cell stream where the cell stream will contains gaps of arbitrary length.

The input port works correctly on both types of data streams. In all cases the start of a cell is marked with the so called cell sync signal which is active during the arrival of the first byte of a cell. As soon as the first byte has entered the device the following 52 (or 55) bytes are assumed to belong to the same cell and are stored accordingly. If during the loading of these 52 (or 55) bytes another cell sync arrives this signal is ignored. The event is registered in the *input status register* and can provide an interrupt, signalling that an early sync has been detected.

The input port can also notice if there is no cell sync immediately following the last loaded cell byte: Late Sync Detection. This is an error when a continuous cell stream should be present. This event can also be registered in the input status register and can also provide an interrupt signal. Systems working with a discontinuous cell stream should simply ignore this status bit.

If the RxEnb\* signal is deasserted this indicates to the device sending cells that it should stop sending data. If the input stream stops there will be no cell sync immediately following the last loaded cell byte. In that case the Late Sync Detection bit is also set.

## 2.1.2 Utopia input port signals

The Utopia interface is meant to couple devices together even if the devices have different operating speeds. The SHAP3 has the task to adapt the cell stream between two devices operating on different speeds. The input port of the SHAP3, although it can be connected to a Utopia port, behaves somewhat different to a normal Utopia interface. The system clock of the SHAP3 must be high enough for the device to receive the maximum data rate and store the incoming cells in the memory. The output rate is then determined by the dual Leaky Bucket shaper function.

At the input port there is no input signal for the Utopia CLAV signal. This is not needed as the SHAP3 accepts data at any time. The SHAP3 can receive cells as long as there is room in the input FIFO.

If the RxEnb\* signal is deasserted and the user ignores this signal and keeps transmitting cells towards the SHAP3 the cells are still processed. That is the SHAP3 will correctly receive the cells and store them in a queue. Cells are lost on two conditions:

- 1. If the input FIFO overflows

- 2. If the queue to store the arriving cell is full

#### The four cell input FIFO gets full

If the input FIFO gets full the SHAP3 can be programmed to deasserted the RxEnb\* signal. However this can happen only if the device can not read the cells fast enough from the FIFO. This is normally a <u>system design error</u> as the system clock must be fast enough for the SHAP3 to read the cells from the FIFO and write the cells in the main memory.

#### The queue is full

This is an indication that the traffic is too bursty or the queue is too small. However in this case an error counter keeps track of the number of lost cells.

The RxEnb\* signal will be deasserted under two conditions:

- 1. If the TxClav is deasserted.

- 2. If the input FIFO gets full.

The RxEnb\* signal can be programmed for four different modes:

- If bit 3 of the *IOC register* is cleared the RxEnb\* signal is asserted at the end of a cell only.

- If bit 3 of the *IOC register* is set the RxEnb\* signal is asserted directly.

- If bit 7 of the *IOC register* is cleared the RxEnb\* signal is asserted when the TxClav signal is deasserted.

- If bit 7 of the *IOC register* is set the RxEnb\* signal is asserted if the TxClav signal is deasserted and the input FIFO is full.

#### 2.1.3 Idle cells

The input port can remove incoming idle cells or pass them on. If idle cell detection is switched on, the device checks whether an incoming cell has an idle cell header (first four bytes) or not. Idle cells are discarded and are not passed through the device. If idle cell detection is switched off all cells are handled by the device.

Bit 2 of the IOC register controls the storage of idle cells.

- If bit 2 of the *IOC register* is cleared idle cells are treated as normal data cells.

- If bit 2 of the *IOC register* is set idle cells are removed from the data stream.

#### 2.1.4 HEC check

The input port can check the cell HEC field and discard the cell if an HEC error occurs. It is not possible to correct the HEC field. This HEC check option can be disabled, allowing the HEC position to contain arbitrary data.

Bit 1 of the IOC register controls the check of the cell header.

- If bit 1 of the *IOC register* is cleared the HEC byte is ignored.

- If bit 1 of the *IOC register* is set the HEC is checked against the HEC-byte. If a HEC error occurs the cell is discarded.

#### 2.1.5 Cell format

The input controller supports three different cell formats:

- 53 byte cells

- 53 byte cells with 3 leading tag bytes

- 56 byte cells

It can also perform cell format conversion from 56 to 53 bytes. In this mode the first three octets of each cell are removed and the system clock must fulfil the following condition:

$$systemclk \ge \frac{53 \text{ bytes}}{56 \text{ bytes}} \bullet RxClk$$

Bits 5 and 6 of the *IOC register* control the type of cells coming into the device:

| IOC [6:5] | Input cell type        | Write to RAM                |

|-----------|------------------------|-----------------------------|

| 00        | 53 bytes               | 53 byte + 24 bit time stamp |

| 01        | 53 bytes + 3 tag bytes | 53 byte + 24 bit time stamp |

| 10        | 56 bytes               | 56 bytes                    |

| 11        | 53 bytes + 3 tag bytes | 53 bytes + 3 tag bytes      |

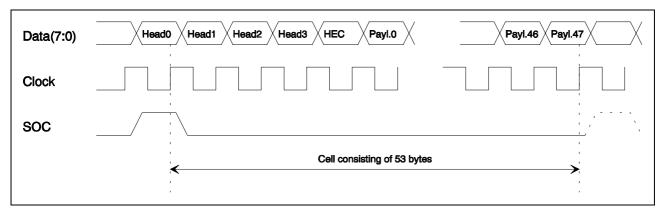

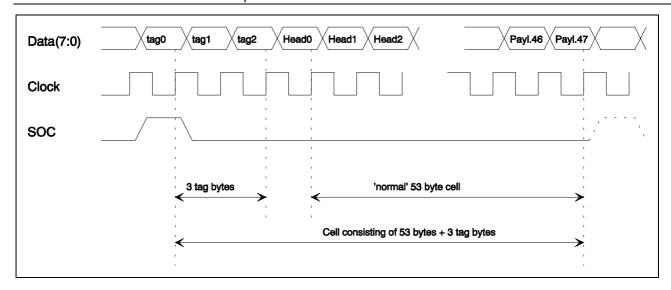

The three different cell formats are shown below:

Figure 2-1: 53 Byte cell format

Page 8 of 55 Nov-96

Figure 2-2: 53 Byte + 3 routing tag bytes cell format

Figure 2-3: 56 Byte cell format

The difference between a 56-byte cell and a 53+3 tag bytes cell is the location of the header in the cell stream. This is important as the SHAP3 uses the information in the header to assign cells to a certain queue.

## 2.1.6 Time stamp

As described above the controller can write a 24 bit time stamp indicating the arrival time of the cell in the memory. For this time stamp two different resolutions are available:

- If bit 4 of the *IOC register* is cleared the time stamp counter is incremented each RxClk.

- If bit 4 of the *IOC register* is set the time stamp counter is incremented once every 53 or every 56 RxClk cycles depending on the selected input cell format.

An increment every RxClk provides the best accuracy. However the time stamp counter will roll over after some time. Before this happens a cell must have arrived. Thus the minimum distance between cells must be  $2^{24}$  clock cycles. This is about one cell every second.

An increment every cell time allows a longer period of non-arriving cells: 53 or 56 seconds.

#### 2.1.7 Input status

The device has a register that reflects the status of the input port. The following events can be noticed:

- Early cell sync

- Late cell sync

- Missing RxClk

- Discarded cell counter rollover

Nov-96 Page 9 of 55

- FIFO level high

- FIFO overflow

Early cell sync and late cell sync have been explained in chapter 2.1.1 Cell alignment.

#### Missing RxClk

The incoming RxClk is checked against the system clock. If the incoming RxClk is not present for 32 system clock cycles the missing RxClk bit will be set.

#### Discarded cell counter overflow

Each queue has a counter counting the number of discarded cells. This counter can be programmed to stay at it's maximum value or roll over and set a status bit. There is only a single status bit for all counters.

#### FIFO level high

A FIFO level high occurs when more than two cells are in the input FIFO. The reason may be that the input cellrate is higher than the output cellrate.

#### FIFO overflow

A FIFO overflow occurs when the input data rate is higher than the output data rate. The device will discard all arriving cells when the FIFO is full and sets the FIFO full bit. The device has a four cell FIFO which is under normal conditions large enough to handle clock variations and flow control between input and output. Although the device is not meant for rate decoupling it can be used as such under certain conditions. It can always perform rate decoupling from a low rate towards a high rate. If the input port removes incoming idle cells and the rate of incoming data cells is sufficient low some rate decoupling from high to low rate can be performed.

Cells discarded due to a FIFO overflow are not counted in the class discarded cell counters.

#### Clearing of status bits

The input status bits will remain set until cleared by a write from the microprocessor. Clearing a status bit is done by writing a "1" to the corresponding position in the *input status register*. This "1" is not stored. It is only used to clear the status bit. Each *input status register* has a related *interrupt control register*. When a bit in the *interrupt control register* is set the corresponding bit in the *input status register* will cause an interrupt to occur.

## 2.2 Output port

The output port is 8 bits wide. As with the input port, the output port can work in continuous or discontinuous mode. The output port has no separate cell-clock signal, instead the system clock can be used as the cell-clock signal.

#### 2.2.1 Utopia output port signals

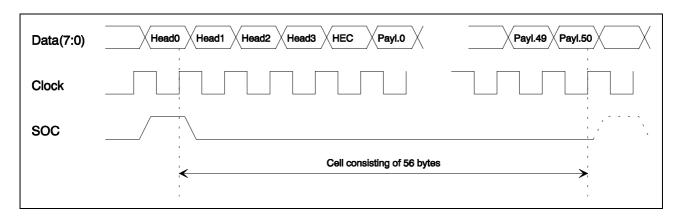

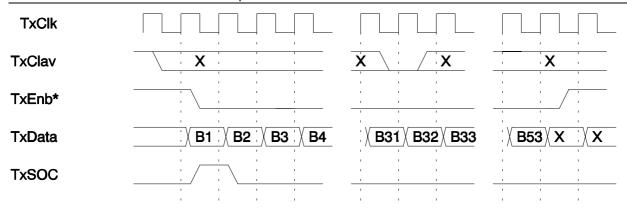

The TxSOC signal is active during the first octet of a cell is present a the ATM output port. As long as the TxData bus holds valid data, the TxEnb\* signal is asserted (set to low).

The SHAP3 works on cell-slot basis. This means that the SHAP3 aligns all cells on a 53 (or 56) clock cycle intervals. In an interval either a valid cell will leave the SHAP3 or not. This also implies that if the output should stop sending data it can not be stopped for an arbitrary time interval but only for a complete cell time. The point at which the TxClav signal is sampled is during the rising clock edge of byte 31 of the cell. This is equal for a 53 and a 56 byte cell. Stopping the output means that the buckets inside the SHAP3 will continue to leak. Thus it can happen that after the output is enabled again the SHAP3 will produce a burst of cells.

Page 10 of 55 Nov-96

<sup>&</sup>lt;sup>1</sup>For real rate decoupling much larger FIFOs are needed.

Figure 2-4: Stopping cell output for 53 byte cells

Figure 2-5: Stopping cell output for 56 Byte cells

### 2.2.2 Idle cell production

In continuous mode the output generates idle cells if no cell is allowed to leave the SHAP3 or all the queues are empty. In discontinuous mode the device outputs no data if no cell is available. In that case there will be gaps between the cells. The gaps will always be 53 (or 56) bytes long as the SHAP3 works on cell slot basis. This means that the SHAP3 aligns all cells on 53 (or 56) system clock cycle intervals. In an interval either a cell will leave the SHAP3 or not.

Bit 0 of the COLB register controls the generation of idle cells.

- If bit 0 of the *COLB register* is cleared idle cells are not produced at the output and there will be gaps between cells if no data cell is output.

- If bit 0 of the COLB register is set an idle cell is generated at the output port if no data cell is output.

#### 2.2.3 Output cell format

The *output control register* determines the output cell format of the SHAP3.

Bit 1 of the *COLB register* controls the type of cells leaving the device:

- If bit 1 of the *COLB register* is cleared cells of 53 bytes leave the SHAP3.

- If bit 1 of the *COLB register* is set cells of 56 bytes leave the SHAP3.

This bit also influences the rate of the SHAP3 related to the system clock. The Leaky Bucket calculations are performed <u>once</u> <u>per cell time</u>. For an outgoing cell format of 53 bytes a cell time equals 53 system clock cycles. For an outgoing cell format of 56 bytes a cell time equals 56 system clock cycles. This bit should only be changed during initialisation of the SHAP3. **It is not allowed to change this bit while the cell stream is running**.

The cell type of the *IOC register* specifies the cell format stored in the memory. Bit 1 of the *COLB register* specifies the format of the outgoing cell. These two functions are completely independent although some combinations give strange results like:

• Input cell size is 56 bytes but output format is 53 bytes. In this case the last 3 bytes of a cell are lost.

Nov-96 Page 11 of 55

Input format is 53 bytes, output format is 56 bytes.

The cell will contain 3 extra bytes at the end that hold the 24 bit time stamp.

(Note that to operate in this mode the following condition must be fulfilled: systemclk ≥ <sup>56 bytes</sup>/<sub>53 bytes</sub> • RxCLk )

As the SHAP3 can work with two different cell sizes throughout this document the description 53 (or 56) is found. If the cell size programmed in the ATM output control register is 53 the system works in a cadence of 53 clock cycles. (Thus storing and reading a cell takes 53 clock cycles, a refresh is performed every nx53 clock cycles, a class increment or decrement can be performed once every 53 clock cycles, etc.). If the programmed cell size in the ATM output control register is 56 the system works in a cadence of 56 clock cycles.

Note that the input stage of the SHAP3 works on the RxClk and thus runs independent from the rest of the chip.

#### 2.2.4 Idle cell format

As the 56 byte cell is non-standard there is no idle cell format defined for such cell sizes. The SHAP3 provides two different cell formats for idle cells:

- If bit 2 of the *COLB register* is cleared an idle cell consists of 3 routing tag bytes all zero followed by a normal 53 byte idle cell pattern.

- If bit 2 of the COLB register is set an idle cell starts as a normal idle cell but with 51 bytes of idle cell payload.

If the cell size is 53 bytes (bit 1 of *COLB register* is cleared) bit 2 is don't care. Otherwise bit 2 specifies the 56 byte idle cell format.

#### 2.2.5 Circular mode

Circular mode is provided to use the SHAP3 as a continuous traffic generator device. The device supports beside the normal operation mode three circular modes. In normal mode cells are read from a queue as long as the queue holds data. This guarantees that the SHAP3 will not output any cells if the queue is empty.

In circular mode this protection is disabled for some, or all the queues. As a consequence the SHAP3 will output all cells from a queue and then start reading at the beginning again. In this mode the SHAP3 will transmit the complete queue contents over and over again. No other aspect of the SHAP3 is changed. Those queues which are not in circular mode function normally.

Bits 5 and 6 of the COLB register control the circular mode.

# 3 Shaping function

The shaper function determines the characteristic of the outgoing data stream. Two operation modes are available: Dual Leaky Bucket or single Leaky Bucket mode. The Leaky Bucket mode is determined by bit 7 of the *Leaky Bucket control register*. In dual Leaky Bucket mode each class has one dual Leaky Bucket parameter (if the external SRAM is used up to 32 dual Leaky Bucket parameter per class). In single Leaky Bucket mode each class has two single Leaky Bucket parameters (if the external SRAM is used up to 64 single Leaky Bucket parameter per class). This mode allows output control with two different single Leaky Bucket parameters without the need of the external parameter RAM.

In single Leaky Bucket the output rate is controlled with a single Leaky Bucket. This allows a user to set the Peak Cell Rate (PCR) and the Cell Delay Variation (CDV) of the outgoing cell stream.

In dual Leaky Bucket mode the output rate is controlled with two Leaky Buckets in parallel. A cell is output if both Leaky Buckets give their OK. This allows cells to be output at a specified Peak Cell rate, Sustainable Cell Rate, Maximum Burst Size at PCR and CDV. This gives a three stage rate control.

## 3.1 Rate parameters

The output rate is based on the system clock together with the cell size. The Leaky Bucket calculations are performed <u>once per cell time</u>. For a 53 byte outgoing cell size a cell time equals 53 system clock cycles. For a 56 byte outgoing cell size a cell time equals 56 system clock cycles.

#### Example 1:

- System clock = 19.44 MHz

- Cell size = 53 bytes

Page 12 of 55 Nov-96

Systemrate is 19.44 10<sup>6</sup> Hz/53 bytes = 366792 cells/sec (=155.52 Mbit/sec)

#### Example 2:

- System clock = 23 MHz

- Cell size = 53 bytes

Systemrate is  $23 \cdot 10^6 \text{ Hz/}53 \text{ bytes} = 433962 \text{ cells/sec} (=184 \text{ Mbit/sec})$

Based on that, the rate is further determined by the following parameters:

#### Limit:

The bucket limit together with the splash determines the maximum burst size that can be output (leak<<splash). The bucket limit value is 24 bits wide. As long as the level is below or equal to the limit a cell is allowed to leave the queue.

#### Splash:

This value together with the leak determines the output rate. The splash value is 8 bits wide. The splash is the amount added to the level for each cell that is leaving the queue. The splash is only added if a cell is actually leaving the queue. Not if a cell-request is made.

#### Leak:

The leak is the amount with which the level is decreased per cell time. The leak parameter is often taken to be 1 and therefore not explicitly mentioned in numerous descriptions of the Leaky Bucket algorithm. This value together with the splash determines the output rate. The leak value is stored in a coded 4 Bit format The table below shows how the leak rate is coded.

| Code | Leak rate | Code | Leak rate |

|------|-----------|------|-----------|

| 0x0  | 128       | 0x8  | 1/2       |

| 0x1  | 64        | 0x9  | 1/4       |

| 0x2  | 32        | 0xA  | 1/8       |

| 0x3  | 16        | 0xB  | 1/16      |

| 0x4  | 8         | 0xC  | 1/32      |

| 0x5  | 4         | 0xD  | 1/64      |

| 0x6  | 2         | 0xE  | 1/128     |

| 0x7  | 1         | 0xF  | 0         |

#### Level:

The level is changing depending on the cell flow and the other three parameters Limit, Splash and Leak. This value is 31 bits wide where 7 bits are fraction bits (because the minimum Leak is 1/128). The Level can be pre-set by the user when setting up a connection. This can be used to avoid that the first cells of this connection are output back to back (if CDV is allowed).

## 3.2 Special rates

#### 3.2.1 Full data stream

The SHAP3 can be programmed to pass all cells of a dedicated class. No shaping is performed. The Leaky Bucket parameter for that class would be:

**Bucket limit** = 0xFFFFFF

Splash = 0x0

Leak code = 0xF (no leaking)

Level = don't care

So the Level is always lower than or equal to the Limit. In dual Leaky Bucket mode both parameters should be programmed this way.

### 3.2.2 Stop data stream

The SHAP3 can be programmed to stop the data stream of a dedicated class. The Leaky Bucket parameter would be:

Bucket limit = 0x0Splash = 0x0

Leak code = 0xF (no leaking)

Level = 0xFFFFFF

So the Level is always higher than the Limit. In dual Leaky Bucket mode only one parameter need to be programmed this way

## 3.3 Single Leaky Bucket

#### 3.3.1 Rate control

The Peak Cell Rate (PCR) is set with the leak and splash parameters according to:

$$PCR = \frac{leak}{splash} \bullet systemrate$$

The splash is normally chosen in the range 128..255 because this gives the best accuracy. A rate change is then possible in steps of  $\frac{1}{128}$  (accuracy 0.78%) to  $\frac{1}{255}$  (accuracy 0.39%).

The minimum PCR can then be calculated from the minimum leak and maximum splash:

$$\frac{1}{128} \bullet \frac{1}{255} = \frac{1}{32640} \,.$$

With a linkrate of 155 Mbits/sec this gives a minimum rate of 4.8 Kbits/sec. It is also possible to select a splash from a different range e.g. 64..127 or 32..63. The accuracy is then 1.56% or 3.12%. Several accuracy values are available between 0.78% and 50%

For example: With an accuracy  $\leq 3.12\%$  we have the following parameters:

- Minimum rate 38 Kbit/sec

- Maximum rate 155 Mbit/sec

- Maximum number of consecutive cells: 256K

The maximum number of consecutive cells is determined by:

At all rates a number of 64K consecutive cells can be obtained. If the limit is set to zero the number of consecutive cells is one. In this case the SHAP3 tries to output all cells equidistant (spacer<sup>2</sup>). It is still possible that due to a higher priority class, cells will leave the SHAP3 not equidistant. This is not the case for class zero in absolute priority mode as there is no class with a higher priority.

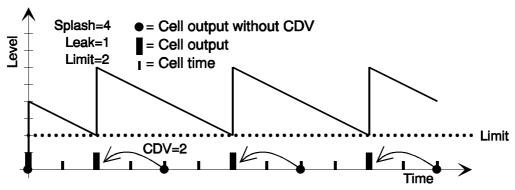

The CDV generated by the Leaky Bucket is determined by:

$$\mathbf{CDV} = \left| \frac{\mathbf{limit}}{\mathbf{leak}} \right| [celltime] \Rightarrow \mathbf{leak} \bullet \mathbf{CDV} \leq \mathbf{limit} < (\mathbf{leak} + 1) \bullet \mathbf{CDV}$$

The CDV is defined to be a positive integer in celltime units.

Note that CDV and the maximum number of consecutive can not be set independently.

The minimum CDV is zero (limit = 0). The maximum CDV depends on the leak rate and the limit. From the formula it can be seen that the largest CDV is reached with low leak rates or a high limit.

If the leak rate and the CDV are given the necessary limit can be calculated by the formula:

$$limit = \lceil leak - 1 \rceil + \lceil leak \bullet CDV \rceil$$

Page 14 of 55 Nov-96

<sup>&</sup>lt;sup>2</sup>Note that a cell shaper is more powerful than a spacer.

The single Leaky Bucket controls PCR and CDV. The Leaky Bucket implementation of ATecoM outputs a cell from the SHAP3 if the level is below or equal to the limit. Thus if the limit is set to zero cells are still allowed to leave the SHAP3.

## 3.3.2 Examples

With a limit set to zero the CDV is zero (See formulas above). Thus all cells will leave the SHAP3 equidistant. Figure 3-1 shows how the level changes as function of the parameters with a limit of zero.

Figure 3-1: Single Leaky Bucket with CDV of zero cell times

With a limit of three we get a CDV of three cell times (two consecutive cells). Figure 3-2 shows this case.

Figure 3-2: Single Leaky Bucket with a CDV of three cell times

If we have Leak=1, Splash=4, Limit=2 we get a CDV of two cell times and a number of consecutive cells of one (Figure 3-3).

Figure 3-3: Single Leaky Bucket with a CDV of two cell times

Consecutive cells could be sent only if the level is dropped far enough below the limit to allow one or more cells. This happens if no cells are output for some time.

There are three cases when no cell is output although the shaper function requests one:

1. There are no more cells in the queue.

Nov-96 Page 15 of 55

- 2. Cells are output from another class.

- 3. The output from the SHAP3 is halted (TxClav signal is low).

The first case happens if the queue is empty, which can only happen if no new cells arrive for the class. Thus an output burst will appear if several cells arrive at the input of the class after a period of rest. The second case can happen at all times except for the class with the highest priority. The third case depends on the hardware configuration in which the device is used. Figure 3-4 shows a typical figure of the SHAP3 output when a large burst of cells arrive. At the moment the burst arrives the bucket level is zero. This is the case if the class has been enabled recently or the queue has been empty for some time.

Figure 3-4: Typical level behaviour

The level is far below the limit thus a large bursts of cells is output while the level rises to the limit. When the limit has been reached the PCR of 1:4 is active unless one of the three cases described above occurs. If no cells are sent for some period the level drops as the bucket is leaking continuously. When cells can be output again, a burst of cells is sent until the limit has been reached again. The setting of a certain CDV can also be used to output a more regular cell flow when more than one class is active. In chapter 4.2 (Queue output conflicts) an example is given.

In case of large CDV values generated by the single Leaky Bucket algorithm a lot of cells are output consecutively. The disadvantage is that all these cells are output with the full link rate. This is often intolerable.

## 3.4 Dual Leaky Bucket

With a single Leaky Bucket the Peak Cell Rate (PCR) and the CDV can be controlled. However the Maximum Burst Size (MBS) at PCR and the Sustainable Cell Rate can not be controlled. To control all four parameters a dual Leaky Bucket shaper is needed.

#### 3.4.1 Rate control

The Peak Cell Rate (PCR) is set with the leak2 and splash2 (of Leaky Bucket2) parameters according to:

$$PCR = \frac{leak2}{splash2} \bullet systemrate$$

The Sustainable Cell Rate (SCR) is set with the **leak1** and **splash1** (of Leaky Bucket1) parameters according to:

$$SCR = \frac{leak1}{splash1} \bullet systemrate$$

The splash is normally chosen in the range 128..255 because this gives the best accuracy. A rate change is then possible in steps of  $\frac{1}{128}$  (accuracy 0.78%) to  $\frac{1}{255}$  (accuracy 0.39%).

The minimum PCR and SCR can then be calculated from the minimum leak and maximum splash:

$$\frac{1}{128} \bullet \frac{1}{255} = \frac{1}{32640} \,.$$

With a linkrate of 155 Mbits/sec this gives a minimum rate of 4.7Kbits/sec.

The Maximum Burst Size (MBS) at PCR cells is determined by:

Page 16 of 55 Nov-96

$$MBS = \frac{limit1}{splash1 - \frac{splash2}{leak2} \bullet leak1} + 1$$

The CDV generated by the Leaky Bucket is determined by:

$$\mathbf{CDV} = \left| \frac{\mathbf{limit2}}{\mathbf{leak2}} \right| [celltime] \Rightarrow \mathbf{leak2} \bullet \mathbf{CDV} \leq \mathbf{limit2} < (\mathbf{leak2} + 1) \bullet \mathbf{CDV}$$

The CDV is defined to be a positive integer in celltime units.

The minimum CDV is zero (limit = 0). The maximum CDV depends on the leak2 rate and the limit2. From the formula it can be seen that the largest CDV is reached with low leak2 rates or a high limit2.

If the leak rate and the CDV are given the necessary limit2 can be calculated by the formula:

$$limit2 = \lceil leak2 - 1 \rceil + \lceil leak2 \cdot CDV \rceil$$

Setting a CDV results in a maximum number of consecutive cells:

$$\label{eq:maximum number of consecutive cells} \begin{aligned} & = \frac{limit2}{splash2 - leak2} + 1 \approx \frac{limit2}{splash2} + 1 & \left( leak2 << splash2 \right) \end{aligned}$$

Note that CDV and the maximum number of consecutive can not be set independently.

The dual Leaky Bucket mode is specially used to control the MBS at PCR. As discussed above the burst from a single Leaky Bucket consists of consecutive cells. Thus the data is sent at the full link rate. In most cases this is not tolerable. To allow not only control of the PCR, but also of the MBS at PCR and the SCR, a second Leaky Bucket is used.

#### 3.4.2 Examples

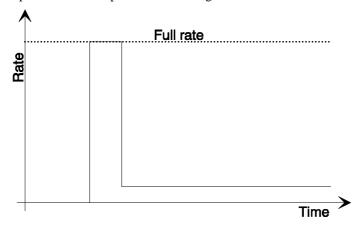

Assume Leaky bucket one has Splash1 = 10, Leak1 = 1, Limit1 = 9000. Thus it allows cells output at 1/10 of the link rate and outputs 1001 consecutive cells if possible. The output is shown in Figure 3-5.

Figure 3-5: Single Leaky Bucket with burst

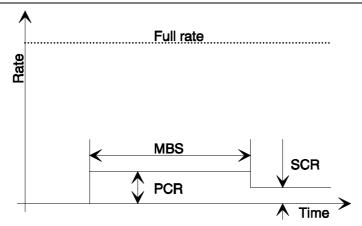

Assume Leaky bucket two has Splash2 = 5, leak2 = 1, Limit2 = 0. Thus it allows cells output at 1/5 of the link rate and has a CDV of zero. The dual Leaky Bucket function outputs a cell only if **both** Leaky Buckets say that it is OK. Under normal operating conditions bucket one will control the Sustainable Cell Rate (SCR) and Bucket two the Peak Cell Rate (PCR). However if the level of bucket one is zero it allows the output of 1001 consecutive cells. This is blocked by bucket two which allows a maximum rate of 1/5 of the link rate (PCR = 1/5). Thus instead of 1001 consecutive cells, the SHAP3 will output 1801 cells at a fifth of the link rate (MBS = 1801) and then output all other cells at a tenth of the link rate (SCR = 1/10). This is shown in Figure 3-6.

Nov-96 Page 17 of 55

Figure 3-6: Dual Leaky Bucket without CDV

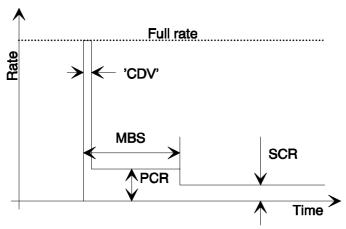

An even more complicated output function can be built by allowing a certain CDV. In such a case the SHAP3 will output number of consecutive cells at the full link rate, then go down for (MBS - number of consecutive cells) at a fifth of the link rate (PCR) and finally settle at a tenth of the link rate (SCR). This gives an output flow in three stages from which the height of stage two and three can be controlled. This is shown in the following figure:

Figure 3-7: Dual Leaky Bucket with CDV

# 3.5 Cell Delay Variation

When setting the shaper parameters a user should keep in mind that the network can change the distance between cells. This is called the cell delay variation (CDV). Thus even if the SHAP3 outputs all the cells with equal distance, it is not guaranteed that they also keep this distance throughout the network. Especially if the cells arrive at the UPC in the network cells can be removed because the 'logic' between the SHAP3 and the UPC block in the network has changed the inter-cell distance.

# 4 Multiple classes

# 4.1 Priorities setting

It is possible that multiple classes perform a request to output a cell. As the SHAP3 has only a single output port a decision must be made about which class is allowed to sent a cell. The priority decoder is needed to perform such arbitration. The SHAP3 allows a mixture of two types of priorities: Static priority and Round Robin priority.

## 4.1.1 Static priority

Using Static priority gives a known behaviour of the SHAP3 towards cell-requests. The class with the lowest number has the highest priority. Thus class zero has priority over class one which has priority over class two etc. Normally at least two classes

Page 18 of 55 Nov-96

are working in static priority because time-critical cells (For example from AAL1 type traffic) must be transported over the network with minimal delay.

## 4.1.2 Round Robin priority

In Round Robin priority the classes are polled one after the other if a cell-request is pending. If this is the case the selected class is allowed to send the cell. The next time the requests are started with the class following the one just served. After reaching class 31 class 0 is polled again. This mechanism allows multiple classes equal access to the output port.

Of course the polling of the 32 classes is all done in one cell time.

#### 4.1.3 Mixed priorities

The following priority schemes are possible:

- All static Class 0 has highest priority. Class 31 has lowest priority.

- All round robin

All classes have equal priority and are serviced on a round-robin basis.

- The classes 0..X have static priority, all other classes X..31 are round robin, but classes 0..X have priority over classes X..31.

| Priority code | Static | Round-Robin |

|---------------|--------|-------------|

| 0             | -      | 031         |

| 1             | 01     | 231         |

| 2             | 03     | 431         |

| 3             | 05     | 631         |

| 4             | 07     | 831         |

| 5             | 09     | 1031        |

| 6             | 011    | 1231        |

| 7             | 013    | 1431        |

| 8             | 015    | 1631        |

| 9             | 017    | 1831        |

| 10            | 019    | 2031        |

| 11            | 021    | 2231        |

| 12            | 023    | 2431        |

| 13            | 025    | 2631        |

| 14            | 027    | 2831        |

| 15            | 029    | 3031        |

| 16            | 031    | -           |

## 4.2 Queue output conflicts

The SHAP3 is normally used with more than one active class. As described above the classes will influence each other when cells should be output. If no measurements are taken some nasty side-effects can occur. Below we give an example of two classes where one is heavily distorted by the other.

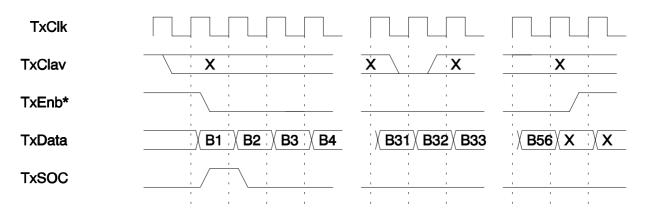

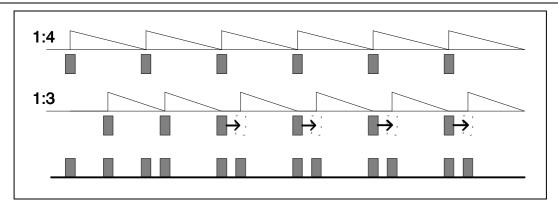

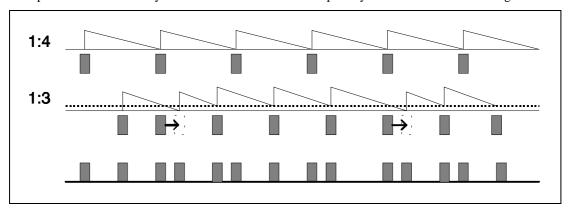

We have one class sending cells at a ratio 1:4 (One cell in 4 time frames), CDV 0 which has a high priority and a second class sending cells at a ratio 1:3, CDV 0 with a lower priority. At some moment both want to output a cell at the same time however only one of them is allowed to do so. As the one with ratio 1:4 has the highest priority the other has to wait for one cell time. The result is shown in Figure 4-1.

Nov-96 Page 19 of 55

Figure 4-1: Cell output without CDV

Once a collision occurs the class with the lowest priority must wait before a cell can be output. In Figure 4-1 this is indicated with an arrow showing that the cell was shifted for one time slot. From this moment on every cell gives a collision as the ratio 1:3 with a time delay of one cell (due to the higher priority of the 1:4 class) also gives a ratio of 1:4. The net effect is that the lower priority class is sending at a ratio of 1:4 instead of 1:3. If the round-robin priority mechanism is used it gives the same result and does not help here.

A solution to the problem is to set a very small CDV of one for the low priority class. This is shown in Figure 4-2.

Figure 4-2: Cell output with CDV of one

Here the Leaky Bucket has a kind of 'memory' when a collision occurs and the cell had to be output with a small delay. Therefore the next cell is output a cellslot earlier (CDV of one).

#### 5 Class data

Each class has a number of configuration and status values stored in three internal RAMs (Queue control RAM, Leaky Bucket parameter RAM and Leaky Bucket level RAM). The internal RAMs can not be accessed directly by the microprocessor. To write to these RAMs the microprocessor must first write the *all purpose data register* with the data and set the number of the class to write to. Then it must give a command to transfer this *all purpose data register* to the specified internal RAM. The opposite is valid for reading the class data. The microprocessor must first specify which class should be read and then give a command to transfer the RAM data to the *all purpose data register*.

All configuration data in all three RAMs should be initialised after reset!

#### 5.1 Queue control RAM

#### 5.1.1 Queue base address

The base address determines where the queue starts in the main memory. The start position is in **blocks** from the memory begin. One block holds 4096 words of 32 bits and can store upto 288 cells. The register is 13 bits wide. The first words in the main memory are used for the class look-up table. This table can be as small as 1 byte or as big as 64K bytes. Even if a single

Page 20 of 55 Nov-96

byte is used this byte may not be overwritten by data. So at least one block must be reserved for the look-up table. The minimum queue start value is then 1. For a look-up table of 64K blocks 0..3 are used and the first free block is number 4.

Note

A cell containing 53 or 56 bytes is stored in 14 words each 32 bits wide. One block of 4096 words can hold:

$$\frac{4096}{14}$$

= 292 cells

However a complete cell is stored and read-back in page mode<sup>3</sup>. As a consequence we can not utilise the memory for the full 100% and thus only 288 cells are stored in a space which **could** hold 292 cells. This gives an efficiency of almost 99%.

#### 5.1.2 Queue size

The 21 bit wide queue size value determines the size of the queue in cells. This allows classes holding a maximum of 2M cells to be defined. Although the start addresses of the queues are 288 cells apart, the queue-size parameter allows smaller queues to be defined. As this is a loss of memory utilisation a minimum queue size of 288 cells is proposed.

The minimum queue size is 2 cells. Setting a smaller queue size will result in unpredictable behaviour of the SHAP3.

#### 5.1.3 CLP-level

The value of the CLP level is compared with the queue level. If the queue level is <u>above</u> the CLP level incoming cells with the CLP bit set can be discarded if CLP discard is enabled.

To enable the CLP discard feature the CLP-cell discard enable bit in the *DRC register* must be set. Bit 7 of the *DRC register* controls the type of cells leaving the device:

- If bit 7 of the *DRC register* is cleared all cells are treated equal.

- If bit 7 of the *DRC register* is set cells with incoming CLP = 1 are discarded if queue level>CLP level.

If this bit is set the SHAP3 looks at the queue level for each incoming cell with the CLP bit set (CLP = 1). If the CLP bit is set AND the queue level is higher than the CLP level the cell will not be stored in the queue.

By setting the CLP-level equal to or larger than the queue size the CLP level becomes inactive. The CLP-level value is 21 bits wide.

The discarded cell counter can be programmed to count these discarded cells as lost or ignore these discarded cells. See also the next chapter.

#### 5.1.4 Discarded cells counter

The discarded cell counter counts how many cells were discarded for a queue. If the maximum value has been reached it this value can be hold or it can set the interrupt bit and start counting from zero again.

- If bit 5 of the *all purpose data register* 1 is cleared when initialising the queue control RAM the counter counts to the maximum value and stays there.

- If bit 5 of the *all purpose data register* 1 is set when initialising the queue control RAM the counter rolls over when reaching the maximum value and sets a status bit.

The counter can also be programmed to count the discarded cells with CLP = 1.

- If bit 6 of the *all purpose data register* 1 is cleared it is also incremented when a cell arrives which has the CLP bit set and the queue level is above the CLP level.

- If bit 6 of the *all purpose data register* 1 is set when initialising the queue control RAM it is only incremented when the queue is full (queue overflow).

When cells are discarded due to an erroneous HEC or a FIFO full status, the counter is not incremented. The cell counter can not be written independent of the rest of the queue data. Thus it is not possible to reset the counters.

#### 5.1.5 Queue level

<sup>&</sup>lt;sup>3</sup>Page mode is a special means of operation of a dynamic RAM. It means a single RAS cycle followed by multiple CAS cycles. In page mode all CAS addresses must remain in a single RAS page. For more details see the data sheet of a dynamic RAM which can work in page mode.

This value can only be read. It shows how many cells are stored for that class. The queue level value is 21 bits wide and is automatically updated when a parameter set is read from the on chip queue control RAM.

#### 5.1.6 Queue status bits

There are three status bits for each queue, the empty, full and CLP level status bit. These bits are automatically updated when a parameter is read from the on chip queue control RAM. The high-level status bit is set if the queue level is larger than the CLP-level.

### 5.1.7 Read/Write queue control RAM

The queue base address, queue size, CLP level, discarded cells counter, read pointer, write pointer and the three configuration bits (*all purpose data register* 1 bit 5 .. 7) are stored in the queue control RAM. It is not possible to access the queue control RAM directly from the microprocessor. Instead the *all purpose data register* is used for intermediate data storage. Under all conditions it is possible to address the queue control RAM.

#### 5.1.7.1 Write queue control RAM

To write to the queue control RAM first the *all purpose data register* 0..16 must be written. It is important that the read pointer, write pointer and bit 7 of the *all purpose data register* 1 used by the queue control algorithm are cleared when setting up a queue control entry. Then the *class select register* must be set with the number of the class to write to. Finally the command *transfer to queue control RAM* (code 0x03) must be written to the *transfer control register*. The SHAP3 will then update the queue control RAM in such a way that it does not interfere with the normal operations. Bit 7 of the *transfer control register* shows the status of the transfer:

- If bit 7 of the *transfer control register* is cleared the transfer is still pending. No new data may be written to the *all purpose data register* while a transfer is pending.

- If bit 7 of the *transfer control register* is set the transfer is ready.

## 5.1.7.2 Read queue control RAM

To read the data from the queue control RAM the first task of the microprocessor is to set the *class select register* with the number of the class to read. The command *transfer from queue control RAM* (code 0x02) must be written to the *transfer control register*. The SHAP3 will then read the queue control RAM data and transfer it to the *all purpose data register*. Bit 7 of the *transfer control register* shows the status of the transfer:

- If bit 7 of the *transfer control register* is cleared the transfer is still pending. The data in the *all purpose data register* is not yet valid

- If bit 7 of the transfer control register is set the transfer is ready. The data in the all purpose data register is valid

Only after the transfer is completed the microprocessor reads the values from the all purpose data register.

# 5.2 Read/Write Shaping settings

The shaping settings are stored in two RAMs:

- The Leaky Bucket parameter RAM

- The Leaky Bucket level RAM

Both RAMs can be set independently. It is allowed to change the Leaky Bucket settings while the SHAP3 is active.

All shaping parameters for all classes whether they are used or not should be initialised after reset! If a class is not used the related shaping parameters should be set to not OK (see chapter 3.2.2 Stop data stream)

#### 5.2.1 Write parameter or level RAM

To write to the RAM the *all purpose data register* must be written first. For the parameters it is the register 0-9, for the level it is the register 0-7. Then the *class select register* must be set with the number of the class to write to. Finally the command *transfer to parameter RAM* (code 0x05) or *transfer to level RAM* (code 0x15) must be written to the *transfer control register*. The SHAP3 will then update the corresponding RAM in such a way that it does not interfere with the normal operations. Bit 7 of the *transfer control register* shows the status of the transfer:

Page 22 of 55 Nov-96

- If bit 7 of the *transfer control register* is cleared the transfer is still pending. No new data may be written to the *all purpose data register* while a transfer is pending.

- If bit 7 of the *transfer control register* is set the transfer is ready.

## 5.2.2 Read parameter or level RAM

To read the data from the Leaky Bucket parameter or level RAM the first task of the microprocessor is to set the *class select register* with the number of the class to read. The command *transfer from parameter RAM* (code 0x04) or the command *transfer from level RAM* (code 0x14) must be written to the *transfer control register*. The SHAP3 will then read the corresponding RAM data and transfer it to the *all purpose data register*. Bit 7 of the *transfer control register* shows the status of the transfer:

- If bit 7 of the *transfer control register* is cleared the transfer is still pending. The data in the *all purpose data register* is not yet valid.

- If bit 7 of the *transfer control register* is set the transfer is ready. The data in the *all purpose data register* is valid.

Only after the transfer is complete the microprocessor can read the values from the all purpose data register.

#### 5.2.3 Read/write static RAM

#### 5.2.3.1 Read/write parameter set

When reading parameter sets from or writing to the external static RAM the procedure is almost the same as described above.

Two differences are to be observed:

- 1. Besides the *class select register* also the *parameter set control register* must be set with the parameter set number.

- 2. The transfer codes (was 0x05 & 0x04) should be 0x07 and 0x06.

Bit 7 of the *parameter set control register* must be set. Otherwise not the parameter sets but the pointer to the parameter set is accessed.

## 5.2.3.2 Read/write parameter set pointer

When reading the parameter set pointer from or writing to the external static RAM the procedure is almost the same as described in chapter 5.2.3.1 Read/write parameter set.

- 1. Select a class using the class select register.

- 2. Write the parameter set pointer value to the all purpose data register 9 (only necessary when writing).

- 3. Clear bit 7 of the *parameter set control register*.

- 4. The transfer codes should be 0x07 (for writing) and 0x06 (for reading).

After finishing the read transfer the *all purpose data register 9* holds the parameter set pointer value.

# 6 CLP bit handling

The device can handle cells with and without CLP bit set differently. This is done by setting an CLP-level for a class and setting the CLP-discard bit in the *DRC register*. As soon as the queue level is beyond the CLP-level all arriving cells which have the CLP bit set are removed. The counter mode determines if these cells are also counted as discarded cells. The SHAP3 is not capable to remove cells with the CLP bit set that are already stored in the queue.

The CLP bit handling can be disabled for a certain class by filling the CLP-level with a value equal to or larger than the queue size. A general CLP enable bit must be set in order to handle cells with incoming CLP-bit set specially.

Bit 7 of the *DRC register* is a global CLP-cell discard enable/disable bit.

- If bit 7 of the *DRC register* is set the CLP level compare for all classes is enabled

- If bit 7 of the *DRC register* is cleared the CLP level compare for all classes is disabled

Nov-96 Page 23 of 55

## 7 Class assignment

Arriving cells are processed on basis of the cell header to assign them to a class. To do this the SHAP3 uses a class lookup table with maximum 64K entries. From each arriving cell up to 16 bits are taken from the header (See *header mask register*). The value of these bits is taken as address in the lookup table. From the lookup table a byte is read. The LS 5 bits of this byte specify the class number where the cell should be written to.

The class lookup table is stored in the external dynamic memory. The size of the class look-up table depends on the number of bits set in the *header mask register*. The maximum number of bits set is 16. For 16 bits the SHAP3 can address  $2^{16}$ =64K entries. Thus the look-up table must be 64K bytes large (4 blocks each 16K bytes). If less then 16 bits are set the logic will force all non-used bits to zero. As a result the MS address bits will always be zero and thus the lookup table can be smaller. The table below gives the size of the look-up table in bytes and SHAP3 memory blocks against the number of header extraction bits.

| Header extr. bits | Table size | Blocks | First free Block |  |

|-------------------|------------|--------|------------------|--|

| 16                | 16 64K     |        | 4                |  |

| 15                | 32K        | 2      | 2                |  |

| 14                | 14 16K     |        | 1                |  |

| 13                | 8K         | 1      | 1                |  |

| 12-0              | 4K         | 1      | 1                |  |

Even for the smallest header extraction value (0 bits) you need at least 1 block. Thus below 14 header extraction bits there is no more gain for memory.

Note that if you set the header extaction mask to all zero's the result will always be zero. In that case only a single byte in the memory (address 0) will be used. Thus all cells go into the queue specified at address 0 of the lookup table.

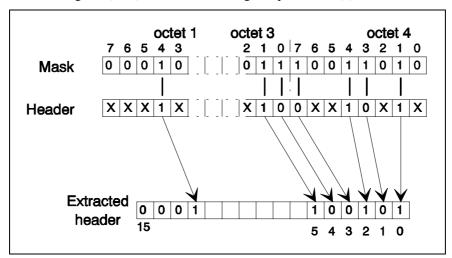

#### 7.1 Header mask

The header mask is used to extract up to 16 bits of the first four octets of a cell. The extracted bits are presented to the class lookup table. The header bits are selected using the four byte *header mask register*. Each bit set in a register will cause the corresponding header bit to be used for selecting a class. If less than 16 bits are set in the mask, the remaining extracted bits are set to zero. If more than 16 bits are set only the last 16 bits are used. *Header mask register* 0 selects bits from octet 1, register 1 from octet 2, etc. The LS bit of a register (bit 0) selects data arriving at input RxData(0).

Figure 7-1: Header extraction mask

## 7.2 Lookup table

The size of the lookup table can vary between 1 byte and 64Kbytes. As the memory of the SHAP3 is allocated in blocks of 4096 words, the smallest lookup table requires 1 block of 4K words the largest requires 4 blocks of 4K words. The memory connected to the SHAP3 should be large enough to hold the lookup table and still have enough storage left to store the cells from the classes.

Page 24 of 55 Nov-96

The maximum extracted header value of 16 bits is only present in excessive circumstances. In most cases the extracted header value will be smaller and thus less memory is needed for the lookup table. However if the complete 16 bits are essential the SHAP3 only requires enough DRAM to fulfil the demands.

If less than 15 bits are used only a single block is required to hold the complete lookup table. Note that if no header extraction bits are set the extraction logic always produces the value 0. Thus the first byte in the memory is used to determine to which class the cell belongs. However as the memory is allocated in blocks, 1 block (4K words) is the minimum lookup table size which is always required.

The SHAP3 can transfer data to and from the class lookup table. The microprocessor has no direct access towards the table. Even if a link is fully loaded (no gaps or idle cells) it is possible to access the lookup table. The lookup table is in the dynamic RAM and each word is 32 bits wide. As for a class we need only 5 bits (as we have only 32 classes) one word holds 4 entries: the LS 5 bits of each byte. Therefore a read or write access will always read/write 4 consecutive table entries.

#### Unused classes should not have an entry in the lookup table.

As the size of the lookup table is variable the number of address bits used to access the lookup table is also variable. The number of address bits equals the number of bit set in the *header mask register* minus 2. Setting a wrong address during a read or write access will cause the SHAP3 to read or write at the wrong place in the memory. When writing data this can cause the SHAP3 to output damaged cells.

To update the lookup table the device has two registers:

#### Class lookup table address

This value is the address to access. It is 32 bits wide (all purpose data register 4 .. 7) where only the least X significant bits should be used. X equals the number of bit set in the header mask register minus 2. The most significant bits should be cleared for lookup table access.

#### Class lookup table data

This value is the data to be read/written (all purpose data register 0 .. 3). From each byte the LS 5 bits are used to indicate one of the 32 queues. Byte 0 of word 0 corresponds with an extracted header value of 0x0000. The second byte of the first word with extracted header value of 0x0001, etc.

To write towards the lookup table, the four class entries (*all purpose data register* 0-3) and the destination address (*all purpose data register* 4-7) are written into the SHAP3. A write transfer will start after writing 0x01 to the *transfer control register*. To read from the lookup table, the source address is written into the SHAP3 (*all purpose data register* 4-7). A read transfer will start after writing 0x00 to the *transfer control register*. The SHAP3 will load the data from the table into it's registers. In both cases the transfer ready bit must be observed to prevent errors.

With a 19.44MHz clock a transfer will take maximum 5.4 µsec (53 byte cell format).

## 7.3 General memory access

In the previous chapter we concentrated on reading from or writing to the lookup table. Therefore we restricted the number of address bits which should be set.

However more than the LS 14 address bits of the class *lookup table address register* can be used. This will only cause the SHAP3 to access a different memory location.

The same holds for the data registers. For the lookup table all 32 bits can be set but only the LS 5 bits are used. For a general memory access all the 32 bits are valid.

The commands to read or write the memory are the same. General memory access can be used to perform a memory check on the DRAM or to access the DRAM in a random way. It is only dangerous to do so when the SHAP3 is operating as it may inadvertently destroy data stored in the memory.

# **8 Class Rate Adaptation**

Often the rate at which data is sent must be changed. This is what we call rate adaptation, which means that the output rate parameters for the Leaky Bucket function can be changed during runtime either under software or under hardware control. This function is available in two forms:

- With external static RAM 32 rates are available per class per Leaky Bucket.

- Without external static RAM 2 rates are available per class if working in single <u>Leaky Bucket</u> mode.

# 8.1 Leaky Bucket select register

When working in single Leaky Bucket mode (controlled by bit 7 of the *Leaky Bucket control register*) the SHAP3 still has two single Leaky Bucket parameters per class available. This register determines for each class whether single Leaky Bucket one or two is used.

#### 8.2 Parameter set select

One parameter set consists of either one dual Leaky Bucket parameter in dual Leaky Bucket mode or two single Leaky Bucket parameters in single Leaky Bucket mode. As mentioned rate adaptation allows a user to choose one of 32 available output rates per class. The output rate is stored in an external static RAM as 32 <u>Leaky Bucket</u> parameter sets for each of the 32 classes. Therefore total 1024 parameter sets are stored in the external static RAM. Only one parameter set can be active for a class. Selecting a parameter set can be done under software or hardware control. For each class a 5 bit parameter set pointer is also stored in the external static RAM which points to the active parameter set. Hence 32 pointers are stored. This pointer indicates the number of the active parameter set.

#### For example:

To select parameter set 5 the value of the pointer should be set to 0x5.

All parameter sets and all pointers in the external static RAM can be changed under CPU control (see chapter 5.2 Read/Write Shaping settings). For each class the actual parameters are stored in the parameter RAM of the SHAP3. The transfer of parameters from the external RAM to the internal RAM can be performed in two ways:

- If bit 4 of the *cell out control register* is cleared the new parameter set can be loaded under hardware control.

- If bit 4 of the *cell out control register* is set the new parameter set can be loaded software controlled.

Two operations are possible to change the active parameter set: **increment** and **decrement** commands can be used to change the pointer value.

The increment always chooses the next higher rate. For the decrement four different decrement modes are available:

- Decrement by 1

- Decrement by 25%

- Decrement by 50%

- Decrement by 75%

The decrement rate is programmed with bits 5 and 6 of the *parameter set control register*:

| Bits [6:5] | Decrement by |

|------------|--------------|

| 00         | 1            |

| 01         | 25%          |

| 10         | 50%          |

| 11         | 75%          |

If the lowest/highest parameter set is selected the decrement/increment command has no effect. The conversion from the various decrement modes are shown in the conversion table below.

The conversion of the **old** parameter set pointer to the **new** parameter set pointer depends on the decrement **mode bits [6:5]** in the *parameter set control register*. The mode bits 6 & 5 are shown below the "New" text:

Page 26 of 55 Nov-96

| Old | New<br>00 | New<br>01 | New<br>10 | New<br>11 | Old | New<br>00 | New<br>01 | New<br>10 | New<br>11 |

|-----|-----------|-----------|-----------|-----------|-----|-----------|-----------|-----------|-----------|

| 0   | 0         | 0         | 0         | 0         | 16  | 15        | 12        | 8         | 4         |

| 1   | 0         | 0         | 0         | 0         | 17  | 16        | 13        | 8         | 4         |

| 2   | 1         | 1         | 1         | 0         | 18  | 17        | 14        | 9         | 4         |

| 3   | 2         | 2         | 1         | 0         | 19  | 18        | 15        | 9         | 4         |

| 4   | 3         | 3         | 2         | 1         | 20  | 19        | 15        | 10        | 5         |

| 5   | 4         | 4         | 2         | 1         | 21  | 20        | 16        | 10        | 5         |

| 6   | 5         | 5         | 3         | 1         | 22  | 21        | 17        | 11        | 5         |

| 7   | 6         | 6         | 3         | 1         | 23  | 22        | 18        | 11        | 5         |

| 8   | 7         | 6         | 4         | 2         | 24  | 23        | 18        | 12        | 6         |

| 9   | 8         | 7         | 4         | 2         | 25  | 24        | 19        | 12        | 6         |

| 10  | 9         | 8         | 5         | 2         | 26  | 25        | 20        | 13        | 6         |

| 11  | 10        | 9         | 5         | 2         | 27  | 26        | 21        | 13        | 6         |

| 12  | 11        | 9         | 6         | 3         | 28  | 27        | 21        | 14        | 7         |

| 13  | 12        | 10        | 6         | 3         | 29  | 28        | 23        | 14        | 7         |

| 14  | 13        | 11        | 7         | 3         | 30  | 29        | 23        | 15        | 7         |

| 15  | 14        | 12        | 7         | 3         | 31  | 30        | 24        | 15        | 7         |

The new value of the parameter set pointer is used to select the new parameter set in the external static RAM. The SHAP3 transfers this new parameter set from the external to the internal RAM. If the highest/lowest class is active further increment/decrement requests are ignored.

#### 8.3 Software rate control

To control the output rate under software there are two possibilities:

- Write new parameters to the internal RAM.

- Transfer parameters from the external static ram to the internal parameter RAM using the increment or decrement command.

The first method is described above and although it allows an arbitrary rate to be set it also requires that the microprocessor sets all the registers and transfers the registers to the parameter RAM.

To transfer parameters from the external static RAM to the internal parameter RAM the increment and decrement commands can be performed under software control. Bit 4 of the *cell out control register* must be set for software control. To increment/decrement the pointer three microprocessor write actions must be performed:

- 1. Write the class number in the *class select register*, the inc/dec bits must be zero.

- 2. Write the class number plus the increment/decrement bit in the *class select register*. The parameter set pointer of the class is incremented/decremented. The new value of the parameter set pointer is used to select the new parameter set in the external static RAM. The SHAP3 transfers this parameter set from external to the on chip parameter RAM.

- 3. Write the class number in the *class select register* and set the inc/dec bits zero again.

It is also possible to set a new pointer value for the parameters under software control. However this command sets only the pointer but does **not** load a new parameter set. An increment or decrement request is always handled in one cell time (53 or 56 cycles). The next increment or decrement command must be at least 53 (or 56) clock cycles after the first pulse. If the next command is less than 53 (or 56) clock cycles after the first one, this additional command may be accepted or not, depending on the internal state of the state machine.

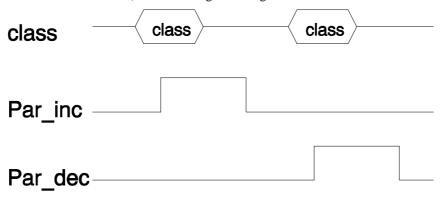

#### 8.4 Hardware rate control

To control the output rate using external hardware control the SHAP3 has seven input signals:

#### class [4:0]:

5 bits wide to select one of the 32 classes.

#### Par\_inc:

The rising edge of this signal stores the selected class and increments the parameter set pointer of this class. The new value of the parameter set pointer is used to select the new parameter set in the external static RAM. The SHAP3 transfers this parameter set from external to the on chip parameter RAM.

#### Par\_dec:

The rising edge of this signal stores the selected class and decrements the parameter set pointer of this class, depending on one of the above decrement formulas. The new value of the parameter set pointer is used to select the new parameter set in the external static RAM. The SHAP3 transfers this parameter set from external to the on chip parameter RAM.

With this method it is not possible to directly select one of the 32 available rates. Instead of this the next higher or a lower rate (depending on the selected decrement formula!) is chosen<sup>4</sup> Signal timing:

Figure 8-1: Par\_inc, Par\_dec signal timing

When an PAR\_inc or PAR\_dec pulse arrives this event is stored together with the class number until the chip can execute this command. An increment or decrement request is always handled in one cell time (53 or 56 cycles). The next PAR\_inc or PAR\_dec pulse must be at least 53 (or 56) clock cycles after the first pulse. If the next pulse is less than 53 (or 56) clock cycles after the first one this additional pulse may be accepted or not depending on the internal state of the state machine.

#### 8.5 Parameter curves

Because of the increment-decrement signals the parameter sets in the table should be ordered in rising or falling output rate. However how fast rising or falling is up to the user. Some possible configurations are:

<sup>&</sup>lt;sup>4</sup>Assuming the rates are stored from low rate to high rate.

Page 28 of 55 Nov-96

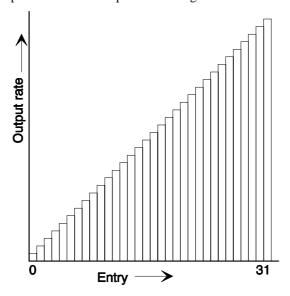

Figure 8-2: Linear rate change

The linear rate change is the most likely to be used. It will cause the SHAP3 to go up or down in a regular way.

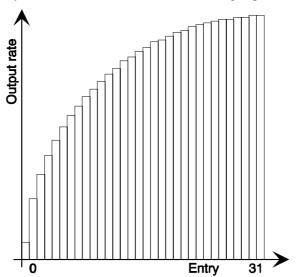

Figure 8-3: Logarithmic rate change

The logarithmic rising range allows a rate increment and decrement to have small change at higher rates and a big change at low rates.

The complement from this function: *logarithmic falling* is not shown here but the reader can easily imagine what it looks like. It allows a rate increment and decrement to have large changes at higher rates and a small change at low rates.

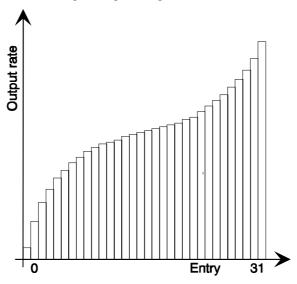

Figure 8-4: Pi-Curve rate change

The PI-curve allows changes in the middle to have lilt effect and at the low and high ends to have more impact.

An alternative to this is the S-curve which is not shown here. It causes changes in the middle of the curve to have a large impact and increments/decrements at the extreme ends to give only little changes.

It is also possible to fill all entries with the same data effectively rendering the parameter change inoperable.

#### 8.5.1 Asymmetric change (ABR)

Thus far we handled the increment and decrement equal. As mentioned above the SHAP3 has four modes in which a decrement can occur:

Nov-96 Page 29 of 55

- Decrement by one.

- Decrement by 25%

- Decrement by 50%

- Decrement by 75%