# S1R72805

# IEEE1394 Link/Transaction USB1.1 Controller

## DESCRIPTION

S1R72805 has the built-in Link/Transaction and USB1.1 Controller conforming to IEEE Std. 1394-1995, P1394a Draft 2.0 and enables to bridge either of both Interface and IDE. If a CPU/Flash ROM is provided to this IC and part of the transaction is made as Hardware and if the address and the sized of Page Table in SBP-2 are set to this IC, This IC will come to automatically following Page Table Fetch and transmit data. When this IC is assembled with a Cable PHY Transceiver/Arbiter conforming to the same standard, this IC will provide with an 1394/USB interface optimum to computer peripheral devices.

The IDE Interface is suitable to Ultra DMA mode5 (ATA100) and realizes high-speed transfer rates.

# **■ FEATURES**

#### «Built-in CPU»

• 32bit RISC CPU S1C33. Operation at 25MHz (CPU cycle operation with minimum 2τ)

Built-in SRAM : 8KB, No-wait operation

Built-in Flash ROM: 64KB, No-wait operation

Programmable timer : Built-in 3 channels

#### «IEEE1394 Interface»

Link/Transaction Controller

Link Layer

Suitable to all two-way data transfer in the Asynchronous and Isochronous modes. The built-in SRAM enables to realize stable two-way data transfers up to the MaxPayload in 100Mbps, 200Mbps or 400Mbps. This enables the Hardware to automatically detect the Isochronous Resources Manager.

## Transaction Layer

Part of the transaction function was made Hardware in order to prevent the actual transfer rate with overhead from being reduced. Communications with upper layers can be simplified by distinguishing the header area from the data area. In addition, the data area can be subdivided into a Stream area and an ORB area. A ring buffer is adopted for the receive header area and the receive data area (receive ORB area). Sizes of respective areas can be set optionally. The Hardware controls Busy states at the time of receive automatically.

### SBP-2 Support

When the address and the size of Page Table are set to SBP-2, following Page Table Fetch and data can be transferred in the automatic mode.

#### PHY/LINK Interface

Conforming to P1394a. Suitable to the transfer rates of 100, 200, and 400Mbps. Suitable to Isolation (in case of built-in bus holder).

Built-in SRAM for data packets: 8KB

#### «USB Interface»

- Suitable to transfer in the full speed mode (12Mbps).

- Suitable to control transfer at the Endpoint 0 and to bulk, interrupt and Iso transfers at three individual Endpoints. For these three Endpoints, the following can be set individually: the IN/OUT direction, four types (8-, 16-, 32- and 64-byte) of maximum packet lengths, optional Endpoint number and single or double buffer size (for isochronous transfer, however, only single is available).

- The built-in SRAM (2KB) can be divided into programmable ones according to user definition.

#### «IDE Interface»

Suitable to PIO Modes 0, 1, 2, 3 and 4, to Multi Word DMA Modes 0, 1 and 2 and to Ultra-DMA Modes 0, 1, 2, 3, 4, and 5.

### «Others»

- 48MHz is input by the crystal oscillation for the USB.

- The built-in Flash ROM (64KB) is suitable to ICP (In Circuit Programming).

- QFP-100pin (0.5mm pitch)

- Supply voltage 3.3V±0.3V

- Radiation-resistant design has not been provided for this specification.

- This IC is a lead-free package.

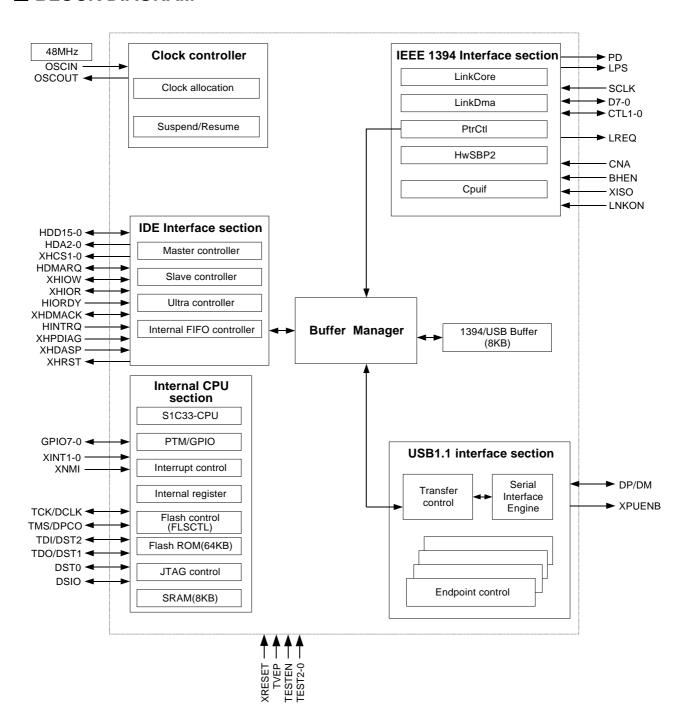

# **■ BLOCK DIAGRAM**

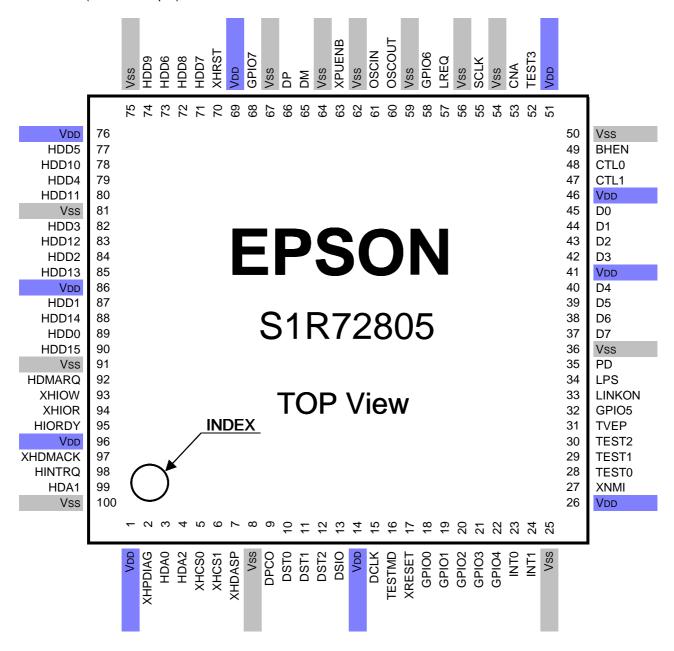

## **■ PIN ASSIGNMENT**

S1R72805 (QFP15-100pin)

# S1R72805

# **■ PIN DESCRIPTION**

Control signals with "X" prefixed to pin names are low active.

| Pin No.     | Signal      | I/O       | Reset     |                                                         | Remarks                    |

|-------------|-------------|-----------|-----------|---------------------------------------------------------|----------------------------|

|             | IEEE1394 P  | HY Inter  | face (18  |                                                         |                            |

| 37          | D7          |           |           | (MSB)                                                   | Drive capability 6mA       |

| 38          | D6          |           |           |                                                         | Schmitt input (bus holder) |

| 39          | D5          |           |           |                                                         | ,                          |

| 40          | D4          |           |           |                                                         |                            |

| 42          | D3          | Is/O      | HI-Z      | Data bus with PHY                                       |                            |

| 43          | D2          |           |           |                                                         |                            |

| 44          | D1          |           |           |                                                         |                            |

| 45          | D0          |           |           | (LSB)                                                   |                            |

| 47          | CTL1        | Is/O      | HI-Z      | Control signal with PHY                                 | Drive capability 6mA       |

| 48          | CTL0        |           |           |                                                         | Schmitt input              |

|             |             |           |           |                                                         | (bus holder)               |

| 57          | LREQ        | 0         | LOW       | Request signal to PHY                                   | Drive capability 6mA       |

| 34          | LPS         | 0         |           | Link power status signal to PHY                         | Drive capability 6mA       |

| 33          | LINKON      | ls        | _         | Link on signal from PHY                                 | Schmitt input              |

|             |             |           |           |                                                         | (bus holder)               |

| 49          | BHEN        | ls        | _         | Bus holder enable signal. At the time of DC             | Schmitt input              |

|             |             |           |           | connection, set this to the LOW level. At the time of   |                            |

|             |             |           |           | single capacitor AC connection, set this to the HIGH    |                            |

|             |             |           |           | level.                                                  |                            |

| 53          | CNA         | Is        | _         | Cable Not Active                                        | Schmitt input (bus holder) |

| 35          | PD          | 0         | LOW       | Power Down Enable                                       | Drive capability 6mA       |

| 55          | SCLK        | Is        | LOW       | Clock signal (49.152MHz) from PHY                       | Schmitt input              |

|             | OOLK        | 13        |           | Olock signal (+3.1321/1112)   Hom 1 111                 | (bus holder)               |

| Relation to | USB1.1 Inte | rface (5) |           | <u> </u>                                                | (bus fielder)              |

| 65          | DM          | I/O       | HI-Z      | USB data port                                           | Conformance to USB         |

|             | D.W.        | ., 0      | ''' _     | oob data port                                           | standard                   |

| 66          | DP          | 1         |           | USB data port                                           |                            |

|             |             |           |           | Arrange the configuration so as to pull up to 3.3V with |                            |

|             |             |           |           | an external resistance of $1.5k\Omega$ .                |                            |

|             |             |           |           | A register control is possible by using the pin         |                            |

|             |             |           |           | "XPUENB."                                               |                            |

| 63          | XPUENB      | Ood       | HI-Z      | The pull-up resistance control pin EnpullUp bit of the  | Drive capability 6mA       |

|             |             |           |           | pin "DP" becomes LOW at the time of HIGH.               |                            |

| 61          | OSCIN       | I         | _         | Crystal oscillation input pin                           | 48.0MHz                    |

| 60          | OSCOUT      | 0         | _         | Clock output pin                                        | 48.0MHz                    |

|             | DE Interfac | e (29)    | All input | s are of 5V tolerance.                                  |                            |

| 90          | HDD15       | 4         |           | (MSB)                                                   |                            |

| 88          | HDD14       |           |           |                                                         |                            |

| 85          | HDD13       | 4         |           |                                                         |                            |

| 83          | HDD12       | 4         |           |                                                         |                            |

| 80          | HDD11       | 4         |           |                                                         |                            |

| 78          | HDD10       | 4         |           |                                                         |                            |

| 74          | HDD9        |           | l         | IDE LA L                                                |                            |

| 72          | HDD8        | I/O       | HI-Z      | IDE data bus                                            | Drive capability 2mA       |

| 71          | HDD7        | 4         |           |                                                         |                            |

| 73          | HDD6        | 4         |           |                                                         |                            |

| 77          | HDD5        | 4         |           |                                                         |                            |

| 79          | HDD4        | 4         |           |                                                         |                            |

| 82          | HDD3        | 4         |           |                                                         |                            |

| 84          | HDD2        | 4         |           |                                                         |                            |

| 87          | HDD1        | 4         |           | (LCD)                                                   |                            |

| 89          | HDD0        | la /0     | 111.7     | (LSB)                                                   | Duly a son a letter our A  |

| 92          | HDMARQ      | Is/O      | HI-Z      | IDE DMA Request Signal                                  | Drive capability 6mA       |

| 93          | XHIOW       | Is/O      |           | IDE Write Signal                                        | Drive capability 2mA       |

| 94          | XHIOR       | Is/O      | HI-Z      | IDE Read Signal                                         | Drive capability 2mA       |

| Pin No.         | Signal        | I/O      | Reset           | Functional description                                            | Remarks                               |

|-----------------|---------------|----------|-----------------|-------------------------------------------------------------------|---------------------------------------|

| 95              | HIORDY        | ls       |                 | IDE IORDY Signal                                                  | _                                     |

| 97              | XHDMACK       | Is/O     |                 | IDE DMA Acknowledge Signal                                        | Drive capability 2mA                  |

| 98              | HINTRQ        | Is       |                 | IDE Interrupt signal                                              | _                                     |

| 2               | XHPDIAG       | Is       | _               | IDE PDIAG Signal                                                  | _                                     |

| 7               | XHDASP        | Is       | _               | IDE DASP Signal                                                   | _                                     |

| 4               | HDA2          |          |                 | (MSB)                                                             |                                       |

| 99              | HDA1          | Otr      | HI-Z            | IDE Address Signal                                                | Drive capability 2mA                  |

| 3               | HDA0          |          |                 | (LSB)                                                             |                                       |

| 6               | XHCS1         | Otr      |                 | IDE Chip Select Signal                                            | Drive capability 2mA                  |

| 5               | XHCS0         | Otr      |                 | IDE Chip Select Signal                                            | Drive capability 2mA                  |

| 70              | XHRST         | Otr      | HI-Z            | IDE Reset Signal                                                  | Drive capability 2mA                  |

| CPU Macro       | o (4)         |          |                 |                                                                   |                                       |

| 17              | XRESET        | ls       | _               | Initial Reset Signal (It must be pulled up externally.)           | 5V tolerance,<br>Schmitt input        |

| 27              | XNMI          | ls       | _               | NMI Input signal (It must be pulled up externally.)               | 5V tolerance,<br>Schmitt input        |

| 23              | XINT0         | lpu      | <del> </del>    | External Input Interrupt Signal                                   | 5V tolerance                          |

| 24              | XINT1         | Ipu      | <del>    </del> | External Input Interrupt Signal                                   | 5V tolerance                          |

|                 | Interface (6) | ipu      | l               | - Morrial Impact Interrupt Orginal                                | o v tototatioo                        |

| 15              | TCK/DCLK      | lpu/O    | HI-Z            | ICD Interface                                                     | Drive capability 6mA,<br>5V tolerance |

| 9               | TDI/DPCO      | Ipu/O    | HI-Z            | ICD Interface                                                     | Drive capability 6mA,                 |

|                 | TDO/DOTO      | 1/0      | 1.014           | 100.1 / /                                                         | 5V tolerance                          |

| 12              | TDO/DST2      | I/O      |                 | ICD Interface                                                     | Drive capability 6mA, 5V tolerance    |

| 11              | DST1          | I/O      | HIGH            | ICD Interface                                                     | Drive capability 6mA,<br>5V tolerance |

| 10              | DST0          | I/O      | HIGH            | ICD Interface                                                     | Drive capability 6mA,<br>5V tolerance |

| 13              | TMS/DSIO      | lpu/O    | HI-Z            | ICD Interface                                                     | Drive capability 6mA,<br>5V tolerance |

| Others (4)      |               |          |                 |                                                                   | ov toloranos                          |

| 18              | GPIO0         |          |                 |                                                                   |                                       |

| 19              | GPIO1         |          |                 |                                                                   |                                       |

| 20              | GPIO2         |          |                 |                                                                   |                                       |

| 21              | GPIO3         | lpu/O    | HI-Z            | General-purpose I/O port                                          | Drive capability 2mA,                 |

| 22              | GPIO4         | ., , ,   |                 | Contral pulpode to port                                           | 5V tolerance                          |

| 32              | GPIO5         |          |                 |                                                                   |                                       |

| 58              | GPIO6         |          |                 |                                                                   |                                       |

| 68              | GPIO7         |          |                 |                                                                   |                                       |

| Others (5)      | J. 107        | I        | I               |                                                                   |                                       |

| 28              | TEST0         | ı        | _               | Test Mode Set Pin (Connect this pin to GND usually.)              | _                                     |

| 29              | TEST1         | İ        | _               |                                                                   | _                                     |

| 30              | TEST2         | İ        | _               |                                                                   | _                                     |

| 52              | TEST3         | İ        | _               | Test Mode Set Pin (Connect this pin to VDD usually.)              | _                                     |

| 16              | TESTMD        | lpd      | _               | I/O pin test control signal (Connect this pin to GND usually.)    | _                                     |

| 31              | TVEP          | _        | _               | Internal Flash ROM Test Signal (Connect this pin to VDD usually.) | _                                     |

| VDD:3.3V (      | 10)           | <u> </u> | 1               |                                                                   |                                       |

| 1,14,26,        | VDD           | _        |                 | Power supply                                                      | _                                     |

| 41,46,51,       |               |          |                 |                                                                   |                                       |

| 69,76,86,<br>96 |               |          |                 |                                                                   |                                       |

| Vss:0V (16      | 0V (16)       |          |                 |                                                                   |                                       |

| 8,14,25,        | Vss           | _        |                 | GND                                                               | _                                     |

| 36,50,54,       | v 33          |          |                 |                                                                   |                                       |

| 56,59,62,       |               |          |                 |                                                                   |                                       |

| 64,67,75,       |               |          |                 |                                                                   |                                       |

| 81,91,100       |               |          |                 |                                                                   |                                       |

| 51,51,100       | <u> </u>      |          |                 |                                                                   | l .                                   |

I : Input Is : Schmitt input Ipu : Pull-up input O : Output Ood : Open drain output Otr : Tristate output Ispu: Pull-up Schmitt input Ipd: Pull-down input Note:

# S1R72805

# **■ MEMORY MAP**

# **● Total Memory Space**

The memory map of this IC is shown in the figure blow. (For the built-in S1C33, 2-Clock is the minimum cycle.)

| Address              |                     | Area | Device Size | Wait                         | Cycle    |

|----------------------|---------------------|------|-------------|------------------------------|----------|

| 0xC0FFFF             | Flash ROM           | 64KB | 16bit       | 0Wait                        | 2Clock   |

| 0xC00000             |                     |      |             |                              |          |

|                      | Reserved            |      |             |                              |          |

| 0x05FFFF             |                     |      |             |                              |          |

| 0x030000             | S1C33-Mini Core Reg |      | 8/16bit     | 0Wait                        | 2Clock   |

|                      | Reserved            |      |             |                              |          |

| 0x011FFF             | 4004/1100 0 1/      | OLCD | 001.4       | 43.87 %                      | 4 01 1   |

| 0x010000             | 1394/USB Buffer     | 8KB  | 32bit       | 1Wait<br>+Ext.Wait           | 4+nClock |

| 0x002100             | Reserved            |      |             |                              |          |

| 0x0020FF<br>0x002000 | Internal Reg        | 256B | 8bit        | 0Wait<br>+Ext.Wait<br>Note 1 | 2+nClock |

| 0x001FFF             | IRAM                |      |             |                              |          |

| 0x000000             | (Work area)         | 8KB  | 32bit       | 0Wait                        | 2Clock   |

Note 1 : At the time of 0x20070-0x2007F or USB-FIFO access by USB Window Register, Ext Wait is input. In other cases, Wait is 0.

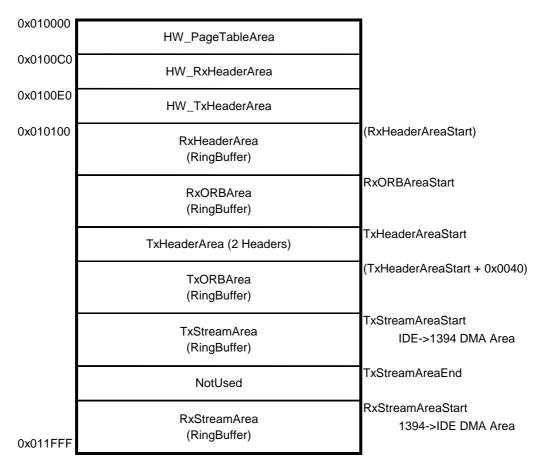

# Memory Map of 1394/USB Buffer Area

#### 8KB

### **TxHeaderArea**

(1) used Asyncronouse only

② used Isocronouse

| TxAreaStart | AsyTxPktHdr 0 |

|-------------|---------------|

| + 0x20      | AsyTxPktHdr 1 |

| + 0x40      |               |

| TxAreaStart | AsyTxPktHdr 0 |

|-------------|---------------|

| + 0x20      |               |

| + 0x30      | IsoTxPktHdr 1 |

| + 0x40      |               |

- Direct Addressing makes it possible to access all the RAM area from the CPU.

- For RxStreamArea and TxStreamArea. Hardware DMA is possible to IDE Interface.

- HW\_PageTableArea (for 24 pages), HW\_RxHeaderArea and HW\_TxHeaderArea respectively secure areas for a header as the Hardware areas. Firmware can independently use both the RxORB and TxORB areas.

- RxHeaderArea, RxORBArea, TxORB, TxStreamArea and RxStreamArea have become ring buffers and guarantee data among areas in the Hardware at the times of receiving 1394 and of executing IDE DMA. (The sizes of respective ring buffer areas can be changed if set by RxORBAreaStart, TxHeaderAreaStart, TxStreamAreaStart, TxStreamAreaEnd or RxStreamAreaStart in the internal register.)

- TxStreamArea and RxStreamArea can be overlapped and can be used as a single StreamArea.

- Post\*\*Ptr and Used\*\*Ptr of RxHeaderArea, RxORBArea, TxStreamArea or RxStreamArea monitor how each area is used. (Rx of 1394 monitors the both free capacities and controls busy\_A, B and X in the Hardware.)

- When the above functions are controlled from the TRANS & SBP2 control block, PageTable Fetch in SBP-2 and data transfer can be operated by the Hardware.

When USB is used in this area, only 2KB (0x011800-0x011FFF) in the latter half is secured for USB-FIFO and other areas can be used for general purposes in the firm but compete with USB operation at the time of access.

### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from anther government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

©Seiko Epson Corporation 2003, All rights reserved.

## **SEIKO EPSON CORPORATION**

ELECTRONIC DEVICES MARKETING DIVISION

IC Marketing & Engineering Group

**ED International Marketing Department** 421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN

Phone: 042-587-5814 FAX: 042-587-5117

■ EPSON Electronic devices Website http://www.epsondevice.com/

First issue July, 2002 Printed June, 2003 in Japan  $\widehat{(H)}$