#### 500MHz 75dB Logarithmic/Limiting Amplifier

Advance Information

Supersedes edition in Professional Products IC Handbook May 1991

DS3534 - 2.0 April 1994

The SL3522 is a monolithic seven stage successive detection logarithmic amplifier integrated circuit for use in the 100MHz to 500MHz frequency range. It features an on–chip video amplifier with provision for external adjustment of log Slope and offset. It also features a balanced RF output. The SL3522 operates from supplies of  $\pm 5$ V.

#### **FEATURES**

- 75dB Dynamic Range

- Surface Mount SO Package

- Adjustable Log Slope and Offset

- OdBm RF Limiting Output

- 60dBm Limiting Range

- 2V Video Output Range

- Low Power (Typ. 1W)

- Temperature Range (T<sub>CASE</sub>): -55°C to +125°C

#### **APPLICATIONS**

- Ultra Wideband Log Receivers

- Channelised and Monpulse Radar

- Instrumentation

#### **ABSOLUTE MAXIMUM RATINGS**

| BOOLOTE MAXIMOM KATINGS        |                 |

|--------------------------------|-----------------|

| Supply Voltage                 | ±6.0V           |

| Storage temperature            | -65°C to +175°C |

| Junction temperature           | +175°C          |

| Thermal resistance             |                 |

| Die-to-case                    | 15.5°C/W        |

| Die-to-ambient                 | 76.5°C/W        |

| Applied DC voltage to RF input | ±400mV          |

| Applied RF power to RF input   | +15dBm          |

|                                |                 |

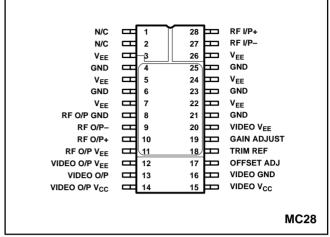

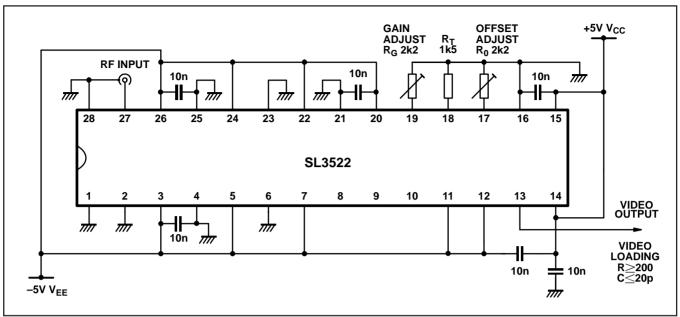

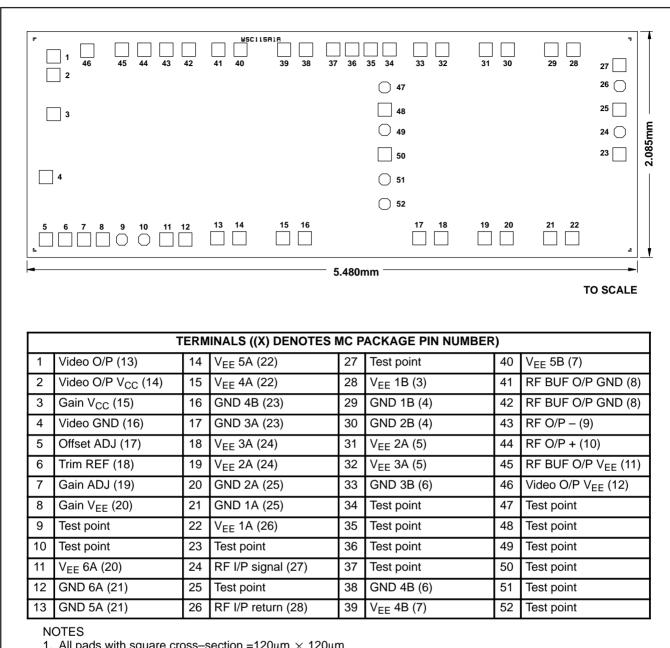

Fig.1 Pin connections - top view

#### **ORDERING INFORMATION**

SL3522 A MC (Miniature Ceramic package) SL3522 C MC (Miniature Ceramic package) SL3522 NA 1C (Probe-tested bare die)

(Also available: SL3522 AA MC screened to Zarlink HI-REL level A. Contact Zarlink Semiconductor sales outlet for a separate datasheet.)

#### **ESD PROTECTION**

To achieve the high frequency performance there are no ESD protection structures on the RF input pins (27, 28). These pins are **highly static sensitive**, typically measured as 250V using MIL-STD-883 method 3015. Therefore, ESD handling precautions are **essential** to avoid degradation of performance or permanent damage to this device.

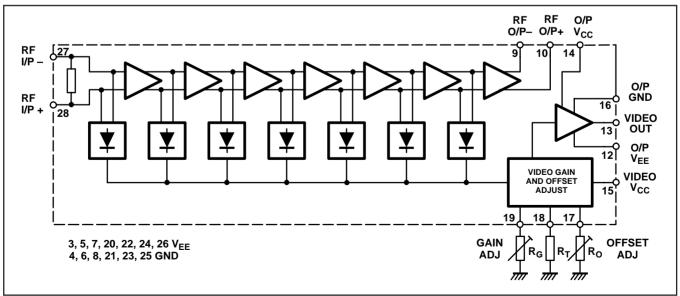

Fig.2 Functional block diagram

#### **ELECTRICAL CHARACTERISTICS**

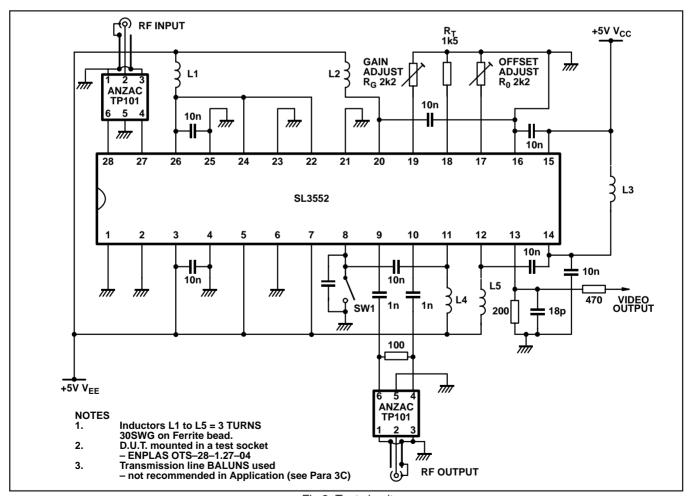

The electrical characteristics are guaranteed over the following range of operating conditions, using test circuit in Fig. 3 (unless otherwise stated):

Temperature range: Military: SL3522 A MC, SL3522 NA 1C 55°C to +125°C (T<sub>CASE</sub>)

Commercial: SL3522 C MC 0°C to +70°C (T<sub>CASE</sub>)

Supply voltage:  $V_{CC}$ : +4.50V to +5.50V (all grades)  $V_{EE}$ : -4.5V to -5.50V (all grades)

Frequency =100MHz to 500MHz

Rg, Ro, Rt =1.5K $\Omega$ Video output load =200 $\Omega$ //20pF

Test conditions (unless otherwise stated):

Temperature: SL3522 A MC: +25°C, +125°C & -55°C (T<sub>CASE</sub>)

SL3522 C MC: +25°C SL3522 NA 1C +25°C

Supply voltage:  $V_{CC} = +5.0V$ ,  $V_{EE} = -5.0V$

| Parameter                           | Pin                 |       | Value      |       | Units | Conditions                         |

|-------------------------------------|---------------------|-------|------------|-------|-------|------------------------------------|

| r ai ailletei                       | Min. Typ. Max.      |       | Conditions |       |       |                                    |

| Positive supply current (quiescent) | 14, 15              |       | 28         | 35    | mA    | V <sub>CC</sub> = +5.0V            |

| Negative supply current             | ALL V <sub>EE</sub> |       | 150        | 175   | mA    | V <sub>EE</sub> = -5.0V See note 1 |

| (quiescent)                         | Pins                |       | 180        | 210   | mA    | V <sub>EE</sub> = -5.0V See note 2 |

| Dynamic range                       |                     | 75    |            |       | dB    | 100 to 400MHz See note 1, 3        |

|                                     |                     | 70    |            |       | dB    | See note 1, 4                      |

| Linearity                           |                     | -1    |            | +1    | dB    | $T_{CASE} = -55^{\circ}C$          |

|                                     |                     | -1    |            | +1    | dB    | $T_{CASE} = +25^{\circ}C$          |

|                                     |                     | -1.25 |            | +1.25 | dB    | $T_{CASE} = +125^{\circ}C$         |

| Video output range                  | 13                  | 1.30  | 1.75       | 2.00  | V     |                                    |

| Video slope                         | 13                  | 18    | 21         | 24    | mV/dB |                                    |

| Video slope variation               | 13                  | -5    |            | +5    | %     | See note 5                         |

| Video slope adjust range            | 13                  | ±20   | ±30        |       | %     | $R_G = 1k\Omega$ to $2.2k\Omega$   |

| Video offset                        | 13                  | -0.1  | +0.25      | +0.5  | V     |                                    |

| Video offset variation              | 13                  |       | -05        |       | mV/°C | $T_{CASE} = +25^{\circ}C$          |

| Video offset adjust range           | 13                  | ±0.5  |            |       | V     | $R_O = 1k\Omega$ to $2.2k\Omega$   |

| Video trim reference                | 17, 18,             | -0.59 | -0.54      | -0.49 | V     |                                    |

| voltage                             | 19                  |       |            |       |       |                                    |

| Video output impedance              | 13                  |       | 10         |       | Ω     | See note 8                         |

| Video rise time                     | 13                  |       | 16         |       | ns    | 10% - 90% (60dB step)              |

|                                     |                     |       |            |       |       | See note 7                         |

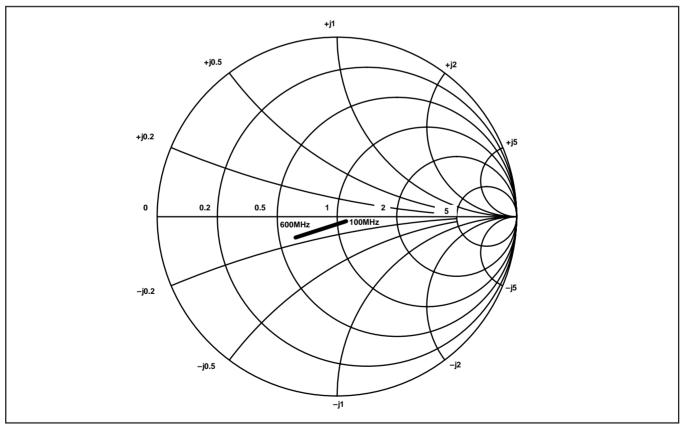

| Input VSWR                          | 27, 28              |       | 1.5:1      |       |       | $Zs = 50\Omega$ See note 7         |

| RF bandwidth                        | 9, 10               |       | 450        |       | MHz   | TCASE = +25°C RFIN = -70dBm        |

|                                     |                     |       |            |       |       | See notes 2, 7                     |

| RF limiting range                   | 9, 10               |       | 60         |       | dB    | See notes 2, 6, 7                  |

| RF limited output level             | 9, 10               | -3.0  | -1.0       | +1.0  | dBm   | $R1 = 50\Omega$ single ended       |

|                                     |                     |       |            |       |       | See note 2                         |

| RF output impedance                 | 9, 10               |       | 50         |       | Ω     | Single ended See notes 2, 8        |

#### **ELECTRICAL CHARACTERISTICS (cont.)**

| Parameter               | Parameter Pin Value Units |      | Units | Conditions |         |                                                |  |

|-------------------------|---------------------------|------|-------|------------|---------|------------------------------------------------|--|

| i arameter              |                           | Min. | Тур.  | Max.       |         | Schallons                                      |  |

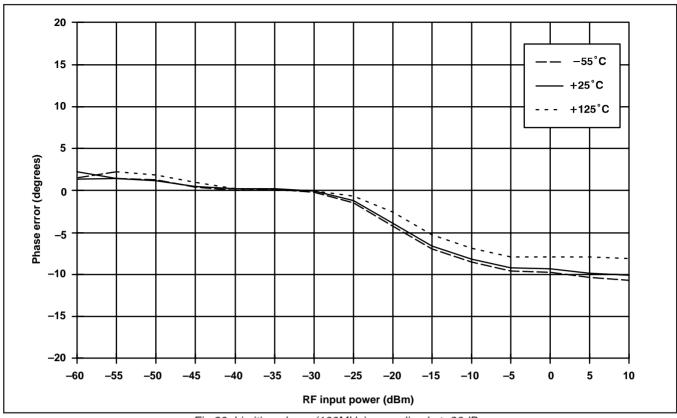

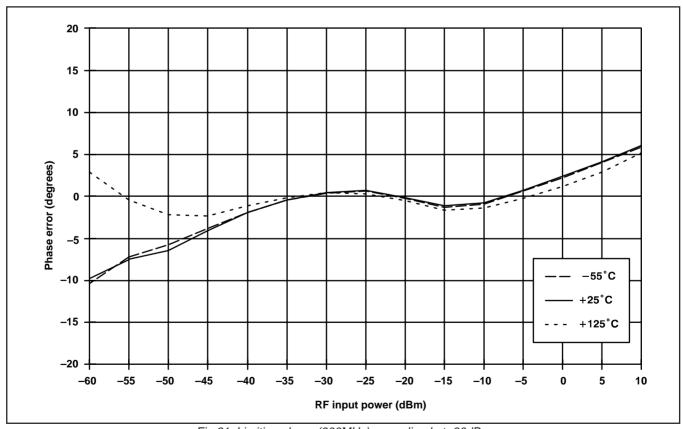

| Phase variation with RF |                           |      | 15    |            | Degrees | Freq = 300MHz RF <sub>IN</sub> = -60 to +10dBm |  |

| Input level             |                           |      |       |            |         | See notes 2, 7                                 |  |

| Phase tracking between  |                           |      | 3     |            | Degrees | T <sub>CASE</sub> = +25°C FREQ = 300MHz        |  |

| units                   |                           |      |       |            |         | See notes 2, 7                                 |  |

#### Notes

- 1 RF output buffer OFF (pin 8 disconnected from 0V)

- 2 RF output buffer ON (pin 8 connected to 0V)

- 3 Minimum dynamic range under any single set of operating conditions

- 4 Log linearity guaranteed for pin = -64dBm to +6dBm for ALL supply, temperature and frequency conditions

- 5 Full range of supply, temperature and frequency conditions

- 6 Input limiting range typically -50dBm to +10dBm

- 7 Not tested, but guaranteed by characterisation

- 8 Not tested, but guaranteed by design

The SL3522 CANNOT be GUARANTEED to operate below 100MHz and meet the electrical characteristics shown above. However, characterisation has shown that the device can still function adequately down to frequencies of 50MHz, with the following reservations:

- 1) The video bandwidth is fixed to approx 40MHz a certain amount of carrier breakthrough on the video O/P (pin 13) will occur, with input signal frequencies below 100MHz.

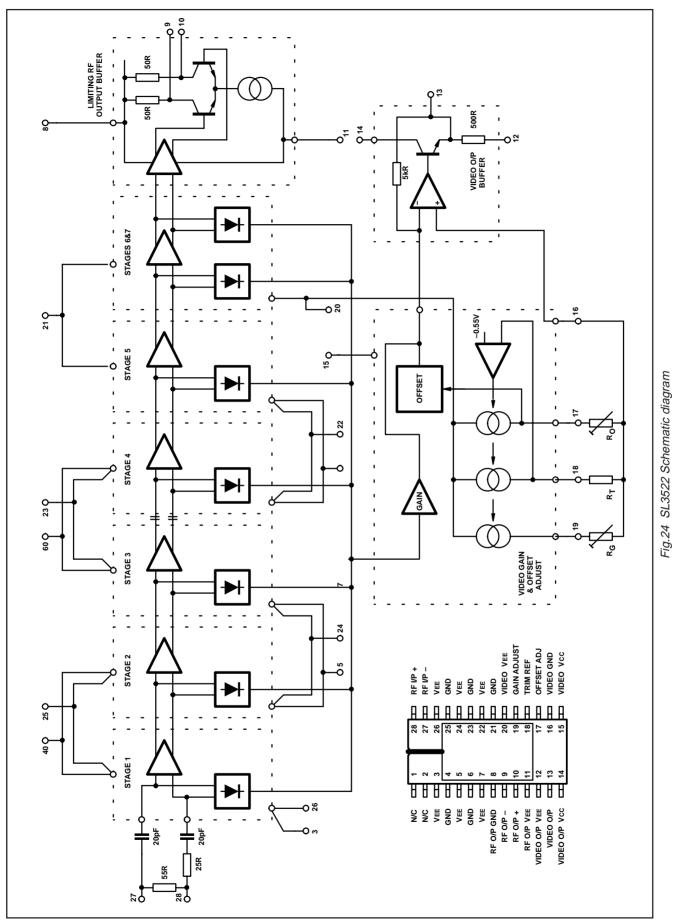

- 2) There are 2 RF coupling capacitors (20pF) on-chip, which couple the output signal from stage 3 to the input of stage 4 (ref Fig. 24). These can introduce undesirable limiting phase performance for input signal frequencies below 100MHz.

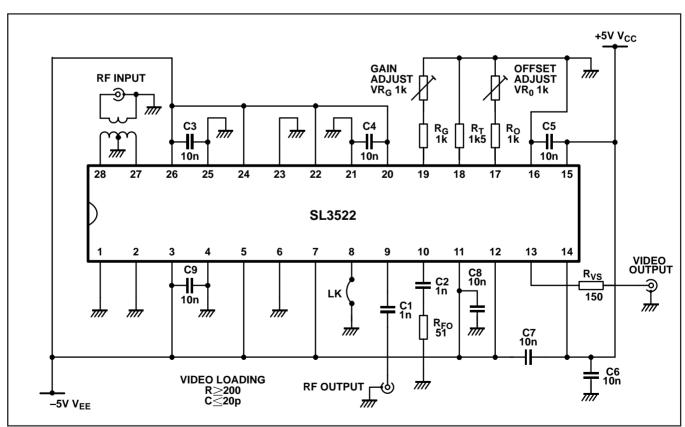

Fig.3 Test circuit

#### PRODUCT DESCRIPTION

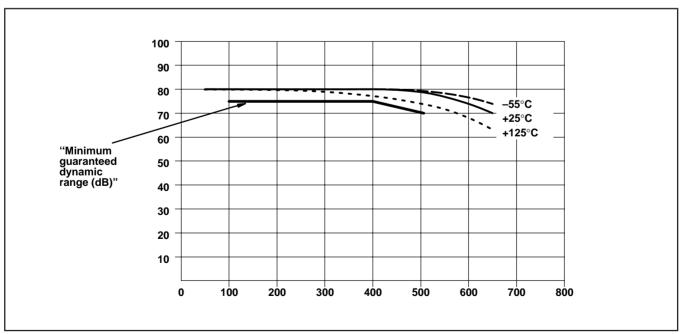

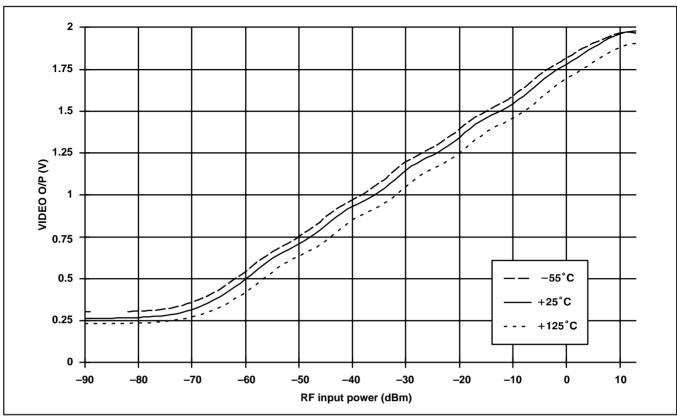

The SL3522 is a complete monolithic successive detection Log/limiting amplifier which can operate over an input frequency range of 100MHz to 500MHz. Producing a log/lin characteristic for input signals between -64dBm and +6dBm, the log amplifier can provide an accuracy of better than  $\pm 1.00 dB$  at case temperatures of -55°C and +25°C and an accuracy of better than  $\pm 1.25 dB$  at +125°C. The dynamic range is better than 75dB over a frequency range of 100MHz to 400MHz. The graph in fig 4 shows how the dynamic range is guaranteed over frequency.

The SL3522 consists of 6 Gain stages, 7 Detector stages, a limiting RF Output buffer and a Video Output amplifier. The power supply connections to each section are isolated from each other to aid stability.

The SL3522 consumes 1.1W of power when ALL parts of the circuit are powered up from a  $\pm 5.0$ V power supply. As the circuit uses a differential architecture, the power consumption of the RF gain/detector stages and RF Output Buffer will be independent of RF input signal level. However, the Video Output (pin 13) is driven by a single ended emitter follower and so the power consumption of the Video amplifier will vary with RF input signal level between pins 27 and 28.(upto 10mA over 2V video output range with max video load of  $200\Omega//20pF$ ) The SL3522 has a high RF gain (>50dB) across a wide bandwidth (>450MHz) when the limiting RF Output Buffer is enabled. The limiting RF Output Buffer provides a balanced Limited Output level of nominally -1.0dBm on each RF Output connection (pin 9 and 10), for RF input signal levels on pins 27 and 28 in excess of -50dBm.

The limiting RF Output Buffer can be isolated from the other sections of the SL3522, by disconnecting the RF Output Buffer GND (pin 8) from 0V, and leave the pin floating. This feature aids stability in applications NOT requiring a Limited RF Output signal, and lowers the power consumption of the SL3522 to 0.95Watts, when the other sections are powered up from a  $\pm 5.0$ V power supply.

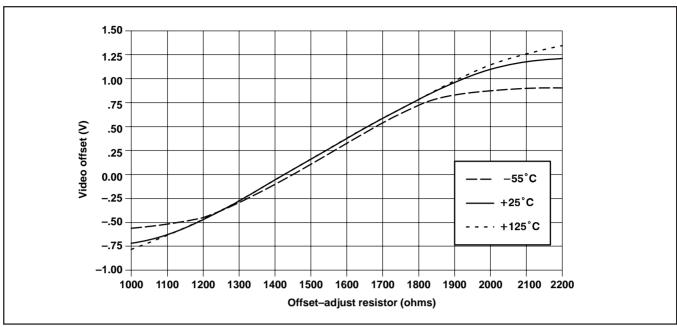

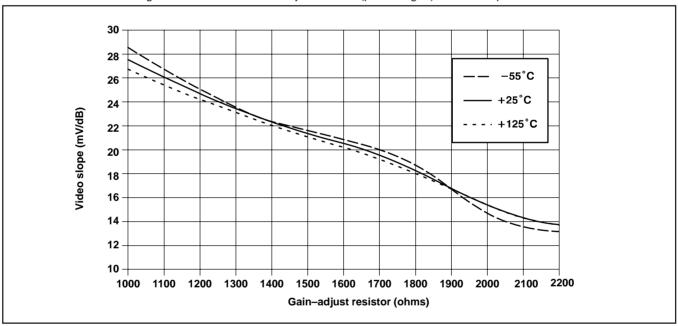

Each of the Gain and Detector stages has approximately 12dB of gain, and a significant amount of on-chip RF decoupling (200pF per stage), also to aid stability. The Video amplifier provides a positive going output signal proportional to the log of the amplitude of an RF input applied between pins 27 and 28. The gain and the offset of the Video amplifier can be adjusted by 3 resistors;  $R_{\rm G}$ ,  $R_{\rm T}$ , and  $R_{\rm O}$  which are connected to Gain adjust (pin 19),Trim reference (pin 18) and Offset adjust (pin 17). With  $R_{\rm T}$  set to  $1.5 k\Omega$ ,  $R_{\rm G}$  can be set to any value between  $1 k\Omega$  and  $2 k2\Omega$  and achieve a range in Video Slope of  $\pm 20\%$ , centred on 21 mV/dB. Similarly,  $R_{\rm O}$  can be set to any value between  $1 k\Omega$  and  $2.2 K\Omega$  and achieve an offset range of  $\pm 0.5 V$ , which should allow the Video Offset to be trimmed to 0V if required.

The RF input pins (27 and 28) have a  $50\Omega$  terminating resistor connected between them on–chip. These are capacitively coupled to the I/P gain stage with 20pF on-chip capacitors. (Refer to APPLICATION NOTES section for information on how to connect an RF input signal to the device).

Fig.4 Plot showing guaranteed dynamic range v. frequency (typical achievable dynamic range lines indicated across temperature)

#### **APPLICATION NOTES**

#### 1) VIDEO-AMPLIFIER

The SL3522 uses a single ended Video amplifier to produce a trimmable Video transfer characteristic. Both the gain (Slope) and Offset of the amplifier can be externally adjusted.

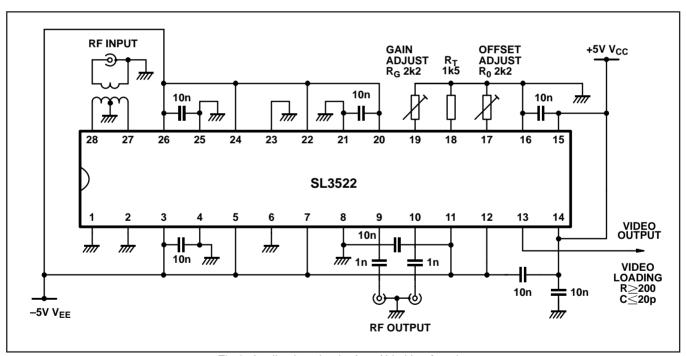

### a) Gain and Offset trimming (ref Applications circuits in figs 5 and 6)

The Gain and Offset control is achieved by adjusting  $R_G$  and  $R_O$  respectively. The control is dependent upon their difference from the Trim reference resistor,  $R_T$ . Adjustment of Gain has an effect on Offset, but adjustment of Offset does NOT affect the Gain. Therefore the Gain should be optimised first. The Offset should only be adjusted once the Gain has been set.

Fig 7 shows the variation of Video Offset with value of  $R_O$ , for a fixed value of  $R_T$  and  $R_G = 1 k S \Omega$ .

Fig 8 shows the variation of Video Slope with value of  $R_G$ , for a fixed value of  $R_T$  and  $R_O = 1k5\Omega$ .

The Video amplifier incorporates temperature compensation for Video gain (Slope). To ensure temperature stability for Video gain (Slope) over the operating temperature range, it is recommended that the resistors with identical temperature coefficients of resistance are used for  $R_T$  and  $R_G$ .

The Video amplifier does NOT incorporate temperature compensation for Video Offset. Although it is recommended that a resistor with identical temperature coefficient of resistance to  $R_T$  be used for  $R_O$ , it may be necessary to use an additional external temperature compensating network.

#### b) Video performance

The Video–amplifier has a critically damped rise time of 16ns (10% - 90%). In order to achieve this transient performance, it is important to ensure that:-

- i) the resistor connected to Trim reference (pin 18), has a nominal resistance of 1.5k $\Omega$ , with a parasitic capacitance LESS than 5pF.

- ii) the load applied to the Video Output (pin 13) does NOT exceed  $200\Omega$  resistance in parallel with 20pF.

Also, the following decoupling should be incorporated:-

- i) The Video Output  $V_{\rm CC}$  (pin 14) should be decoupled with a 10nF capacitor to the RETURN line from the video load, connected to Video GND (pin 16), avoiding any common impedance path.

- ii) The Video Output Vee (pin 12) should be decoupled with a 10nF capacitor DIRECTLY to Video-Output  $V_{\rm CC}$  (pin 14).

## 2) SL3522 AS A LOG AMPLIFIER with RF output buffer disabled (pin 8 floating)

If the SL3522 is to be used as a Logarithmic successive detection amplifier only, with no requirement for a limited RF Output, the RF input (pins 27 and 28) can be driven EITHER differentially or single ended from a  $50\Omega$  source. If being used with a single ended input, the SIGNAL should be applied to pin 27 and the RETURN should be connected to pin 28, as shown in the Application circuit diagram in Fig 5.

The SL3522 is VERY stable when used in this way. Although not a crucial requirement, it is recommended that the device should be mounted using a ground plane.

## 3) SL3522 AS A LOG/LIMITING AMPLIFIER - with RF Output-Buffer ENABLED (pin 8 connected to GND)

If the SL3522 is to be used as a Limiting or Log/limiting amplifier with a requirement for a Limited RF Output signal, care is required in the layout of components and connections around the device to ensure stability. The following precautions should be observed (refer to Application circuit diagram in Fig. 6):-

- a) The device should be mounted on a ground plane, ensuring that the impedance between the ground plane and ALL the GND pins is kept as low as possible. If a multilayer PCB is used where the ground plane is connected to the GND pins using through-plated holes (vias), it is essential to ensure that the vias have a very low impedance. ALL supply decoupling capacitors should be RF chip capacitors whose leads should be kept as short as possible.

- b) The RF  $V_{\text{EE}}$  connections (pins 3,5,7,11,20,22,24,26) should be connected to a low impedance copper plane. A two layer PCB should help to achieve this.

- c) The RF input (pins 27 and 28) should be driven with a balanced source impedance. One way of achieving this is to use an <code>isolating</code> BALUN transformer (50 $\Omega$  UNBALANCED  $\rightarrow$  50 $\Omega$  BALANCED) connected between the signal source and the RF input pins. (e.g. Mini circuits TT1–6, TO–75). The device stability is VERY sensitive to an imbalance of the differential source impedance at pins 27 and 28. Use of a transmission line BALUN though, is NOT recommended.

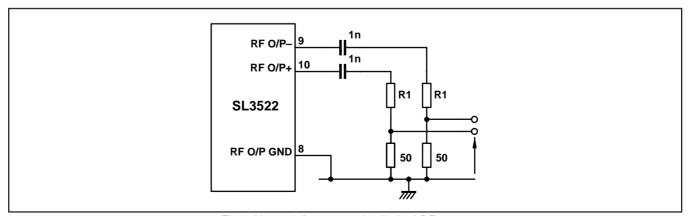

- d) The RF Output connections (pins 9 and 10) should each be loaded with matched impedances ideally  $50\Omega$  transmission lines. The RF Output lines leading away from the device should be balanced. Driving highly reactive SWR loads is NOT recommended as these can encourage device instability, as can an imbalance of the differential load impedance at pins 9 and 10.

- e) The RF Output connections (pins 9 and 10) are DC coupled, and ideally the output pins should be capacitively coupled to their loads using 1nF capacitors. However the RF Outputs can drive a DC load to GND and a DC offset of approx. 400mV will exist on each RF Output pin. IT WILL NOT BE POSSIBLE TO DISABLE THE RF OUTPUT BUFFER UNDER THESE CONDITIONS.

- f) The RF output (pins 9 and 10) has a tendancy to limit on self noise, particularly at low ambient temperatures (-55°C), when the RF output buffer is enabled.

NOTE that this will effect the liminting range as the gain of the RF output buffer will reduce as the amount of noise limiting increases.

If required the limited RF Output can be attenuated using an attenuation network as shown in fig. 9. Under these conditions the effective RF Output currents will be reduced, allowing the device to operate with a greater margin of stability.It may be possible to run the device without a BALUN transformer on the RF input if the total output impedance on the RF Output >>  $50\Omega$ , and the attenuation components are mounted as close as possible to the RF Output connections (pins 9 and 10). The RF input connection could then be configured as in Fig 5.

Fig.5 Application circuit successive detection logarithmic function only

Fig.6 Application circuit - Log / Limiting function

Fig.7 Video offset v. offset-adjust resistor (pin17 to gnd) across temperature

Fig.8 Video slope v. gain-adjust resistor (pin19 to gnd) across temperature

Fig.9 Network for attenuating limited RF output

#### A PRACTICAL APPLICATION FOR THE SL3522 AS A LOG/LIMITING AMPLIFIER

The SL3522, with the RF Output-Buffer ENABLED, has a large limited RF Output level (0dBm on each of two RF Output pins (9 and10)) and a wide RF bandwidth (450MHz) in a small 28 pin Miniature Ceramic S.O package. As a result, there is a tendency for the device to become unstable unless care is used in the application.

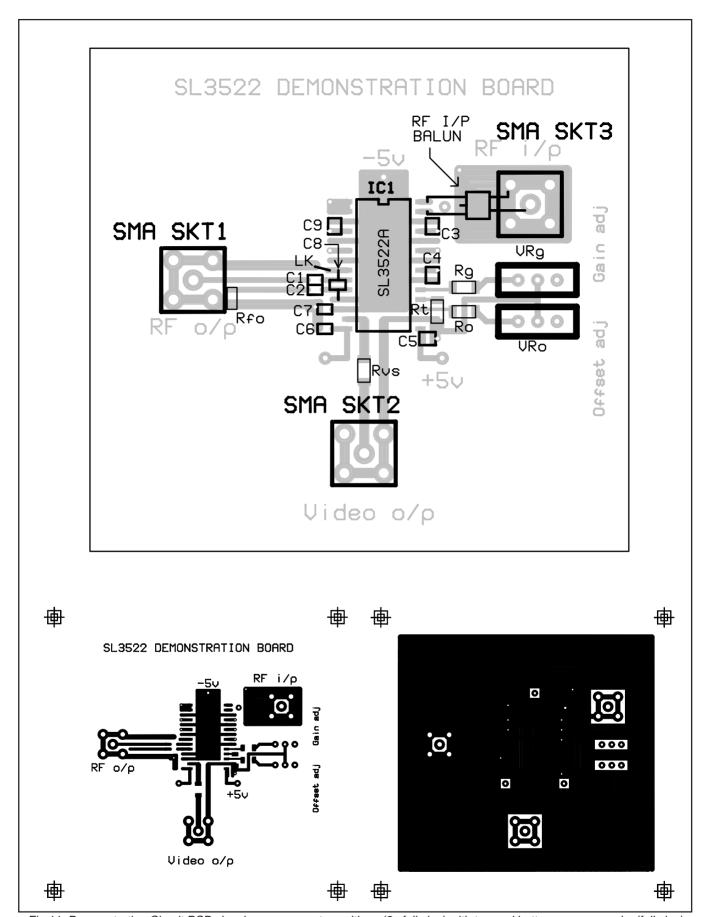

The PCB layout for a "SL3522 DEMONSTRATION BOARD" in Fig. 11 has proved reliably stable. The PCB is a double layer Fibre epoxy board which uses SMDs where possible. A circuit diagram for the Demonstration PCB appears in Fig. 10.

The following points should be noted when this application is realised practically:-

- 1) A wire needs to connect the two pads connected to pins 14 and 15 of the SL3522, to allow +5V to appear at both pins.

- 2) ALL the GND connections to the SL3522 are made through the PCB to a Ground plane on the bottom side. It is important to ensure that the impedance of each of these connections is kept to an absolute minimum to prevent instability. If these connections are achieved using through plated holes, it is recommended that they are filled with solder to lower their impedance.

- 3) The PCB is configured to accept SMA, SMB or SMC connectors for the RF input, RF Output and Video Output connections. These can be changed if necessary to an alternative type, but it is vital to ensure that the ground plane is solidly connected to the Guard Ring which surrounds the RF Output tracks.

- 4) The PCB is configured to accept a small surface mounting DC isolating BALUN transformer (e.g VANGUARD VE43666, available from Vanguard Electronics Company Inc, 1480 West 178th St. GARDENA, C.A. 90248, U.S.A. Tel:-U.S.A. (213) 323 4100) to couple a signal into the RF input connections (pins 27 and 28). It is NOT recommended to attempt operating the SL3522 with the RF Output Buffer enabled, WITHOUT using an input BALUN, although it may be possible, provided the input source impedance to both pins 27 and 28 remains balanced. The centre tap of the secondary winding of the transformer should be soldered to the small ground plane on the upper side of the PCB.

- 5) The RF Output connection to the PCB is from pin 9 of the SL3522 only, with pin 10 being terminated on the PCB using a  $51\Omega$  resistor. It is important to ensure that both pin 9 and 10 are terminated with equal impedances.

- 6) The RF Output Buffer can be enabled by soldering a link (LK) between pin 8 of the SL3522 and the adjacent guard track around the RF Output lines. Similarly, the buffer can be disabled by removing the same link. When the buffer is disabled, the following components can be omitted:-

1nF capacitors (C1, C2)

10nF capacitor (C8)

51Ω resistor ( $R_{FO}$ )

7) The Slope (gain) and Offset of the Video Output can be adjusted using two 1k $\Omega$  trimmers, provision for which is included in the PCB layout.

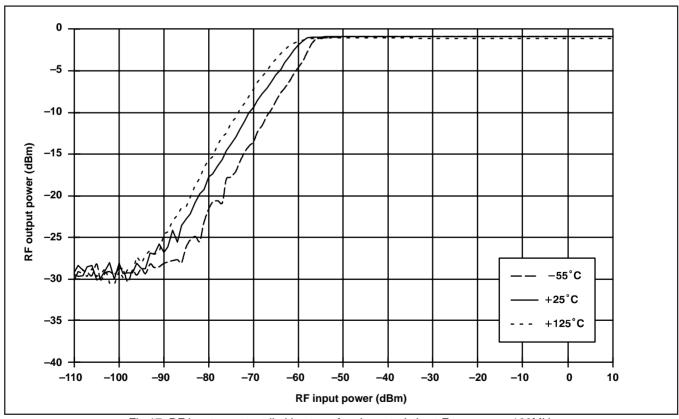

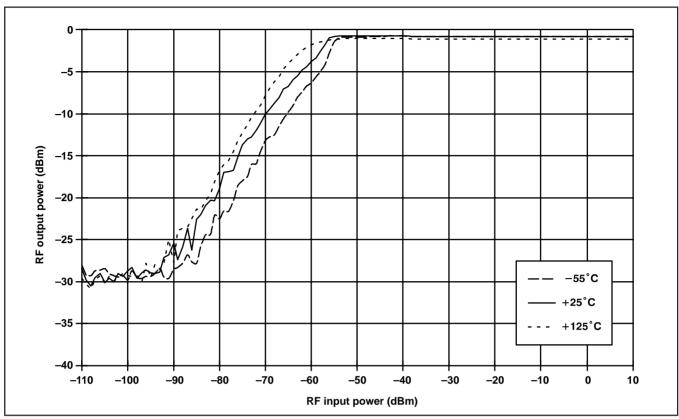

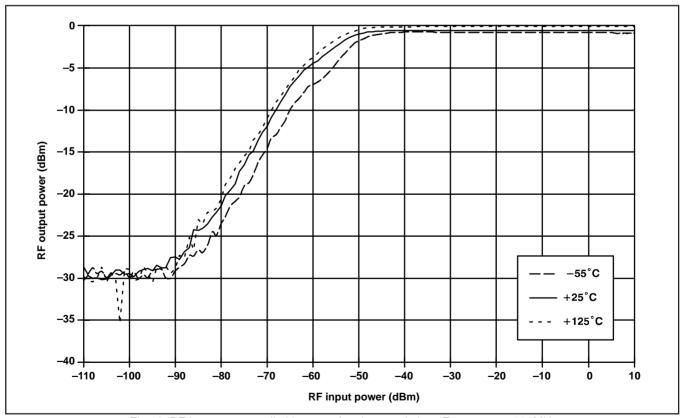

The plots in Fig. 12 to fig. 23 are typical of the performance of SL3522 devices used with the PCB layout detailed in Fig. 11.

Fig.10 SL3522 demonstration board circuit diagram

Fig.11 Demonstartion Circuit PCB showing components positions (2x full size) with top and bottom copper masks (full size)

Fig.12 Video O/P vs CW input level at 325MHz across temperature ( $V_{CC} = +5.0V$ ,  $V_{EE} = -5.0V$ )

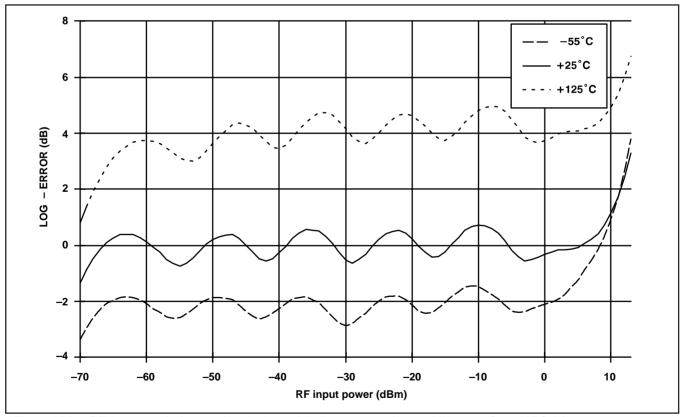

Fig.13 Video O/P log-error, (referenced to single straight line measured at 325MHz, +25°C, 5.0V PSUs) across temperature

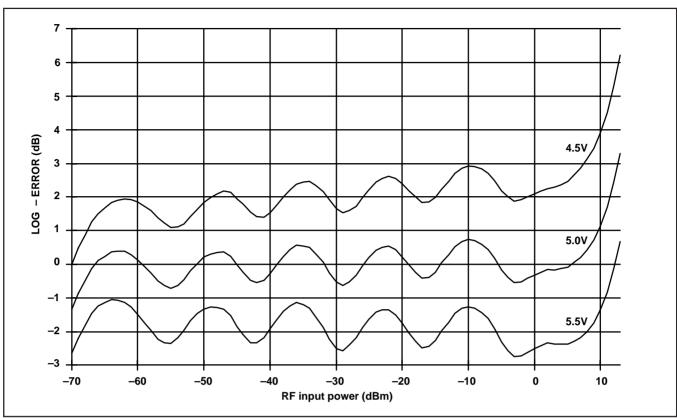

Fig.14 Video log error, (referenced to single straight line measured at 325MHz, 25°C, 5.0V PSUs), across supply voltage

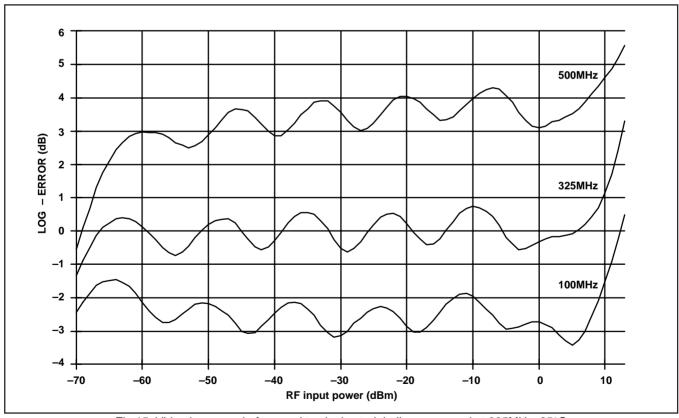

Fig.15 Video log error, (referenced to single straight line measured at 325MHz, 25°C,

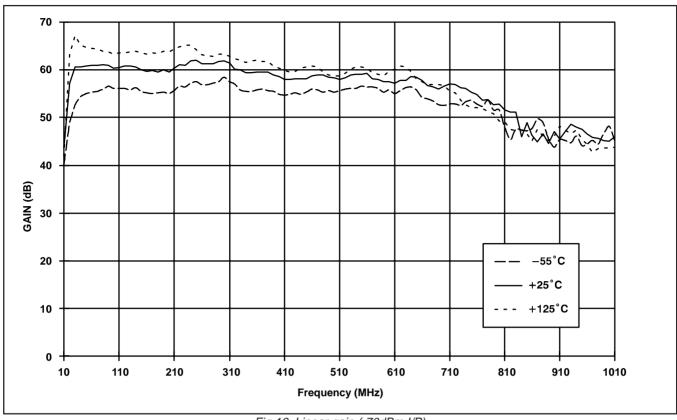

Fig.16 Linear gain (-70dBm I/P)

Fig.17 RF input  $\rightarrow$  output limiting transfer characteristic at Frequency = 100MHz

Fig.18 RF input → output limiting transfer characteristic at Frequency = 325MHz

Fig.19 RF input  $\rightarrow$  output limiting transfer characteristic at Frequency = 500MHz

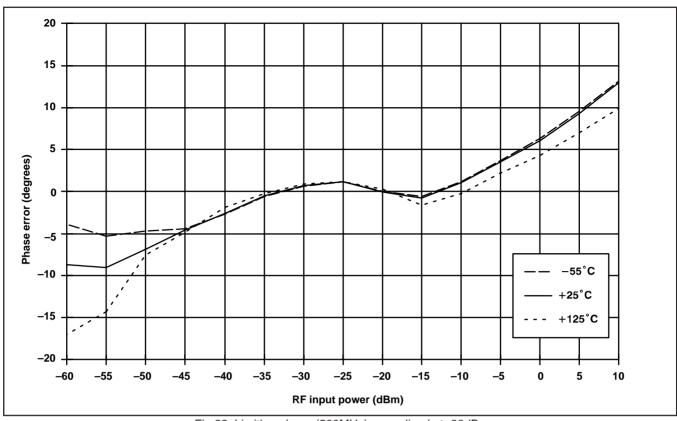

Fig.20 Limiting phase (100MHz) normalised at -30dBm

Fig.21 Limiting phase (300MHz) normalised at -30dBm

Fig.22 Limiting phase (500MHz) normalised at -30dBm

Fig.23 Typical input impedance normalised to 50Ω - 20dBm I/P level

16

- 1. All pads with square cross–section =120 $\mu$ m imes 120 $\mu$ m

- 2. All pads with octagonal cross–section =100 $\mu$ m imes 100 $\mu$ m

- 3. Chip is passivated with polyimide

Fig.25 SL3522 pad map for bare IC dice

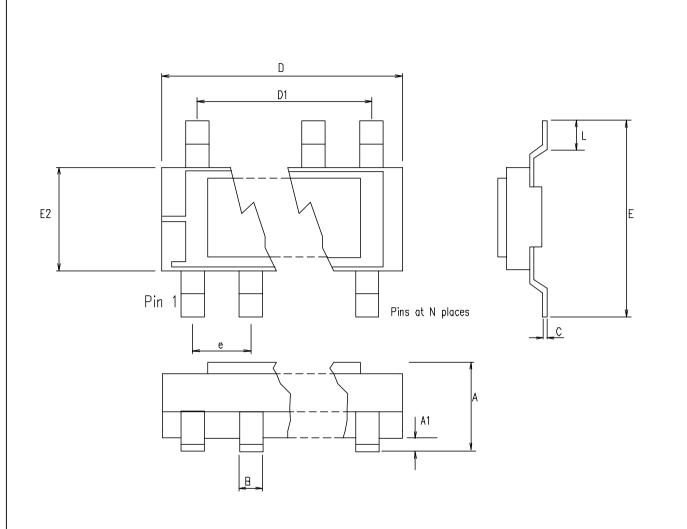

|        | Altern. Dimensions |                |       |  |            | ol Dimer |       |

|--------|--------------------|----------------|-------|--|------------|----------|-------|

| Symbol | in                 | in millimetres |       |  | in inches  |          |       |

|        | MIN                | Nominal        | MAX   |  | MIN        | Nominal  | MAX   |

| Α      | 2.20               |                | 2.75  |  | 0.087      |          | 0.108 |

| A1     |                    |                | 0.30  |  |            |          | 0.012 |

| В      | 0.37               |                | 0.47  |  | 0.015      |          | 0.019 |

| С      | 0.17               |                | 0.23  |  | 0.007      |          | 0.009 |

| D      | 17.70              |                | 18.10 |  | 0.697      |          | 0.713 |

| D1     | 16.36              |                | 16.66 |  | 0.644      |          | 0.656 |

| E      | 10.00              |                | 10.67 |  | 0.394      |          | 0.420 |

| E2     | 7.30               |                | 7.60  |  | 0.287      |          | 0.299 |

| е      | 1.27 BSC.          |                |       |  | 0.050 BSC. |          |       |

| L      | 0.75               |                | 1.08  |  | 0.030      |          | 0.043 |

|        |                    |                |       |  |            |          |       |

|        |                    |                |       |  |            |          |       |

|        |                    |                |       |  |            |          |       |

|        | Pin features       |                |       |  |            |          |       |

| N      | 28                 |                |       |  |            |          |       |

| ND     | 14                 |                |       |  |            |          |       |

| NE     | 0                  |                |       |  |            |          |       |

| NOTE   | RECTANGULAR        |                |       |  |            |          |       |

|       |           |           | This drawing supersedes 418/ED/51300/005 issue 1 (Swindon) |  |  |  |  |  |

|-------|-----------|-----------|------------------------------------------------------------|--|--|--|--|--|

|       |           |           | ORIGINATING SITE: SWINDON                                  |  |  |  |  |  |

| ISSUE | 1         | 2         | Title: Outline drawing for                                 |  |  |  |  |  |

| ACN   | 201634    | 201849    | 28 Lead S.O. (MC)                                          |  |  |  |  |  |

| DATE  | 12.NOV.96 | 11.FEB.97 | Drawing Number                                             |  |  |  |  |  |

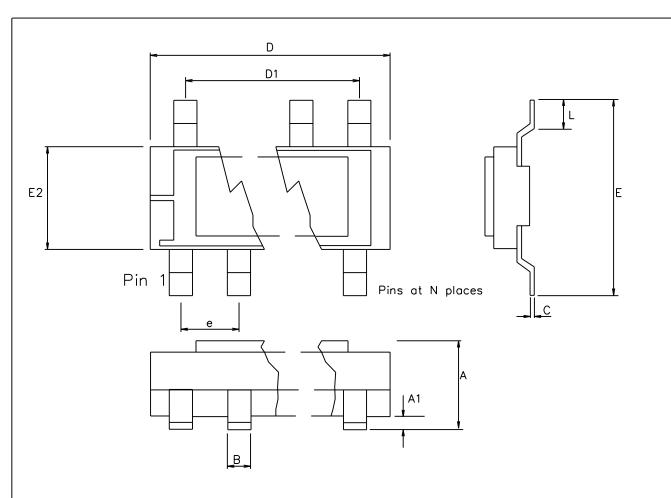

|        | Altern. Dimensions |         |       |  |            | ol Dimer |       |

|--------|--------------------|---------|-------|--|------------|----------|-------|

| Symbol | in millimetres     |         |       |  | in inches  |          | 3     |

|        | MIN                | Nominal | MAX   |  |            | Nominal  | MAX   |

| Α      | 2.20               |         | 2.75  |  | 0.087      |          | 0.108 |

| A1     |                    |         | 0.30  |  |            |          | 0.012 |

| В      | 0.37               |         | 0.47  |  | 0.015      |          | 0.019 |

| С      | 0.17               |         | 0.23  |  | 0.007      |          | 0.009 |

| D      | 17.70              |         | 18.10 |  | 0.697      |          | 0.713 |

| D1     | 16.36              |         | 16.66 |  | 0.644      |          | 0.656 |

| E      | 10.00              |         | 10.67 |  | 0.394      |          | 0.420 |

| E2     | 7.30               |         | 7.60  |  | 0.287      |          | 0.299 |

| е      | 1.27 BSC.          |         |       |  | 0.050 BSC. |          |       |

| L      | 0.75               |         | 1.08  |  | 0.030      |          | 0.043 |

|        |                    |         |       |  |            |          |       |

|        |                    |         |       |  |            |          |       |

|        |                    |         |       |  |            |          |       |

|        | Pin features       |         |       |  |            |          |       |

| Ν      | 28                 |         |       |  |            |          |       |

| ND     | 14                 |         |       |  |            |          |       |

| NE     | 0                  |         |       |  |            |          |       |

| NOTE   | RECTANGULAR        |         |       |  |            |          |       |

This drawing supersedes 418/ED/51300/005 issue 1 (Swindon)

| © Zarlink Semiconductor 2002 All rights reserved. |         |         |         |  |  |  |

|---------------------------------------------------|---------|---------|---------|--|--|--|

| ISSUE                                             | 1       | 2       | 3       |  |  |  |

| ACN                                               | 201634  | 201849  | 212449  |  |  |  |

| DATE                                              | 12Nov96 | 11Feb97 | 26Mar02 |  |  |  |

| APPRD.                                            |         |         |         |  |  |  |

|                        | Package Code                                                         |

|------------------------|----------------------------------------------------------------------|

| Previous package codes | Package Outline for 28 lead<br>SOIC (ceramic) (0.150" Body<br>Width) |

|                        | GPD00267                                                             |

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE