# **Preliminary**

SH58201 SH58216 EV

#### **Features**

- 65C02-based single chip 8 bit micro-controller

- Operation voltage:2.2V~3.5V

- Dual oscillation circuits:System oscillator

RC or Crystal Mode selected by pad option

(oscillator can be 3.58M ceramic or 4~16M Crystal

or 4~16M RC under 3.0V Operating)

32.768K Crystal for real time clock

- MCU(CPU) operate speed --software programmable Source Clock /2, /4, /8 mode 32.678KHz (Crystal)

- RAM: Built-in 12K x 8 bits(incl. program Var. & stack)

External RAM available (Max. up to 2M byte)

- ROM: Built-in 256K x 8 bits (incl. Program and Data)

External ROM available (Max. up to 4M byte)

- Internal and external ROM Co-existed (Max. 4M byte)

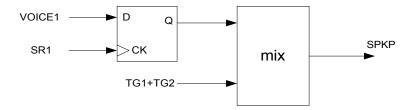

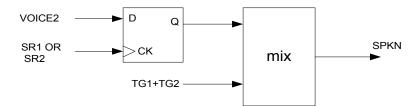

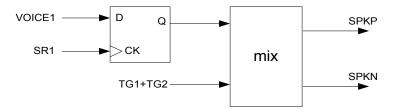

- Voice Synthesizer of 2 channels & Tone

- Software selectable compression structure for various sound quality and duration requirements:

4 bits ADPCM or 5 bit u-law or 8 bit PCM

- 2 Modes of PWM/DAC output Double-Pin Single Ended (only for PWM) Single-Pin Single Ended

- Can connect with 2 speakers output for STEREO effect

- UART with maximum baud rate 57.6Kbps is available

- Two I/O ports--PA & PB (16 I/O pads)

- One O/P port--PC (8 O/P pads)

- One Special Purpose I/O port PD (this port can be switched as I/O or special function port)

- 1 external interrupt

- 1 build-in remote control carrier synthesizer software programmable

- 1 serial input for UART

- 1 serial output for UART

- 8 bit I/O configured as push-pull/open-collector output

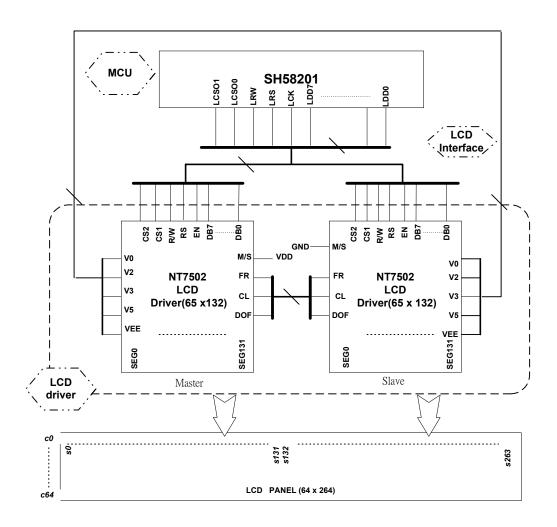

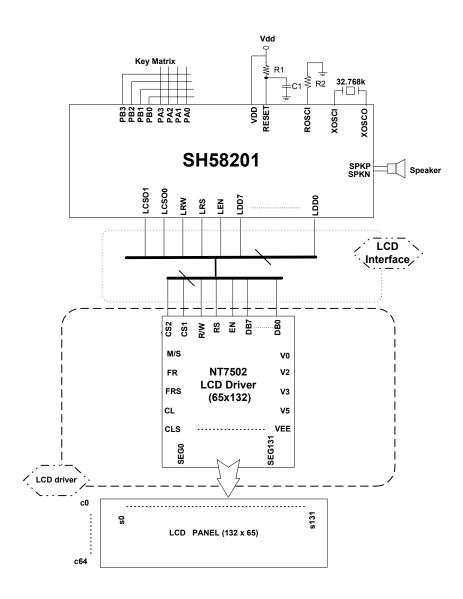

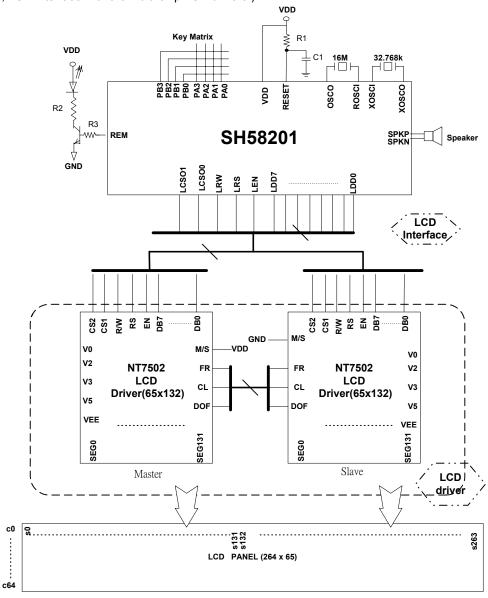

- Standard LCD driver interface (13 ports including 2 chip select)

- Three 8-bit timers----Timer0, Timer1, Timer2.

- Two 16-bit sample rate counters (SR1,SR2)

- SR1and SR2 are used for Voice sample rate clock

- One programmable watchdog timer

- One programmable wake-up timer

- Two interrupt levels and various interrupt sources:

NMI and IRQ ( priority: NMI > IRQ) IRQ source

Timer0, Timer1, Timer2, Wake-Up Timer, PA&PB (falling edge), External Interrupt, SR2 Sample rate clock

NMI source

PA, SR1 Sample rate clock, SRI & STI for serial interface

- Power saving mode and wake-up function

- Low power detector

## **General Description**

The SH58201 is a powerful 8-bit micro-controller with LCD drivers interfaces. It integrates a 65C02 8-bit core CPU, SRAM, ROM, and complicated logic blocks, such as timers, PWM/DAC. The dual-buffered PWM allows user to connect one speaker directly or 2 speakers with external components. The standby/wakeup function, which can be used to stop/wake-up the oscillator, facilitates the system entrance/quitting the low power dissipation. This chip offers 2 channels of voice or tone or mixed, the speech sources can be coded as PCM, u-Law or ADPCM format through NOVATEK's tools.

Voice duration depends on the compression structure. Lower compression rate gains high sound quality and shorter duration. Normally, ADPCM can meet most requirements especially the sound frequency varies not so violent.

SH58201 also offers total 16 I/O, 8 O/P pins and 8 speical purpose I/O, which can be used for keyboard scan or others high I/O pins needed application. The embeded UART also facilitates the device communicating with the PC via RS232 serial port. Using the LCD interface, it's suitable to be a LCD ELA product control engine. Furthermore, the electronic dictionary, the electrical data bank or personal digital assistance (PDA) equipment, talking instrument and general speech synthesizer are also applicable.

- 1 - Ver0.13

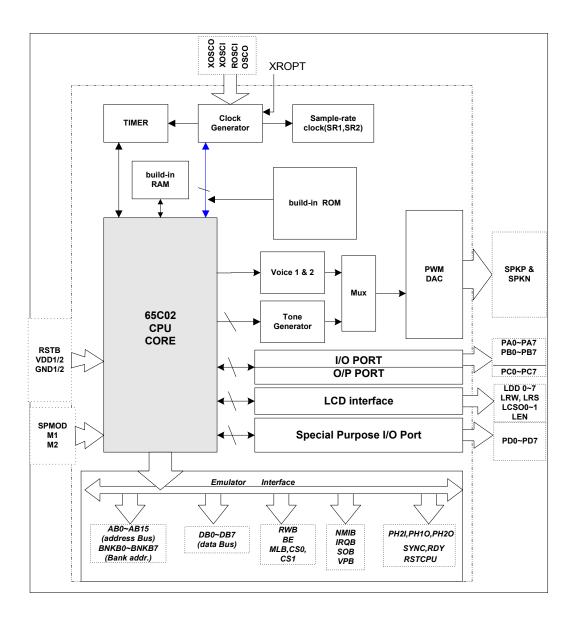

# **Block Diagram**

- 2 - Ver0.13

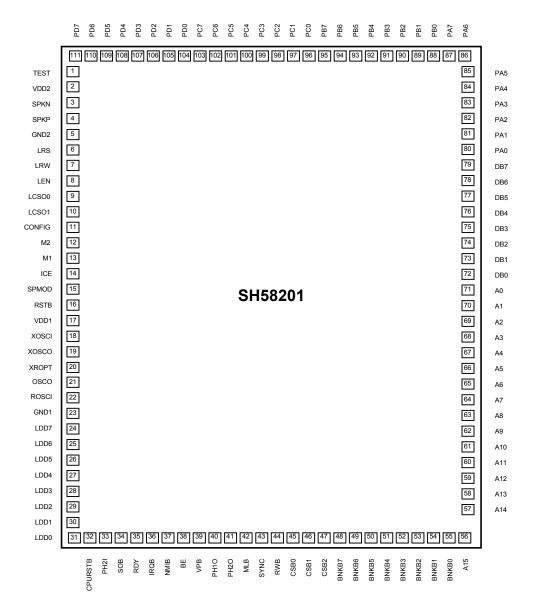

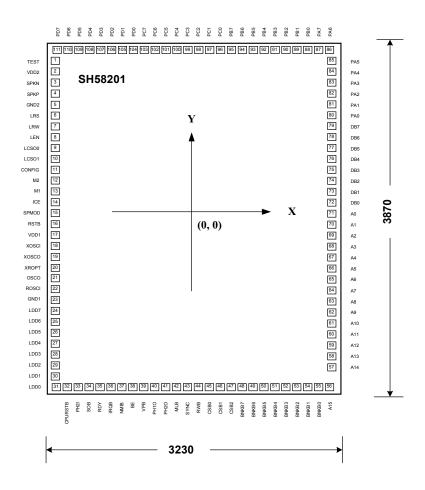

# **Pad Configuration**

- 3 - Ver0.13

# Pin · Pad Descriptions

| Pin No.    | Pad No | Designation    | I/O      | Description                                                       |

|------------|--------|----------------|----------|-------------------------------------------------------------------|

|            |        | XOSCI          | I        | 32768 Hz crystal oscillator input pin                             |

|            |        | XOSCO          | 0        | 32768 Hz crystal oscillator output pin                            |

|            |        | ROSCI          | Ī        | System oscillator (RC or Crystal) input pin                       |

|            |        | OSCO           | 0        | System oscillator (Crystal) output pin (Pad option)               |

|            |        | XROPT          | Ī        | 0=RC type; 1=X'tal /Resonator type                                |

|            |        | RSTB           | i        | Reset pin                                                         |

|            |        | VDD1           | i        | Positive power pin                                                |

|            |        | GND1           | <u>'</u> | Ground pin                                                        |

|            |        | VDD2           | <u>'</u> | Positive power pin                                                |

|            |        | GND2           | <u>'</u> | Ground pin                                                        |

|            |        | PA0~PA7        | I/O      | Bi-directional I/O port (all bit programmable )                   |

|            |        | PB0~PB7        | 1/0      | Bi-directional I/O port (high /low nibble programmable)           |

|            |        | PC0~PC7        |          | Output only port                                                  |

|            |        | PD0 / EXT_INT  | I/O      | Special purpose I/O (can switch as normal I/O or special function |

|            |        | PD0 / EXT_INT  | 1/0      | pin) PD.0 can be switched as external interrupt; PD.3 can be      |

|            |        | PD2 / RXD      |          | switched as Remote control synthesizer carrier; PD2 & PD1 can     |

|            |        | PD3 / REMO     |          | be switched as UART receive input and transmit output,            |

|            |        | PD4 ~ PD7      |          | individually.                                                     |

|            |        | 1 54 1 57      |          | PD4~7 can be selected as open drain output.                       |

|            |        | SPKP,SPKN      | 0        | Positive/Negative terminal of PWM output pins                     |

|            |        | Or rai, or rai |          | (directly connect with speaker or separate as 2 channels)         |

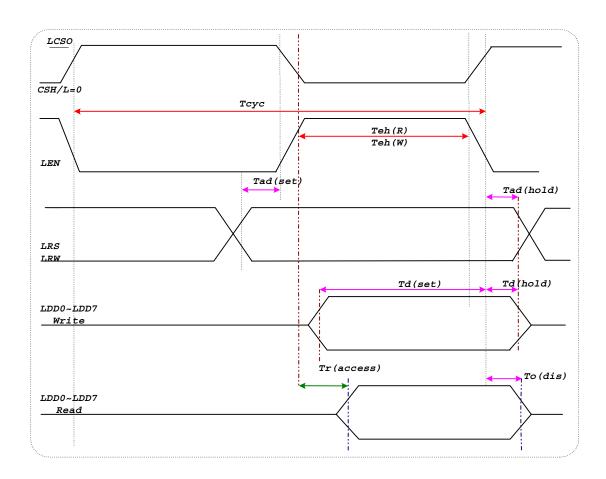

|            |        | LDD0~~LDD7     | I/O      | LCD interface(for data bus)                                       |

|            |        | LRS            | 0        | LCD interface(for register select, choose Command/Data mode)      |

|            |        | LCSO0~LCSO1    | 0        | LCD interface(for chip select in the multi-chip mode)             |

|            |        | LRW            | 0        | LCD interface(read /write signal )                                |

|            |        | LEN            | 0        | LCD interface( read/write enable signal)                          |

|            |        | CSB0           | 0        | External ROM chip select enable (Low active)                      |

|            |        | CSB1           | 0        | External Flash ROM chip select enable (Low active)                |

|            |        | CSB2           | 0        | External RAM chip select enable (Low active)                      |

|            |        | SPMOD          | ī        | Special mode switch                                               |

|            |        | CONFIG         | Ö        | CONFIG SETTING (Low active)                                       |

|            |        | M1, M2         | i        | Mode selection(ICE or Normal mode) → Default: M1 floating         |

|            |        | BNKB0~BNKB7    | 0        | Address Bus for bank switch                                       |

|            |        | DB0~DB7        | 1/0      | 65C02 CPU signal(data bus)                                        |

|            |        | A0~A15         | 1/0      | 65C02 CPU signal(address Bus)                                     |

|            |        | BE             | 0        | 65C02 CPU signal (Bus enable signal)                              |

|            |        | MLB            | 1/0      | 65C02 CPU signal (Memory lock)                                    |

|            | +      | RWB            | 1/0      | 65C02 CPU signal (Read or write selection)                        |

|            | 1      | PH2I           | 0        | 65C02 CPU signal (Phase 2 input clock)                            |

|            | +      | PH10,PH20      | 1/0      | 65C02 CPU signal (Phase1,2 output clock)                          |

|            | +      | SYNC           | I/O      | 65C02 CPU signal (Synchronize input)                              |

|            | 1      | RDY            | 0        | 65C02 CPU signal (Ready)                                          |

|            | 1      | NMIB, IRQB     | 0        | 65C02 CPU signal (Non-maskable IRQ, Interrupt request)            |

|            | 1      | SOB            | 0        | 65C02 CPU signal (Nori-maskable IRQ, interrupt request)           |

|            | +      | VPB            | 1/0      | 65C02 CPU signal (Set overnow)                                    |

|            |        | CPURSTB        | 1/0      | 65C02 CPU signal (Vector full)                                    |

|            |        |                | 1/0      |                                                                   |

|            |        | ICE<br>TEST    | I        | For ICE with 65C02                                                |

| Total pin  |        | IESI           | <u> </u> | Test pin                                                          |

| No. 111pin |        |                |          |                                                                   |

- 4 - Ver0.13

# **SYSTEM REGISTER (1)**

| ADDRESS          | REGISTER             | 7       | 6       | 5         | 4             | 3       | 2      | 1           | 0           | R/W      |  |  |  |

|------------------|----------------------|---------|---------|-----------|---------------|---------|--------|-------------|-------------|----------|--|--|--|

|                  |                      |         | _       | MEN       | MORY          | -       |        |             | _           | I        |  |  |  |

| \$1F00           | ROM_BNK1             | BNK1.7  | BNK1.6  | BNK1.5    | BNK1.4        | BNK1.3  | BNK1.2 | BNK1.1      | BNK1.0      | R/W      |  |  |  |

| \$1F01           | ROM_BNK2             | BNK2.7  | BNK2.6  | BNK2.5    | BNK2.4        | BNK2.3  | BNK2.2 | BNK2.1      | BNK2.0      | R/W      |  |  |  |

| \$1F0B           | RAM_BNK              | BNK3.7  | BNK3.6  | BNK3.5    | BNK3.4        | BNK3.3  | BNK3.2 | BNK3.1      | BNK3.0      | R/W      |  |  |  |

| \$1F02           | RAM_NO               | -       | -       | -         | -             | -       | RAM.2  | RAM.1       | RAM.0       | R/W      |  |  |  |

| \$1F03           | ROM_NO               | -       | -       | -         | -             | -       | ROM.2  | ROM.1       | ROM.0       | R/W      |  |  |  |

| \$1F0C           | EX_RAM_E             | enable  | -       | -         | -             | -       | •      | -           | •           | W        |  |  |  |

| \$1F0D           | EX_ROM_S             | enable  | -       | -         | -             | -       | ı      | -           | ı           | W        |  |  |  |

| SYSTEM CONTROL   |                      |         |         |           |               |         |        |             |             |          |  |  |  |

| \$1F04           |                      |         |         |           |               |         |        |             |             |          |  |  |  |

| \$1F05           | SPECIAL2             | EXTINT  | UART    | WDT       | REMO          | -       | -      | -           | -           | R/W      |  |  |  |

| \$1F06           | SYS_CTRL             | D.7     | D.6     | D.5       | D.4           | D.3     | -      | -           | -           | R/W      |  |  |  |

| \$1F07           | PWR_SAV              | -       | -       | -         | -             | -       | -      | X32KEN      | SPDUP       | R/W      |  |  |  |

| \$1F08           | RESET                | -       | -       | -         | -             | -       | WT     | WD          | IPA         | R        |  |  |  |

| \$1F09           | LPD_CTRL             | LPD_EN  | -       | -         | -             | -       | -      | -           | LPD         | R/W      |  |  |  |

| \$1F0A           | CONFIG               | SPM     | -       | -         | -             | -       | -      | -           | CONFIG      | R or W   |  |  |  |

|                  |                      | I       | I       |           | RRUPT         | 1       |        | I           |             | 1        |  |  |  |

| \$1F10           | NMI_IE               | NMISR1  | -       | -         | -             | -       | NMISR  | NMIST       | NMIPA       | R/W      |  |  |  |

| \$1F11           | NMI_IF               | NMISR1  | -       | -         | -             | -       | NMISRI | NMISTI      | NMIPA       | R        |  |  |  |

| \$1F12           | IRQ_IE               | IRQSR2  | IRQWT   | IRQEXT    | IRQPB         | IRQPA   | IRQT2  | IRQT1       | IRQT0       | R/W      |  |  |  |

| \$1F13           | IRQ_IF               | IRQSR2  | IRQWT   | IRQEXT    | IRQPB         | IRQPA   | IRQT2  | IRQT1       | IRQT0       | R        |  |  |  |

|                  |                      |         |         |           | /IER          |         |        |             |             |          |  |  |  |

| \$1F14           | TM0_CTRL             | BD/TM   | T/RCLK  | -         | -             | TM0.3   | TM0.2  | TM0.1       | TM0.0       | W        |  |  |  |

| \$1F15           | TM0COUNT             | T7      | T6      | T5        | T4            | T3      | T2     | T1          | TO          | R/W      |  |  |  |

| \$1F16           | TM1_CTRL             | BD/TM   | T/RCLK  | -<br>     | -             | TM1.3   | TM1.2  | TM1.1       | TM1.0       | W        |  |  |  |

| \$1F17<br>\$1F18 | TM1COUNT<br>TM2 CTRL | T7      | T6      | T5        | T4            | T3      | T2     | T1          | TM2.0       | R/W<br>W |  |  |  |

| \$1F10<br>\$1F19 | TM2_CTRL             | -<br>T7 | -<br>TC | -<br>TE   | -<br>T4       | -<br>T3 | TM2.2  | TM2.1       | TM2.0       |          |  |  |  |

| \$1F19<br>\$1F1A | WKT CTRL             |         | T6      | T5        | T4            |         | T2     | T1<br>WKT.1 | T0<br>WKT.0 | R/W<br>W |  |  |  |

| \$1F1B           | WDT RST              | -       | -       | -         | -             | -       | -      | VVIX.I.     | VVK1.U      | W        |  |  |  |

| \$1F1B           | WDI_RSI              | -       | -       | CARRIER S | -<br>SVNTHIZE | <br>D   | -      | -           | -           | VV       |  |  |  |

| \$1F1C           | RF CTRL              | enable  | _       | -         |               | _       |        |             | RFQ.0       | W        |  |  |  |

| \$1F1D           | RF_OUTPUT            | enable  | -       | -         | _             | _       | -      | -           | DATA        | R/W      |  |  |  |

| Ψ11 1D           | 141_001101           | _       | _       | INPUT/OU  | TPLIT POR     | <br>T   |        | _           | שאוא        | 17/77    |  |  |  |

| \$1F20           | IPA MODE             | -       | _       |           |               | -       | _      | _           | Edge/level  | W        |  |  |  |

| \$1F21           | PA PA                | PA.7    | PA.6    | PA.5      | PA.4          | PA.3    | PA.2   | PA.1        | PA.0        | R/W      |  |  |  |

| \$1F22           | PAC                  | PAC.7   | PAC.6   | PAC.5     | PAC.4         | PAC.3   | PAC.2  | PAC.1       | PAC.0       | R/W      |  |  |  |

| \$1F23           | PB                   | PB.7    | PB.6    | PB.5      | PB.4          | PB.3    | PB.2   | PB.1        | PB.0        | R/W      |  |  |  |

| \$1F24           | PBC                  | -       | -       | -         | -             | -       | -      | PBC.H       | PBC.L       | R/W      |  |  |  |

| \$1F25           | PC                   | PC.7    | PC.6    | PC.5      | PC.4          | PC.3    | PC.2   | PC.1        | PC.0        | W        |  |  |  |

| \$1F26           | PD                   | PD.7    | PD.6    | PD.5      | PD.4          | PD.3    | PD.2   | PD.1        | PD.0        | R/W      |  |  |  |

| \$1F27           | PDC                  | PDC.7   | PDC.6   | PDC.5     | PDC.4         | PDC.3   | PDC.2  | PDC.1       | PDC0        | R/W      |  |  |  |

| \$1F28           | PDS                  | PDS.7   | PDS.6   | PDS.5     | PDS.4         | PDS.3   | PDS.2  | PDS.1       | PDS.0       | R/W      |  |  |  |

|                  | •                    |         |         |           | terface       |         |        |             |             | •        |  |  |  |

| \$1F29           | LCS                  | -       | -       | -         | -             | -       | CSH/L  | SEL1        | SEL0        | W        |  |  |  |

| \$1F2A           | LRS                  | -       | -       | -         | -             | -       | -      | -           | RS          | W        |  |  |  |

| \$1F2B           | RD_DATA              | 7       | 6       | 5         | 4             | 3       | 2      | 1           | 0           | R        |  |  |  |

| \$1F2C           | LCD0                 | 7       | 6       | 5         | 4             | 3       | 2      | 1           | 0           | R/W      |  |  |  |

| \$1F2D           | LCD1                 | 7       | 6       | 5         | 4             | 3       | 2      | 1           | 0           | R/W      |  |  |  |

- 5 - Ver0.13

# **SYSTEM REGISTER (2)**

|        |              |         | SPEEC  | H & SOU | ND CONT | ROL    |        |        |        |     |

|--------|--------------|---------|--------|---------|---------|--------|--------|--------|--------|-----|

| \$1F30 | TG1_L        | TG1.7   | TG1.6  | TG1.5   | TG1.4   | TG1.3  | TG1.2  | TG1.1  | TG1.0  | R/W |

| \$1F31 | TG1_H        | TG1.15  | TG1.14 | TG1.13  | TG1.12  | TG1.11 | TG1.10 | TG1.9  | TG1.8  | R/W |

| \$1F32 | TG1_CTL      | enable  | loop   | -       | -       | -      | -      | CS1    | CS0    | W   |

| \$1F33 | TG2_L        | TG2.7   | TG2.6  | TG2.5   | TG2.4   | TG2.3  | TG2.2  | TG2.1  | TG2.0  | R/W |

| \$1F34 | TG2_H        | TG2.15  | TG2.14 | TG2.13  | TG2.12  | TG2.11 | TG2.10 | TG2.9  | TG2.8  | R/W |

| \$1F35 | TG2_CTL      | enable  | loop   | •       | -       | -      | -      | CS1    | CS0    | W   |

| \$1F36 | TG1_ENV      | ı       | E6     | E5      | E4      | E3     | E2     | E1     | E0     | R/W |

| \$1F37 | TG2_ENV      | ı       | E6     | E5      | E4      | E3     | E2     | E1     | E0     | R/W |

| \$1F39 | SR1_COUNT(L) | SR1.7   | SR1.6  | SR1.5   | SR1.4   | SR1.3  | SR1.2  | SR1.1  | SR1.0  | R/W |

| \$1F3A | SR1_COUNT(H) | SR1.15  | SR1.14 | SR1.13  | SR1.12  | SR1.11 | SR1.10 | SR1.9  | SR1.8  | R/W |

| \$1F3B | SR1_CTRL     | enable  | loop   | -       | -       | -      | -      | CS1    | CS0    | W   |

| \$1F3C | SR2_COUNT(L) | SR2.7   | SR2.6  | SR2.5   | SR2.4   | SR2.3  | SR2.2  | SR2.1  | SR2.0  | R/W |

| \$1F3D | SR2_COUNT(H) | SR2.15  | SR2.14 | SR2.13  | SR2.12  | SR2.11 | SR2.10 | SR2.9  | SR2.8  | R/W |

| \$1F3E | SR2_CTRL     | enable  | loop   | -       | -       | -      | -      | CS1    | CS0    | W   |

| \$1F3F | VOICE1       | D7      | D6     | D5      | D4      | D3     | D2     | D1     | D0     | W   |

| \$1F41 | VOICE2       | D7      | D6     | D5      | D4      | D3     | D2     | D1     | D0     | W   |

| \$1F43 | PWM_CTL      | SR2_E   | -      | -       | -       | -      | -      | -      | ST_ON  | R/W |

| \$1F44 | SD_CTL       | PWM/DAC | -      | -       | -       | DAC2EN | PWM2EN | DAC1EN | PWM1EN | R/W |

|        |              |         |        | UAF     | RT      |        |        |        |        | ·   |

| \$1F50 | STBUF        | TD.7    | TD.6   | TD.5    | TD.4    | TD.3   | TD.2   | TD.1   | TD.0   | R/W |

| \$1F51 | SRBUF        | RD.7    | RD.6   | RD.5    | RD.4    | RD.3   | RD.2   | RD.1   | RD.0   | R   |

| \$1F52 | SCON         | SM      | -      | -       | REN     | TB8    | RB8    | -      | -      | R/W |

- 6 - Ver0.13

# **Functional Descriptions**

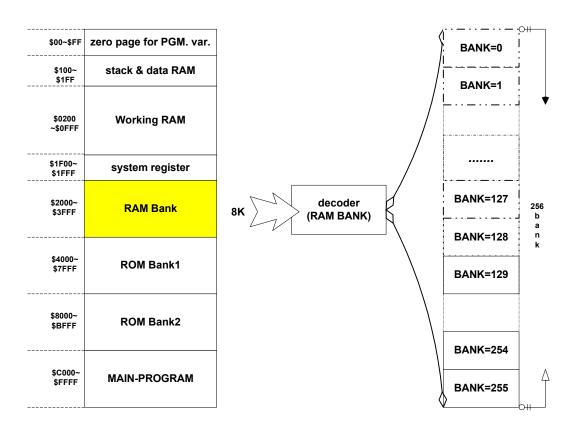

# **Memory Allocation**

## **RAM** allocation

SH58201 provides 12k x 8 bit RAM, including data memory, stack, programming variable & system register

| RAM ADDRESS   | Description                    |

|---------------|--------------------------------|

| \$0000~\$00FF | Zero page for program variable |

| \$0100~\$01FF | Stack Area                     |

| \$0200~\$0FFF | Working RAM                    |

| \$2000~\$3FFF | Working RAM (Window for Bank)  |

| \$1F00~\$1FFF | System register                |

## **RAM** mapping

- 7 - Ver0.13

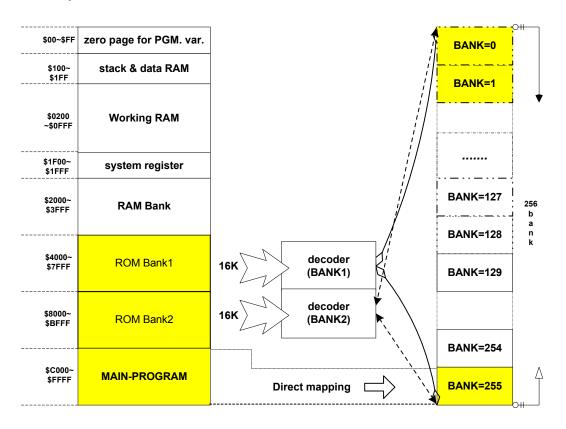

## **ROM** allocation map

# **ROM** mapping

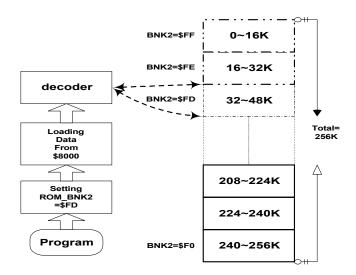

Under 65C02 core structure, the program counter (16 bit) can only addressed 64K x 8 bit space, hence, for the ROM/RAM size above 64K x 8 bit, the SH58201 offers the method of switching banks to extend the CPU address space. This chip offers 3 bank mapping areas, one is located at \$2000~\$3FFF(8K), one is located at \$4000~\$7FFF(16K) and the other is located at \$8000~\$BFFF (16K). There are 256 banks derived from each mapping area decoding.

There are 2 chip selections for choosing memory modules. For \$2000~\$3FFF, this block indicates 8K x 8bit while at \$4000~\$7FFF and \$8000~\$BFFF, this block will indicate 16K x 8 bit. Hence, the system can address max. 2048K x 8 bit (RAM) and 4096K x 8 bit (ROM).

Bank switch register

| ADDRESS | REGISTER | 7                                                 | 6      | 5      | 4      | 3      | 2      | 1      | 0      | R/W | Default  |

|---------|----------|---------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|-----|----------|

| \$1F00  | ROM_BNK1 | BNK1.7                                            | BNK1.6 | BNK1.5 | BNK1.4 | BNK1.3 | BNK1.2 | BNK1.1 | BNK1.0 | R/W | 11111111 |

| \$1F01  | ROM_BNK2 | BNK2.7                                            | BNK2.6 | BNK2.5 | BNK2.4 | BNK2.3 | BNK2.2 | BNK2.1 | BNK2.0 | R/W | 11111111 |

| \$1F0B  | RAM_BNK  | BNK3.7                                            | BNK3.6 | BNK3.5 | BNK3.4 | BNK3.3 | BNK3.2 | BNK3.1 | BNK3.0 | R/W | 11111111 |

| Initial | setting  | Default: :: ROM_BNK1, ROM_BNK2=FFh, RAM_BNK = FFh |        |        |        |        |        |        |        |     |          |

- (A). The 16-bit program counter of 65C02 just can address 64K x 8 bits memory space. Bank switch is used to extend the CPU address space. The two upper 16K bytes ROM (\$4000~\$7FFF & \$8000~\$BFFF) blocks map to coordinate bank (according to the BANK register, listed as follows:) while the middle 8K bytes RAM blocks map to coordinate bank.

- (B). The ROM & RAM mapping is described as follows:

- 8 - Ver0.13

| ADDRESS       | _              | ROM_BNK1<br>ROM BNK2 | ROM_BNK<br>1ROM BN | _        | _        | _          | _      |

|---------------|----------------|----------------------|--------------------|----------|----------|------------|--------|

|               | =0             | =1                   | K2=238             | K2=239   | K2=240   | <br>K2=254 | K2=255 |

| \$C000~\$FFFF |                |                      |                    |          |          |            | 0K~16K |

| \$4000~\$7FFF | 4080~4096<br>K | 4064~4080<br>K       | 272~288K           | 256~272K | 240~256K | 16~32K     | 0K~16K |

| \$8000~\$BFFF | 4080~4096      | 4064~4080            | 272~288K           | 256~272K | 240~256K | 16~32K     | 0K~16K |

|               | K              | K                    |                    |          |          |            |        |

| ADDRESS       | RAM_BNK<br>=0 | RAM_BNK<br>=1 | <br>RAM_BNK<br>=222 | RAM_BNK<br>=223 | RAM_BNK<br>=224 | <br>RAM_BNK<br>=254 | RAM_BNK<br>=255 |

|---------------|---------------|---------------|---------------------|-----------------|-----------------|---------------------|-----------------|

| \$0000~\$1FFF |               |               |                     |                 |                 |                     |                 |

| \$2000~\$3FFF | 2040~2048     | 2032~2040     | 264~272K            | 256~264K        | 248~256K        | 8~16K               | 0~8K            |

|               | K             | K             |                     |                 |                 |                     |                 |

Unit: Byte

## (C). Bank Switch:

- (1). When the SH58201 is powered on, the ROM\_BNK1, ROM\_BNK2 & RAM\_BNK are initially switched to bank FFh.

- (2). In order to linearize the ROM mapping, the address \$C000~\$FFFF will direct map to the bank 255, listed above, and it will meet the rule of the vector table for the 65C02(the vector table should be located at \$FFFA~\$FFFF)

- (3). Wherever the ROM bank is, if the program counter read the \$C000~\$FFFF area, the bank must be switched to bank 255, thus, the program code and the vector table will not be lost in the bank switching. (the value of ROM\_BNK1, ROM\_BNK2 will not be changed)

- (4). The SH58201 build in 256K x 8 bit ROM, hence, in the Normal Mode (shown in the next page), ROM\_BNK1 & ROM\_BNK2 only can set in the following range: \$F0~\$FF.

- (5). If the user need the ROM size over than 256K x 8 bit, the SH58201 also supply the External ROM access solution: Step 1: Into the special mode by jumping the SPMOD pin to high (SPMOD=1), set proper ROM size by writing \$1F03 (ROM size select register).

- Step 2: Choose the External ROM mode by setting the M1, M2.

#### Example:

- 9 - Ver0.13

## **Chip Operation Mode Select**

#### Develop environment switch (Mode1, Mode2)

M1, M2: choose the developing environment In ICE or Normal mode with Internal ROM or External ROM.

| MODE                                                    | MEMORY ACCESS                        | M2  | M1 |  |  |  |  |  |  |

|---------------------------------------------------------|--------------------------------------|-----|----|--|--|--|--|--|--|

| Normal Mode                                             | Internal ROM                         | 0   | 0  |  |  |  |  |  |  |

| (internal CPU)                                          | External ROM                         | 0   | 1  |  |  |  |  |  |  |

| ICE Mode                                                | Internal ROM                         | 1   | 0  |  |  |  |  |  |  |

| (External CPU)                                          | External ROM                         | 1   | 1  |  |  |  |  |  |  |

| M2: Choose Develop in the ICE mode or internal CPU mode |                                      |     |    |  |  |  |  |  |  |

| M1: Choose the ROM mo                                   | de in the Internal ROM or External I | ROM |    |  |  |  |  |  |  |

- (2). In the case of internal ROM mode, that is [M2, M1]=[0,0] or [1,0]. If any extension ROM is connected to the SH58201 address bus, when programme accesses the address above 256K byte, the SH58201's address decoder will decode to the external ROM. (In the case of internal ROM mode, the internal ROM and external ROM can be co-existed.)

- (3). It is suggested when the internal ROM mode is selected, for the build-in ROM, it can be used to store the important documents or data or password, and so on, and the external ROM usually contains the main programme.

- (4). In the case of external ROM mode, it will be unavailable to access the build-in ROM (256K byte). That is to say, in the external ROM mode, the address decoder will decodes to external ROM.(Not Access the built-in ROM)

## **Special Mode control (SPMOD)**

- (1). The SPMOD pin is used to control the function block Enabled/Disabled for the SH582xx expansion serial products.

- (2). The special mode environment is only existed in the SPMOD pin being set.(that is: SPMOD =1). And the following register would be useful.

## Special mode control register (SPMOD =1)

| ADDRESS | REGISTER | 7      | 6    | 5   | 4    | 3    | 2    | 1    | 0      | R/W    | Default |

|---------|----------|--------|------|-----|------|------|------|------|--------|--------|---------|

| \$1F04  | SPECIAL1 | PD     |      | -   | PC_H | PC_L | PB_H | PB_L | PA_H   | R/W    | 111111  |

| \$1F05  | SPECIAL2 | EXTINT | UART | WDT | REMO | -    | -    | -    | -      | R/W    | 1111    |

| \$1F0A  | CONFIG   | SPM    | -    | -   | -    | -    | -    | -    | CONFIG | R or W | 00      |

| Control bit | Function description                                                | Def     | ault    |

|-------------|---------------------------------------------------------------------|---------|---------|

|             | Special Mode: SPMOD=1                                               | SPMOD=0 | SPMOD=1 |

| PA_H        | Enable/Disable the function block of PORTA's HIGH nibble            | 1       | 1       |

|             | ( 0:disable)                                                        |         |         |

|             | Note: the use of PB_H, PC_H is the same as PA_H                     |         |         |

| PB_L        | Enable/Disable the function block of PORTB's LOW nibble             | 1       | 1       |

|             | (0:disable)                                                         |         |         |

|             | Note: the use of PC_L is the same as PB_L                           |         |         |

| PD          | Enable/Disable the function block of PORTD (0:disable)              | 1       | 1       |

| REMO        | Enable/Disable the function block of CARRIER GENERATOR              | 1       | 1       |

|             | ( 0:disable)                                                        |         |         |

| WDT         | Enable/Disable the function Block of WATCHDOG (0:disable)           | 1       | 1       |

| UART        | Enable/Disable the function Block of UART (0:disable)               | 1       | 1       |

| EXTINT      | Enable/Disable the function Block of External Interrupt (0:disable) | 1       | 1       |

- The control bit of WDT is used to turn ON/OFF Watchdog function block, there are several ways to disable the Watchdog timer.

- (1.a). Because the clock source of Watchdog timer is come from the 32.768K X'tal oscillator, hence, disable the 32.768K X'tal by setting the control bit of X32KEN (\$1F07 PWR\_SAV) as "0" will turn off the Watchdog timer clock.

- (1.b). Disable the control bit of WDT (\$1F05,SPECIAL2) can also turn off the Watchdog function.

- (2). The control bit of REMO is used to turn ON/OFF the CARRIER GENERATOR function block. If it is enabled, the remote output pin is shared with the PORTD.3.

- 10 - Ver0.13

- (3). The control bit of EXTINT is used to turn ON/OFF the External Interrupt function block. If it is enabled, the external interrupt input pin is shared with the PORTD.0.

- (4). The control bit of UART is used to turn ON/OFF the Universal Asynchonous Receiver\_Transmitter function block. If it is enabled, the transmitter output pin is shared with the PORTD.1 as well as the receiver input pin with the PORTD.2.

Configure Setting control register (\$1F0B)

|        | R/W        | Function Description         | Default           |

|--------|------------|------------------------------|-------------------|

| SPM    | Read Only  | Read the status of SPMOD Pin | rely on SPMOD pin |

| CONFIG | Write/Only | Driver the Configure LED     | 0                 |

#### Note:

- (1). For the SH582xx expansion products, some will not have the PA high nibble function or REMO. In this case, it is necessary to set properly the corresponding bit to enable or disable the relevant function. Otherwise, the SH58201 can not be used to emulate the different serial products.

- (2). Only entering the special mode situation (the SPMOD pin is connected to HIGH), the ROM and RAM size register just can be used to control the ROM size, RAM size for the different extension product.

- (3). In the Special mode: Default = enable all function.

- (4). In the SH58201 mode, all the functions are enabled.

## Configure setting method

- (1). Set the SPMOD pin to HIGH (only in the SPMOD =1, the control register of SPECIAL1, SPECIAL2 is useful.)

- (2). Set the control bit of CONFIG (\$1F0A) to HIGH. (It will turn the external LED OFF to announce the user)

"IT IS CONFIGURATION SETTING NOW, BE WAITING"

At the same time, this signal will also send to the system to permit the Configuration setting of SH58201.

- (3). Properly set the SPECIAL MODE control register of SPECIAL1, SPECIAL2 (according to the feature of NT582XX expansion series, turn ON/OFF the coordinate control bit)

- (4). Properly set the RAM and ROM size register (\$1F02, \$1F03)

- (5). Properly set the configuration setting of SH58201.

- (6). Set the control bit of CONFIG (\$1F0A) to LOW.(It will turn the external LED ON to announce the user:

- "CONFIGURATION SETTING END", To set the SPMOD pin to LOW right now. At the same time, it means that the SH58201 has finished the system configuration setting.

## RAM Size Selection (SPMOD=1)

RAM size select register

| ADDRESS | REGISTER | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     | R/W | Default |

|---------|----------|---|---|---|---|---|-------|-------|-------|-----|---------|

| \$1F02  | RAM_NO   | - | - | - | - | - | RAM.2 | RAM.1 | RAM.0 | R/W | 000     |

- (A). The SH58201 chip includes a lot of different RAM sizes. It can be used to emulate the different chips in SH582xx series by choosing a proper RAM size (SPMOD =1)

- (B). Since the different RAM size, if it is selected improperly, it won't get right result. That is to say, if the RAM size is set as 2K under the SPMOD=1, the programme accessing range will not exceed (Read/Write) the address of 2K.

| RAM.2 | RAM.1 | RAM.0 | RAM size (byte) | SPMOD=0 | SPMOD=1 |

|-------|-------|-------|-----------------|---------|---------|

| 0     | 0     | 0     | 12K             | Default | Default |

| 0     | 0     | 1     | 8K              |         |         |

| 0     | 1     | 0     | 4K              |         |         |

| 0     | 1     | 1     | 2K              |         |         |

| 1     | 0     | 0     | 1.5K            |         |         |

| 1     | 0     | 1     | 1K              |         |         |

| 1     | 1     | ×     | 0.5K            |         |         |

(C). Data RAM (program variable) can be shared with the stack. (Unit: Byte)

| RAM Size | Zero Page Available | BYTE | Stack Available | BYTE | Other(program Variable) | BYTE |

|----------|---------------------|------|-----------------|------|-------------------------|------|

| 12K      | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  | 0200h~0FFFh             | 3584 |

| IZN      | 000011~00FF11       | 230  | 010011~01FF11   | 250  | 2000h~3FFFh             | 8192 |

|          |                     |      |                 |      | 0200h~0FFFh             | 3584 |

| 8K       | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  | 2000h~2FFFh             | 4096 |

|          |                     |      |                 |      | 3000h~3FFFh (reserved)  |      |

| 4K       | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  | 0200h~0FFFh             | 3584 |

| 2K       | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  | 0200h~07FFh             | 1536 |

| 1.5K     | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  | 0200h~05FFh             | 1024 |

| 1K       | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  | 0200h~03FFh             | 512  |

| 0.5K     | 0000h~00FFh         | 256  | 0100h~01FFh     | 256  |                         |      |

**External RAM control register**

| ADDRESS | REGISTER | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 | R/W | Default |

|---------|----------|--------|---|---|---|---|---|---|---|-----|---------|

| \$1F0C  | EX RAM E | enable | - | - | - | - | - | - | - | W   | 0       |

| enable | Description                                   |

|--------|-----------------------------------------------|

| 0      | External SRAM disable (default)               |

| 1      | External SRAM enable (Pin CSB2=0; low active) |

#### Note:

This bit7 of the external RAM control register is used to control the external RAM chip select signal. If the value of EX\_RAM\_E is "0" (default), the external RAM is not available. That means the system can only access the internal RAM. At this time, the RAM BNK register (\$1F0B) is unavailable for operation.

If the value of EX\_RAM\_E is '1", the external RAM is available. That is to say, when the system RAM accessing range exceeds the relevant size (maximum: 12Kbyte) controlled by certain setting of the RAM.2~RAM.0bits, the operation of RAM reading/writing can access the external RAM automatically through proper writing the value of the RAM\_BNK register (\$1F0B). But, if the programme needs accessing the internal RAM (Range: \$2000 ~ \$3000), the EX\_RAM\_E bit must be writen to "0" again. Otherwise the accessing operation will not be executed. Therefor, the operating for this bit (enable) at \$1F0C is always available whenever the SPMOD pin is fixed to high or low.

- 12 - Ver0.13

## **ROM Size Selection (SPMOD=1)**

**ROM** size select register

| ADDRESS | REGISTER | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     | R/W | Default |

|---------|----------|---|---|---|---|---|-------|-------|-------|-----|---------|

| \$1F03  | ROM_NO   | - | - | - | - | - | ROM.2 | ROM.1 | ROM.0 | R/W | 100     |

- (A). The SH58201 chip includes a lot of different ROM sizes. It can be used to emulate the different chips in SH582xx series by choosing a proper ROM size (SPMOD =1)

- (B). Since the different ROM size, if it is selected improperly, it won't get right result.

| ROM.2 | ROM.1 | ROM.0 | ROM Size | Bank Limited | SPMOD=0 | SPMOD=1 |

|-------|-------|-------|----------|--------------|---------|---------|

| 0     | 0     | 0     | 4M       | 00 h ~ FF h  |         |         |

| 0     | 0     | 1     | 2M       | 80 h ~ FF h  |         |         |

| 0     | 1     | 0     | 1024K    | C0 h ~ FF h  |         |         |

| 0     | 1     | 1     | 512K     | E0 h ~ FF h  |         |         |

| 1     | 0     | 0     | 256K     | F0 h ~ FF h  | Default | Default |

| 1     | 0     | 1     | 128K     | F8 h ~ FF h  |         |         |

| 1     | 1     | ×     | 64K      | FC h ~ FF h  |         |         |

- (C). For the different ROM size, if it is set improperly, it won't be got right result. For instance, if the ROM size is selected 128K, in the SPMOD=1, the programme accessing (Read) won't exceed the address of 128K.

- (D). When the ROM size is above 256K byte, The system can be worked in the purely external ROM or internal and external ROM co-existed by setting the M1, M2 pins. (see in the page 10)

**External ROM control register**

|         | · · · · · · · · · · · · · · · · · · · |        |   |   |   |   |   |   |   |     |         |

|---------|---------------------------------------|--------|---|---|---|---|---|---|---|-----|---------|

| ADDRESS | REGISTER                              | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 | R/W | Default |

| \$1F0D  | EX_ROM_S                              | enable | - | - | - | - | - | - | - | W   | 0       |

| enable | Description                                                     |

|--------|-----------------------------------------------------------------|

| 0      | External ROM enable (Pin CSB0=0, CSB1=1; low active ) (default) |

| 1      | External Flash ROM enable (Pin CSB0=1, CSB1=0; low active )     |

#### Note:

- (1). When in the external ROM case (M1=1), if the program counter reads the \$C000~\$FFFF area, the CSB0 pin will always be active. That means the system CPU can only fetch codes from the external EPROM, regardless the M2 pin is fixed to high or low, regardless the value of EX\_ROM\_S is set to "1" or "0", either.

- (2). If the value of EX\_ROM\_S is "0" (default), when the PC's accessing range exceeds \$C000~\$FFFF under the external ROM case, the system can also access the external EPROM.

- (3). If the value of EX\_ROM\_S is set to "1" by program writing, when the PC's accessing range exceeds \$C000~\$FFFF, the system must access the external FLASH ROM automatically (Pin CSB1=0/CSB0=1, low active), regardless M1 is fixed to high or low.

- 13 - Ver0.13

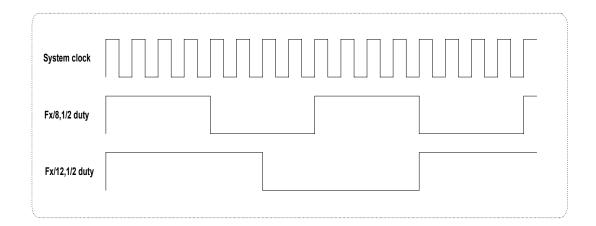

## **Dual Clock Selection**

The SH58201 offers dual clock selection one for RC/Crystal oscillation, the other is 32.768K oscillator for real time clock. At the same time, MCU's operating speed is also software programmable, it is controlled by setting the following register.

System control register

| ADDRESS | REGISTER | 7   | 6   | 5   | 4   | 3   | 2 | 1 | 0 | R/W | Default |

|---------|----------|-----|-----|-----|-----|-----|---|---|---|-----|---------|

| \$1F06  | SYS_CTRL | D.7 | D.6 | D.5 | D.4 | D.3 | - | - | - | R/W | 00000   |

| D.7     | System Clock Source select bit                                    |  |  |  |

|---------|-------------------------------------------------------------------|--|--|--|

| 0       | Select system clock source from RC/Crystal                        |  |  |  |

| 1       | Select system clock source from time base clock (32.768K Crystal) |  |  |  |

| D.6 D.5 | When D.7=0, this bit is used to select clock source frequency     |  |  |  |

| 0 0     | F <sub>osc</sub> = 4M ( or 3.58M)                                 |  |  |  |

| 0 1     | F <sub>osc</sub> = 8M                                             |  |  |  |

| 1 0     | F <sub>osc</sub> = 12M                                            |  |  |  |

| 1 1     | F <sub>osc</sub> = 16M                                            |  |  |  |

| D.4           | D.3                                                  | Prescaler |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| 0             | 0                                                    | /8        |  |  |  |  |  |  |  |

| 0             | 1                                                    | /4        |  |  |  |  |  |  |  |

| 1             | 1 × /2                                               |           |  |  |  |  |  |  |  |

| When D.7=0, C | When D.7=0, CPU clock is fetched from this prescaler |           |  |  |  |  |  |  |  |

#### Note:

- (A). System oscillator component must be connected and it can be RC or crystal type according to the "XROPT" pin state(pad option). As to the time base clock,32768 Hz,Crystal oscillator may be connected or not depended on the application condition.

- (B). When the 32.768K crystal is connected, the system register \$1F07 "X32KEN" (see the Next page) should be set to "1" to enable 32.768KHz crystal oscillator.

- (C). The CPU clock is 32768Hz when bit7(D.7) is set to "1". Normally, this situation just happened at "STANDBY" mode to keep LCD display in regular.

- (D). When 32.768k is used as system clock source, that is D.7=1, then D[6:3] are no more effected.

- (E). d[7:3]=00h(default). That means "Clock Source is not from 32.768KHz, F<sub>osc</sub>=4MHz, and the Prescaler = /8 ", So the system will work on 500K Hz.

### Caution:

The Tone frequency generator circuit of Melody will vary in the different operating voltage, by properly setting this bit, it will be suitable for the different application environment.

- 14 - Ver0.13

#### **Low Power Detection**

#### **Function of LPD circuit**

The low power detection (LPD) is used to monitor the supply voltage and generate an internal flag for indicating the battery energy having been much lower that may damage the operation status of system. The appearance of low voltag signal can remind user to replace the battery.

## LPD operation

When a SH58201 operates in the 3V power supply condition, the LPD voltage is defined as 2.5V. Therefore, if the power supply voltage is any lower than 2.5V, the LPD circuit must detect out and then set the flag (bit0 of the LPD\_CTRL) as "1".

| Electrical Property | $V_{\scriptscriptstyle { m DD}}$ | $V_{LPD}$ |

|---------------------|----------------------------------|-----------|

|                     | 3.0V                             | 2.5V      |

LPD control register

| ADDRESS | REGISTER | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0   | R/W | Default |

|---------|----------|--------|---|---|---|---|---|---|-----|-----|---------|

| \$1F09  | LPD_CTRL | LPD_EN | - | - | - | - | - | - | LPD | R/W | 00      |

| Ī | LPD | Description                                                                       | R/W |

|---|-----|-----------------------------------------------------------------------------------|-----|

| Ī | 1   | "1" means the CPU detects out the $V_{DD} \leq V_{LPD}$ ( 0: $V_{DD} > V_{LPD}$ ) | R   |

| LPD_EN | Description                       | R/W |

|--------|-----------------------------------|-----|

| 1      | LPD enable ( otherwise: disable ) | W   |

- (1). Enable the LPD detection by set LPD\_EN =1, Default: LPD\_EN = 0 (disable)

- (2). If the LPD is enabled, the flag (LPD) will be set to "1" when the LPD circuit has detected out  $V_{DD} \le V_{LPD}$ . In this case, the programme maybe turn into the LPD service subroutine to indicate that it's time to replace the supply battery.

- 15 - Ver0.13

# **Power Saving Control**

To reduce power consumption, this chip offers 2 power-saving steps:

- (1). The 65C02 power saving method: STOP instruction

- (2). Power saving register control: to control ON/OFF the 32.768KHz oscillator

Power Saving register:

| ADDRESS | REGISTER | 7 | 6 | 5 | 4 | 3 | 2  | 1      | 0     | R/W | Default |

|---------|----------|---|---|---|---|---|----|--------|-------|-----|---------|

| \$1F07  | PWR_SAV  | - | - | - | - | - | -  | X32KEN | SPDUP | R/W | 11      |

| \$1F08  | RESET    | - | - | - | - | - | WT | WD     | IPA   | R   | 000     |

| Control bit | Description                                                                                                                                                   | Default     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| X32KEN      | Turn ON/OFF 32.768K crystal. If CPU & Crystal is turned off at the same time, the system will be shut down. That is, only the I/O PortA can wake up the chip. | 1 (Turn-ON) |

| SPDUP       | Speed up the 32K Oscillator in the CPU turn-on status.(1:turn on the function) It should be noticed that turnning off the function when the CPU is stable.    | 1 (Turn-ON) |

**RESET** (reset status register):

| WT | WD | IPA | Description                                           |

|----|----|-----|-------------------------------------------------------|

|    |    | 1   | System was reset by External trigger(PORTA interrupt) |

|    | 1  |     | System was reset by Watchdog                          |

| 1  |    |     | System was reset by wake up timer                     |

#### Note:

- (1). Once the operation of reading this reset status register is occured, the 3-bits will be immediately cleared on the next ph0 rising edge. This register can be used to detect which source has caused the system reset. After reading operation, the register's status will be cleared so it can be ready for next reset happening. In addition, the most important thing is that pin RSTB causing the system reset will clear all status of this register firstly and immediately. (6502 power on reset vector is located at the \$FFFC ~\$FFFD)

- (2). Before STOP instruction is commanded in the program, if the 32.768K oscillator has been turn off, there is only one way to wake the CPU up---that is: PORTA interrupt.

- (3). Before STOP instruction is commanded in the program, if the 32.768K oscillator is still turned on, there will have three ways to wake the CPU up—they are: Wake up timer, Watchdog timer, and the PortA interrupt.

- (4) When the system is in the power saving condition (after executing STOP instruction), the PORTA interrupt can wake up CPU. At this time, there are two types of interrupt provided for different applications. One is low level triggering (default) as well as the other is edge triggering (falling active). The different function is selected by the status of the IPA mode control register (IPA\_MODE) bit0.

IPA mode control register

| ADDRESS | REGISTER | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0          | R/W | Default |

|---------|----------|---|---|---|---|---|---|---|------------|-----|---------|

| \$1F20  | IPA_MODE |   | - | - | - | - | - | - | Edge/Level | W   | 0       |

| Edge/Level | Description                                             |

|------------|---------------------------------------------------------|

| 0          | PORTA interrupt level triggering (low active) (default) |

| 1          | PORTA interrupt edge triggering (falling edge)          |

- 16 - Ver0.13

# Interrupt-NMI & IRQ

#### **NMI** enable

| ADDRESS | REGISTER | 7      | 6 | 5 | 4 | 3 | 2     | 1     | 0     | R/W | Default |

|---------|----------|--------|---|---|---|---|-------|-------|-------|-----|---------|

| \$1F10  | NMI_IE   | NMISR1 | - | - | - | - | NMISR | NMIST | NMIPA | R/W | 0000    |

- (A). The register is used to **decide** which NMI source will be activated.(Non-Maskable Interrupt).

- (B). 0: Disable (default)

1: Enable (If the bit is set to "1", that means the relevant event can interrupt CPU.)

|   | (11 41.0 511.0 001.10 |       | over carring con            |

|---|-----------------------|-------|-----------------------------|

| ſ | NMISR1                | NMIPA | DESCRIPTION                 |

| ſ | -                     | 1     | Input PORTA trigger         |

| ſ | 1                     | -     | SR1 Counter counts overflow |

NMI request flag register:

| ADDRESS | REGISTER | 7      | 6 | 5 | 4 | 3 | 2      | 1      | 0     | R/W | Default |

|---------|----------|--------|---|---|---|---|--------|--------|-------|-----|---------|

| \$1F11  | NMI_IF   | NMISR1 | - | - | - | - | NMISRI | NMISTI | NMIPA | R   | 0000    |

- (A). The register is used to **record** NMI request status. For Example, if the NMI source (SR1) counts overflow from FFFFh to 0000h, the bit7 of this register will be set. In this time, if the coordinate NMI\_IE is set to "1", the NMI will be triggered, and the program counter will point to the NMI vector.(6502 NMI vector is located at the \$FFFAh~\$FFFBh)

- (B). When the operation of reading this register, the status of this register will be cleared right now.

| 0=inactive | (the Counter don't count overflow yetDefault)                       |

|------------|---------------------------------------------------------------------|

| 1=active   | (the Counter counts overflow from \$FF to \$00, NMI flag activates) |

IRQ enable register:

| ADDRESS | REGISTER | 7      | 6     | 5             | 4     | 3     | 2     | 1     | 0     | R/W | Default  |

|---------|----------|--------|-------|---------------|-------|-------|-------|-------|-------|-----|----------|

| \$1F12  | IRQ_IE   | IRQSR2 | IRQWT | <b>IRQEXT</b> | IRQPB | IRQPA | IRQT2 | IRQT1 | IRQT0 | R/W | 00000000 |

- (A). The register is used to **decide** which IRQ source will be triggered (IRQ: Interrupt Request).

- (B). 0: Disable (default)

1: Enable (If the bit is set to "1", that means the relevant event can interrupt CPU.)

| IRQSR2 | IRQWT                         | IRQEXT | <b>IRQPB</b> | IRQPA | IRQT2 | IRQT1 | IRQT0                       | DESCRIPTION             |  |  |  |

|--------|-------------------------------|--------|--------------|-------|-------|-------|-----------------------------|-------------------------|--|--|--|

|        |                               |        |              |       |       |       | 1                           | Timer0 count overflow   |  |  |  |

|        |                               |        |              |       |       | 1     |                             | Timer1 count overflow   |  |  |  |

|        |                               |        |              |       | 1     |       |                             | Timer2 count overflow   |  |  |  |

|        |                               |        |              | 1     |       |       |                             | Input PORTA trigger     |  |  |  |

|        |                               |        | 1            |       |       |       |                             | Input PORTB trigger     |  |  |  |

|        |                               | 1      |              |       |       |       |                             | external interrupt      |  |  |  |

|        | 1                             |        |              |       |       |       |                             | Wake up timer overflows |  |  |  |

| 1      | 1 SR2 Counter counts overflow |        |              |       |       |       | SR2 Counter counts overflow |                         |  |  |  |

|        | 0: Disable (Default)          |        |              |       |       |       |                             | 1: Enable               |  |  |  |

IRQ request flag

| ADDRESS | REGISTER | 7      | 6     | 5      | 4     | 3     | 2     | 1     | 0     | R/W | Default  |

|---------|----------|--------|-------|--------|-------|-------|-------|-------|-------|-----|----------|

| \$1F13  | IRQ_IF   | IRQSR2 | IRQWT | IRQEXT | IRQPB | IRQPA | IRQT2 | IRQT1 | IRQT0 | R   | 00000000 |

- (A). The register is used to record individually IRQ request flag, simply as NMI\_IF.

- (B). The IRQ will be triggered when the IRQ\_IE.x=1 and the corresponding bit of IRQ\_IF=1 together. At this time, IRQ will activate and the program counter will start from the IRQ vector address. (65C02's IRQ vector is defined in \$FFFEh ~ \$FFFFh)

- (C). After IRQ occured, the relevant bit of IRQ request flag was set to "1". If the IRQ\_IF flag won't be cleared, the IRQ will be triggered immediately again (because the IRQ\_IE.x was still enabled). The unpredicted thing will be happened (Ex: stack overflow). Therefore, the IRQ request (IRQ\_IF) must be cleared immediately by reading the IRQ\_IF at the beginning of the IRQ interrupt service subroutine.

#### Note:

- (A). When NMI enable register (NMI\_IE) is set to "1", the SH58201 can service multi-level interrupt. However, there is only one NMI vector for 65C02, therefore, it is necessary to reset the NMI\_IF register if there are several (NMI) interrupt sources shared in the program. In this situation, it is important to store the value of NMI\_IF into the program variable before clearing NMI\_IF flag. Then, it is available to judge the (NMI) interrupt source causing the NMI.

- (B). If the corresponding NMI IE.x is set to "0", the NMI IF.x will not be set to "1" while NMI source is coming up.

- (C). Interrupt priority: NMI >> IRQ

#### Example:

| MAIN F  | PROG   | ISR        |                      |

|---------|--------|------------|----------------------|

| <br>LDA | IRQ_IF | LDA<br>STA | IRQ_IF<br>wSAVE FLAG |

| LDA     | · · ·  |            |                      |

| STA     | IRQ_IE |            |                      |

| <br>••  |        |            |                      |

this programme can be triggered by timer0 interrupt. When TM0 counts from FFH→00H the PC. will jump to Interrupt Service Routine.

## **Timer / Counter**

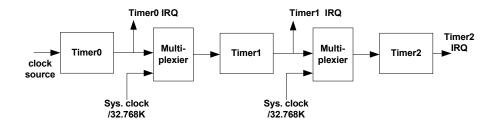

SH58201 has several timers: Timer0, Timer1, Timer2, Wake-up timer and Watchdog timer.

## Timer0

| ADDRESS | REGISTER | 7     | 6      | 5  | 4  | 3     | 2     | 1     | 0     | R/W | Default  |

|---------|----------|-------|--------|----|----|-------|-------|-------|-------|-----|----------|

| \$1F14  | TM0_CTRL | BD/TM | T/RCLK | -  | -  | TM0.3 | TM0.2 | TM0.1 | TM0.0 | W   | 00000    |

| \$1F15  | TM0COUNT | T7    | T6     | T5 | T4 | T3    | T2    | T1    | T0    | R/W | 00000000 |

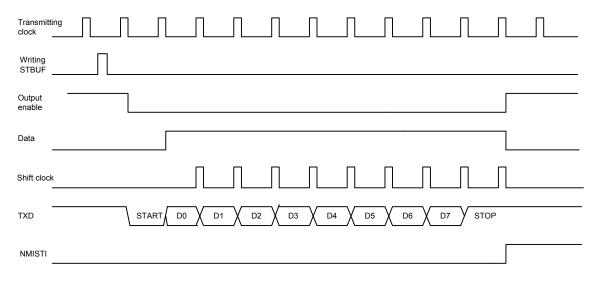

- (1). Timer0 is a 8 bit up-count timer. When it counts overflow from FFh to 00h, it will generate a timer IRQ request (and set the coordinate IRQ request flag IRQT0=1). If the corresponding bit of IRQ\_IE is set to "1" then timer0 interrupt will be activated.

- (2). The clock source of Timer0 can be system clock or external crystal (32.768K).

- (3). Timer0 starts counting when the TM0COUNT is setting.

TM0\_CTRL(timer0 control register):

| L(uniero control | register).                                                     |

|------------------|----------------------------------------------------------------|

| BD/TM            | Timer0 function control                                        |

| 0                | General timer (default)                                        |

| 1                | Timer0 used as Baud rate generator                             |

| T/RCLK           | Transmit/Receive clock selection (available only when BD/TM=1) |

| 0                | Timer0 overflow used as receiver clock (default)               |

| 1                | Timer0 overflow used as transmitter clock                      |

| TM0.3            | Control timer0 enable or disable                               |

| 0                | Disable                                                        |

| 1                | Enable                                                         |

| TM0.2            | Control auto reload function                                   |

| 0                | Disable                                                        |

| 1                | Enable (always enable when BD/TM=1)                            |

|       |       | De                                                 | scription |                     |                 |                                    |  |

|-------|-------|----------------------------------------------------|-----------|---------------------|-----------------|------------------------------------|--|

|       |       | Timer 0 clock source                               | from      |                     | TM0 divisor     |                                    |  |

| TM0.1 | TM0.0 | System oscillator<br>(assume 8MHz, and /2<br>mode) | Pre-scale | Timer 0 clock input | (TM0COUNT)      | Frequency from TM0                 |  |

| 0     | 0     | System clock (4MHz)                                | /65536    | 61.04Hz             | 1(FF) ~ 256(00) | 61.04~0.24Hz                       |  |

| 0     | 1     | System clock (4MHz)                                | /2048     | 1953.13Hz           | 1(FF) ~ 256(00) | 1953.13~7.66Hz                     |  |

| 1     | 0     | System clock (4MHz)                                | /2        | 2MHz                | 1(FF) ~ 256(00) | 2M~7843.14Hz                       |  |

| 1     | 1     | 32.768KHz or 31.25KHz                              | /8        | 4096Hz or 3096.25Hz | 1/66/26/1001    | 4096.00~16.06Hz or 3096.25~12.14Hz |  |

- (A). TM0.1 and TM0.0 are used to decide the pre-scale values.

- (B). If the external clock32.768K) is not connected to the system, then TM0.1=1 and TM0.0=1 will cause the Timer0 to change the source from 32.768KHz to the system clock, 31.25K.

- (C). If BD/TM=1, TM0.1 and TM0.0 will choose the different prescaler values which will be described in detail as follow.

- 19 - Ver0.13

|       |       | De                                                 | scription |                     |                           |                    |  |

|-------|-------|----------------------------------------------------|-----------|---------------------|---------------------------|--------------------|--|

|       |       | Timer 0 clock source                               | from      |                     | TMO divisor               | Frequency from TM0 |  |

| TM0.1 | TM0.0 | System oscillator<br>(assume 8MHz, and /2<br>mode) | Pre-scale | Timer 0 clock input | TM0 divisor<br>(TM0COUNT) |                    |  |

| 0     | 0     | System clock (4MHz)                                | /1        | 4MHz                | 1(FF) ~ 256(00)           | 4M~15686.28        |  |

| 0     | 1     | System clock (4MHz)                                | /2        | 2MHz                | 1(FF) ~ 256(00)           | 2M~7843.14Hz       |  |

| 1     | ×     | System clock (4MHz)                                | /16       | 250KHz              | 1(FF) ~ 256(00)           | 250K~980.39Hz      |  |

### TM0COUNT (timer0 counter register):

- (A). In the read mode: The counter value can be accessed. But due to the asynchronous counting characteristics, the reading value may not be accurate! It must be careful for processing the value accessed from Timer0.

- (B). In the write mode: This counter value can be programmed as preload counter. Writing data to this register can set initial counting value, thus it can change the peroid of the timer's overflowing.

## Example:

If the clock source=system (4M), prescale=65536 (TM0.1=0, TM0.0=0), TM0\_COUNT=128, then Timer0 frequency={4000000 / (65536)} / {256-128}=0.48 Hz

When Timer0 is used as Baud rate generator (BD/TM=1), if oscillator frequency is 8MHz and in 1/2 mode (system clock=4MHz), prescaler=1, TM0\_COUNT=48, then

the Baud rate (timer0's overflow)= {4000000 / 16} / {256-48}=1201.92 Hz According to 1200 baud rate, the deviation is ( {1201.92-1200}/1200 ) 0.16%.

- If: (system clock=4MHz), prescaler=1, TM0\_COUNT=243, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-243}= 19230.77 Hz the relevant deviation is 0.16%

- If: (system clock=4MHz), prescaler=1, TM0\_COUNT=230, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-230}= 9615.38 Hz the relevant deviation is 0.16%

- If: (system clock=4MHz), prescaler=1, TM0\_COUNT=204, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-204}= 4807.69 Hz the relevant deviation is 0.16%

- If: (system clock=4MHz), prescaler=1, TM0\_COUNT=152, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-152}= 2403.85 Hz the relevant deviation is 0.16%

#### Caution:

When the timer is used as baud rate generator, Timer0 and Timer1 can not be used in the same transmitter or receiver clock, simultaneously. Otherwise, the UART system will not operate correctly.

- 20 - Ver0.13

## Timer1

| ADDRESS | REGISTER | 7     | 6      | 5  | 4  | 3     | 2     | 1     | 0     | R/W | Default  |

|---------|----------|-------|--------|----|----|-------|-------|-------|-------|-----|----------|

| \$1F16  | TM1_CTRL | BD/TM | T/RCLK | -  | -  | TM1.3 | TM1.2 | TM1.1 | TM1.0 | W   | 010000   |

| \$1F17  | TM1COUNT | T7    | T6     | T5 | T4 | T3    | T2    | T1    | T0    | R/W | 00000000 |

## TM1\_CTRL (timer1 control register):

| BD/TM  | Timer1 function control                                        |

|--------|----------------------------------------------------------------|

| 0      | General timer (default)                                        |

| 1      | Timer1 used as Baud rate generator                             |

| T/RCLK | Transmit/Receive clock selection (available only when BD/TM=1) |

| 0      | Timer1 overflow used as receiver clock (default)               |

| 1      | Timer1 overflow used as transmitter clock                      |

| TM1.3  | Control timer1 enable or disable                               |

| 0      | Disable                                                        |

| 1      | Enable                                                         |

| TM1.2  | Control auto reload function                                   |

| 0      | Disable                                                        |

| 1      | Enable (always enable when BD/TM=1)                            |

| TM4 4       | TM4 0                          |                     | escription |                     | TM1 divisor     | Frequency from TM1                   |

|-------------|--------------------------------|---------------------|------------|---------------------|-----------------|--------------------------------------|

| 1 101 1 . 1 | M1.1 TM1.0 Timer1 clock source |                     | Pre-scale  | Timer 1 clock input | (TM1COUNT)      | Frequency from TWT                   |

| 0           | 0                              | Timer0 overflow     |            |                     | 1(FF) ~ 256(00) |                                      |

| 0           | 1                              | System clock (4MHz) | /2048      | 1953.13Hz           | 1(FF) ~ 256(00) | 1953~7.66Hz                          |

| 1           | 0                              | 32.768K or 31.25K   | /16        | 2048Hz or 1953.13Hz | 1(FF) ~ 256(00) | 2048 ~ 8.03Hz or<br>1935.13 ~ 7.66Hz |

| 1           | 1                              | 32.768K or 31.25K   | /2         | 16384Hz or 15625Hz  | 1(FF) ~ 256(00) | 16294 - 64 25Uz or                   |

- (A). If the clock source of Timer1 comes from Timer0, a new preload value of timer1 for getting various frequency won't be loaded into the counter until TM0 overflows. Actually, it is available to change the contents of Timer0 to get a desired frequency from TM1 without preload a new value into TM1.

- (B). If the external clock (32.768K) is not connected to the system, then TM1.1=1 and TM1.0=1 will cause the Timer1 to change the source from 32.768KHz to the system clock, 31.25K.

- (C). If BD/TM=1, TM1.1 and TM1.0 will choose the different prescaler values from that mentioned above. The difference is described in detail as follow.

|       |       | De                                                 | scription |                     |                 |                    |  |

|-------|-------|----------------------------------------------------|-----------|---------------------|-----------------|--------------------|--|

|       |       | Timer 1 clock source                               | from      |                     | TM1 divisor     | Frequency from TM1 |  |

| TM1.1 | TM1.0 | System oscillator<br>(assume 8MHz, and /2<br>mode) | Pre-scale | Timer 1 clock input | (TM1COUNT)      |                    |  |

| 0     | 0     | System clock (4MHz)                                | /1        | 4MHz                | 1(FF) ~ 256(00) | 4M~15686.28        |  |

| 0     | 1     | System clock (4MHz)                                | /2        | 2MHz                | 1(FF) ~ 256(00) | 2M~7843.14Hz       |  |

| 1     | ×     | System clock (4MHz)                                | /16       | 250KHz              | 1(FF) ~ 256(00) | 250K~980.39Hz      |  |

- 21 - Ver0.13

# TM1COUNT (timer1 count register):

- (A). In the read mode: The counter value can be accessed. But due to the asynchronous counting characteristics, the reading value may not be accurate! It must be careful for processing the value accessed from Timer1.

- (B). In the write mode: This counter value can be programmed as preload counter. Writing data to this register can set initial counting value, thus it can change the peroid of the timer's overflowing.

#### Example:

If the clock source=timer0, system clock=(4M), prescale=2048(TM0.1=0, TM0.0=1), TM0\_COUNT=128, TM1\_COUNT= 64, Timer1 frequency={[4000000 /(2048)] / [256-128] } / [256-64] =0.08 Hz

When Timer1 is used as Baud rate generator (BD/TM=1), if oscillator frequency is 8MHz and in 1/2 mode (system clock=4MHz), prescaler=16, TM1\_COUNT=48, then the Baud rate (timer1's overflow)= {4000000 / 16} / {256-48}=1201.92 Hz

According to 1200 baud rate, the deviation is ( {1201.92-1200}/1200 ) 0.16%.

- If: (system clock=4MHz), prescaler=1, TM1\_COUNT=243, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-243}= 19230.77 Hz the relevant deviation is 0.16%

- If: (system clock=4MHz), prescaler=1, TM1\_COUNT=230, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-230}= 9615.38 Hz the relevant deviation is 0.16%

- If: (system clock=4MHz), prescaler=1, TM1\_COUNT=204, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-204}= 4807.69 Hz the relevant deviation is 0.16%

- f: (system clock=4MHz), prescaler=1, TM1\_COUNT=152, then the Baud rate (timer0's overflow)= {4000000 / 16} / {256-152}= 2403.85 Hz the relevant deviation is 0.16%

## Caution:

When the timer is used as baud rate generator, Timer0 and Timer1 can not be used in the same transmitter or receiver clock, simultaneously. Otherwise, the UART system will not operate correctly.

- 22 - Ver0.13

## Timer2

| ADDRESS | REGISTER | 7  | 6  | 5  | 4  | 3  | 2     | 1     | 0     | R/W | Default  |

|---------|----------|----|----|----|----|----|-------|-------|-------|-----|----------|

| \$1F18  | TM2_CTRL | -  | -  | -  | -  | -  | TM2.2 | TM2.1 | TM2.0 | W   | 000      |

| \$1F19  | TM2COUNT | T7 | T6 | T5 | T4 | T3 | T2    | T1    | T0    | R/W | 00000000 |

## TM2\_CTRL (timer2 control register):

| TM2.2 | Control timer2 enable or disable |

|-------|----------------------------------|

| 0     | Disable                          |

| 1     | Enable                           |

| TM2.1 | Control auto reload function     |

| 0     | Disable                          |

| 1     | Enable                           |

| TM2.0   | De                       | TM2 divisor | Frequency           |                 |                                  |

|---------|--------------------------|-------------|---------------------|-----------------|----------------------------------|

| 11012.0 | Timer2 clock source from | Pre-scale   | Timer 2 clock input | (TM2COUNT)      | from TM2                         |

| 0       | Timer1 overflow          |             |                     | 1(FF) ~ 256(00) |                                  |

| 1       | 32.768K or 31.25K        | /16         | 2048Hz or 1953.13Hz | 1(FF) ~ 256(DD) | 2048~8.03Hz or<br>1953.13~7.66Hz |

- (A). If the clock source of Timer2 comes from timer1, a new preload value of TM2 for getting various frequency won't be loaded into the counter until TM1 overflows. Actually, it is available to change the contents of Timer1 to get a desired frequency from TM2 without preload a new value into TM2.

- (B). If the external clock (32.768K) is not connected to the system, then TM2.0=1 will cause the Timer2 to change the source from 32.768KHz to the system clock, 31.25K.

## TM2COUNT (timer2 count register):

- (A). In the read mode: The counter value can be accessed. But due to the asynchronous counting characteristics, the reading value may not be accurate! It must be careful for processing the value accessed from Timer2.

- (B). In the write mode: This counter value can be programmed as preload counter. Writing data to this register can set initial counting value, thus it can change the peroid of the timer's overflowing.

Timer cascade block diagram

- 23 - Ver0.13

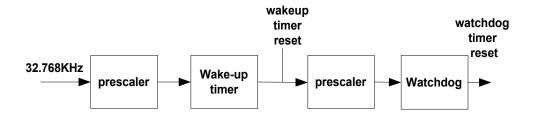

## Wakeup timer

| ADDRESS | REGISTER | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     | R/W | Default |

|---------|----------|---|---|---|---|---|---|-------|-------|-----|---------|

| \$1F1A  | WKT_CTRL | - | - | - | - | - | - | WKT.1 | WKT.0 | W   | 00      |

(A). The clock source of wakeup timer is 32.768K. It can be derived a different wake-up period by setting the WKT\_CTRL register. If the associated bit of IRQ.IE (bit6) is set to "1", it will trigger the IRQ of wakeup timer when it counts overflow.

| WKT.1 | WKT.0 | Timer-out period |

|-------|-------|------------------|

| 0     | 0     | 0.25(sec)        |

| 0     | 1     | 0.5(sec)         |

| 1     | 0     | 1(sec)           |

| 1     | 1     | 2(sec)           |

(B). If the external crystal (32.768KHz) is not connected to the system or the oscillator is disabled (bit 1 of PWR\_SAV=0), the Wakeup timer will be disabled either.

## Watch dog timer (WDT)

WDT\_RS T(watchdog reset register):

| ADDRESS | REGISTER | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | R/W |

|---------|----------|---|---|---|---|---|---|---|---|-----|

| \$1F1B  | WDT_RST  | - | - | - | - | - | - | - | - | W   |

- (A). The clock source of Watchdog timer is cascaded from wakeup timer. The Watchdog timer is designed for preventing a software malfunction or sequence jumping to an unknown location causing unpredictable results. It can be disabled by entering special mode (using SPMOD pin). If it is disabled, all executing for WDT will result in no operation.

- (B). The period of watchdog timer is four times the wakeup timer. If the WDT is enabled, an overflow of Watchdog timer under the operation mode must enforce the system to create a "RESET" status. Therefore, for preventing it's timing out and generating a device RESET condition, it is necessary to write any data to the WDT\_RST register.

- The period of watchdog timer =  $4 \times (the period of wakeup timer)$

- (C). If the external crystal (32.768KHz) is not connected to the system or the oscillator is disabled (bit 1 of PWR\_SAV=0), the Watchdog timer will be disabled either.

#### The cascade block diagram of Wakeup timer, Watchdog timer is as following:

- 24 - Ver0.13

## I/O Port

The SH58201 provides 16 bits I/O (PA, PB), 8 O/P only port. (PC) and 1 special purpose I/O (PD)

# PORT pull up control

- (1). The pull-up devices are controlled by the port data registers (PA and PB) of each port. Hence, setting "1" to the relevant bit to turn ON the pull-up MOS individually.

- (2). Internal pull-up MOS is only used in the INPUT mode.

## Example:

If bit7 and bit2 of PORTA internal pull up are desired,

Step1. Setting #10000100b to the PORTA control register (input mode).

Step2. Setting #10000100b to the PORTA data register.

## PORTA control register (bi-directional I/O):

|         |          |       | <b>/</b> - |       |       |       |       |       |       |     |          |

|---------|----------|-------|------------|-------|-------|-------|-------|-------|-------|-----|----------|

| ADDRESS | REGISTER | 7     | 6          | 5     | 4     | 3     | 2     | 1     | 0     | R/W | Default  |

| \$1F21  | PA       | PA.7  | PA.6       | PA.5  | PA.4  | PA.3  | PA.2  | PA.1  | PA.0  | R/W | 11111111 |

| \$1F22  | PAC      | PAC.7 | PAC.6      | PAC.5 | PAC.4 | PAC.3 | PAC.2 | PAC.1 | PAC.0 | W   | 11111111 |

## PAC (PORTA control register):

| PAC.[7~0] | Setting PA as Input /Output (all bit programmable) |

|-----------|----------------------------------------------------|

| 1         | Set PORTA.x as input buffer (default)              |

| 0         | set PORTA.x as output buffer                       |

# PA (PORTA data register): The data output or input buffers.

## PORTB control register (bi-directional I/O):

| ADDRESS | REGISTER | 7    | 6    | 5    | 4    | 3    | 2    | 1     | 0     | R/W | Default  |

|---------|----------|------|------|------|------|------|------|-------|-------|-----|----------|

| \$1F23  | PB       | PB.7 | PB.6 | PB.5 | PB.4 | PB.3 | PB.2 | PB.1  | PB.0  | R/W | 11111111 |

| \$1F24  | PBC      | -    | -    | -    | -    | -    | -    | PBC.H | PBC.L | W   | 11       |

## PBC (PORTB control register):

| PBC.H | PBC.L | Setting PB high nibble and low nibble as Input /Output               |

|-------|-------|----------------------------------------------------------------------|

| ×     | 1     | Set PB's low nibble as input ports (0: low nibble as output ports)   |

| 1     | ×     | Set PB's high nibble as input ports (0: high nibble as output ports) |

## PB (PORTB data register): The data output or input buffers

PC(PORTC data register): (Output only)

| ADDRESS | REGISTER | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | R/W | Default  |

|---------|----------|------|------|------|------|------|------|------|------|-----|----------|

| \$1F25  | PC       | PC.7 | PC.6 | PC.5 | PC.4 | PC.3 | PC.2 | PC.1 | PC.0 | W   | 00000000 |

- 25 - Ver0.13

PORTD control register (bi-directional I/O):

| ADDRESS | REGISTER | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | R/W | Default  |

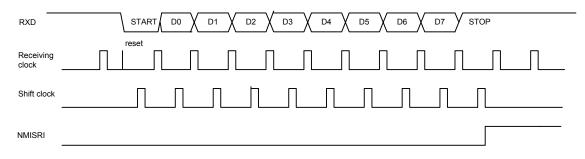

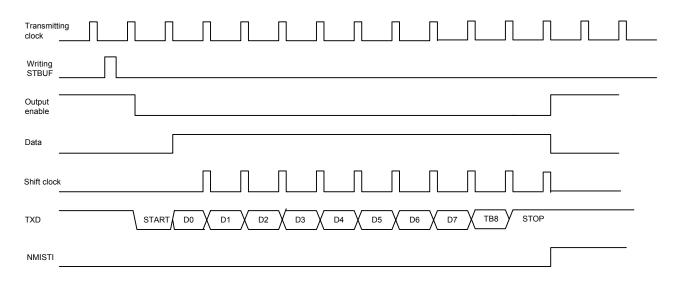

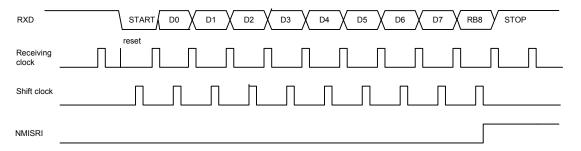

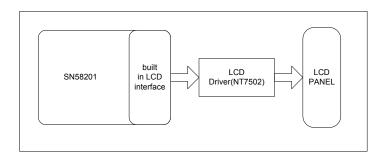

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-----|----------|