# SH93422

## Caller ID Controller with LCD driver

Preliminary 1.1

#### **Features**

- Memory

- ROM: 14K x 10 bits

Includes:

Program code

Character/Graphic pattern

• RAM: 3328 x 4 bits

Includes:

RAM mapped control registers

Memory registers

Stack

LCD memory

Data memory

- Subroutine nesting

- 16-level subroutine nesting

- LCD Controller/Driver

- 16 commons x 40 segments

- Duty option: 1/8, 1/16

- Bias option: 1/4, 1/5

- External contrast control

- · 16-level contrast control with external adjustment

- Ring signal regulation

- Built-in ring signal regulator

- FSK demodulator

- Compatible with Bell 202 and ITU-T V.23

- Keyboard

- 4 scan lines maximum

- Battery-low detection

- 4-level detection for battery-low

- I/O Pins

- 1 input / LED driver pin

- 11 general I/O pins

- 8 I/O pins shared with LCD common pins

- 16 I/O pins shared with LCD segment pins

#### ■ DTMF Generator

- · Built-in low distortion DTMF generator

- Interrupts

- 10 interrupts are available

- Beeper

- 4 options of frequency for each CPU speed

- Timers/Counters

- One 8-bit Watch Timer/Counter (driven by a standard 32.768KHz crystal oscillator)

- One 8-bit programmable Timer/Counter with external clock option

- One 8-bit programmable Timer

- One 12-bit programmable Timer

- Power-down modes

- Stop mode (CPU stop with main oscillator off)

- Halt mode (CPU stop with main oscillator on)

- Dual Oscillators System

- Main oscillator frequency (Fmain): 3.579545MHz crystal/ceramic oscillator

- Watch oscillator frequency (Fwatch): 32.768KHz crystal oscillator

- Instruction Execution Time

- $1.1\mu s$ ,  $2.2\mu s$  or  $4.4\mu s$  (Fmain = 3.58MHz)

- Power System

- · Operating voltage range:

For CPU: 2.4V to 5.5V

For FSK demodulator: 3.5V to 5.5V

• CPU Standby current: 3μA typical for 3V

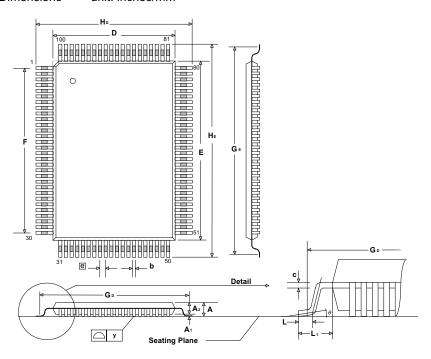

- Package Type

- 100-pin QFP package

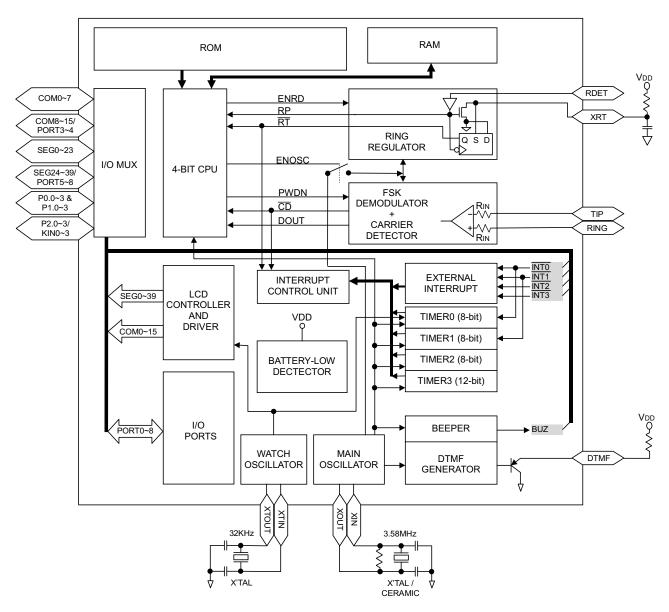

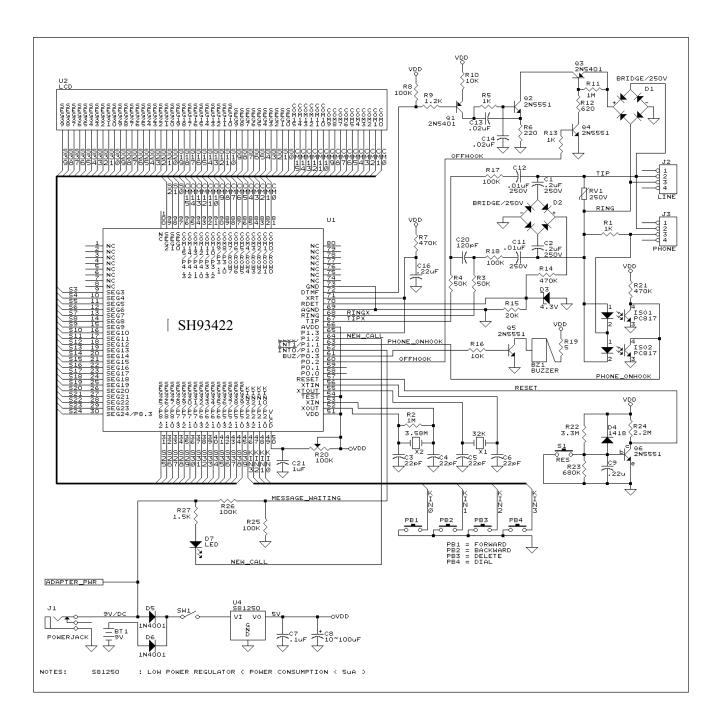

### **General Description**

This chip is a single-chip CMOS 4-bit micro-controller that dedicates to serve the telephone calling identification. To achieve the best performance, it is integrated with one real time clock, two 8-bit timers, one 12-bit Timer, FSK demodulator, Ring signal regulator, Battery-low detector, DTMF generator and 16 x 40 LCD driver. Up to 36 pins of this chip can be specified as a general I/O. The built-in

DTMF generator can provide the call back service. Ten interrupt vectors provide rapid response to internal and external events. Ring signal regulator can work even in STOP mode. Furthermore, it also offers two power consumption modes (STOP and HALT) for energy saving in idle condition.

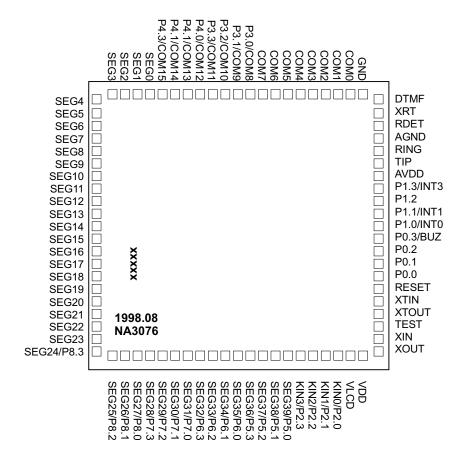

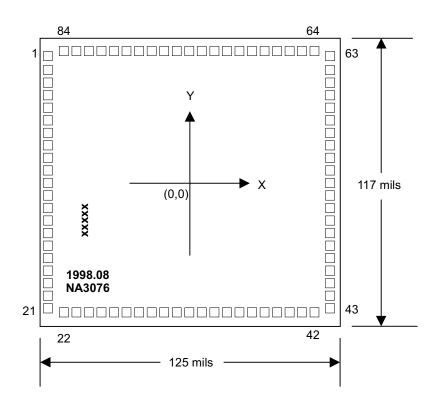

### **Pad Configuration**

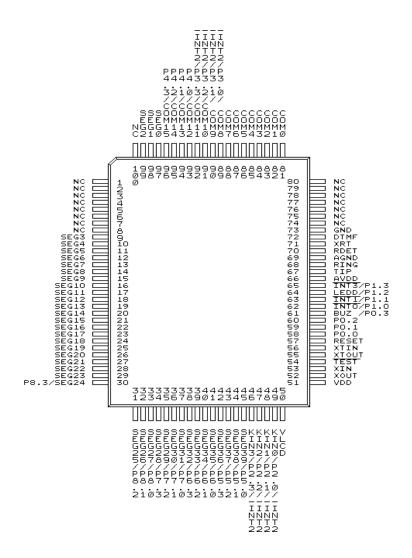

## **Pin Configuration**

### **Block Diagram**

PAD(S) : BONDING PAD(S)

## **Pad Description**

| Pin No. | Designation              | I/O      | Description                                         |

|---------|--------------------------|----------|-----------------------------------------------------|

| 1 ~ 20  | SEG4~23                  | 0        | LCD segment signal outputs                          |

| 21 ~ 24 | SEG24~27 /<br>P8.3~0     | O<br>I/O | LCD segment signal outputs / Port8                  |

| 25 ~ 28 | SEG28~31 /<br>P7.3~0     | O<br>I/O | LCD segment signal outputs / Port7                  |

| 29 ~ 32 | SEG32~35 /<br>P6.3~0     | 0  /0    | LCD segment signal outputs / Port6                  |

| 33 ~ 36 | SEG36~39 /<br>P5.3~0     | 0 1/9    | LCD segment signal outputs / Port5                  |

| 37 ~ 40 | KIN3~0 (INT2)/<br>P2.3~0 | I<br>I/O | Keyboard interrupt inputs ( INT2 ) / Port2          |

| 41      | VLCD                     | I        | Input pin of LCD reference voltage                  |

| 42      | VDD                      | Р        | Power supply input                                  |

| 43      | XOUT                     | 0        | Main oscillator output                              |

| 44      | XIN                      | I        | Main oscillator input                               |

| 45      | TEST                     | I        | Enable TEST MODE 1 when low (For factory used only) |

| 46      | XTOUT                    | 0        | Watch crystal oscillator output                     |

| 47      | XTIN                     | - 1      | Watch crystal oscillator input                      |

| 48      | RESET                    | I        | System reset input (High active)                    |

| 49      | P0.0                     | I/O      | Port0.0                                             |

| 50      | P0.1                     | I/O      | Port0.1                                             |

| 51      | P0.2                     | I/O      | Port0.2                                             |

| 52      | BUZ /<br>P0.3            | O<br>I/O | Buzzer output (Normal low) / Port0.3                |

| 53      | INTO /<br>P1.0           | I<br>I/O | External interrupt inputs (INT0)/<br>Port1.0        |

| 54      | INT1 /<br>P1.1           | I<br>I/O | External interrupt inputs (INT1) / Port1.1          |

| 55      | P1.2<br>LEDD             | I<br>0   | Input pin Port1.2<br>LED driver pin (open drain)    |

| 56      | INT3 /<br>P1.3           | I<br>I/O | External interrupt input (INT3)/<br>Port1.3         |

| 57      | AVDD                     | Р        | Analog power supply input                           |

| 58      | TIP                      | I        | TIP line input pin                                  |

| 59      | RING                     | I        | RING line input pin                                 |

# Pin Description (continuous)

| 60      | AGND                          | Р        | Analog ground                                                        |

|---------|-------------------------------|----------|----------------------------------------------------------------------|

| 61      | RDET                          | I        | Ring detected input pin                                              |

| 62      | XRT                           | 0        | Ring detected output pin (open drain, low active)                    |

| 63      | DTMF                          | 0        | DTMF signal output pin                                               |

| 64      | GND                           | Р        | Ground                                                               |

| 65 ~ 72 | COM0-7                        | 0        | LCD common signal outputs (Keyboard scanning outputs)                |

| 73 ~ 76 | COM8~11 /<br>P3.0~3 /<br>INT2 | 0  /     | LCD common signal outputs / Port3 / Keyboard interrupt inputs (INT2) |

| 77 ~ 80 | COM12~15 /<br>P4.0~3          | O<br>I/O | LCD common signal outputs / Port4                                    |

| 81 ~ 84 | SEG0~3                        | 0        | LCD segment signal outputs                                           |

## Note:

All external interrupt inputs would be triggered by any negative-edge signal

### **Absolute Maximum Ratings**

### Comments

Stresses above those listed under **Absolute Maximum Ratings** may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these of any other conditions above specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC Electrical Characteristics (Temperature = 0°C to 70°C, V<sub>DD</sub> = 5.0V±10%, GND = 0V)

| Parameter                  | Symbol            | Min.                 | Тур.                    | Max.                   | Unit | Conditions                        |                                           |  |

|----------------------------|-------------------|----------------------|-------------------------|------------------------|------|-----------------------------------|-------------------------------------------|--|

| Cupply voltage             | Vcpu              | 2.4                  |                         | 5.5                    | V    | For all mode                      | e with FSK off                            |  |

| Supply voltage             | VFSK              | 3.5                  |                         | 5.5                    | V    | For all mode                      | e with FSK on                             |  |

|                            | I <sub>DD1</sub>  |                      | 1.5                     | 2                      | mA   | V <sub>DD</sub> = 5V              | Normal mode                               |  |

|                            | I <sub>DD2</sub>  |                      | 0.7                     | 1.2                    | mA   | V <sub>DD</sub> = 3V              | FSK off, DTMF off                         |  |

| Operating current          | Іррз              | IDD1 + 1.6 IDD1      |                         | I <sub>DD1</sub> + 2.5 | mA   | V <sub>DD</sub> = 5V              | Normal mode<br>FSK on, DTMF off           |  |

|                            | I <sub>DD4</sub>  |                      | I <sub>DD1</sub> + 0.45 | I <sub>DD1</sub> + 1.0 | mA   | V <sub>DD</sub> = 5V              | Normal mode<br>FSK off, DTMF on           |  |

| Standby current            | Isb1              |                      | 600                     | 900                    | μΑ   | V <sub>DD</sub> = 5V              | Halt mode<br>FSK off, DTMF off<br>LCD off |  |

| Standby Current            | IsB2              |                      | 12                      | 30                     | μΑ   | V <sub>DD</sub> = 5V              | Stop mode                                 |  |

|                            | Is <sub>B</sub> 3 |                      | 3                       | 20                     | μΑ   | V <sub>DD</sub> = 3V              | FSK off, DTMF off<br>LCD off              |  |

|                            | V <sub>IH1</sub>  | 0.9 V <sub>DD</sub>  |                         | V <sub>DD</sub> +0.3   | V    | RESET                             | 1                                         |  |

| Input high voltage         | VIH2              | V <sub>DD</sub> -0.3 |                         | V <sub>DD</sub> +0.3   | V    | XIN, XTIN                         |                                           |  |

| g.                         | V <sub>I</sub> H3 | 0.8 V <sub>DD</sub>  |                         | V <sub>DD</sub> +0.3   | V    | All pins except RESET, XIN & XTIN |                                           |  |

|                            | VIL1              | -0.3                 |                         | 0.1 V <sub>DD</sub>    | V    | RESET                             |                                           |  |

| Input low voltage          | VIL2              | -0.3                 |                         | 0.3                    | V    | XIN, XTIN                         |                                           |  |

|                            | VIL3              | -0.3                 |                         | 0.2 V <sub>DD</sub>    | V    | All pins exce                     | ept RESET, XIN &                          |  |

| Output high voltage        | Vон               | V <sub>DD</sub> -1.0 |                         |                        | V    | Output pin v                      | vithout loading                           |  |

| Output low voltage         | Vol               |                      |                         | 0.6                    | V    | Output pin v                      | vithout loading                           |  |

| Drive/Sink current of      | <b>І</b> он1      | 1.5                  | 2.0                     |                        | mA   | Voн = 4.0V,                       |                                           |  |

| general output pins        | lol1              | -1.5                 | -2.0                    |                        | mA   | Port0, Port1                      | , Port2, Port3 & Port4                    |  |

| Drive/Sink current of      | <b>І</b> он2      | 1.0                  | 1.5                     |                        | mA   | Vон = 4.0V,                       |                                           |  |

| shared output pins         | lol2              | -1.0                 | -1.5                    |                        | mA   | Port5, Port6                      | i, Port7 and Port8                        |  |

| Sink current of LED driver | <b>І</b> оьз      | <b>-</b> 5           | -10                     |                        | mA   | Vol = 0.6V,                       | P1.2                                      |  |

| Pull-up resistance 1       | Rup1              | 130                  | 180                     | 230                    | ΚΩ   | Port0, Port1                      | , Port2, Port3 & Port4                    |  |

| Pull-up resistance 2       | R <sub>UP2</sub>  | 50                   | 100                     | 150                    | ΚΩ   | Port5, Port6                      | i, Port7 & Port8                          |  |

# Analog Electrical Characteristics (Temperature = $0^{\circ}$ C to $70^{\circ}$ C, $V_{DD}$ = $5.0V\pm10\%$ , GND = 0V)

| Parameter                                     | Symbol | Min.       | Тур.                         | Max.                  | Unit  | Conditions                                        |

|-----------------------------------------------|--------|------------|------------------------------|-----------------------|-------|---------------------------------------------------|

| Single Row Tone Output<br>Amplitude           | Vor    | 500        | 580                          | 650                   | mVp-p | With 100K $\Omega$ pull-up resister               |

| Single Column Tone Output<br>Amplitude        | Voc    | 685        | 760                          | 835                   | mVp-p | With 100KΩ pull-up resister                       |

| DTMF output distortion                        | DIS%   |            | 2                            | 5                     | %     | With 100KΩ pull-up resister                       |

| DTMF pre-emphasis                             | Twist  | 1          | 2                            | 3                     | dB    | With 100K $\Omega$ pull-up resister               |

| Tip/Ring input impedance                      | RIN    | 400        | 500                          | 600                   | ΚΩ    | Input frequency = 0                               |

| Input sensitivity of Tip and Ring             | Psig   | <b>–45</b> | -48                          |                       | dBm   | SNR = 15dB                                        |

| Hysteresis of Carrier detected                | Нср    |            | 3                            |                       | dB    | SNR = 15dB                                        |

| Frequency response of the Band<br>Pass Filter |        |            | -54<br>0<br>+1<br>-19<br>-35 |                       | dB    | ≤ 60Hz<br>1200Hz<br>2200Hz<br>5000Hz<br>≥ 10000Hz |

| Battery detected level                        | VBAT   | VDET -0.3  |                              | V <sub>DET</sub> +0.3 | V     | V <sub>DET</sub> = 2.8V or 3.6V or 4.4V           |

# AC Electrical Characteristics (Temperature = $0^{\circ}$ C to $70^{\circ}$ C, $V_{DD}$ = $5.0V\pm10\%$ , GND = 0V)

| Parameter                            | Symbol           | Min. | Тур.     | Max. | Unit | Conditions                               |

|--------------------------------------|------------------|------|----------|------|------|------------------------------------------|

| Execution cycle time                 | Тсус             | 1.1  |          | 4.4  | μs   | Fmain = 3.58MHz                          |

| Hardware Reset duration              | Tres             | 2    |          |      | Тсус | Fmain = 3.58MHz                          |

| CPU start up time from Reset or STOP | Тсри             |      | 2.5      | 10   | ms   | Fmain = 3.58MHz<br>By crystal oscillator |

| FSK power up time before data in     | T <sub>PUD</sub> |      | 8        | 20   | ms   | Psig = 40dBm, SNR = 30dB                 |

| CD delay time                        | T <sub>CDD</sub> |      | 7        | 20   | ms   | Psig = 40dBm, SNR = 30dB                 |

| CD hold time                         | T <sub>CDH</sub> |      | 9        | 20   | ms   | Psig = 40dBm, SNR = 30dB                 |

| Main oscillator frequency            | Fmain            |      | 3.579545 |      | MHz  | Crystal or Ceramic oscillator            |

| Watch oscillator frequency           | Fwatch           |      | 32.768   |      | KHz  | Crystal oscillator                       |

| Watch oscillator start up time       | Tws              |      |          | 1    | Sec  | Crystal oscillator                       |

## **Functional Description**

#### **Program memory**

This 4-bit CPU can directly access up to 14K words of program memory. Most instruction (except RET & RETI) would complete its operation in one or two execution cycle(s). For instruction RET or RETI, it takes 3 execution cycles to complete the operation of returning from a subroutine.

#### Vector address area (\$0000 to \$001F)

This chip provides a vector address area for program initialization and interrupt services. They are:

| \$00~01 | Jump to RESET (initialization) routine   |

|---------|------------------------------------------|

| \$02~03 | Jump to INTO service routine             |

| \$04~05 | Jump to INT1 service routine             |

| \$06~07 | Jump to INT2 service routine             |

| \$08~09 | Jump to INT3 service routine             |

| \$0A~0B | Jump to TIMER0 service routine           |

| \$0C~0D | Jump to TIMER1 service routine           |

| \$0E~0F | Jump to TIMER2 service routine           |

| \$10~11 | Jump to TIMER3 service routine           |

| \$12~13 | Reserved (2 NOPs should be put)          |

| \$14~15 | Jump to Ring detected service routine    |

| \$16~17 | Jump to Carrier detected service routine |

| \$18~1F | Reserved                                 |

## **ROM MAP**

| \$0000 |                       |

|--------|-----------------------|

| \$001F | Vector Address Area   |

| \$0020 |                       |

|        | Zero-page Subroutines |

| \$003F |                       |

| \$0040 |                       |

|        | System Program        |

| \$37FF |                       |

#### **Random Access Data Memory**

Resident data memory is organized as 3328 x 4 bits (3328 nibbles). RAM is used for data storage, register storage, stack, and storage of segment data for LCD display RAM. All the interrupt control registers and other special function registers are implemented by means of memory mapping to the internal RAM space.

#### **RAM Addressing**

Like most CPU structure, data may be accessed either by direct or indirect addressing. Direct addressing is defined by operand itself while indirect addressing is defined by the three registers, V, X and Y. Indirect addressing is more general than direct addressing because only the first 1K data can be accessed by means of direct addressing while the others have no limitation for this. There are 16 special RAM spaces (R0 to R15) that can be accessed directly either by special instruction or the general one.

#### **RAM Mapping**

This chip employs memory-mapped registers for controlling the system function and on-chip peripherals, such as Interrupts, I/O port, LCD control and Timers. All the control bits and data are defined from address \$000 through \$03F in data memory.

## **RAM MAP**

| \$000 | RAM Mapped Register     |

|-------|-------------------------|

| \$040 | Memory Register (R0~15) |

| \$050 | Data                    |

| \$100 | LCD Display Area        |

| \$200 | Stack                   |

| \$240 |                         |

| \$CFF | Data                    |

## **RAM Mapped Register**

| Re           | gister |                                 |              | Contents                    |              |             |           |

|--------------|--------|---------------------------------|--------------|-----------------------------|--------------|-------------|-----------|

| Addr         | Name   | Description                     | Bit3         | Bit2                        | Bit1         | Bit0        | Attribute |

| \$000        | SENSE0 | Sense register 0                | IE0 (s/r/t)  | IRQ0 (r/t)                  | RSP (r)      | IE (s/r/t)  | -         |

| \$001        | SENSE1 | Sense register 1                | IE2 (s/r/t)  | IRQ2 (r/t)                  | IE1 (s/r/t)  | IRQ1 (r/t)  | -         |

| \$002        | SENSE2 | Sense register 2                | IET1 (s/r/t) | IRQT1 (r/t)                 | IET0 (s/r/t) | IRQT0 (r/t) | -         |

| \$003        | SENSE3 | Sense register 3                | IET2 (s/r/t) | IRQT2 (r/t)                 | -            | -           | -         |

| \$004        | TMOD0  | Timer 0 mode register           | TMOD0.3      | TMOD0.2                     | TMOD0.1      | TMOD0.0     | W         |

| \$005        | TMOD1  | Timer 1 mode register           | TMOD1.3      | TMOD1.2                     | TMOD1.1      | TMOD1.0     | W         |

| \$006        | TC00   | Timer 0 counter register 0      | TC00.3       | TC00.2                      | TC00.1       | TC00.0      | R         |

| φυυσ         | TL00   | Timer 0 load register 0         | TL00.3       | TL00.2                      | TL00.1       | TL00.0      | W         |

| \$007        | TC01   | Timer 0 counter register 1      | TC01.3       | TC01.2                      | TC01.1       | TC01.0      | R         |

| φυυ <i>τ</i> | TL01   | Timer 0 load register 1         | TL01.3       | TL01.2                      | TL01.1       | TL01.0      | W         |

| \$008        | TC10   | Timer 1 counter register 0      | TC10.3       | TC10.2                      | TC10.1       | TC10.0      | R         |

| φυυο         | TL10   | Timer 1 load register 0         | TL10.3       | TL10.2                      | TL10.1       | TL10.0      | W         |

| \$009        | TC11   | Timer 1 counter register 1      | TC11.3       | TC11.2                      | TC11.1       | TC11.0      | R         |

| φυυθ         | TL11   | Timer 1 load register 1         | TL11.3       | TL11.2                      | TL11.1       | TL11.0      | W         |

| \$00A        | -      | Reserved                        | -            | -                           | -            | -           | -         |

| \$00B        | -      | Reserved                        | -            | -                           | -            | -           | -         |

| \$00C        | -      | Reserved                        | -            | -                           | -            | -           | -         |

| \$00D        | CKS    | System clock register           | Reserved     | ENOSC<br>(Must be set to 1) | CKS.1        | CKS.0       | W         |

| \$00E        | BPM    | Beep mode register              | ВРМ.3        | BPM.2                       | BPM.1        | BPM.0       | W         |

| \$00F        | TESTM  | Test mode register              |              | CONFIDE                     | NTIAL        |             | W         |

| \$010        | PMODA  | Port mode register A            | PMODA.3      | PMODA.2                     | PMODA.1      | PMODA.0     | W         |

| \$011        | PMODB  | Port mode register B            | PMODB.3      | PMODB.2                     | PMODB.1      | PMODB.0     | W         |

| \$012        | PMODC  | Port mode register C            | PMODC.3      | PMODC.2                     | PMODC.1      | PMODC.0     | W         |

| \$013        | TMOD3  | Timer 3 mode register           | TMOD3.3      | TMOD3.2                     | TMOD3.1      | TMOD3.0     | W         |

| \$014        | PMODE  | Port mode register E            | PMODE.3      | PMODE.2                     | PMODE.1      | PMODE.0     | W         |

| \$015        | PMODF  | Port mode register F            | PMODF.3      | PMODF.2                     | PMODF.1      | PMODF.0     | W         |

| \$016        | -      | Reserved for EV-chip            | -            | -                           | -            | -           | -         |

| \$017        | LCON   | LCD control register            | LCON.3       | LCON.2                      | LCON.1       | LCON.0      | W/s/r     |

| \$018        | LMOD0  | LCD mode register 0             | LMOD0.3      | LMOD0.2                     | LMOD0.1      | LMOD0.0     | W         |

| \$019        | LMOD1  | LCD mode register 1             | LMOD1.3      | LMOD1.2                     | LMOD1.1      | LMOD1.0     | W         |

| \$01A        | TGC    | Tone generator control register | TGC.3        | TGC.2                       | TGC.1        | TGC.0       | W         |

| \$01B        | TGD    | Tone generator Data register    | TGD.3        | TGD.2                       | TGD.1        | TGD.0       | W         |

## RAM Mapped Register (continued)

| Re          | gister |                            |        |         | Cont    | tents    |         |         |        |        |           |

|-------------|--------|----------------------------|--------|---------|---------|----------|---------|---------|--------|--------|-----------|

| Addr        | Name   | Description                | Bi     | t3      | Bit2    | 2        | В       | it1     | Bitt   | )      | Attribute |

| <b>CO10</b> | TC30   | Timer 3 counter register 0 | TC3    | 30.3    | TC30.2  |          | TC30.1  |         | TC30.0 |        | R         |

| \$01C       | TL30   | Timer 3 load register 0    | TL3    | 30.3    | TL30.2  |          | TL30.1  |         | TL30.0 |        | W         |

|             | TC31   | Timer 3 counter register 1 | TC3    | 31.3    | TC31.2  |          | TC      | 31.1    | TC31   | .0     | R         |

| \$01D       | TL31   | Timer 3 load register 1    | TL3    | 31.3    | TL31    | 1.2      | TL      | 31.1    | TL31   | .0     | W         |

|             | TC32   | Timer 3 counter register 2 | TC3    | 32.3    | TC32    | 2.2      | TC      | 32.1    | TC32   | 2.0    | R         |

| \$01E       | TL32   | Timer 3 load register 2    | TL3    | 32.3    | TL32    | 2.2      | TL      | 32.1    | TL32   | 0      | W         |

| \$01F       | CTL0   | Control register 0         |        |         | ENBAT   | (W/t)    |         | -       | -      |        | -         |

| \$020       | SPA    | Stack pointer register A   | Rese   | erved   | Reser   | ved      | SF      | P.11    | SP.1   | 0      | R/W/t     |

| \$021       | SPB    | Stack pointer register B   | SF     | P.9     | SP.     | .8       | S       | P.7     | SP.    | 6      | R/W/t     |

| \$022       | SPC    | Stack pointer register C   | SF     | P.5     | SP.     | .4       | S       | P.3     | SP.:   | 2      | R/t       |

| \$023       | SENSE4 | Sense register 4           | IECD   | (s/r/t) | IRQCD   | (r/t)    | IET3    | (s/r/t) | IRQT3  | (r/t)  | -         |

| \$024       | SENSE5 | Sense register 5           | IERT   | (s/r/t) | IRQRT   | (r/t)    | IE3     | (s/r/t) | IRQ3   | (r/t)  | -         |

| \$025       | TMOD2  | Timer 2 mode register      | TMO    | D2.3    | TMOD2.2 |          | TMOD2.1 |         | TMOD   | 2.0    | W         |

| 0000        | TC20   | Timer 2 counter register 0 | TC2    | TC20.3  |         | TC20.2   |         | TC20.1  |        | TC20.0 |           |

| \$026       | TL20   | Timer 2 load register 0    | TL20.3 |         | TL20.2  |          | TL      | TL20.1  |        | TL20.0 |           |

| 0007        | TC21   | Timer 2 counter register 1 | TC2    | TC21.3  |         | TC21.2 T |         | 21.1    | TC21.0 |        | R         |

| \$027       | TL21   | Timer 2 load register 1    | TL2    | 21.3    | TL21.2  |          | TL21.1  |         | TL21.0 |        | W         |

| \$028       | -      | Reserved                   |        | •       | -       |          | -       |         | -      |        | -         |

| \$029       | -      | Reserved                   | -      | -       | -       |          | -       |         | -      |        | -         |

| \$02A       | -      | Reserved                   | -      | -       | -       |          | -       |         | -      |        | -         |

| \$02B       | -      | Reserved                   | -      | -       | -       |          | -       |         | -      |        | -         |

| \$02C       | -      | Reserved                   | -      | -       | -       |          | -       |         | -      |        | -         |

| \$02D       | -      | Reserved                   |        | •       | -       |          |         | -       | -      |        | -         |

| \$02E       | -      | Reserved                   | -      | -       | -       |          |         | -       | -      |        | -         |

| \$02F       | -      | Reserved                   |        | •       | -       |          |         | -       | -      |        | -         |

| \$030       | P0     | Port 0                     | PC     | ).3     | P0.2    | 2        | Р       | 0.1     | P0.0   | 0      | R/W/t     |

| \$031       | P1     | Port 1                     | P1     | .3      | P1.2    | 2        | Р       | 1.1     | P1.0   | 0      | R/W/t     |

| \$032       | P2     | Port 2                     | P2     | 2.3     | P2.2    | 2        | Р       | 2.1     | P2.0   | 0      | R/W/t     |

| \$033       | P3     | Port 3                     | P3     | 3.3     | P3.2    | 2        | Р       | 3.1     | P3.0   | 0      | R/W/t     |

| \$034       | P4     | Port 4                     | P4     | 1.3     | P4.2    | 2        | Р       | 4.1     | P4.0   | 0      | R/W/t     |

| \$035       | P5     | Port 5                     | P5     | 5.3     | P5.2    | 2        | Р       | 5.1     | P5.0   | 0      | R/W/t     |

| \$036       | P6     | Port 6                     | P6     | 3.3     | P6.2    | 2        | Р       | 6.1     | P6.0   | 0      | R/W/t     |

| \$037       | P7     | Port 7                     | P7     | 7.3     | P7.2    | 2        | Р       | 7.1     | P7.0   | 0      | R/W/t     |

| \$038       | P8     | Port 8                     | P8     | 3.3     | P8.2    | 2        | Р       | 8.1     | P8.0   | )      | R/W/t     |

### **RAM Mapped Register (continued)**

| Re    | gister |                      |          | Contents |        |        |           |

|-------|--------|----------------------|----------|----------|--------|--------|-----------|

| Addr  | Name   | Description          | Bit3     | Bit2     | Bit1   | Bit0   | Attribute |

| \$039 | -      | Reserved             | -        | -        | -      | -      | -         |

| \$03A | -      | Reserved for EV-chip | -        | -        | -      | -      | -         |

| \$03B | -      | Reserved for EV-chip | -        | -        | -      | -      | -         |

| \$03C | CTL1   | Control register 1   | RT       | -        | CD     | DOUT   | R/t       |

| \$03D | CTL2   | Control register 2   | RP       | BAT.2    | BAT.1  | BAT.0  | R/t       |

| φυσυ  | CILZ   | Control register 2   | Reserved | PWDN     | ENRD   | BEEP   | W         |

| \$03E | CVAR   | Reserved             | CVAR.3   | CVAR.2   | CNAR.1 | CVAR.0 | W         |

| \$03F | -      | Reserved             | -        | -        | -      | -      | -         |

#### **Notes**

R/W/s/r/t: R: Available for all nibble-read instructions, for example, MTA

W: Available for all nibble-write instructions, for example, ITMD

s: Available for instructions, SM and SMD r: Available for instructions, RM and RMD t: Available for instructions, TM and TMD

Fig. Enable all Interrupts of this chip

IEn: Enable Interrupt n,

IRQn: Interrupt request of INTn

IETn: Enable Interrupt of Timer n.

IRQTn: Interrupt request of Timer n.

IERT: Enable Interrupt of Ring time detected,

IECD: Enable Interrupt of Carrier detected,

SP.y: Bit y of stack pointer,

IRQRT: Interrupt request of Ring time detected IRQCD: Interrupt request of Carrier detected

RSP: Reset stack pointer address

SP.y: Bit y of stack pointer,CKS: Clock selection register

CKS.0 and CKS.1 are used to select the system clock speed,

e.g. If CKS = xx00, then system clock = Fmain/16

If CKS = xx01, then system clock = Fmain/8

If CKS = xx10, then system clock = Fmain/4

© ENBAT: Enable low-battery detection when high

BAT.m: Battery power level data (Please refer to the Battery-low table)

RP: Bit for indicates Ring pulse signal

RT: Bit for indicates Ring time pulse status

CD: Bit for indicates Carrier detected status

DOUT: FSK demodulator output data bit

ENRD: Enable Internal Ring detector

PWDN: Turn off the FSK demodulator when set

# ENOSC: Enable the clock for FSK demodulator and frequency counter (within the Ring Detector) when set

(It must be set to one during initialization if FSK demodulator has to be used in case!)

BEEP: Enable Beeper

(m = 0, 1, 2; n = 0, 1, 2, 3; x = 0,1; y = 2, ..., 11)

#### **Registers and Flags**

This chip provides nine registers and two flags for CPU operation. They are described below:

### Accumulator A (4 bits) and Register B (4 bits)

Accumulator A and Register B are 4-bit registers that hold the result of the arithmetic logic units (ALU). They are the very basic registers for a CPU to execute all the arithmetic calculation, logic operation and data transfer among memories, I/Os and registers.

#### Register V (4 bits)

Register V is a 4-bit register that holds the page address (256 addresses per page) of RAM.

#### Register X (4 bits), Register Y (4 bits)

Register X and Y register are used for indirect RAM addressing such that the RAM address is defined as the following format:

| Bit location | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----|

| RAM addr     | V3 | V2 | V1 | V0 | X3 | X2 | X1 | X0 | Y3 | Y2 | Y1 | Y0 |

#### Register EX (4 bits), Register EY (4 bits)

Register EX and EY are 4-bit registers available to assist register X and Y, respectively.

#### Carry Flag, CY (1 bit)

The carry flag holds the ALU overflow bit generated by arithmetic operation. It can be set or reset by instruction directly, and is affected by the rotation instruction.

### Status Flag, SF (1 bit)

The flag holds ALU compare, arithmetic instruction and the status of accumulator. This flag would be tested by those instructions of conditional jump and conditional call.

After the execution of BR, LBR, CAL, or CALL instruction, the status bit would be set. Furthermore, SF will be pushed onto the stack during serving interrupt. Note that SF will not be restored by instruction RET, but instruction RETI

#### Program Counter, PC (14 bits)

The program counter is used for addressing ROM data. It is reserved in the RAM space from \$200 to \$23F, so that 16 program addresses can be restored for subroutine call function or interrupt service.

#### Stack Pointer, SP (12 bits)

The stack pointer is implemented by a typical RAM mapped structure so as to make the system become more flexible. SP is a 12-bit register that holds the start address of the recent level of Stack. Stack is combined of sixteen 4-nibble registers, which hold the return address with its status flag and carry flag. Therefore, 16-level stack operation is possible. And yet it can be initialized to the starting address (\$23F) of the stack by either system reset or software method.

The following table shows how the stack register configured:

#### Reset Stack Pointer Flag, RSP (1bit)

RSP is used for resetting the stack pointer to \$23F and it will be cleared while system RESET. In general, it would not be used unless software reset of stack pointer is necessary for extraordinary condition. The stack pointer can be reset to \$23F by reset RSP through instruction RM/RMD.

Stack Register Bits Configuration: (For level 1)

| Address |     | Bit 3 |     | Bit 2 |     | Bit 1 |     | Bit 0 |  |

|---------|-----|-------|-----|-------|-----|-------|-----|-------|--|

| \$23F   | S3  | -PC3  | S2  | -PC2  | S1  | -PC1  | S0  | -PC0  |  |

| \$23E   | S7  | CY    | S6  | -PC6  | S5  | -PC5  | S4  | -PC4  |  |

| \$23D   | S11 | -PC10 | S10 | -PC9  | S9  | -PC8  | S8  | -PC7  |  |

| \$23C   | S15 | SF    | S14 | -PC13 | S13 | -PC12 | S12 | -PC11 |  |

Note: PC stored in the stack is a negative value.

### **Memory Allocation of Stack Level**

| Level | Address       | Level | Address       | Address Level |               | Address Level |               |

|-------|---------------|-------|---------------|---------------|---------------|---------------|---------------|

| 16    | \$203 ~ \$200 | 12    | \$213 ~ \$210 | 8             | \$223 ~ \$220 | 4             | \$233 ~ \$230 |

| 15    | \$207 ~ \$204 | 11    | \$217 ~ \$214 | 7             | \$227 ~ \$224 | 3             | \$237 ~ \$234 |

| 14    | \$20B ~ \$208 | 10    | \$21B ~ \$218 | 6             | \$22B ~ \$228 | 2             | \$23B ~ \$238 |

| 13    | \$20F ~ \$20C | 9     | \$21F ~ \$21C | 5             | \$22F ~ \$22C | 1             | \$23F ~ \$23C |

#### Interrupts

There are ten interrupts with one system initialization:

- 1. System initialization:

- RESET (Reset pin)

- 2. General interrupts:

- INTO (Interrupt from pin P1.0)

INT1 (Interrupt from pin P1.1)

- INT2 (Interrupt from pin Port2 / Port3)

- INT3 (Interrupt from pin P1.3)

- 3. Timer interrupts:

- TIMER0 (Interrupt from pin Timer 0)

TIMER1 (Interrupt from pin Timer 1)

TIMER2 (Interrupt from pin Timer 2)

- TIMER3 (Interrupt from pin Timer 3)

- 4. Ring detected interrupt:

- RT (interrupt from Ring detector)

- 5. Carrier detected interrupt:

- CD (interrupt from FSK demodulator)

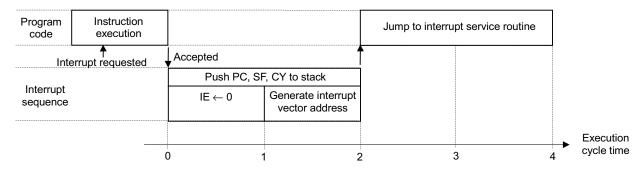

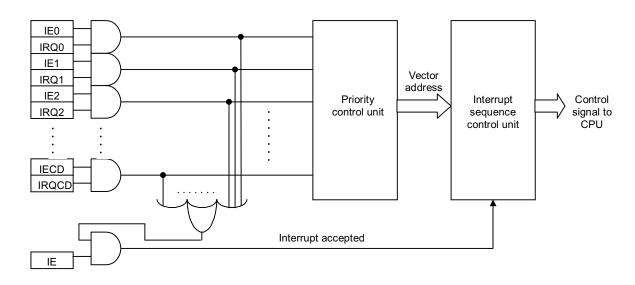

#### Interrupt Control bits and Request flags

The RAM mapped register from \$00 through \$03, \$23 and \$24 can only be accessed by bit operation instructions. Any interrupt (such as  $\overline{\text{INTn}}$ ) may be accepted while IE and its own enable flag (such as IEn) were set. The interrupt request flag (such as IRQn) will only be set by its interrupt signal (a negative-edge signal). Yet this request flag can be cleared by system RESET or software.

### Interrupt Enabled (IE)

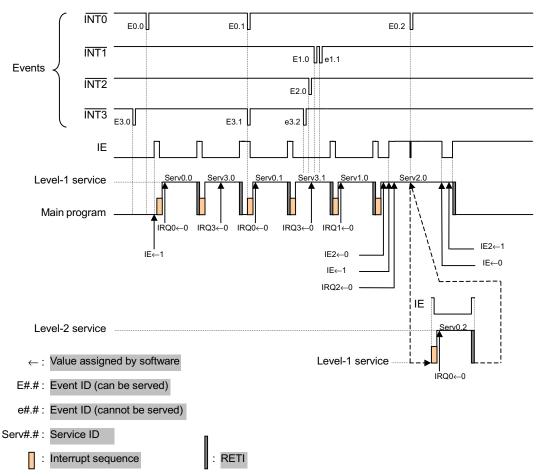

The interrupt-enable bit, IE, enables all interrupt requests when it is set. Also, it can be enabled by instruction RETI and will be reset during entering the interrupt service routine automatically. Once the program enters the interrupt service routine, IE will be reset by CPU itself so that other interrupt (if any) would be pending with its execution priority. That is the reason why only one level of interrupt service can be performed in general. However, multi-level interrupt service can be achieved by reset IE within the interrupt service routine. For multi-level interrupt programming, please refer to the Timing diagram of interrupt events.

Actually, it is the gate for all interrupt requests. No interrupt service would be done until IE is set.

Any two different interrupts occurred in the same instruction cycle would be treated as collision of interrupt when IE=1. The interrupt service with higher priority will come first while the other is pending.

Any two different interrupts occurred whatever in the same or different instruction cycle would also be treated as collision of interrupt when IE=0. Both interrupts would be pending until IE is set. Once IE is set, the interrupt service with higher priority will come first while the other is pending.

#### Individual Interrupt Enabled (IEn, IETn, IESI, IECD)

The interrupt-enable bit (such as IEn) enables a specific interrupt request (such as IRQn) when it is set. In other words, it is the gate for its own interrupt request only.

#### **General Interrupts**

#### INTO, INT1:

Interrupt request flag, IRQ0/IRQ1, will be set while interrupt input,  $\overline{\text{INT0}}$  /  $\overline{\text{INT1}}$ , has received any negative edge signal. The program will enter the service routine of  $\overline{\text{INT0}}$  /  $\overline{\text{INT1}}$  provided that both IE and IE0/IE1 were set. Also,  $\overline{\text{INT0}}$  or  $\overline{\text{INT1}}$  (P1.0 or P1.1) can be programmed as an external clock input of Timer0 or Timer1 by the register, TMOD0 or TMOD1, respectively.

#### INT2:

Interrupt request flag, IRQ2, will be set while any one of the interrupt inputs,  $\overline{\text{INT2}}$  (Port2.0-3/Port3.0-3), has received a negative edge signal. Generally, it is used as a keyboard interrupt. Port3 can not be used as interrupt when 1/16 duty of LCD has been selected.

#### INT3:

Interrupt request flag, IRQ3, will be set while interrupt input INT3 has received any negative edge signal.

#### **Timer Interrupts**

Interrupt request flag, IRQTn, will be set by the output signal of Timer n (n = 0, 1, 2, 3). Details should be referred to the section of Timer.

#### Ring detected interrupt

Interrupt request flag, IRQRT, will be set by the internal signal from Ring regulator provided that Ring regulator has been enabled (ENRD = 1). Details should be referred to the section of Ring regulator.

#### Carrier detected interrupt

Interrupt request flag, IRQCD, will be set in NORMAL mode by the internal signal from Carrier detector provided that FSK demodulator has been turned on (PWDN = 0 & ENOSC = 1). Note that it does not work in STOP mode.

## Interrupt Vector Address and execution priority

| Interrupt | Signal   | Priority         | Issued by | Condition                                       | Vector |

|-----------|----------|------------------|-----------|-------------------------------------------------|--------|

| RESET     | External | 1 <sup>st</sup>  | Reset pin | RESET PIN = 1 for at least 2 instruction cycles | \$00   |

| INT0      | External | 2 <sup>nd</sup>  | IRQ0      | IE = IE0 = IRQ0 = 1                             | \$02   |

| INT1      | External | 3 <sup>rd</sup>  | IRQ1      | IE = IE1 = IRQ1 = 1                             | \$04   |

| INT2      | External | 4 <sup>th</sup>  | IRQ2      | IE = IE2 = IRQ2 = 1                             | \$06   |

| ĪNT3      | External | 5 <sup>th</sup>  | IRQ3      | IE = IE3 = IRQ3 = 1                             | \$08   |

| TIMER0    | Internal | 6 <sup>th</sup>  | IRQT0     | IE = IET0 = IRQT0 = 1                           | \$0A   |

| TIMER1    | Internal | 7 <sup>th</sup>  | IRQT1     | IE = IET1 = IRQT1 = 1                           | \$0C   |

| TIMER2    | Internal | 8 <sup>th</sup>  | IRQT2     | IE = IET2 = IRQT2 = 1                           | \$0E   |

| TIMER3    | Internal | 9 <sup>th</sup>  | IRQT3     | IE = IET3 = IRQT3 = 1                           | \$10   |

| RT        | Internal | 10 <sup>th</sup> | IRQRT     | IE = IERT = ENRD = 1                            | \$14   |

| CD        | Internal | 11 <sup>th</sup> | IRQCD     | IE = IECD = ENOSC = 1 & PWDN = 0                | \$16   |

## Timing of interrupt sequence

## Hardware structure of interrupt control unit

## **Example of Timing of interrupt events**

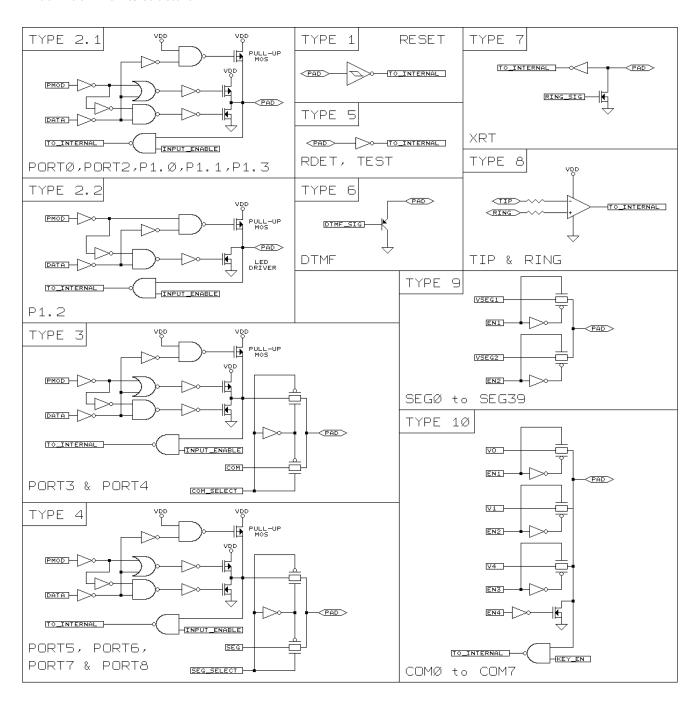

### Input/Output Port

There are 36 I/O pins, which are divided into 9 groups. Each I/O pin contains a pull-up resistor that can be controlled by software. The pull-up resistor will be enabled if it is configured as an input pin with a data '1'. For example, the pull-up resistor of P0.3 would be enabled by the following procedure:

ITMD :1110, PMODA ;set P0 as I/P port ITMD :1000, P0 ;enable pull-up resistor of P0.3

Do not let any unconnected pin floating because it may cause the large current problem to the chip.

All the I/O pins would be reset to the default status (input with pull-up resistor enabled) after system reset.

In case there is an internal pull-up resistor of input pin have been disabled, an external pull-up/pull-down resistor (100 K $\Omega$  typically) must be connected.

| Port Mode Register | Bit 3    | Bit 2    | Bit 1                  | Bit 0    | Mode              |           |

|--------------------|----------|----------|------------------------|----------|-------------------|-----------|

| PMODA (\$010)      | PORT3    | PORT2    | Reserved PORT0 0: Inpu |          | 0: Input          | 1: Output |

| PMODB (\$011)      | PORT7    | PORT6    | PORT5                  | Reserved | 0: Input          | 1: Output |

| PMODC (\$012)      | Reserved | Reserved | Reserved               | PORT8    | 0: Input          | 1: Output |

| PMODE (\$014)      | PORT1.3  | PORT1.2  | PORT1.1                | PORT1.0  | 0: Input          | 1: Output |

| PMODF (\$015)      | PORT4.3  | PORT4.2  | PORT4.1                | PORT4.0  | 0: Input 1: Outpu |           |

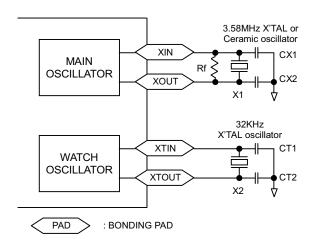

#### **Oscillators**

This is a typical dual oscillator system such that low power idle state with real time clock can be guaranteed even if the CPU has been stopped. Also, a simple RC delay circuit that co-operates with an I/O pin, the Timer0 and suitable software routine can give out a practical Watch-dog Timer. As shown in the following figure, the main oscillation circuit should be connected to an external crystal or ceramic oscillator. To ensure that these two oscillators can work well, a feedback resistor and 4 auxiliary capacitors should

be employed. The recommendation for the value of these components is:

| Component | RANGE     | RECOMMENDED |  |  |

|-----------|-----------|-------------|--|--|

| Rf        | 1ΜΩ~5ΜΩ   | 1ΜΩ         |  |  |

| CX1       | 22pF~30pF | 22pF        |  |  |

| CX2       | 22pF~30pF | 22pF        |  |  |

| CT1       | 22pF~30pF | 22pF        |  |  |

| CT2       | 22pF~30pF | 22pF        |  |  |

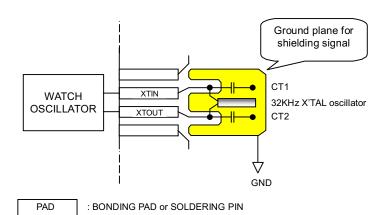

To ensure the oscillation quality of the real time clock, there is a recommendation for the PC board layout that can be help for improving the noise immunity. In addition, any micro-strip that cross over the oscillation signal would cause unexpected high-frequency noise to the watch

oscillator. As shown in the following figure, the oscillation signal is easily be shielded by such simple ground plane for one-layer or two-layer design. Similarly, this method can be applied for the main oscillator in some noisy environment.

#### **Timers**

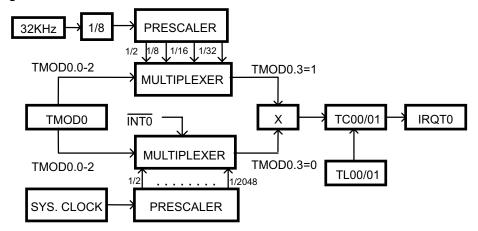

There are 4 Timers (Timer 0~3), in which prescaler and clock selection circuits have been built. By programming timer mode registers TMOD0~TMOD3, different clock source and speed can be selected. Yet Timer 0 can be set up as a real time clock for the watch oscillator would never stop after power up.

#### 1) Operation of Timer 0: 8-bit Watch Timer

Timer 0 is an 8-bit timer, which consists of two 4-bit write-only timer load registers (TL00, TL01) and two 4-bit read-only counter registers (TC00, TC01). Besides the internal clock source, Fmain, an external clock source, INTO, is also provided.

To write this load register, the lower nibble, TL00, must be written first, then the upper nibble, TL01.

To read the data of this counter register, the upper nibble, TC01, must be read out first, then the lower nibble, TC00.

The order of data reading and writing must be followed otherwise unexpected counting may be occurred.

There are three kinds of clock source can be selected by controlling the timer mode register 0 (TMOD0, \$004):

- The first one is the system clock, which can be programmed to Fmain/4, Fmain/8 or Fmain/16 by writing 00, 01 or 10 to CKS.1-0 respectively.

- The second one is the standard watch oscillator, 32768Hz

- The Last one is the external source, INTO.

Interrupt request flag (IRQT0) will be set when its 8-bit up counter has been overflowed (IRQT0 will be set during the transition from \$FF, the counter value, to \$00)

For the clock speed value, please refer the following table.

## Timer 0 Block Diagram

#### Timer Mode 0 Register (TMOD0, \$004)

(Fcyc = 1/Tcyc = Fmain/4 or Fmain/8 or Fmain/16)

| TMOD1.3 | TMOD1.2 | TMOD1.1 | TMOD1.0 | Clock speed   | Clock Source          |

|---------|---------|---------|---------|---------------|-----------------------|

| 0       | 0       | 0       | 0       | Fcyc / 2048   | Main oscillator       |

| 0       | 0       | 0       | 1       | Fcyc / 512    | Main oscillator       |

| 0       | 0       | 1       | 0       | Fcyc / 128    | Main oscillator       |

| 0       | 0       | 1       | 1       | Fcyc / 32     | Main oscillator       |

| 0       | 1       | 0       | 0       | Fcyc / 8      | Main oscillator       |

| 0       | 1       | 0       | 1       | Fcyc / 4      | Main oscillator       |

| 0       | 1       | 1       | 0       | Fcyc / 2      | Main oscillator       |

| 0       | 1       | 1       | 1       | -             | External source, INTO |

| 1       | 0       | 0       | 0       | 32768Hz / 256 | Watch oscillator      |

| 1       | 0       | 0       | 1       | 32768Hz / 128 | Watch oscillator      |

| 1       | 0       | 1       | 0       | 32768Hz / 64  | Watch oscillator      |

| 1       | 0       | 1       | 1       | 32768Hz / 16  | Watch oscillator      |

| 1       | 1       | Х       | Х       | -             | Reserved              |

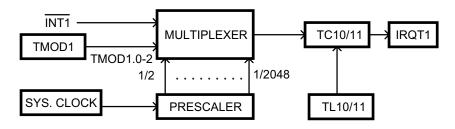

### 2) Operation of Timer 1: 8-bit Timer

Auto-reload function has been implemented in Timer 1. User can select different clock speed with or without auto-reload by putting the appropriate value into the timer mode register 1, TMOD1. Besides the internal clock source, Fmain, an external clock source, INT1, is also provided.

To write this load register, the lower nibble, TL10, must be written first, then the upper nibble, TL11.

To read the data of this counter register, the upper nibble, TC11, must be read out first, then the lower nibble, TC10.

The order of data reading and writing must be followed otherwise unexpected counting may be occurred.

Interrupt request flag (IRQT1) will be set when its 8-bit up counter has been overflowed (IRQT1 will be set during the transition from \$FF, the counter value, to \$00).

For the clock speed value, please refer the following table.

### **Timer 1 Block Diagram**

Timer Mode Register 1: (TMOD1 \$005)

(Fcyc = 1/Tcyc = Fmain/4 or Fmain/8 or Fmain/16)

| TMOD1.3 | TMOD1.2 | TMOD1.1 | TMOD1.0 | Clock speed              | Clock Source    | Auto-Reload |

|---------|---------|---------|---------|--------------------------|-----------------|-------------|

| 0       | 0       | 0       | 0       | Fcyc / 2048              | Main oscillator | No          |

| 0       | 0       | 0       | 1       | Fcyc / 1024              | Main oscillator | No          |

| 0       | 0       | 1       | 0       | Fcyc / 512               | Main oscillator | No          |

| 0       | 0       | 1       | 1       | Fcyc / 32                | Main oscillator | No          |

| 0       | 1       | 0       | 0       | Fcyc / 16                | Main oscillator | No          |

| 0       | 1       | 0       | 1       | Fcyc / 8                 | Main oscillator | No          |

| 0       | 1       | 1       | 0       | Fcyc / 2                 | Main oscillator | No          |

| 0       | 1       | 1       | 1       | -                        | External, INT1  | No          |

| 1       | 0       | 0       | 0       | Fcyc / 2048              | Main oscillator | Yes         |

| 1       | 0       | 0       | 1       | Fcyc / 1024              | Main oscillator | Yes         |

| 1       | 0       | 1       | 0       | Fcyc / 512               | Main oscillator | Yes         |

| 1       | 0       | 1       | 1       | Fcyc / 32                | Main oscillator | Yes         |

| 1       | 1       | 0       | 0       | Fcyc / 16                | Main oscillator | Yes         |

| 1       | 1       | 0       | 1       | Fcyc / 8 Main oscillator |                 | Yes         |

| 1       | 1       | 1       | 0       | Fcyc / 2                 | Main oscillator | Yes         |

| 1       | 1       | 1       | 1       | -                        | External, INT1  | Yes         |

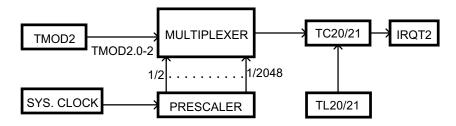

### 3) Operation of Timer 2: 8-bit Timer

Auto-reload function has been implemented in Timer 2. User can select different clock speed with or without auto-reload by putting the appropriate value into the timer mode register 2, TMOD2.

Only the internal clock source, Fmain, is provided for Timer 2.

To write this load register, the lower nibble, TL20, must be written first, then the upper nibble, TL21.

To read the data of this counter register, the upper nibble, TC21, must be read out first, then the lower nibble, TC20.

The order of data reading and writing must be followed otherwise unexpected counting may be occurred.

Interrupt request flag (IRQT2) will be set when its 8-bit up counter has been overflowed (IRQT2 will be set during the transition from \$FF, the counter value, to \$00).

For the clock speed value, please refer the following table.

## **Timer 2 Block Diagram**

#### Timer Mode Register 2: (TMOD2 \$0025)

(Fcyc = 1/Tcyc = Fmain/4 or Fmain/8 or Fmain/16)

| TMOD2.3 | TMOD2.2 | TMOD2.1 | TMOD2.0 | Clock speed | Clock Source              | Auto-Reload |

|---------|---------|---------|---------|-------------|---------------------------|-------------|

| 0       | 0       | 0       | 0       | Fcyc / 2048 | Main oscillator           | No          |

| 0       | 0       | 0       | 1       | Fcyc / 1024 | Main oscillator           | No          |

| 0       | 0       | 1       | 0       | Fcyc / 512  | Main oscillator           | No          |

| 0       | 0       | 1       | 1       | Fcyc / 128  | Main oscillator           | No          |

| 0       | 1       | 0       | 0       | Fcyc / 32   | Main oscillator           | No          |

| 0       | 1       | 0       | 1       | Fcyc / 16   | Main oscillator           | No          |

| 0       | 1       | 1       | 0       | Fcyc / 8    | Main oscillator           | No          |

| 0       | 1       | 1       | 1       | Fcyc / 2    | Main oscillator           | No          |

| 1       | 0       | 0       | 0       | Fcyc / 2048 | Main oscillator           | Yes         |

| 1       | 0       | 0       | 1       | Fcyc / 1024 | Main oscillator           | Yes         |

| 1       | 0       | 1       | 0       | Fcyc / 512  | Main oscillator           | Yes         |

| 1       | 0       | 1       | 1       | Fcyc / 128  | Main oscillator           | Yes         |

| 1       | 1       | 0       | 0       | Fcyc / 32   | Main oscillator           | Yes         |

| 1       | 1       | 0       | 1       | Fcyc / 16   | Feye / 16 Main oscillator |             |

| 1       | 1       | 1       | 0       | Fcyc / 8    | / 8 Main oscillator       |             |

| 1       | 1       | 1       | 1       | Fcyc / 2    | Fcyc / 2 Main oscillator  |             |

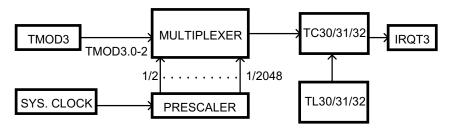

### 4) Operation of Timer 3: 12-bit Timer

Auto-reload function has also been implemented in Timer 3. User can select different clock speed with or without auto-reload by putting the appropriate value into the timer mode register 3, TMOD3.

Only the internal clock source, Fmain, is provided for Timer 3.

To write this load register, the lower nibble, TL30, must be written first, then the middle nibble, TL31, and finally the upper nibble, TL32.

To read the data of this counter register, the upper nibble, TC32, must be read out first, then the TC31, and finally the TC30.

The order of data reading and writing must be followed otherwise unexpected counting may be occurred.

Interrupt request flag (IRQT3) will be set when its 12-bit up counter has been overflowed (IRQT3 will be set during the transition from \$FFF, the counter value, to \$000).

For the clock speed value, please refer the following table.

### **Timer 3 Block Diagram**

Timer Mode Register 3: (TMOD3, \$013)

(Fcyc = 1/Tcyc = Fmain/4 or Fmain/8 or Fmain/16)

| TMOD3.3 | TMOD3.2 | TMOD3.1 | TMOD3.0 | Clock speed              | Clock Source    | Auto-Reload |

|---------|---------|---------|---------|--------------------------|-----------------|-------------|

| 0       | 0       | 0       | 0       | Fcyc / 2048              | Main oscillator | No          |

| 0       | 0       | 0       | 1       | Fcyc / 1024              | Main oscillator | No          |

| 0       | 0       | 1       | 0       | Fcyc / 512               | Main oscillator | No          |

| 0       | 0       | 1       | 1       | Fcyc / 128               | Main oscillator | No          |

| 0       | 1       | 0       | 0       | Fcyc / 32                | Main oscillator | No          |

| 0       | 1       | 0       | 1       | Fcyc / 16                | Main oscillator | No          |

| 0       | 1       | 1       | 0       | Fcyc / 8                 | Main oscillator | No          |

| 0       | 1       | 1       | 1       | Fcyc / 2                 | Main oscillator | No          |

| 1       | 0       | 0       | 0       | Fcyc / 2048              | Main oscillator | Yes         |

| 1       | 0       | 0       | 1       | Fcyc / 1024              | Main oscillator | Yes         |

| 1       | 0       | 1       | 0       | Fcyc / 512               | Main oscillator | Yes         |

| 1       | 0       | 1       | 1       | Fcyc / 128               | Main oscillator | Yes         |

| 1       | 1       | 0       | 0       | Fcyc / 32                | Main oscillator | Yes         |

| 1       | 1       | 0       | 1       | Fcyc / 16                | Main oscillator | Yes         |

| 1       | 1       | 1       | 0       | Fcyc / 8 Main oscillator |                 | Yes         |

| 1       | 1       | 1       | 1       | Fcyc / 2                 | Main oscillator | Yes         |

## Liquid Crystal Display (LCD)

This chip can directly drive a LCD panel of up to 640 dots (16 commons x 40 segments). LCD driver contains:

- · LCD controller/driver

- Display RAM for storing display data (\$100~\$1FF) (some of them are empty space (no memory cell))

- 16 common output pins (COM0~COM15)

- 40 segment output pins (SEG0~SEG39)

- 16-level contrast control

LCD control register, LCON, is used to turn the LCD display on and off so as to save energy in some cases. Also, it can control the LCD bias voltage to accommodate different type of LCD.

LCD mode register 0, LMOD0, is in charge of controlling the frame frequency of LCD and the display modes.

Users can select 1/8 or 1/16 duty for LCD by setting or resetting the bit, LMOD1.0. When it is reset to zero, for example, 1/8 duty will be performed and COM8~COM15 will also be recovered to be the normal I/O ports, Port3, Port4. In addition, LMOD1.1~LMOD1.3 offers 5 choices of I/O combination.

When LCON.0 is set, the LCD would always be enabled even in STOP or HALT mode.

## LCD Control Register: LCON (\$017)

| LCON.3 | LCON.2 | LCON.1 | LCON.0 | Function                |

|--------|--------|--------|--------|-------------------------|

| 0      | 0      |        | 0      | Disable LCD (Power off) |

| 0      | 0      |        | 1      | Enable LCD (Power on)   |

| 0      | 0      | 0      |        | 1/5 bias                |

| 0      | 0      | 1      |        | 1/4 bias                |

| 0      | 0      |        |        | Rx = 50KΩ               |

| 0      | 1      |        |        | $Rx = 50K\Omega / 2$    |

| 1      | 0      |        |        | Rx = 50KΩ / 4           |

| 1      | 1      |        |        | Rx = 50KΩ / 8           |

### LCD Mode Register 0: LMOD0 (\$018)

| LMOD0.3 | LMOD0.2 | LMOD0.1 | LMOD0.0 | Function                 |

|---------|---------|---------|---------|--------------------------|

|         |         | 0       | 0       | All LCD dots off (Blank) |

|         |         | 0 1     |         | All LCD dots on          |

|         |         | 1       | 0       | Normal display           |

|         |         | 1       | 1       | Normal display           |

| 0       | 0       |         |         | Frame Frequency = 32Hz   |

| 0       | 1       |         |         | Frame Frequency = 64Hz   |

| 1       | 0       |         |         | Frame Frequency = 128Hz  |

| 1       | 1       |         |         | Frame Frequency = 256Hz  |

### LCD Mode Register 1: LMOD1 (\$019)

| LMOD1.3 | LMOD1.2 | LMOD1.1 | LMOD1.0 | Pin30~33  | Pin34~37  | Pin38~41  | Pin42~45  | Pin82~85  | Pin86~89  | Duty |

|---------|---------|---------|---------|-----------|-----------|-----------|-----------|-----------|-----------|------|

| 0       | 0       | 0       |         | SEG24~27  | SEG28~31  | SEG32~35  | SEG36~39  |           |           |      |

| 0       | 0       | 1       |         | SEG24~27  | SEG28~31  | SEG32~35  | Port5.3~0 |           |           |      |

| 0       | 1       | 0       |         | SEG24~27  | SEG28~31  | Port6.3~0 | Port5.3~0 |           |           |      |

| 0       | 1       | 1       |         | SEG24~27  | Port7.3~0 | Port6.3~0 | Port5.3~0 |           |           |      |

| 1       | Х       | Х       |         | Port8.3~0 | Port7.3~0 | Port6.3~0 | Port5.3~0 |           |           |      |

|         |         |         | 0       |           |           |           |           | Port3.0~3 | Port4.0~3 | 1/8  |

|         |         |         | 1       |           |           |           |           | COM8~11   | COM12~15  | 1/16 |

### **LCD RAM Mapped Address**

LCD data RAM (\$100-\$1FF) is a dual port RAM that data can be transferred without any software restriction. Each bit represents a segment value, SEGn, corresponding to a COMn and can be set (LCD dot on) or reset (LCD dot

off) by bit or nibble operation instructions. The following diagram shows the configuration of the RAM Mapped of LCD.

#### **LCD RAM Area Configuration**

|       | COM0  |       |       |       |       | COM1  |       |       |       |  |       |       | COM15 |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|-------|-------|-------|-------|-------|

| Addr  | В3    | B2    | B1    | В0    | Addr  | В3    | B2    | B1    | В0    |  | Addr  | В3    | B2    | B1    | В0    |

| \$100 | SEG3  | SEG2  | SEG1  | SEG0  | \$110 | SEG3  | SEG2  | SEG1  | SEG0  |  | \$1F0 | SEG3  | SEG2  | SEG1  | SEG0  |

| \$101 | SEG7  | SEG6  | SEG5  | SEG4  | \$111 | SEG7  | SEG6  | SEG5  | SEG4  |  | \$1F1 | SEG7  | SEG6  | SEG5  | SEG4  |

| \$102 | SEG11 | SEG10 | SEG9  | SEG8  | \$112 | SEG11 | SEG10 | SEG9  | SEG8  |  | \$1F2 | SEG11 | SEG10 | SEG9  | SEG8  |

| \$103 | SEG15 | SEG14 | SEG13 | SEG12 | \$113 | SEG15 | SEG14 | SEG13 | SEG12 |  | \$1F3 | SEG15 | SEG14 | SEG13 | SEG12 |

| \$104 | SEG19 | SEG18 | SEG17 | SEG16 | \$114 | SEG19 | SEG18 | SEG17 | SEG16 |  | \$1F4 | SEG19 | SEG18 | SEG17 | SEG16 |

| \$105 | SEG23 | SEG22 | SEG21 | SEG20 | \$115 | SEG23 | SEG22 | SEG21 | SEG20 |  | \$1F5 | SEG23 | SEG22 | SEG21 | SEG20 |

| \$106 | SEG27 | SEG26 | SEG25 | SEG24 | \$116 | SEG27 | SEG26 | SEG25 | SEG24 |  | \$1F6 | SEG27 | SEG26 | SEG25 | SEG24 |

| \$107 | SEG31 | SEG30 | SEG29 | SEG28 | \$117 | SEG31 | SEG30 | SEG29 | SEG28 |  | \$1F7 | SEG31 | SEG30 | SEG29 | SEG28 |

| \$108 | SEG35 | SEG34 | SEG33 | SEG32 | \$118 | SEG35 | SEG34 | SEG33 | SEG32 |  | \$1F8 | SEG35 | SEG34 | SEG33 | SEG32 |

| \$109 | SEG39 | SEG38 | SEG37 | SEG36 | \$119 | SEG39 | SEG38 | SEG37 | SEG36 |  | \$1F9 | SEG39 | SEG38 | SEG37 | SEG36 |

| \$10A | -     | -     | -     | -     | \$11A | -     | -     | -     | -     |  | \$1FA | -     | -     | -     | -     |

| \$10B | -     | -     | -     | -     | \$11B | -     | -     | -     | -     |  | \$1FB | -     | -     | -     | -     |

| \$10C | -     | -     | -     | -     | \$11C | -     | -     | -     | -     |  | \$1FC | -     | -     | -     | -     |

| \$10D | -     | -     | -     | -     | \$11D | -     | -     | -     | -     |  | \$1FD | -     | -     | -     | -     |

| \$10E | -     | -     | -     | -     | \$11E | -     | -     | -     | -     |  | \$1FE | -     | -     | -     | -     |

| \$10F | -     | -     | -     | -     | \$11F | -     | -     | -     | -     |  | \$1FF | -     | -     | -     | -     |

Note: F The RAM space without name that listed above is empty space (no memory cell existed).

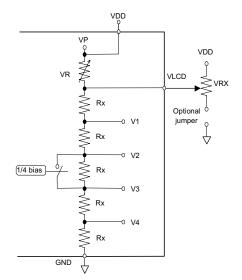

#### **LCD Contrast Control**

LCD contrast can easily be adjusted by software or by an external component (resistor or potentiometer). The simplified LCD power supply circuit below illustrates the idea of how the LCD contrast ratio can be adjusted by software programming. Because the VR is connected between VP and VLCD, the required contrast ratio can be

set by the value of register CVAR (\$03E). On the table below, it listed all the VR values according to different programming value of register, CVAR. Note that the default value of CVAR is zero. In addition, this contrast ratio can easily be modified by an external potentiometer. The following figure shows how they are configured.

| CVAR.3 | CVAR.2 | CVAR.1 | CVAR.0 | VR   |

|--------|--------|--------|--------|------|

| 0      | 0      | 0      | 0      | 35ΚΩ |

| 0      | 0      | 0      | 1      | 30ΚΩ |

| 0      | 0      | 1      | 0      | 25ΚΩ |

| 0      | 0      | 1      | 1      | 20ΚΩ |

| 0      | 1      | 0      | 0      | 15ΚΩ |

| 0      | 1      | 0      | 1      | 10ΚΩ |

| 0      | 1      | 1      | 0      | 5ΚΩ  |

| 0      | 1      | 1      | 1      | 0ΚΩ  |

| 1      | 0      | 0      | 0      | 40ΚΩ |

| 1      | 0      | 0      | 1      | 45ΚΩ |

| 1      | 0      | 1      | 0      | 50ΚΩ |

| 1      | 0      | 1      | 1      | 55ΚΩ |

| 1      | 1      | 0      | 0      | 60ΚΩ |

| 1      | 1      | 0      | 1      | 65ΚΩ |

| 1      | 1      | 1      | 0      | 70ΚΩ |

| 4 | 4 | 4 | 4 | 75KO |

|---|---|---|---|------|

| 1 | 1 | 1 | 1 | 75KO |

#### **Low Power Consumption Modes**

To save power, user can issue one of the Low Power consumption modes by instructions, STOP or HALT. Both of these modes can make the CPU going sleep. It means that CPU does nothing anyway until an external

interrupt or a reset signal comes up. STOP mode will save more power than that of the others (HALT or NORMAL), however, it takes a little bit longer to wake up the CPU due to the settling time for main oscillator.

| Operation mode | Issued by instruction | Main<br>oscillator | Watch<br>oscillator | RAM<br>Data | Registers<br>& Flags | I/O<br>Pins | Released by                      |

|----------------|-----------------------|--------------------|---------------------|-------------|----------------------|-------------|----------------------------------|

| Stop Mode      | STOP                  | Stop               | Alive               | Hold        | Hold                 | Hold        | Reset, IRQ0~3, IRQT0 or IRQRT    |

| Halt Mode      | HALT                  | Alive              | Alive               | Hold        | Hold                 | Hold        | Reset or any available interrupt |

#### **Battery-low Detection**

To monitor power consumption, the function of battery-low detection is enabled by setting ENBAT (\$01F.2) to one. The Battery-low detection table shows what the 3 bits, BAT.2-0 (\$03D.2-0), would respond while the battery power drops to a certain rank of voltage level. ENBAT should be reset to zero while it is not in use.

#### **DTMF Generation Circuit**

This chip provides a dual tone multi-frequency (DTMF) generation circuit. The DTMF signal consists of two sine waves with which to access the switching system. The following figure shows the relationship between the key pressed and its dual tone frequencies.

The DTMF generator employs 2 dedicate D/A converters, which can generate two separate single-tone signals, low-frequency group for Row and high-frequency group for Column. These two signals would finally mix together producing a Dual Tone Frequency Signal. Each single-tone signal consists of 32-level waveform that guarantees low distortion signal quality.

This DTMF is basically controlled by a 4-bit write-only Tone Generator Control register, TGC, and the signal data would be prepared by programming another 4-bit write-only register called Tone Generator Data register, TGD.

#### **Battery-low detection table**

| Power Supply Level | BAT.2 | BAT.1 | BAT.0 |

|--------------------|-------|-------|-------|

| 4.4V < VDD         | 0     | 0     | 0     |

| 3.6V < VDD ≤ 4.4V  | 1     | 0     | 0     |

| 2.8V < VDD ≤ 3.6V  | 1     | 1     | 0     |

| VDD ≤ 2.8V         | 1     | 1     | 1     |

These two registers, TGC & TGD, would be cleared to zero while system is reset.

Single Tone signal can also be generated for quality checking by means of programming TGC.1 or TGC.2.

| COL   | 1209Hz | 1336Hz | 1477Hz | 1633Hz |

|-------|--------|--------|--------|--------|

| 697Hz | 1      | 2      | 3      | Α      |

| 770Hz | 4      | 5      | 6      | В      |

| 852Hz | 7      | 8      | 9      | С      |

| 941Hz | #      | 0      | *      | D      |

### Tone Generator Control Register: TGC (\$01A)

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function      |            |            |  |

|-------|-------|-------|-------|---------------|------------|------------|--|

| Dit 3 | Dit 2 |       | Bit 0 | Column signal | Row signal | DTMF power |  |

|       | X     | X     | 0     | Disable       | Disable    | OFF        |  |

|       | 0     | 0     | 1     | Disable       | Disable    | ON         |  |

|       | 0     | 1     | 1     | Disable       | Enable     | ON         |  |

|       | 1     | 0     | 1     | Enable        | Disable    | ON         |  |

|       | 1     | 1     | 1     | Enable        | Enable     | ON         |  |

### Tone Generator Data Register: TGD (\$01B)

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Output Frequency | Digit  |

|-------|-------|-------|-------|------------------|--------|

| 0     | 1     | 1     | 1     | 941 + 1336Hz     | ″0 ″   |

| 0     | 0     | 0     | 0     | 697 + 1209Hz     | ″1 ″   |

| 0     | 1     | 0     | 0     | 697 + 1336Hz     | ″2 ″   |

| 1     | 0     | 0     | 0     | 697 + 1477Hz     | ″3 ″   |

| 0     | 0     | 0     | 1     | 770 + 1209Hz     | ″4 ″   |

| 0     | 1     | 0     | 1     | 770 + 1336Hz     | ″5 ″   |

| 1     | 0     | 0     | 1     | 770 + 1477Hz     | ″6 ″   |

| 0     | 0     | 1     | 0     | 852 + 1209Hz     | ″7 ″   |

| 0     | 1     | 1     | 0     | 852 + 1336Hz     | ″8 ″   |

| 1     | 0     | 1     | 0     | 852 + 1477Hz     | ″9 ″   |

| 0     | 0     | 1     | 1     | 941 + 1209Hz     | //* // |

| 1     | 0     | 1     | 1     | 941 + 1477Hz     | ″# ″   |

| 1     | 1     | 0     | 0     | 697 + 1633Hz     | "A "   |

| 1     | 1     | 0     | 1     | 770 + 1633Hz     | ″B ″   |

| 1     | 1     | 1     | 0     | 852 + 1633Hz     | ″C ″   |

| 1     | 1     | 1     | 1     | 941 + 1633Hz     | ″D ″   |

### Clock Selection Register: CKS (\$00D)

CKS.0~1 is in charge of controlling the speed of CPU. After the value of CKS.0~1 has been changed, the speed of CPU will be changed on the next instruction without any additional delay. ENOSC (CKS.2) is such a bit for

controlling the clock source for FSK demodulator and Frequency counter for Ring detection. For Caller-ID application, it is recommended that ENOSC should be set to one during initialization.

| Bit3 | Bit2 | Bit1 | Bit0 | Description                                                                     |

|------|------|------|------|---------------------------------------------------------------------------------|

|      |      |      | 0    | System Clock = Fmain / 16                                                       |

|      |      | 0    | 1    | System Clock = Fmain / 8                                                        |

|      |      | 1    | 0    | System Clock = Fmain / 4                                                        |

|      |      | 1    | 1    | Inhibited                                                                       |

|      | 0    |      |      | Disable the clock for FSK demodulator                                           |

|      | 1    |      |      | Enable the clock for FSK demodulator (Must be set to one during initialization) |

## **Beeper Output Circuit**

The beep output circuit can be selected by setting the RAM-mapped register bit, BEEP (\$03D.0) to one. The beep mode register (BPM) is the register used to specify operation mode of the beep output circuit. This circuit can

also be implement as a key-tone generator by software programming so that different key-tone may indicate different key operation message, such as, acceptance or error message.

### Beep Mode Register, BPM

| BEEP (\$03D.0) |       | BPM ( | (\$00E) |       | P0.3    | BUZ        |            |            |  |

|----------------|-------|-------|---------|-------|---------|------------|------------|------------|--|

|                | ВРМ.3 | BPM.2 | BPM.1   | BPM.0 |         | CKS = xx10 | CKS = xx01 | CKS = xx00 |  |

| 0              | Х     | Х     | Х       | Х     | Enable  | Disable    | Disable    | Disable    |  |

| 1              | 0     | Х     | Х       | Х     | Disable | Low        | Low        | Low        |  |

| 1              | 1     | Х     | 0       | 0     | Disable | 7KHz       | 3.5KHz     | 1.7KHz     |  |

| 1              | 1     | Х     | 0       | 1     | Disable | 3.5KHz     | 1.7KHz     | 874Hz      |  |

| 1              | 1     | Х     | 1       | 0     | Disable | 1.7KHz     | 874Hz      | 437Hz      |  |

| 1 | 1 | Х | 1 | 1 | Disable | 874Hz | 437Hz | 219Hz |

|---|---|---|---|---|---------|-------|-------|-------|

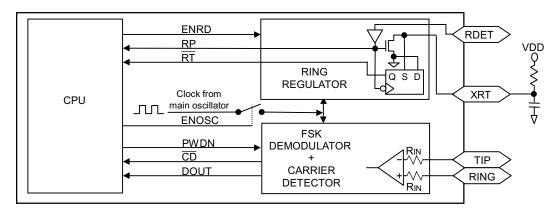

### Built-in FSK Demodulator, Carrier Detector and Ring regulator

A FSK demodulator, Carrier detector and Ring detector are employed to serve the Calling Identification. These circuits are merged to a 4-bit CPU by several interface signals, which are described below:

Fmain: System clock from main oscillator ENRD: Enable the internal Ring Detector PWDN: Switch off/on the FSK demodulator only

RP: Ring pulse signal RT: Ring time signal

XRT: Ring detected output signal CD: Carrier detected signal DOUT: Data output stream

If there is any part of the Ring Detector has to be utilized, bit ENRD must be set to 1 first.  $\overline{\text{CD}}$  or  $\overline{\text{RD}}$  will be available only if ENOSC = 1. It is recommended that bit ENOSC should be set to one during initialization. Details should be referred to the section of Timing Description.

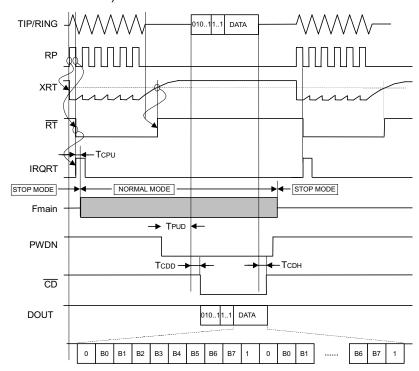

### Timing Diagram (ENRD = ENOSC = 1)

### **Timing description**

#### A. Software detection with internal Ring regulator (ENRD=1)

- Step 1: After power up initialization, CPU should enters into stop mode, and also FSK demodulator should enters into power down mode for saving power.

- Step 2: During ringing, the internal Ring regulator will sense the ring-in signal and will send out an interrupt request, IRQRT, to CPU. After receiving such request, CPU will then activate the main oscillator, so as to enter into normal operation mode.

- Step 3: Afterwards, CPU should check the bit RP (\$3D.3) bit if it is ring-in signal until time out. (Notes that checking the ringing frequency by software needs a relative complicate programming sequence!) If this RP signal has been confirmed by software, CPU should

- check the bit RT until it goes high. At this moment, CPU should reset bit PWDN (\$3D.2) in order to turn on the FSK demodulator for detecting carrier. Otherwise, CPU should return to STOP mode until next.

- Step 4: Once the FSK demodulator senses the FSK signal, the bit CD (\$3C.1) would go low and an interrupt request, IRQCD, would be issued. This interrupt request starts up the service routine for sampling out the data stream from the bit DOUT.

- Step 5: CD and DOUT will go back to high after FSK signal disappeared. Also CPU should then return to STOP mode and prepares for another Ringing.

### B. Software detection with external Ring regulator (ENRD=0, and IRQn is employed)

- Step 1: After power up initialization, CPU should enters into stop mode, and also FSK demodulator should enters into power down mode for saving power.