PRELIMINARY

## **4K 4-bit Microcontroller with LCD Driver**

---

### **Features**

- SH6610C-based single-chip 4-bit microcontroller with LCD driver.

- ROM: 4096 X 16 bits.

- RAM: 256 X 4 bits.

- Operation voltage: 1.2V ~ 1.7V.

- 4-Level subroutine nesting (include interrupts).

- One 8-bit Timers with pre-divider circuit.

- One 8-bit Base Timer.

- Warm-up timer for power on reset.

- Powerful interrupt sources:

- External interrupts (Falling or rising edge)

- Timer0 interrupts

- Base Timer interrupts

- PORTB, C interrupts (Falling or rising edge)

- 24 CMOS bi-directional I/O pins.

- -PC, PD, PE, PF can switch to segment.

- LCD driver: Up to 6x 38 dots.

- 1/6 duty, 1/3 bias; 1/5 duty, 1/3 bias; 1/4 duty, 1/3 bias or 1/3 duty, 1/2 bias selected by code option.

- 17 segment shared with PORTC, D, E, F and CX.

- Built-in voltage double and treble charge pump circuit.

- Dual clock sources:

- OSC: Crystal oscillator: 32.768kHz, RC oscillator: 32kHz or 131kHz. (selected by code option)

- OSCX: Ceramic oscillator: 455kHz, RC oscillator: 262kHz or 500kHz (400kHz~600kHz). (Selected by system register).

- Instruction cycle time:

- 122.07 $\mu$ s for 32.768 kHz crystal

- 30.53 $\mu$ s for 131 kHz RC

- 8.79 $\mu$ s for 455kHz ceramic

- 15.27 $\mu$ s for 262kHz RC

- 8 $\mu$ s for 500kHz RC

- Built-in 2-channel PSG.

- Built-in alarm generator.

- Built-in EL-light driver.

- Built-in watchdog timer.

- Built-in RESET de-bounce circuit.

- Built-in Resistor to Frequency converts circuit.

- Two low power operation modes: HALT and STOP.

- Low power consumption.

- Bonding option for multi-code software.

- Available in CHIP FORM

### **General Description**

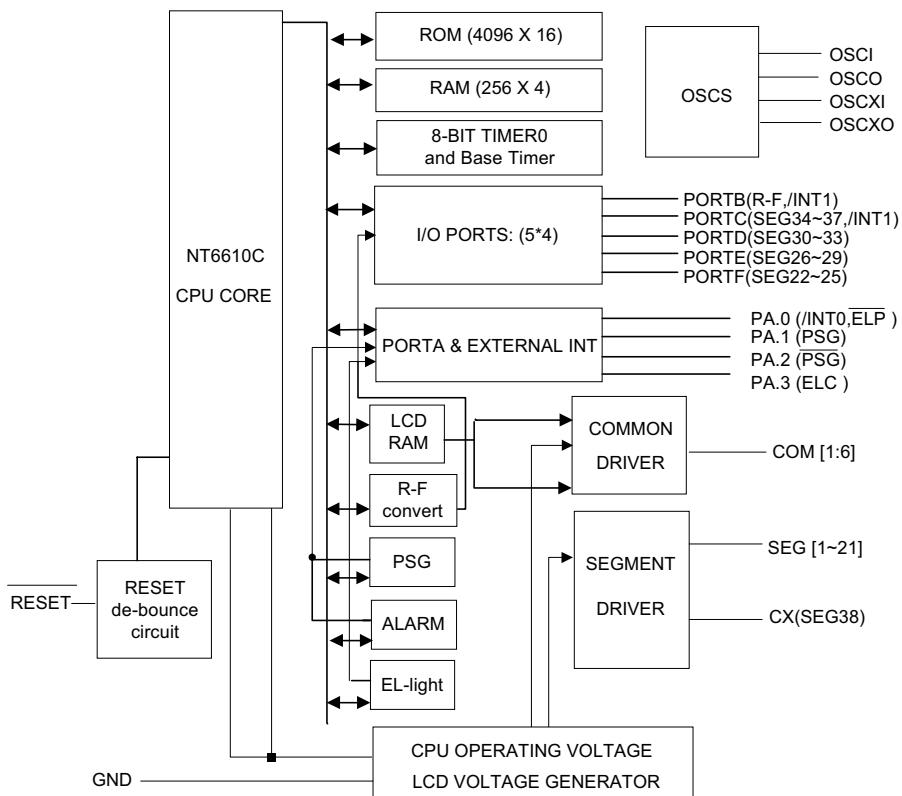

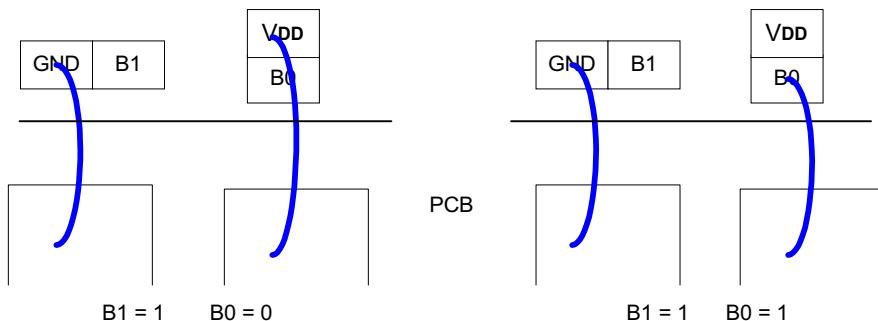

SH67L19 is a single chip microcontroller integrated with 4K mask ROM, SRAM, timer, PSG, alarm, R-F, EL-light, LCD driver, I/O ports. This chip builds in a dual-oscillator to enhance the total chip performance.

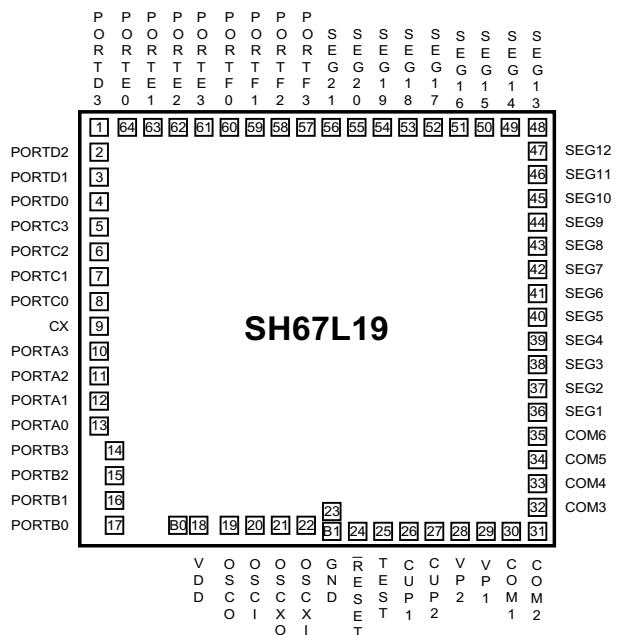

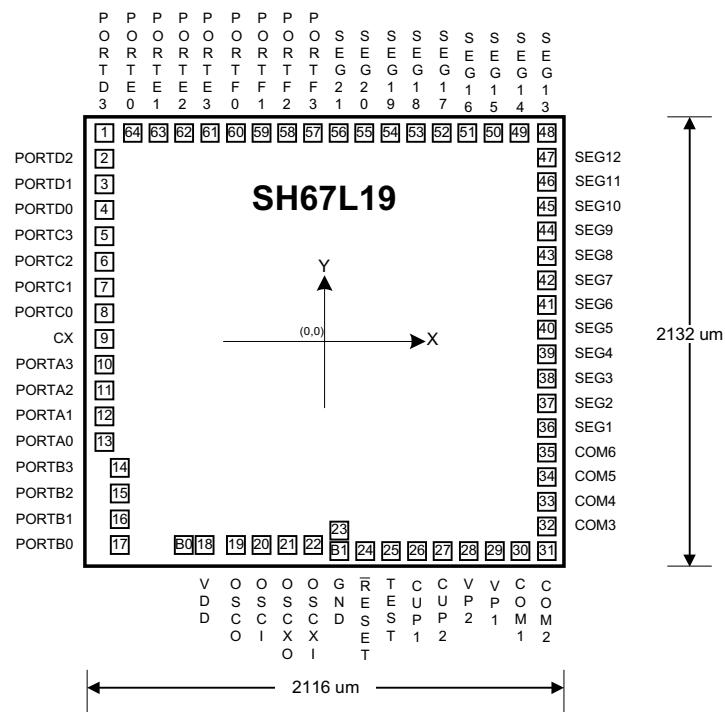

## Pad Configuration

## Block Diagram

**Pad Description**

| PIN No. | Designation  | I/O | Description                                                                                                                                                                                                            |

|---------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36 – 56 | SEG1 – SEG21 | O   | Segment signal output for LCD display,                                                                                                                                                                                 |

| 30 – 35 | COM1 – COM6  | O   | Common signal output for LCD display                                                                                                                                                                                   |

| 29, 28  | VP1, VP2     | P   | Power supply pin for LCD driver.                                                                                                                                                                                       |

| 26, 27  | CUP1 ~ 2     | P   | Connection for voltage doubler capacitor.                                                                                                                                                                              |

| 25      | TEST         | I   | Test pin (Internal pull-low). No connect for user.                                                                                                                                                                     |

| 24      | RESET        | I   | Reset input (internal pull-high selected by code option).                                                                                                                                                              |

| 18      | VDD          | P   | Power supply.                                                                                                                                                                                                          |

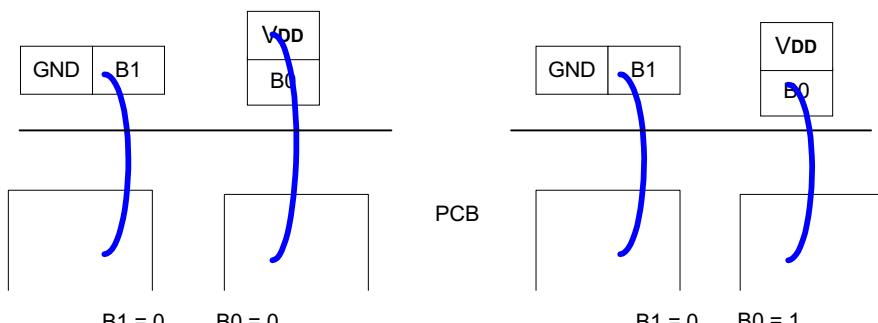

|         | B0           | I   | Bonding option, internally pull-low.                                                                                                                                                                                   |

|         | B1           | I   | Bonding option, internally pull-high.                                                                                                                                                                                  |

| 23      | GND          | P   | Ground pin.                                                                                                                                                                                                            |

| 21      | OSCxo        | O   | Oscillator X output                                                                                                                                                                                                    |

| 22      | OSCxi        | I   | Oscillator X input                                                                                                                                                                                                     |

| 19      | OSCO         | O   | Oscillator output                                                                                                                                                                                                      |

| 20      | OSCI         | I   | Oscillator input                                                                                                                                                                                                       |

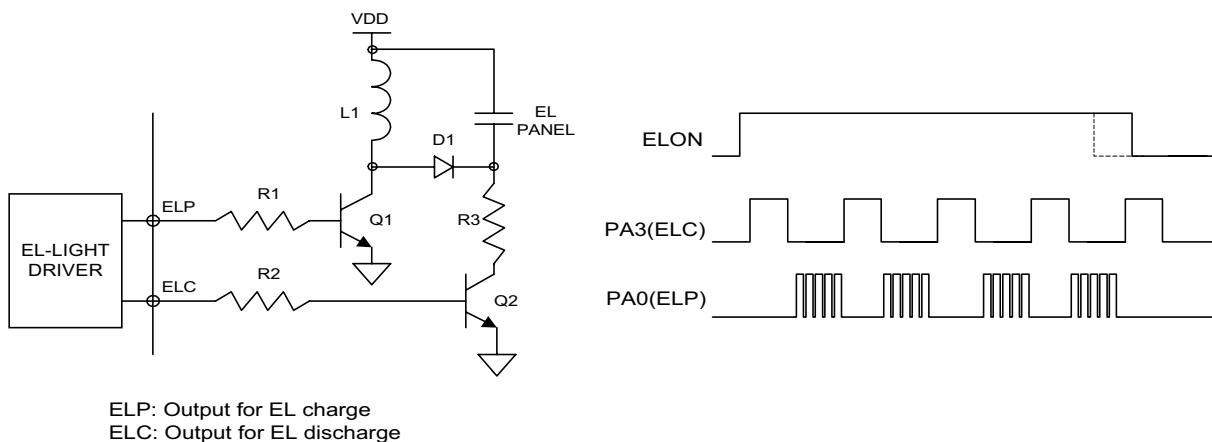

| 10 – 13 | PORTA3~0     | I/O | Bit programmable I/O, PA0 could be External Interrupt (/INT0), PA0 input is a schmitt trigger<br>PA.0, PA.3 could be EL-light output PA.0 (ELP), PA.3 (ELC). PA.1, PA.2 could be buzzer output PA.1 (PSG), PA.2 (/PSG) |

| 14 – 17 | PORTB3~0     | I/O | Bit programmable I/O, PB could be PORT Interrupt (/INT1)<br>PB.0 ~2 shared with RX1~3, PB.3 shared with RXB.                                                                                                           |

| 5 – 8   | PORTC3~0     | I/O | Bit programmable I/O, PC could be PORT Interrupt (/INT1).<br>PORTC3~0 shared with LCD Seg34~37.                                                                                                                        |

| 1 – 4   | PORTD3~0     | I/O | Bit programmable I/O, PORTD3~0 shared with LCD Seg30~33.                                                                                                                                                               |

| 61 – 64 | PORTE3~0     | I/O | Bit programmable I/O, PORTE3~0 shared with LCD Seg26~29.                                                                                                                                                               |

| 57 – 60 | PORTF3~0     | I/O | Bit programmable I/O, PORTF3~0 shared with LCD Seg22~25.                                                                                                                                                               |

| 9       | CX           | I/O | R-F converter counter input pin, shared with Seg38.                                                                                                                                                                    |

## Functional Description

### 1.CPU

The CPU core contains the following function blocks: Program Counter, ALU, Carry Flag, Accumulator, Table Branch Register (TBR), Data Pointer (INX, DPH, DPM and DPL), and Stack.

#### 1.1. PC (Program Counter)

The PC is used for ROM addressing consisting of 12-bits: Page Register (PC11), and Ripple Carry Counter (PC10 - PC0).

The program counter normally increases by one (+1) with each execution of an instruction except in the following cases:

- (1) When executing a jump instruction (such as JMP, BA0, BC),

- (2) When executing a subroutine call instruction (CALL),

- (3) When an interrupt occurs,

- (4) When the chip is at INITIAL RESET.

The program counter is loaded with data corresponding to each instruction. The unconditional jump instruction (JMP) can be set at 1-bit page register for higher than 2K. Program Counter can only address a 4K of program ROM.

#### 1.2. ALU and CY

The ALU performs arithmetic and logic operations.

It provides the following functions:

Binary addition/subtraction

(ADC, SBC, ADD, SUB, ADI, SBI)

Decimal adjustment for addition/subtraction (DAA, DAS), Logic operations (AND, EOR, OR, ANDIM, EORIM, ORIM)

Decision (BA0, BA1, BA2, BA3, BAZ, BC)

The Carry Flag (CY) holds the arithmetic operation ALU overflow.

During interrupt or call instruction, carry is pushed into stack and restored from stack by RTNI. It is unaffected by an RTNW instruction.

#### 1.3. Accumulator

The accumulator is a 4-bit register holding the results of the arithmetic logic unit. In conjunction with the ALU, data transfers between the accumulator and system register, LCD RAM, or data memory can be performed.

#### 1.4. Stack

This group of registers is used to save the contents of CY & PC (11 - 0) sequentially with each subroutine call or interrupt. It is organized 13 bits X 4 levels. The MSB is saved for CY. Four levels are the maximum allowed for subroutine calls and interrupts.

The contents of Stack are returned sequentially to the PC with the return instructions (RTNI/RTNW). Stack is operated on a first-in, last-out basis. This 4-level nesting includes both subroutine calls and interrupts requests. Note that program execution may enter an abnormal state if the number of calls and interrupt requests exceeds 4, where then the bottom of stack will be shifted out.

## 2.ROM

SH67L19 can address  $4096 \times 16$  bit of program area \$000 to \$FFF. There is an area from addresses \$000 through \$004 that is reserved for special interrupts service routines such as starting vector address.

| Address | Instruction     | Function                                           |

|---------|-----------------|----------------------------------------------------|

| 000H    | JMP Instruction | Jump to RESET service routine                      |

| 001H    | JMP Instruction | Jump to external interrupt service routine (/INT0) |

| 002H    | JMP Instruction | Jump to Timer0 service routine                     |

| 003H    | JMP Instruction | Jump to Base Timer service routine                 |

| 004H    | JMP Instruction | Jump to PORTB, C service routine (/INT1)           |

### 3.RAM

Built-in SRAM contains general-purpose data memory, LCD RAM, and system registers. Direct addressing in one instruction can access them.

The following is the memory allocation map:

\$000 - \$01F: System register and I/O.      \$020 - \$11F: Data memory ( $256 \times 4$  bits, divide into 2 banks).

\$300 - \$325, \$330 - \$355: LCD RAM      \$360 - \$368: PSG control registers ( $9 \times 4$  bits).

\$269 - \$26D: R-F counter registers ( $5 \times 4$  bit)

#### The configuration of system register

| Address | Bit3  | Bit2  | Bit1   | Bit0  | R/W | Function                                                                                                                                                                                       | Initial Value |

|---------|-------|-------|--------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| \$00    | IEX   | IETO  | IEBT   | IEP   | R/W | Interrupt enable flags                                                                                                                                                                         | 0000          |

| \$01    | IRQX  | IRQT0 | IRQBT  | IRQP  | R/W | Interrupt request flags                                                                                                                                                                        | 0000          |

| \$02    | TM0.3 | TM0.2 | TM0.1  | TM0.0 | R/W | Timer0 mode register                                                                                                                                                                           | 0000          |

| \$03    | BTM.3 | BTM.2 | BTM.1  | BTM.0 | R/W | Base timer mode register                                                                                                                                                                       | 0000          |

| \$04    | T0L.3 | T0L.2 | T0L.1  | T0L.0 | R/W | Timer0 load/counter low nibble                                                                                                                                                                 | 0000          |

| \$05    | T0H.3 | T0H.2 | T0H.1  | T0H.0 | R/W | Timer0 load/counter high nibble                                                                                                                                                                | 0000          |

| \$06    | ENX   | ELON  | LCDOFF | PSGON | R/W | Bit0: PSG on/off control<br>Bit1: LCD on/off control<br>Bit2: EL-light on/off control<br>Bit3: R-F convert counter on/off control                                                              | 0010          |

| \$07    | O/RF  | RX3EN | RX2EN  | RX1EN | R/W | Bit0~2: count resister1~3 enable.<br>Bit3: set Port B as R-F converter.                                                                                                                        | 0000          |

| \$08    | PA.3  | PA.2  | PA.1   | PA.0  | R/W | PORTA data register                                                                                                                                                                            | 0000          |

| \$09    | PB.3  | PB.2  | PB.1   | PB.0  | R/W | PORTB data register                                                                                                                                                                            | 0000          |

| \$0A    | PC.3  | PC.2  | PC.1   | PC.0  | R/W | PORTC data register                                                                                                                                                                            | 0000          |

| \$0B    | PD.3  | PD.2  | PD.1   | PD.0  | R/W | PORTD data register                                                                                                                                                                            | 0000          |

| \$0C    | PE.3  | PE.2  | PE.1   | PE.0  | R/W | PORTE data register                                                                                                                                                                            | 0000          |

| \$0D    | PF.3  | PF.2  | PF.1   | PF.0  | R/W | PORTF data register                                                                                                                                                                            | 0000          |

| \$0E    | TBR.3 | TBR.2 | TBR.1  | TBR.0 | R/W | Table branch register                                                                                                                                                                          | -             |

| \$0F    | INX.3 | INX.2 | INX1   | INX.0 | R/W | Index register (INX)                                                                                                                                                                           | -             |

| \$10    | DPL3  | DPL2  | DPL1   | DPL0  | R/W | Data pointer for INX low nibble                                                                                                                                                                | -             |

| \$11    | -     | DPM.2 | DPM.1  | DPM.0 | R/W | Data pointer for INX middle nibble                                                                                                                                                             | -             |

| \$12    | -     | DPH.2 | DPH.1  | DPH.0 | R/W | Data pointer for INX high nibble                                                                                                                                                               | -             |

| \$13    | ELF   | ELPF  | SOH/L  | S/CX  | R/W | Bit0: Set CX as LCD segment 38<br>Bit1: Select LCD segment output high or low<br>EL-LIGHT mode control<br>Bit2: ELP driver output frequency control.<br>Bit3: EL-LIGHT driver frequency select | 0001          |

| \$14    | OXS   | OXM   | OXON   | HLM   | R/W | Bit0: Heavy Load Mode<br>Bit1: Turn on OSCX oscillator<br>Bit2: CPU clocks select (1:OSCX /0:OSC)<br>Bit3: OSCX type selection                                                                 | 0000          |

## System register (Cont.)

| Address | Bit3   | Bit2   | Bit1   | Bit0   | R/W   | Function                                                                                                                                                 | Initial Value |

|---------|--------|--------|--------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| \$15    | PULLEN | PH/PL  | B1     | B0     | R/W R | Bit0,1: Bonding Option<br>Bit2: Port pull high (falling edge interrupt) or pull low (rising edge interrupt) select<br>Bit3: pull high/low enable control | 0010          |

| \$16    | O/S4   | O/S3   | O/S2   | O/S1   | R/W   | Bit0: Set PORTC as LCD segment<br>Bit1: Set PORTD as LCD segment<br>Bit2: Set PORTE as LCD segment<br>Bit3: Set PORTF as LCD segment                     | 1111          |

| \$17    | WDT    | WT2    | WT1    | WT0    | W     | Bit3: WDT time-out bit (write one to reset WDT)<br>Bit2~0: Watchdog timer on/off control (initial: 010, watchdog on)                                     | 1010          |

| \$18    | PACR.3 | PACR.2 | PACR.1 | PACR.0 | W     | Set PORTA to be output port                                                                                                                              | 0000          |

| \$19    | PBCR.3 | PBCR.2 | PBCR.1 | PBCR.0 | W     | Set PORTB to be output port                                                                                                                              | 0000          |

| \$1A    | PCCR.3 | PCCR.2 | PCCR.1 | PCCR.0 | W     | Set PORTC to be output port                                                                                                                              | 0000          |

| \$1B    | -      | PFCR   | PECR   | PDCR   | W     | Bit0: Set PORTD to be output port<br>Bit1: Set PORTE to be output port<br>Bit2: Set PORTF to be output port                                              | -000          |

| \$1C    | PCIN   | PDIN   | PEIN   | PFIN   | W     | When PC~PF used as input, their input state control. Used in key matrix's application                                                                    | 0000          |

| \$1D    |        |        | PAIN   | PBIN   | W     | When PA, PB used as input, their input state control. Used in key matrix's application                                                                   | --00          |

| \$1E~1F | -      | -      | -      | -      |       | Reserved                                                                                                                                                 |               |

| \$360   | C1.3   | C1.2   | C1.1   | C1.0   | W     | PSG channel 1 low nibble                                                                                                                                 | 0000          |

| \$361   | CM1    | C1.6   | C1.5   | C1.4   | W     | PSG channel 1high nibble<br>Bit3: channel 1 mode control                                                                                                 | 0000          |

| \$362   | C2.3   | C2.2   | C2.1   | C2.0   | W     | PSG channel 2 nibble 1 or alarm output                                                                                                                   | 0000          |

| \$363   | C2.7   | C2.6   | C2.5   | C2.4   | W     | PSG channel 2 nibble 2                                                                                                                                   | 0000          |

| \$364   | C2.11  | C2.10  | C2.9   | C2.8   | W     | PSG channel 2 nibble 3                                                                                                                                   | 0000          |

| \$365   | CM2    | C2.14  | C2.13  | C2.12  | W     | PSG channel 2 nibble 4<br>Bit3: channel 2 mode control                                                                                                   | 0000          |

| \$366   | VOL1   | VOL0   | CH2EN  | CH1EN  | W     | Bit0, Bit1: Channel 1, 2 enable<br>Bit2, Bit3: volume control                                                                                            | 0000          |

| \$367   | P2.1   | P2.0   | P1.1   | P1.0   | W     | PSG1 and PSG2 Pre-scalar                                                                                                                                 | 0000          |

| \$368   | -      | F262   | ALM    | SEL    | W     | Bit0: PSG clock source select.<br>Bit1: Alarm on or off.<br>Bit2: OSCX RC oscillator select                                                              | 0000          |

| \$269   | RF1.3  | RF1.2  | RF1.1  | RF1.0  | R/W   | R-F counter register nibble 1 (bit0~3)                                                                                                                   | 0000          |

| \$26A   | RF2.3  | RF2.2  | RF2.1  | RF2.0  | R/W   | R-F counter register nibble 2 (bit4~7)                                                                                                                   | 0000          |

| \$26B   | RF3.3  | RF3.2  | RF3.1  | RF3.0  | R/W   | R-F counter register nibble 3 (bit8~11)                                                                                                                  | 0000          |

| \$26C   | RF4.3  | RF4.2  | RF4.1  | RF4.0  | R/W   | R-F counter register nibble 4 (bit12~15)                                                                                                                 | 0000          |

| \$26D   | RF5.3  | RF5.2  | RF5.1  | RF5.0  | R/W   | R-F counter register nibble 5 (bit16~19)                                                                                                                 | 0000          |

#### 4. Data memory

The general-purpose data memory is organized as 256 \* 4 bits. Because of its static feature, the RAM can retain data after the CPU enters STOP or HALT mode.

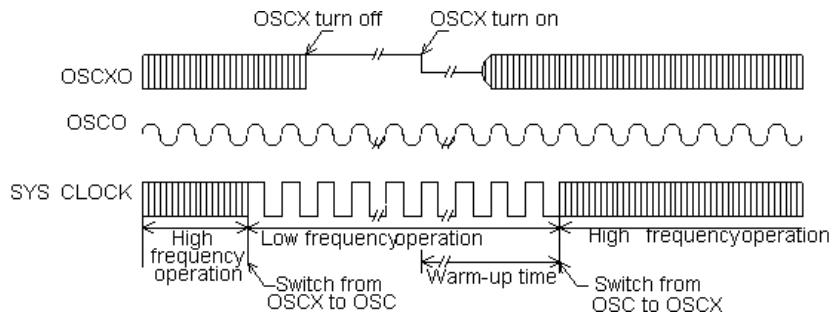

#### 5. Oscillator circuit

##### 5.1. Circuit Configuration

SH67L19 has two on-chip oscillation circuits OSC and OSCX.

OSC is a low frequency crystal (32.768kHz) or RC (32kHz or 131kHz) oscillator determined by the code option. This is designed for low frequency operation. OSCX is a high frequency ceramic (455kHz) or RC (262kHz or 500kHz) oscillator. It is designed for high frequency operation.

It is possible to select the high speed CPU processing by a high frequency clock and select low power operation by low operation clock. At the start of reset initialization, OSC is turned on and OSCX is turned off. Immediately after reset initialization, the OSC is automatically selected as the system clock input source.

When start of reset, the system clock must be use OSC, frequency is 32k crystal, 32k RC or 131k RC. After initialization, user can turn on OSCX. Then OSC can be switched to OSCX as system clock, and two-oscillation circuit can be switch to another random. If the OSCX is not used, the OSCXI pin must be connected to GND.

OSC and OSCX will be turned off in STOP mode. When wake up from STOP, the system clock also must be use OSC. After wake up from STOP, the OSC can be switched to OSCX as system clock, if user wants to use high frequency clock.

##### 5.2. Control of oscillator

The oscillator control register configuration is shown as follows:

| Address | Bit3 | Bit2 | Bit1 | Bit0 | Function                                                                                                    |

|---------|------|------|------|------|-------------------------------------------------------------------------------------------------------------|

| \$14    | OXS  | OXM  | OXON | HLM  | ...<br>Bit1: Turn on OSCX oscillator<br>Bit2: CPU clock select (1:OSCX /0:OSC)<br>Bit3: OSCX type selection |

OXON: OSCX oscillation on/off.

0: Turn-off OSCX oscillation

1: Turn-on OSCX oscillation

OXM: switching system clock.

0: select OSC as system clock

1: select OSCX as system clock

OXS: OSCX oscillator type selection.

0: OSCX set as Ceramic oscillation

1: OSCX set as RC oscillator

##### 5.3. Programming notes

It takes at least 5 ms for the OSCX oscillation circuit to turn on until the oscillation stabilizes. When switching the CPU system clock from OSC to OSCX, the user must wait a minimum of 5ms since the OSCX oscillation is running. However, the start time varies with respect to oscillator characteristics and the condition of use. Thus the wait time depends on the application. When switching from OSCX to OSC, and turning off OSCX in one instruction. The OSCX turn off control will be delayed for one instruction cycle automatically to prevent CPU operation error.

#### 5.4.Timing of System Clock Switching

#### 6.System clock

The system clock varies as the clock source changes. The following table shows the instruction execution time according to each frequency of the system clock source.

|            | 32.768k (OSC)  | 131k (OSC)   | 455k (OSC <sub>X</sub> ) | 262k (OSC <sub>X</sub> ) | 500k (OSC <sub>X</sub> ) |

|------------|----------------|--------------|--------------------------|--------------------------|--------------------------|

| Cycle time | 122.07 $\mu$ s | 30.5 $\mu$ s | 8.79 $\mu$ s             | 15.3 $\mu$ s             | 8 $\mu$ s                |

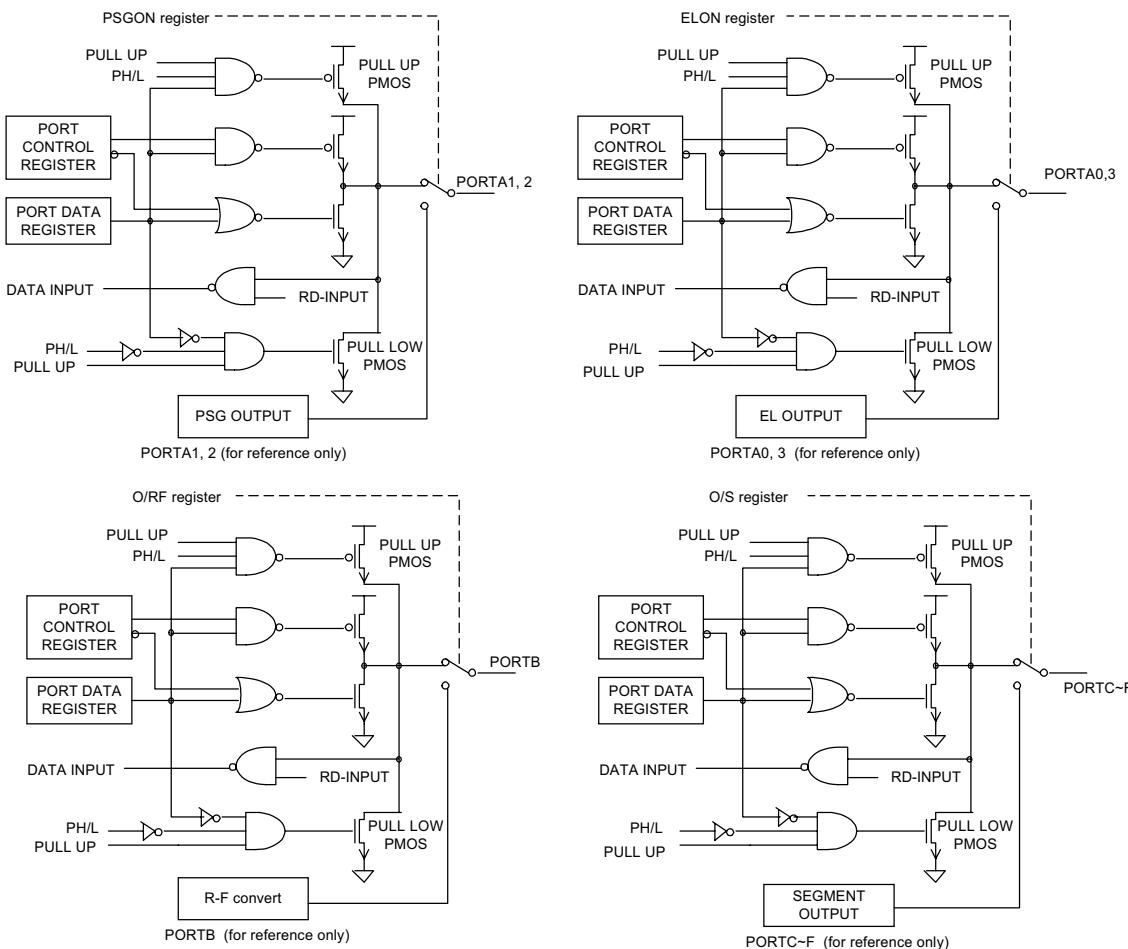

#### 7.I/O PORT

SH67L19 has 24 CMOS bi-directional I/O ports: PORTA~PORTF. Each I/O pin contains pull-high and pull-low MOS controllable through programming. The PORT control register controls the ON/OFF of the output buffer. I/O ports of SH67L19 can be accessed by read/write the system register. User can output any value to any I/O port bit at any time. The circuit configuration of PORTA - F as is shown as Figure 1.

##### 7.1. Controlling the pull-high/low MOS

PORTA~F contain pull-high/low MOS controlled by program. System register \$15 Bit3, Bit2 controls pull-high/low MOS on or off. Pull-high/low MOS is also controlled by the port data registers of each port as well. Thus the pull-high/low MOS can be turned on/off individually.

##### Port mode register (PMOD)

| Address | Bit3   | Bit2  | Bit1 | Bit0 | Function                                                                     |

|---------|--------|-------|------|------|------------------------------------------------------------------------------|

| \$15    | PULLEN | PH/PL | B1   | B0   | ...<br>Bit2: Port pull-high/low set<br>Bit3: Port pull-up/low enable control |

PULLEN: Pull high/low enable

0: Disable pull-high/low MOS      1: Enable pull-high/low MOS

PH/PL: select pull high or pull low

0: port pull low resistor on      1: port pull high resistor on

##### 7.2. Port Interrupt (/INT1)

The PORTB and PORTC are used as port interrupt sources (falling or rising edge), only the input port can generate PORT interrupt. When PULLEN=1, PH/PL=1 and IEP is set to 1, any one of the PORTB and PORTC input pin transitions from VDD to GND will generate an interrupt request. When PULLEN=1, PH/PL=0 and IEP is set to 1, any one of the PORTB and PORTC input pin transitions from GND to VDD will generate an interrupt request. When PORTB are used as R-F converter (O/RF=1), the PORTB interrupt were disabled even the IEP is set to 1. When PORTC are used as LCD outputs (O/S1=1), the PORTC interrupt were disabled also even the IEP is set to 1.

### 7.3. External Interrupt (/INT0)

The PORTA0 is used as external interrupt sources (falling or rising edge), only PA0 is input port can generate an external interrupt. When PULLEN=1, PH/PL=1 and IEX is set to 1, PA0 input pin transitions from VDD to GND will generate an interrupt request. When PULLEN=1, PH/PL=0 and IEX is set to 1, PA0 input pin transitions from GND to VDD will generate an interrupt request. When PA0 is used as ELP, the External interrupt was disabled even the IEX is set to 1.

NOTE: If internal PORT pull-high and pull-low resistor is not used, the SH67L19 will respond PBC or PA0 interrupt by connect resistor to VDD or GND externally.

### 7.4. Port I/O control register:

| Address | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|--------|--------|--------|--------|

| \$18    | PACR.3 | PACR.2 | PACR.1 | PACR.0 |

| \$19    | PBCR.3 | PBCR.2 | PBCR.1 | PBCR.0 |

| \$1A    | PCCR.3 | PCCR.2 | PCCR.1 | PCCR.0 |

| \$1B    | -      | PFCR   | PECR   | PDCR   |

I/O control register: PACR.X~PCCR.X (X = 0, 1, 2, 3) by bit control

1: Defined as an output terminal.

0: Defined as an input terminal (default).

PDCR, PECR, PFRCR by port control

1: Defined the port as output terminal.

0: Defined the port as input terminal (default).

Figure 1

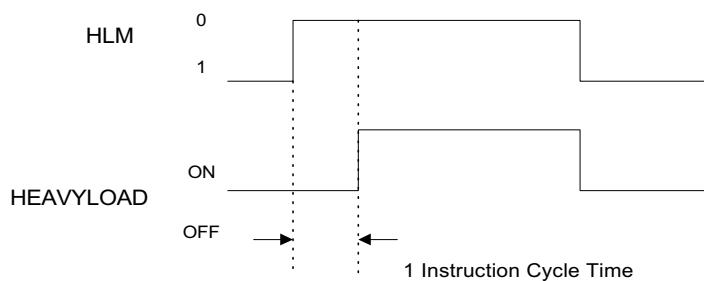

### 7.5. Heavy load mode (HLM)

| Address | Bit3 | Bit2 | Bit1 | Bit0 | Function                     |

|---------|------|------|------|------|------------------------------|

| \$14    | OXS  | OXM  | OXON | HLM  | Bit0: Heavy Load Mode<br>... |

HLM: 0 = Heavy load protection mode is released      1 = Heavy load protection mode is set.

The MCU has a heavy load protection circuit for when the battery load becomes heavy, such as, when an external buzzer sounds or an external speaker is turned on. In this mode, the low frequency crystal oscillator circuit and high frequency ceramic circuit have been backup for high gain. When setup this mode, more power would be provided to an oscillator circuit. Unless it is necessary, be careful not to set this mode with the software since the mode enters would delay for one instruction. Please activate heavy load driving only after setting HLM at least one instruction wait cycle through the software. The following shows the programming setting.

### 7.6. Ports as key matrix

SH67L19's I/O can make up key matrix and PortC~PortF can use as LCD segment output as same time. In this application, user should control that scanning key matrix share the timing of LCD display and will not affect the LCD display. Only when user scan key matrix, all of Ports are used as I/O; otherwise PC~PF use as LCD segment output to drive LCD panel. The Ports used as I/O or segment is controlled by software.

In scan key application, when user doesn't execute operation of scan key, Ports which don't share as LCD segment output should be set as I/O, disabled it's pull high/pull low resistor and input/output access by write system register (\$18H~\$1DH)'s corresponding bit. Execute above operation can prevent LCD voltage input to the general I/O Ports and Port's pull high/pull low or output affect the LCD segment's waveform.

When user wants to scan key, all ports which make up of the key matrix should be used as general I/O, the ports' pull high or pull low resistor and input access should be enabled by clear the system register (\$1CH, \$1DH)'s corresponding bit.

#### Key matrix's input ports control register

|       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | R/W | Remark                                                                                           |

|-------|-------|-------|-------|-------|-----|--------------------------------------------------------------------------------------------------|

| \$1CH | PCIN  | PDIN  | PEIN  | PFIN  | W   | Control PORTC~PORTF input and output access enable or disable. Used in key matrix's application. |

| \$1DH |       |       | PAIN  | PBIN  | W   | Control PORTA~PORTB input and output access enable or disable. Used in key matrix's application. |

PAIN...PFIN: In the key matrix's application, control PORTA~F input and output access.

0: Enable PA~PF pull high/pull low resistor and I/O access, Ports in normal state

1: Disable PA~PF pull high/pull low resistor and it's I/O access

## 8. Programmable sound generator (PSG)

PSG has channel1 and channel2. Channel 1 is a 7-bit pseudo random counter. Channel 2 is a 15-bit pseudo random counter. Mode bits C1M, C2M determine which of the two counters will be a noise or a tone generator. To reduce power consumption, disable the sound effect generator during STOP mode. Channel 2 TONE mode is same as Channel 1. (7-bit pseudo-random counter). PSG also provides alarm function. The alarm on or off controlled by register (ALM). This eliminates some programming codes.

|       |       |       |       |       |                                                                                                        |      |   |

|-------|-------|-------|-------|-------|--------------------------------------------------------------------------------------------------------|------|---|

| \$360 | C1.3  | C1.2  | C1.1  | C1.0  | PSG channel 1 low nibble                                                                               | 0000 | W |

| \$361 | CM1   | C1.6  | C1.5  | C1.4  | PSG channel 1 high nibble<br>Bit3: channel 1 mode control                                              | 0000 | W |

| \$362 | C2.3  | C2.2  | C2.1  | C2.0  | PSG channel 2 nibble 1 or alarm output                                                                 | 0000 | W |

| \$363 | C2.7  | C2.6  | C2.5  | C2.4  | PSG channel 2 nibble 2                                                                                 | 0000 | W |

| \$364 | C2.11 | C2.10 | C2.9  | C2.8  | PSG channel 2 nibble 3                                                                                 | 0000 | W |

| \$365 | CM2   | C2.14 | C2.13 | C2.12 | PSG channel 2 nibble 4<br>Bit3: channel 2 mode control                                                 | 0000 | W |

| \$366 | VOL1  | VOL0  | CH2EN | CH1EN | Bit0: Channel 1 enable<br>Bit1: Channel 2 enable<br>Bit2, Bit3: volume control (initially 0, no sound) | 0000 | W |

| \$367 | P2.1  | P2.0  | P1.1  | P1.0  | PSG1 and PSG2 Pre-scalar                                                                               | 0000 | W |

| \$368 | -     | F262  | ALM   | SEL   | Bit0: PSG clock source select.<br>Bit1: Alarm on or off.<br>Bit2: OSCX RC oscillator select            | 0000 | W |

### PA1 and PA2 output control and Vol. control

When PSGON = 1 and ALM=0, the PA1 PA2 is used as PSG output and controlled by the volume control bit into 4 volume levels output. When PSGON = 1 and ALM=1, the alarm function will open, PA1 PA2 is used as alarm output.

| PSGON | ALM | Function                    |

|-------|-----|-----------------------------|

| 0     | X   | PA1 and PA2 as I/O Port     |

| 1     | 0   | PA1 and PA2 as PSG output   |

| 1     | 1   | PA1 and PA2 as Alarm output |

| VOL1 | VOL0 | Vol. Level  |

|------|------|-------------|

| 0    | 0    | 1(no sound) |

| 0    | 1    | 2           |

| 1    | 0    | 3           |

| 1    | 1    | 4           |

### PSG two channels mode control

When use PSG output (PSGON = 1 and ALM=0), two channels' mode is controlled by C1M (\$362 bit3), C2M (\$365H bit3):

C1M: 1: channel 1 is noise generator. 0: channel 1 is tone generator.

C2M: 1: channel 2 is noise generator. 0: channel 2 is tone generator.

#### Channel 1

Channel 1 constructed by a 7-bit pseudo random counter. Channel 1 is enabled/disabled by CH1EN. It can be a 7-bit wide-band noise generator or a 7-bit sound generator. It can create either sound frequency by writing value N in C1.6~C1.0.

#### Channel 2

Channel 2 constructed by a 15-bit pseudo random counter. Channel 2 is enabled/disabled by CH2EN. It can be a 15-bit wide-band noise generator or a 7-bit sound generator. It can create either sound frequency by writing value N in C2.8~C2.14.

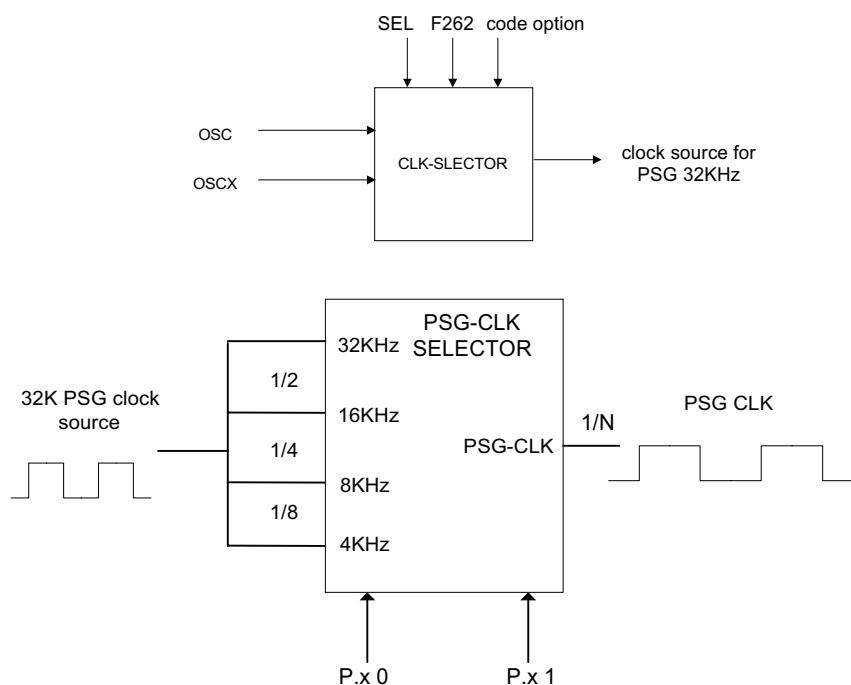

**PSG clock control register**

|       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Remark                                                                                      |

|-------|-------|-------|-------|-------|---------------------------------------------------------------------------------------------|

| \$367 | P2.1  | P2.0  | P1.1  | P1.0  | PSG1 and PSG2 Pre-scalar                                                                    |

| \$368 | -     | F262  | ALM   | SEL   | Bit0: PSG clock source select.<br>Bit1: Alarm on or off.<br>Bit2: OSCX RC oscillator select |

P1.0, P1.1 and P2.0, P2.1 select the pre-scalar of PSG actual clock.

| P1.1, P2.1 | P1.0, P2.0 | Pre-scalar Divide Ratio | Clock Source | Actual Clock |

|------------|------------|-------------------------|--------------|--------------|

| 0          | 0          | 1                       | 32K          | 32 kHz       |

| 0          | 1          | 2                       | 32K          | 16 kHz       |

| 1          | 0          | 4                       | 32K          | 8 kHz        |

| 1          | 1          | 8                       | 32K          | 4 kHz        |

SEL: select OSC or OSCX used to generate PSG clock source.

0: PSG clock source is provided by OSC (low frequency clock).

1: PSG clock source is provided by OSCX (high frequency clock)

F262: OSCX RC oscillator frequency selection.

0: Use 500k RC as oscillator

1: Use 262k RC as oscillator

When the OSCX is used as system clock, the value of bit "F262" must correspond to the OSCX's frequency. Otherwise PSG clock source will be not true. No matter which oscillator and frequency is selected to provide PSG clock source, the PSG clock source is always equal 32kHz.

**PSG sub-block diagram:**

**Example:**

A user uses 500kHz RC clock, and he wants to create a tone 'C3' whose frequency are 130.81Hz.

If he writes 00H to P.1 and P.0, and set OXON, OXM, OXS=1, that the 500k as system clock, PSG clock source is 32kHz and PSG-CLK=32kHz, the value of N is  $32k/130.81/2=122.3$ , look up 122 in the table, the corresponding initial data of LSFR is 20H.

If he writes 01H to P.1 and P.0, then the PSG-CLK is 16kHz, the value of N is  $16k/130.81/2=61.2$ , and the initial data is 49H

If he writes 10H to P.1 and P.0, then the PSG-CLK is 8kHz, the value of N is  $8k/130.81/2=31$ , and the initial data is 4BH.

If he writes 11H to P.1 and P.0, then the PSG-CLK is 4kHz, the value of N is  $4k/130.81/2=15$ , and the initial data is 15H.

When the tone frequency is too low, the wanted value of N maybe greater than 127, the counter cannot create this value, the better way is to select low PSG-CLK. For example, the frequency of tone 'C1' is 32.7Hz, if the PSG-CLK is greater than 8KHz, the wanted N is greater than 127, but the 4kHz PSG-CLK can create this tone.

According to the illustration before, users can make a music table themselves, If user selects any oscillator and PSG-CLK, the music table is provided as following.

**Music Table1:** Following is the music scale reference table for channel 1(or channel 2) under Actual Clock=32KHz.

| Note | Ideal freq. | N   | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % | Note | Ideal freq. | N  | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % |

|------|-------------|-----|-------------------------------------|------------|---------|------|-------------|----|-------------------------------------|------------|---------|

| C3   | 130.81      | 122 | 20                                  | 131.15     | 0.26%   | G4   | 392.0       | 41 | 58                                  | 390.24     | -0.44%  |

| D3   | 146.83      | 109 | 51                                  | 146.79     | -0.03%  | A4   | 440.0       | 36 | 1A                                  | 444.44     | 1.01%   |

| E3   | 164.81      | 97  | 45                                  | 164.95     | 0.08%   | B4   | 493.9       | 32 | 25                                  | 500.00     | 1.24%   |

| F3   | 174.61      | 92  | 33                                  | 173.91     | -0.40%  | C5   | 523.2       | 31 | 4B                                  | 516.13     | -1.36%  |

| G3   | 195.99      | 82  | 27                                  | 195.12     | -0.44%  | D5   | 587.3       | 27 | 3B                                  | 592.59     | 0.90%   |

| A3   | 220.00      | 73  | 21                                  | 219.18     | -0.37%  | E5   | 659.2       | 24 | 5C                                  | 666.67     | 1.13%   |

| B3   | 246.94      | 65  | 44                                  | 246.15     | -0.32%  | F5   | 698.4       | 23 | 39                                  | 695.65     | -0.40%  |

| C4   | 261.62      | 61  | 49                                  | 262.30     | 0.26%   | G5   | 784.0       | 20 | 4C                                  | 800.00     | 2.04%   |

| D4   | 293.66      | 54  | 5A                                  | 296.30     | 0.90%   | A5   | 880.0       | 18 | 32                                  | 888.89     | 1.01%   |

| E4   | 329.62      | 49  | 5B                                  | 326.53     | -0.94%  | B5   | 987.7       | 16 | 4A                                  | 1000.00    | 1.24%   |

| F4   | 349.22      | 46  | 5E                                  | 347.83     | -0.40%  | C6   | 1046.5      | 15 | 15                                  | 1066.67    | 1.93%   |

**Music Table2:** Following is the music scale reference table for channel 1(or channel 2) under Actual Clock=16KHz.

| Note | Ideal freq. | N   | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % | Note | Ideal freq. | N  | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % |

|------|-------------|-----|-------------------------------------|------------|---------|------|-------------|----|-------------------------------------|------------|---------|

| C2   | 65.41       | 122 | 20                                  | 65.57      | 0.26%   | G3   | 195.99      | 41 | 58                                  | 195.12     | -0.44%  |

| D2   | 73.41       | 109 | 51                                  | 73.39      | -0.03%  | A3   | 220.00      | 36 | 1A                                  | 222.22     | 1.01%   |

| E2   | 82.41       | 97  | 45                                  | 82.47      | 0.08%   | B3   | 246.94      | 32 | 25                                  | 250.00     | 1.24%   |

| F2   | 87.31       | 92  | 33                                  | 86.96      | -0.40%  | C4   | 261.62      | 31 | 4B                                  | 258.06     | -1.36%  |

| G2   | 98.00       | 82  | 27                                  | 97.56      | -0.44%  | D4   | 293.66      | 27 | 3B                                  | 296.30     | 0.90%   |

| A2   | 110.00      | 73  | 21                                  | 109.59     | -0.37%  | E4   | 329.62      | 24 | 5C                                  | 333.33     | 1.13%   |

| B2   | 123.47      | 65  | 44                                  | 123.08     | -0.32%  | F4   | 349.22      | 23 | 39                                  | 347.83     | -0.40%  |

| C3   | 130.81      | 61  | 49                                  | 131.15     | 0.26%   | G4   | 391.99      | 20 | 4C                                  | 400.00     | 2.04%   |

| D3   | 146.83      | 54  | 5A                                  | 148.15     | 0.90%   | A4   | 439.99      | 18 | 32                                  | 444.44     | 1.01%   |

| E3   | 164.81      | 49  | 5B                                  | 163.27     | -0.94%  | B4   | 493.87      | 16 | 4A                                  | 500.00     | 1.24%   |

| F3   | 174.61      | 46  | 5E                                  | 173.91     | -0.40%  | C5   | 523.24      | 15 | 15                                  | 533.33     | 1.93%   |

**Music Table3:** Following is the music scale reference table for channel 1(or channel 2) under Actual Clock=8KHz.

| Note | Ideal freq. | N   | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % | Note | Ideal freq. | N  | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % |

|------|-------------|-----|-------------------------------------|------------|---------|------|-------------|----|-------------------------------------|------------|---------|

| C1   | 32.70       | 122 | 20                                  | 32.79      | 0.26%   | G2   | 98.00       | 41 | 58                                  | 97.56      | -0.44%  |

| D1   | 36.71       | 109 | 51                                  | 36.70      | -0.03%  | A2   | 110.00      | 36 | 1A                                  | 111.11     | 1.01%   |

| E1   | 41.20       | 97  | 45                                  | 41.24      | 0.08%   | B2   | 123.47      | 32 | 25                                  | 125.00     | 1.24%   |

| F1   | 43.65       | 92  | 33                                  | 43.48      | -0.40%  | C3   | 130.81      | 31 | 4B                                  | 129.03     | -1.36%  |

| G1   | 49.00       | 82  | 27                                  | 48.78      | -0.44%  | D3   | 146.83      | 27 | 3B                                  | 148.15     | 0.90%   |

| A1   | 55.00       | 73  | 21                                  | 54.79      | -0.37%  | E3   | 164.81      | 24 | 5C                                  | 166.67     | 1.13%   |

| B1   | 61.73       | 65  | 44                                  | 61.54      | -0.32%  | F3   | 174.61      | 23 | 39                                  | 173.91     | -0.40%  |

| C2   | 65.41       | 61  | 49                                  | 65.57      | 0.26%   | G3   | 195.99      | 20 | 4C                                  | 200.00     | 2.04%   |

| D2   | 73.41       | 54  | 5A                                  | 74.07      | 0.90%   | A3   | 220.00      | 18 | 32                                  | 222.22     | 1.01%   |

| E2   | 82.41       | 49  | 5B                                  | 81.63      | -0.94%  | B3   | 246.94      | 16 | 4A                                  | 250.00     | 1.24%   |

| F2   | 87.31       | 46  | 5E                                  | 86.96      | -0.40%  | C4   | 261.62      | 15 | 15                                  | 266.67     | 1.93%   |

**Music Table4:** Following is the music scale reference table for channel 1(or channel 2) under Actual Clock=4KHz.

| Note | Ideal freq. | N   | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % | Note | Ideal freq. | N  | LSFR<br>(C1.6~C1.0)<br>(C2.14~C2.8) | Real freq. | Error % |

|------|-------------|-----|-------------------------------------|------------|---------|------|-------------|----|-------------------------------------|------------|---------|

| C0   | 16.35       | 122 | 20                                  | 16.39      | 0.26%   | G1   | 49.00       | 41 | 58                                  | 48.78      | -0.44%  |

| D0   | 18.35       | 109 | 51                                  | 18.35      | -0.03%  | A1   | 55.00       | 36 | 1A                                  | 55.56      | 1.01%   |

| E0   | 20.60       | 97  | 45                                  | 20.62      | 0.08%   | B1   | 61.73       | 32 | 25                                  | 62.50      | 1.24%   |

| F0   | 21.83       | 92  | 33                                  | 21.74      | -0.40%  | C2   | 65.41       | 31 | 4B                                  | 64.52      | -1.36%  |

| G0   | 24.50       | 82  | 27                                  | 24.39      | -0.44%  | D2   | 73.41       | 27 | 3B                                  | 74.07      | 0.90%   |

| A0   | 27.50       | 73  | 21                                  | 27.40      | -0.37%  | E2   | 82.41       | 24 | 5C                                  | 83.33      | 1.13%   |

| B0   | 30.87       | 65  | 44                                  | 30.77      | -0.32%  | F2   | 87.31       | 23 | 39                                  | 86.96      | -0.40%  |

| C1   | 32.70       | 61  | 49                                  | 32.79      | 0.26%   | G2   | 98.00       | 20 | 4C                                  | 100.00     | 2.04%   |

| D1   | 36.71       | 54  | 5A                                  | 37.04      | 0.90%   | A2   | 110.00      | 18 | 32                                  | 111.11     | 1.01%   |

| E1   | 41.20       | 49  | 5B                                  | 40.82      | -0.94%  | B2   | 123.47      | 16 | 4A                                  | 125.00     | 1.24%   |

| F1   | 43.65       | 46  | 5E                                  | 43.48      | -0.40%  | C3   | 130.81      | 15 | 15                                  | 133.33     | 1.93%   |

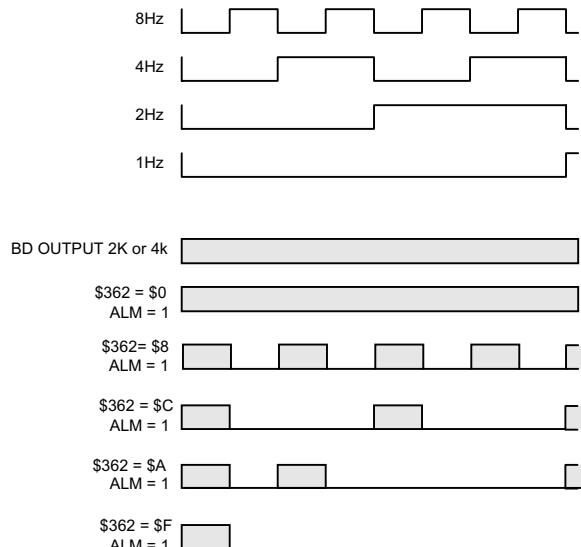

**Alarm generator mode:**

When PSGON=1 and ALM=1, the circuit will provides the alarm carrier frequency (4K or 2K selected by code option) and Channel 2 provides the alarm envelope signal. The channel 2 low nibble C2.0~C2.3 will be the alarm control register.

Alarm control register:

| \$362 | C2.3 | C2.2 | C2.1 | C2.0 | Alarm output control |

|-------|------|------|------|------|----------------------|

|       | 0    | 0    | 0    | 0    | DC envelop           |

|       | X    | X    | X    | 1    | 1Hz output           |

|       | X    | X    | 1    | X    | 2Hz output           |

|       | X    | 1    | X    | X    | 4Hz output           |

|       | 1    | X    | X    | X    | 8Hz output           |

The programming alarm waveform is shown below:

The value N of divider1 is corresponding to the REG C1.6 ~ C1.0 or REG C2.14 ~ C2.8 as shown in the following table:

| LSFR<br>(C1.6 ~ C1.0)<br>(C2.14 ~ C2.8) | N   | LSFR<br>(C1.6 ~ C1.0)<br>(C2.14 ~ C2.8) | N  | LSFR<br>(C1.6 ~ C1.0)<br>(C2.14 ~ C2.8) | N  | LSFR<br>(C1.6 ~ C1.0)<br>(C2.14 ~ C2.8) | N  |

|-----------------------------------------|-----|-----------------------------------------|----|-----------------------------------------|----|-----------------------------------------|----|

| 01                                      | 127 | 16                                      | 95 | 12                                      | 63 | 4B                                      | 31 |

| 02                                      | 126 | 2C                                      | 94 | 24                                      | 62 | 17                                      | 30 |

| 04                                      | 125 | 59                                      | 93 | 49                                      | 61 | 2E                                      | 29 |

| 08                                      | 124 | 33                                      | 92 | 13                                      | 60 | 5D                                      | 28 |

| 10                                      | 123 | 67                                      | 91 | 26                                      | 59 | 3B                                      | 27 |

| 20                                      | 122 | 4E                                      | 90 | 4D                                      | 58 | 77                                      | 26 |

| 41                                      | 121 | 1D                                      | 89 | 1B                                      | 57 | 6E                                      | 25 |

| 03                                      | 120 | 3A                                      | 88 | 36                                      | 56 | 5C                                      | 24 |

| 06                                      | 119 | 75                                      | 87 | 6D                                      | 55 | 39                                      | 23 |

| 0C                                      | 118 | 6A                                      | 86 | 5A                                      | 54 | 73                                      | 22 |

| 18                                      | 117 | 54                                      | 85 | 35                                      | 53 | 66                                      | 21 |

| 30                                      | 116 | 29                                      | 84 | 6B                                      | 52 | 4C                                      | 20 |

| 61                                      | 115 | 53                                      | 83 | 56                                      | 51 | 19                                      | 19 |

| 42                                      | 114 | 27                                      | 82 | 2D                                      | 50 | 32                                      | 18 |

| 05                                      | 113 | 4F                                      | 81 | 5B                                      | 49 | 65                                      | 17 |

| 0A                                      | 112 | 1F                                      | 80 | 37                                      | 48 | 4A                                      | 16 |

| 14                                      | 111 | 3E                                      | 79 | 6F                                      | 47 | 15                                      | 15 |

| 28                                      | 110 | 7D                                      | 78 | 5E                                      | 46 | 2A                                      | 14 |

| 51                                      | 109 | 7A                                      | 77 | 3D                                      | 45 | 55                                      | 13 |

| 23                                      | 108 | 74                                      | 76 | 7B                                      | 44 | 2B                                      | 12 |

| 47                                      | 107 | 68                                      | 75 | 76                                      | 43 | 57                                      | 11 |

| 0F                                      | 106 | 50                                      | 74 | 6C                                      | 42 | 2F                                      | 10 |

| 1E                                      | 105 | 21                                      | 73 | 58                                      | 41 | 5F                                      | 9  |

| 3C                                      | 104 | 43                                      | 72 | 31                                      | 40 | 3F                                      | 8  |

| 19                                      | 103 | 07                                      | 71 | 63                                      | 39 | 7F                                      | 7  |

| 72                                      | 102 | 0E                                      | 70 | 46                                      | 38 | 7E                                      | 6  |

| 64                                      | 101 | 1C                                      | 69 | 0D                                      | 37 | 7C                                      | 5  |

| 48                                      | 100 | 38                                      | 68 | 1A                                      | 36 | 78                                      | 4  |

| 11                                      | 99  | 71                                      | 67 | 34                                      | 35 | 70                                      | 3  |

| 22                                      | 98  | 62                                      | 66 | 69                                      | 34 | 60                                      | 2  |

| 45                                      | 97  | 44                                      | 65 | 52                                      | 33 | 40                                      | 1  |

| 0B                                      | 96  | 09                                      | 64 | 25                                      | 32 |                                         |    |

## 9. Timer 0

SH67L19 has one 8-bit timer. The timer consists of an 8-bit up counter and an 8-bit preload register.

The timers provide the following functions:

- Programmable internal timer function

- Read the counter values

### 9.1. Timer 0 configuration and operation

The timer 0 consists of an 8-bit write-only timer load register (TL0L, TL0H) and an 8-bit read-only timer counter (TC0L, TC0H). Each has low order digits and high order digits. Writing data into the timer load register (TL0L, TL0H) can initialize the timer counter. Write the low-order digit first and then the high-order digit. The timer counter is loaded with the content of the load register automatically when the high order digit is written or counts overflow happens. The timer overflow will generate an interrupt, if the interrupt enable flag is set.

The timer can be programmed in several different system clock sources by setting the Timer Mode register (TM0).

Timer 0 reads and writes operations follow these rules:

| Write Operation                   | Read Operation     |

|-----------------------------------|--------------------|

| Low nibble first                  | High nibble first  |

| High nibble to update the counter | Low nibble follows |

### 9.2. Timer0 mode register (TM0)

The 8-bit counter counts pre-scaler overflow output pulses. TM0 are 4-bit registers used for timer control as shown in Table 1.2. When the OSC used as system clock, the timer0's clock source can't be selected by TM0.3, the timer0's clock source is system clock (OSC/4). See in Table1.

**Table 1. Timer0 Mode registers (\$02)**

| TM0.3 | TM0.2 | TM0.1 | TM0.0 | Prescaler | Clock Source |

|-------|-------|-------|-------|-----------|--------------|

| 0     | 0     | 0     | 0     | /2048     | System clock |

| 0     | 0     | 0     | 1     | /512      | System clock |

| 0     | 0     | 1     | 0     | /128      | System clock |

| 0     | 0     | 1     | 1     | /32       | System clock |

| 0     | 1     | 0     | 0     | /8        | System clock |

| 0     | 1     | 0     | 1     | /4        | System clock |

| 0     | 1     | 1     | 0     | /2        | System clock |

| 0     | 1     | 1     | 1     | /1        | System clock |

When the OSCX used as system clock, the TM0.3 can be select timer0's clock source. See in Table 2

TM0.3 =0: timer0 clock source is system clock (OSCX/4)

TM0.3 =1: timer0 clock source is generated by OSC, clock source is32k (32k crystal, 32k RC or RC 131k/4).

**Table 2. Timer0 Mode registers (\$02)**

| TM0.3 | TM0.2 | TM0.1 | TM0.0 | Prescaler | Clock Source |

|-------|-------|-------|-------|-----------|--------------|

| 0     | 0     | 0     | 0     | /2048     | System clock |

| 0     | 0     | 0     | 1     | /512      | System clock |

| 0     | 0     | 1     | 0     | /128      | System clock |

| 0     | 0     | 1     | 1     | /32       | System clock |

| 0     | 1     | 0     | 0     | /8        | System clock |

| 0     | 1     | 0     | 1     | /4        | System clock |

| 0     | 1     | 1     | 0     | /2        | System clock |

| 0     | 1     | 1     | 1     | /1        | System clock |

| 1     | 0     | 0     | 0     | /2048     | 32K          |

| 1     | 0     | 0     | 1     | /512      | 32K          |

| 1     | 0     | 1     | 0     | /128      | 32K          |

| 1     | 0     | 1     | 1     | /32       | 32K          |

| 1     | 1     | 0     | 0     | /8        | 32K          |

| 1     | 1     | 0     | 1     | /4        | 32K          |

| 1     | 1     | 1     | 0     | /2        | 32K          |

| 1     | 1     | 1     | 1     | /1        | 32K          |

### 9.3. Warm-up counter

In 32K RC mode, the warm-up counter prescaler is divided by  $2^{10}$  (1024).

In 131K RC mode, the warm-up counter prescaler is divided by  $2^{12}$  (4096).

In CRYSTAL mode, the warm-up counter prescaler is divided by  $2^{13}$  (8192).

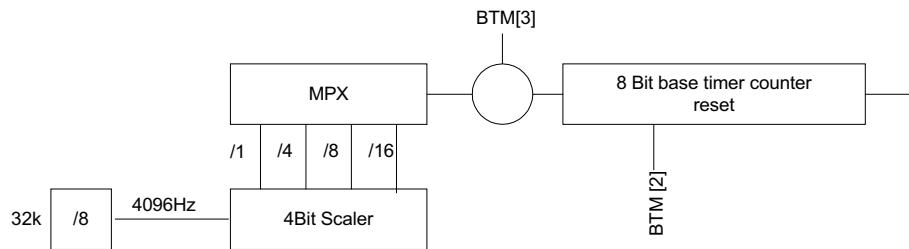

## 10. Base Timer

The MCU has a base timer. The base timer clock source is 32k (32k crystal, 32k RC or RC 131k/4). After MCU is reset, it counts at every clock-input signal. When it counts to \$FF, right after next clock input, counter counts to \$00 and generates an overflow. This causes the interrupt of base timer interrupt request flag to 1. Therefore, the base timer can function as an interval timer periodically, generating overflow output as every 256th clock signal output.

The timer accepts 4kHz clock, and base timer generates an accurate timing interrupt.

This clock-input source is selected by BTM register.

|      | Bit3  | Bit2  | Bit1  | Bit0  | Remark                   |

|------|-------|-------|-------|-------|--------------------------|

| \$03 | BTM.3 | BTM.2 | BTM.1 | BTM.0 | Base timer mode register |

BTM.3 = 0: Disable the base timer

BTM.3 = 1: Enable the base timer

BTM.2 = 0: Non reset the base timer

BTM.2 = 1: reset the base timer

| BTM.1 | BTM.0 | Prescaler Ratio | Clock source |

|-------|-------|-----------------|--------------|

| 0     | 0     | /1              | 4096Hz       |

| 0     | 1     | /4              | 4096Hz       |

| 1     | 0     | /8              | 4096Hz       |

|       | 1     | /16             | 4096Hz       |

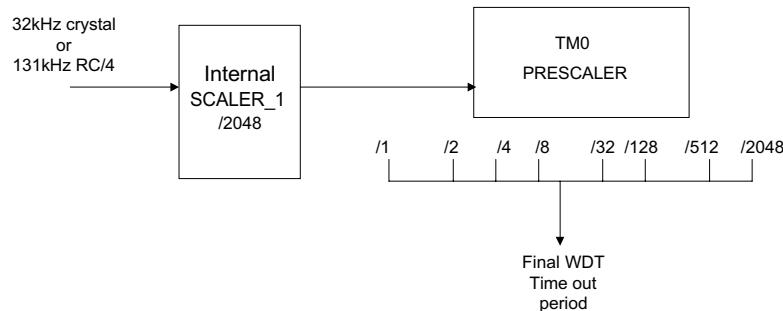

## 11. Watch Dog Timer

SH67L19 has a Watch-Dog-Timer. The input clock of the watchdog timer is fetched from the low frequency oscillator (OSC). So the WDT will not run in the STOP mode. SH67L19 will generate a RESET condition when the Watchdog times-out. The Watchdog can be enabled or disabled permanently by the system register (\$17)'s bit2~0. To prevent it timing out and generating a device RESET condition, user should write bit3 of system register \$17 as "1" before timing-out. If a longer timeout periods is desired, a prescaler with a division ratio of up to 1:2048 can be assigned to the WDT under software controlled by writing to the TM0 register (\$02).

### System Register \$1D

|      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Remark                                                                                           | Power On |

|------|-------|-------|-------|-------|--------------------------------------------------------------------------------------------------|----------|

| \$17 | WDT   | WT2   | WT1   | WT0   | Bit3: Watchdog timer reset/flag. (write 1 to reset WDT)<br>Bit2~0: Watchdog timer on/off control | 1010     |

WT2~WT0 = 010 (defualt), 000, 001, 011, 100 110, 111: watchdog timer is enabled.

WT2~WT0 = 101: watchdog timer is disable.

Prescaler divide ratio:

| TM0.2 | TM0.1 | TM0.0 | Prescaler divide ratio    | Time out period |

|-------|-------|-------|---------------------------|-----------------|

| 1     | 1     | 1     | 1:1                       | 64ms            |

| 1     | 1     | 0     | 1:2                       | 128ms           |

| 1     | 0     | 1     | 1:4                       | 256ms           |

| 1     | 0     | 0     | 1:8                       | 512ms           |

| 0     | 1     | 1     | 1:32                      | 2048ms          |

| 0     | 1     | 0     | 1:128                     | 8192ms          |

| 0     | 0     | 1     | 1:512                     | 32768ms         |

| 0     | 0     | 0     | 1:2048 (Power on initial) | 131072ms        |

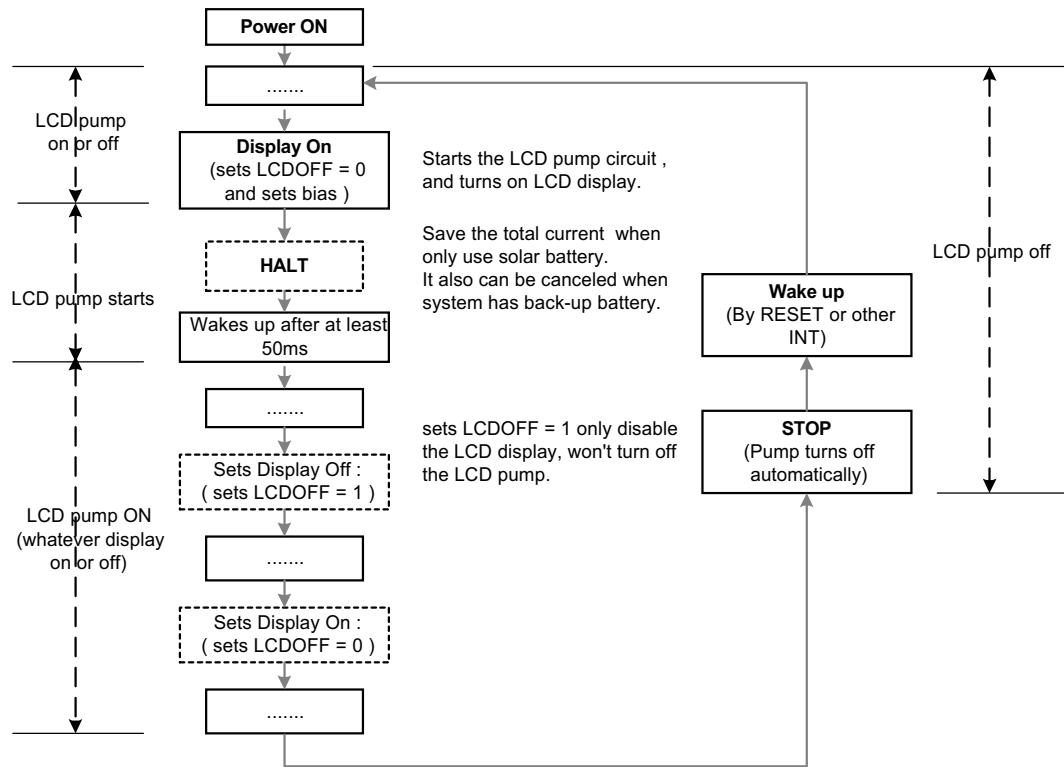

## 12. LCD Driver

The LCD driver contains a controller, a voltage generator, 6 common signal pins and up to 38 segment driver pins. There are three different driving modes: 1/6 duty and 1/3 bias, 1/5 duty and 1/3 bias, 1/4 duty and 1/3 bias, 1/3 duty and 1/2 bias. The driving mode is controlled by code option. Also port C ~ F can be used as LCD segment (selected by system register).

When the "STOP" instruction is executed, the LCD will be turned off, but the data of LCD RAM is the same before execution the "STOP" instruction. When LCD off, both COMMON and SEGMENT output high or low. The OSC will always be source clock for LCD frame frequency, no matter the CPU system clock is OSC or OSCX.

### 12.1. LCD Control Register

|      | Bit3 | Bit2 | Bit1   | Bit0  | Remarks                                                                                                                                          | Power On |

|------|------|------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| \$06 | ENX  | ELON | LCDOFF | PSGON | ...<br>Bit1: LCD on/off control<br>...                                                                                                           | 0010     |

| \$13 | ELF  | ELPF | SOH/L  | S/CX  | Bit0: Select CX or LCD segment38<br>Bit1: Select LCD segment output high or low<br>...                                                           | 0001     |

| \$16 | O/S4 | O/S3 | O/S2   | O/S1  | Bit0: Select PORTC or LCD segment<br>Bit1: Select PORTD or LCD segment<br>Bit2: Select PORTE or LCD segment<br>Bit3: Select PORTF or LCD segment | 1111     |

LCDOFF: 0: LCD on and pump on 1:LCD off

SOH/L: 0: When LCD off, COM and SEG output low

1: When LCD off, COM and SEG output high

S/CX: 0: CX 1: SEG38

O/S4: 0: Port F as I/O 1: Port F as segment 22~25

O/S3: 0: Port E as I/O 1: Port E as segment 26~29

O/S2: 0: Port D as I/O 1: Port D as segment 30~33

O/S1: 0: Port C as I/O 1: Port C as segment 34~37

#### Notice:

1. The LCDOFF (system register 06H bit1) will set to 1 when reset, and the LCD display will be disabled.

2. The LCD pump circuit may be on or off after power on reset. When LCDOFF (system register 06H bit1) is cleared to 0, the LCD pump circuit will turn on. It will turn off only after receiving a "STOP" instruction.

3. Set LCDOFF = 1 disables LCD display output only, and won't turn off the LCD pump circuit.

4. When SH67L19 runs into STOP mode, the LCD pump circuit turns off automatically. The user should turn on the LCD pump (set LCDOFF = 0) after the next wake up.

Example:

## 12.2. Configuration of LCD RAM

LCD 1/6 duty, 1/3 bias (COM1 - 6, SEG1 - 38)

| Address | Bit3  | Bit2  | Bit1  | Bit0  | Address | Bit3 | Bit2 | Bit1  | Bit0  |

|---------|-------|-------|-------|-------|---------|------|------|-------|-------|

|         | COM4  | COM3  | COM2  | COM1  |         | -    | -    | COM6- | COM5  |

| 300H    | SEG1  | SEG1  | SEG1  | SEG1  | 330H    | -    | -    | SEG1  | SEG1  |

| 301H    | SEG2  | SEG2  | SEG2  | SEG2  | 331H    | -    | -    | SEG2  | SEG2  |

| 302H    | SEG3  | SEG3  | SEG3  | SEG3  | 332H    | -    | -    | SEG3  | SEG3  |

| 303H    | SEG4  | SEG4  | SEG4  | SEG4  | 333H    | -    | -    | SEG4  | SEG4  |

| 304H    | SEG5  | SEG5  | SEG5  | SEG5  | 334H    | -    | -    | SEG5  | SEG5  |

| 305H    | SEG6  | SEG6  | SEG6  | SEG6  | 335H    | -    | -    | SEG6  | SEG6  |

| 306H    | SEG7  | SEG7  | SEG7  | SEG7  | 336H    | -    | -    | SEG7  | SEG7  |

| 307H    | SEG8  | SEG8  | SEG8  | SEG8  | 337H    | -    | -    | SEG8  | SEG8  |

| 308H    | SEG9  | SEG9  | SEG9  | SEG9  | 338H    | -    | -    | SEG9  | SEG9  |

| 309H    | SEG10 | SEG10 | SEG10 | SEG10 | 339H    | -    | -    | SEG10 | SEG10 |

| 30AH    | SEG11 | SEG11 | SEG11 | SEG11 | 33AH    | -    | -    | SEG11 | SEG11 |

| 30BH    | SEG12 | SEG12 | SEG12 | SEG12 | 33BH    | -    | -    | SEG12 | SEG12 |

| 30CH    | SEG13 | SEG13 | SEG13 | SEG13 | 33CH    | -    | -    | SEG13 | SEG13 |

| 30DH    | SEG14 | SEG14 | SEG14 | SEG14 | 33DH    | -    | -    | SEG14 | SEG14 |

| 30EH    | SEG15 | SEG15 | SEG15 | SEG15 | 33EH    | -    | -    | SEG15 | SEG15 |

| 30FH    | SEG16 | SEG16 | SEG16 | SEG16 | 33FH    | -    | -    | SEG16 | SEG16 |

| 310H    | SEG17 | SEG17 | SEG17 | SEG17 | 340H    | -    | -    | SEG17 | SEG17 |

| 311H    | SEG18 | SEG18 | SEG18 | SEG18 | 341H    | -    | -    | SEG18 | SEG18 |

| Address | Bit3  | Bit2  | Bit1  | Bit0  | Address | Bit3 | Bit2 | Bit1  | Bit0  |

|---------|-------|-------|-------|-------|---------|------|------|-------|-------|

|         | COM4  | COM3  | COM2  | COM1  |         | -    | -    | COM6- | COM5  |

| 312H    | SEG19 | SEG19 | SEG19 | SEG19 | 342H    | -    | -    | SEG19 | SEG19 |

| 313H    | SEG20 | SEG20 | SEG20 | SEG20 | 343H    | -    | -    | SEG20 | SEG20 |

| 314H    | SEG21 | SEG21 | SEG21 | SEG21 | 344H    | -    | -    | SEG21 | SEG21 |

| 315H    | SEG22 | SEG22 | SEG22 | SEG22 | 345H    | -    | -    | SEG22 | SEG22 |

| 316H    | SEG23 | SEG23 | SEG23 | SEG23 | 346H    | -    | -    | SEG23 | SEG23 |

| 317H    | SEG24 | SEG24 | SEG24 | SEG24 | 347H    | -    | -    | SEG24 | SEG24 |

| 318H    | SEG25 | SEG25 | SEG25 | SEG25 | 348H    | -    | -    | SEG25 | SEG25 |

| 319H    | SEG26 | SEG26 | SEG26 | SEG26 | 349H    | -    | -    | SEG26 | SEG26 |

| 31AH    | SEG27 | SEG27 | SEG27 | SEG27 | 34AH    | -    | -    | SEG27 | SEG27 |

| 31BH    | SEG28 | SEG28 | SEG28 | SEG28 | 34BH    | -    | -    | SEG28 | SEG28 |

| 31CH    | SEG29 | SEG29 | SEG29 | SEG29 | 34CH    | -    | -    | SEG29 | SEG29 |

| 31DH    | SEG30 | SEG30 | SEG30 | SEG30 | 34DH    | -    | -    | SEG30 | SEG30 |

| 31EH    | SEG31 | SEG31 | SEG31 | SEG31 | 34EH    | -    | -    | SEG31 | SEG31 |

| 31FH    | SEG32 | SEG32 | SEG32 | SEG32 | 34FH    | -    | -    | SEG32 | SEG32 |

| 320H    | SEG33 | SEG33 | SEG33 | SEG33 | 350H    | -    | -    | SEG33 | SEG33 |

| 321H    | SEG34 | SEG34 | SEG34 | SEG34 | 351H    | -    | -    | SEG34 | SEG34 |

| 322H    | SEG35 | SEG35 | SEG35 | SEG35 | 352H    | -    | -    | SEG35 | SEG35 |

| 323H    | SEG36 | SEG36 | SEG36 | SEG36 | 353H    | -    | -    | SEG36 | SEG36 |

| 324H    | SEG37 | SEG37 | SEG37 | SEG37 | 354H    | -    | -    | SEG37 | SEG37 |

| 325H    | SEG38 | SEG38 | SEG38 | SEG38 | 355H    | -    | -    | SEG38 | SEG38 |

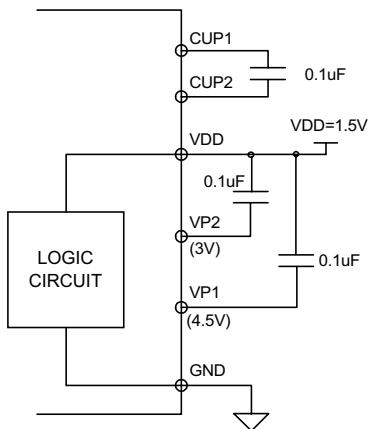

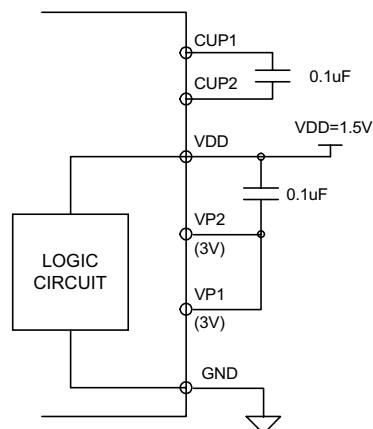

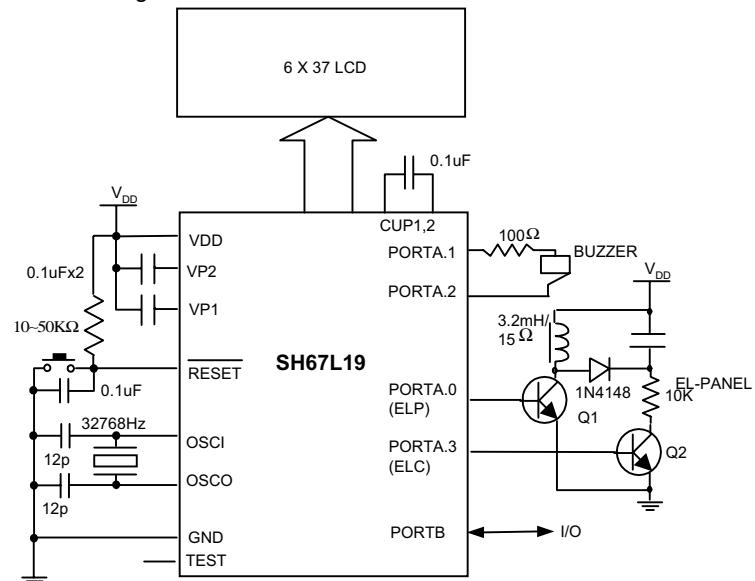

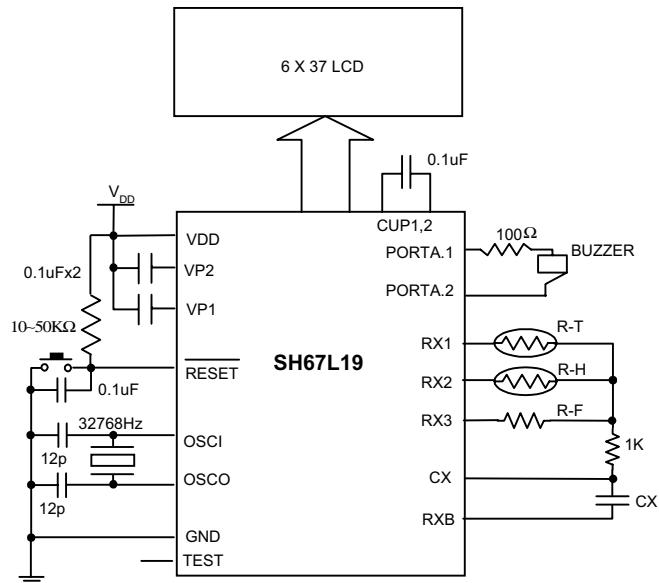

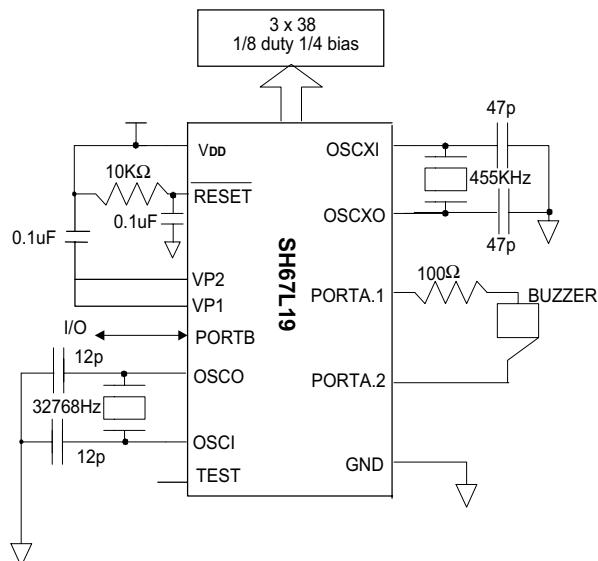

### 12.3. Connection diagram

The pump circuit frequency could be 2K and 4K (selected by code option).

1. VDD=1.5V, 4.5V LCD, 1/6 duty, 1/3bias

and 1/5 duty, 1/3 bias

and 1/4 duty, 1/3 bias

2. VDD=1.5V, 3V LCD, 1/3 duty, 1/2bias

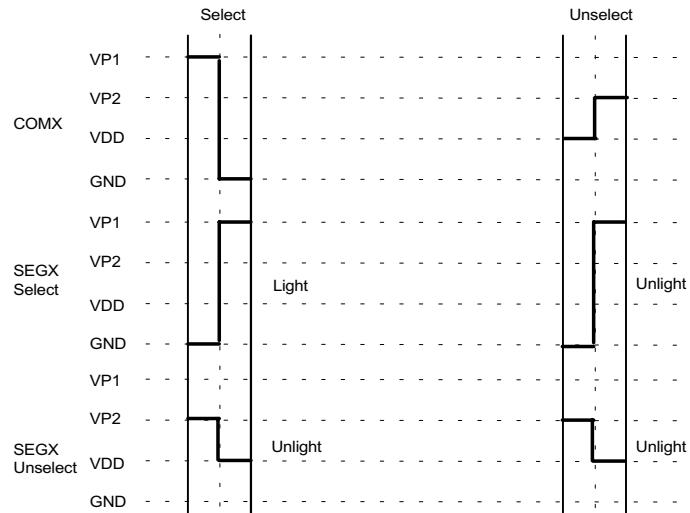

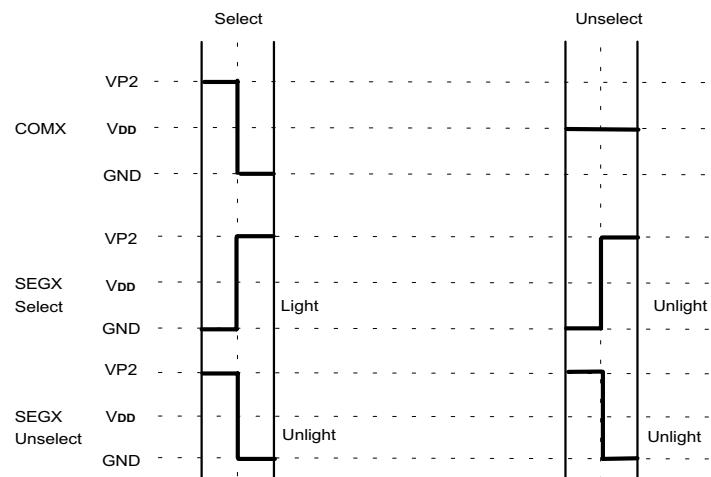

#### 12.4. LCD waveform

1/6, 1/5, 1/4 duty, 1/3 bias LCD waveform (VDD=1.5V, VP1=4.5V, VP2=3V)

1/3 duty, 1/2 bias LCD waveform (VDD=1.5V, VP1=VP2=3V)

### 13. Interrupt

4 interrupt sources are available on SH67L19:

- External interrupt (/INT0 shared with PA0)

- Timer0 interrupt (TM0INT)

- Base Timer interrupt (BTINT)

- Port B&Cs falling or rising edge detection interrupt (/INT1)

The configuration of interrupt's system register:

| Address | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function                   |

|---------|-------|-------|-------|-------|----------------------------|

| \$00    | IEX   | IET0  | IEBT  | IEP   | 1: Enable / 0: Disable     |

| \$01    | IRQX  | IRQT0 | IRQBT | IRQP  | 1: Request / 0: No request |

#### 13.1. External Interrupt (/INT0)

External interrupt is shared with the PA.0 (falling or rising edge active). When the bit 3 of the register \$0 (IEX) is set to 1, the external interrupt is enabled, only PA0 at input mode will generate external interrupt.

#### 13.2. Timer 0 interrupt (T0INT), Base timer interrupt (BTINT), Port interrupt (/INT1)

If IET0 = 1, the overflow of timer 0 will create the interrupt of timer 0. If IEBT = 1, the overflow of the Base timer will create the interrupt of the Base timer. If IEP = 1, the falling or rising edge of every port in PORTB&C will create /INT1 interrupt (The condition is PORTB, C at input mode).

#### 13.3. The Enable flags and Request flags

Both the Enable flags and Request flags can be read or written by the software.

But the Request flags will be set "1" by the hardware interrupt and the Enable flags will be reset by the hardware when the interrupt service routine is entered.

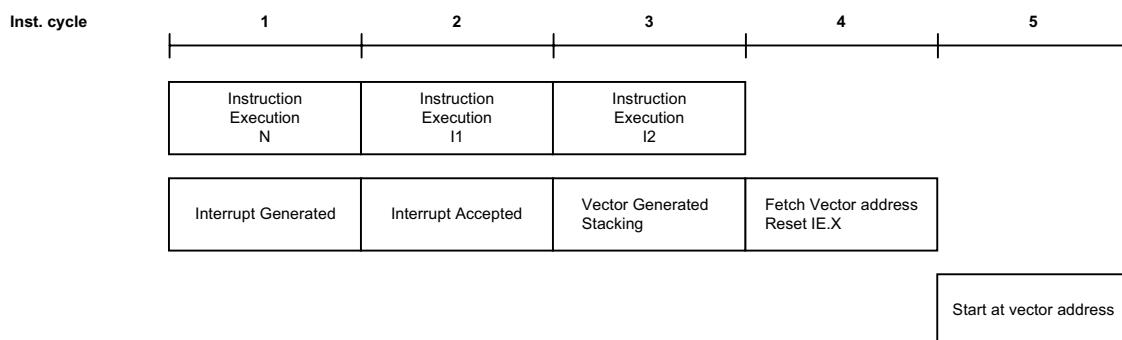

#### 13.4. Interrupt Servicing Sequence Diagram:

In SH6610C CPU interrupt services routine, the user can enable any interrupt enable flag before returning from an interrupt. The frequently asked question is when the next interrupt would be serviced? Will the nesting interrupt happen? From the servicing sequence timing diagram, if interrupt request is ready and instruction execution N is IE enable. Then the interrupt can start right after the next two instructions: I1 or instruction I2 disable the interrupt request or enable flag, then interrupt service sequence would be terminated.

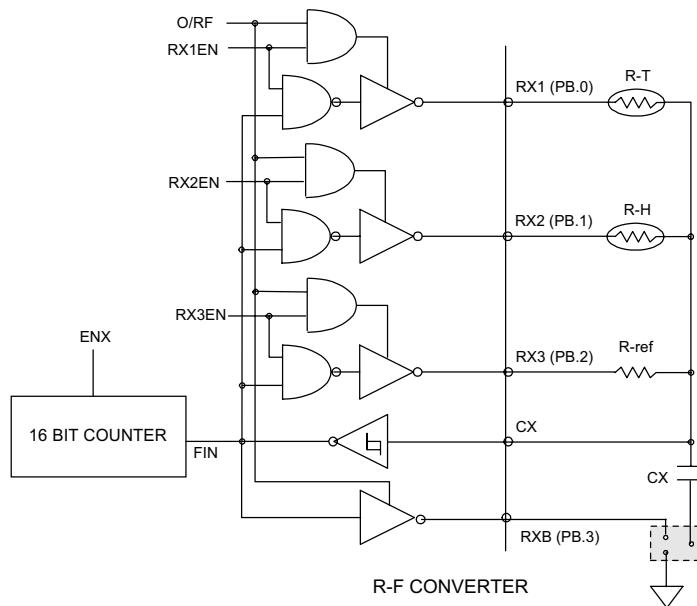

#### 14. Resistor to Frequency Converter

|       | Bit 3 | Bit 2 | Bit 1  | Bit 0 | R/W | Remarks                                                                                                      | Power On |

|-------|-------|-------|--------|-------|-----|--------------------------------------------------------------------------------------------------------------|----------|

| \$06  | ENX   | ELON  | LCDOFF | PSGON | R/W | ...<br>Bit3: R-F convert counter on.                                                                         | 0010     |

| \$07  | O/RF  | RX3EN | RX2EN  | RX1EN | R/W | Bit0: count resistor1.<br>Bit1: count resistor2.<br>Bit2: count resistor3.<br>Bit3: set PB as R-F converter. | 0000     |

| \$269 | RF1.3 | RF1.2 | RF1.1  | RF1.0 | R/W | R-F counter register nibble 1 (bit0~3)                                                                       | 0000     |

| \$26A | RF2.3 | RF2.2 | RF2.1  | RF2.0 | R/W | R-F counter register nibble 2 (bit4~7)                                                                       | 0000     |

| \$26B | RF3.3 | RF3.2 | RF3.1  | RF3.0 | R/W | R-F counter register nibble 3 (bit8~11)                                                                      | 0000     |

| \$26C | RF4.3 | RF4.2 | RF4.1  | RF4.0 | R/W | R-F counter register nibble 4 (bit12~15)                                                                     | 0000     |

| \$26D | RF5.3 | RF5.2 | RF5.1  | RF5.0 | R/W | R-F counter register nibble 5 (bit16~19)                                                                     | 0000     |

When we set O/RF=1, Port B is used as R-F converter. It's like a RC oscillation circuit, and use the 20-bit counter to get the resistive value of the sensor. First set RX1EN=1(enable RX1-F convert), then start timer1 or timer0 counter and set ENX=1(start R-F counter). When timer INT happened, we can get the value of the RX1-F counter. So, we can get different count value of R-T, R-H, R-ref by set RX1EN, RX2EN, RX3EN=1 in turn.

R-F converter could keep on working in HALT mode, and would stop automatic when execute "STOP" instruction. (Keep the last state of RX1-3 ports and stop the R-F counter.)

SH67L19 provides two methods of R-F's application to improve the R-F application's performance (selected by code option). When designing the R-F's peripheral circuit, it can select the capacitor connect with CX and PB3 or CX and GND. Note: the method of the capacitor connection must match the corresponding code option.

Temperature sensor resistor: 10K ~ 50K @25°C (for reference only)

Humidity sensor: 60K @25°C, 50%RH (for reference only)

- Notice:

1. When O/RF set to 1, PORTB interrupt will be disabled.

2. Connect CX to VDD or GND when R-F converter not used.

3. The 20 bit counter can use as an event counter when not using R-F converter.

4. Max-frequency of R-F converter should less than 2MHz.

## 15. EL-LIGHT

|      | Bit 3 | Bit 2 | Bit 1  | Bit 0 | R/W | Remarks                                                                                                       | Power On |

|------|-------|-------|--------|-------|-----|---------------------------------------------------------------------------------------------------------------|----------|

| \$06 | ENX   | ELON  | LCDOFF | PSGON | R/W | ...<br>Bit2: EL-light on/off, set PA3 as ELC and<br>PA0 as ELP<br>...                                         | 0010     |

| \$13 | ELF   | ELPF  | HLM    | S/CX  | R/W | EL-LIGHT mode control<br>Bit2: ELP driver output frequency control.<br>Bit3: EL-LIGHT driver frequency select | 0000     |

ELPF: (frequency of ELP pin charge waveform)