***THIS DOCUMENT IS FOR MAINTENANCE

PURPOSES ONLY AND IS NOT

RECOMMENDED FOR NEW DESIGNS***

# SL6442

## 1GHZ AMPLIFIER/MIXER

(Supersedes May 1992 Edition)

The SL6442 UHF Amplifier and Mixer is designed for use in cordless telephones, cellular telephones, pagers and low-power receivers operating at frequencies up to 1GHz. It contains a low noise amplifier (LNA) with AGC facility and two mixers for use in I and Q direct conversion receivers or image cancelling in superheterodyne receivers.

Operating from a single supply of 5V, the SL6442 requires a current of 4.6mA (typ.) when powered up and only 11 $\mu$ A (typ.) when powered down using the battery economy facility.

### FEATURES

- 1GHz Operation

- Very Low Power

- Suitable for Direct Conversion or Superhet Systems

- On-Chip RF Amplifier

- Power Down Facility for Battery Economy

- AGC Capability

### ORDERING INFORMATION

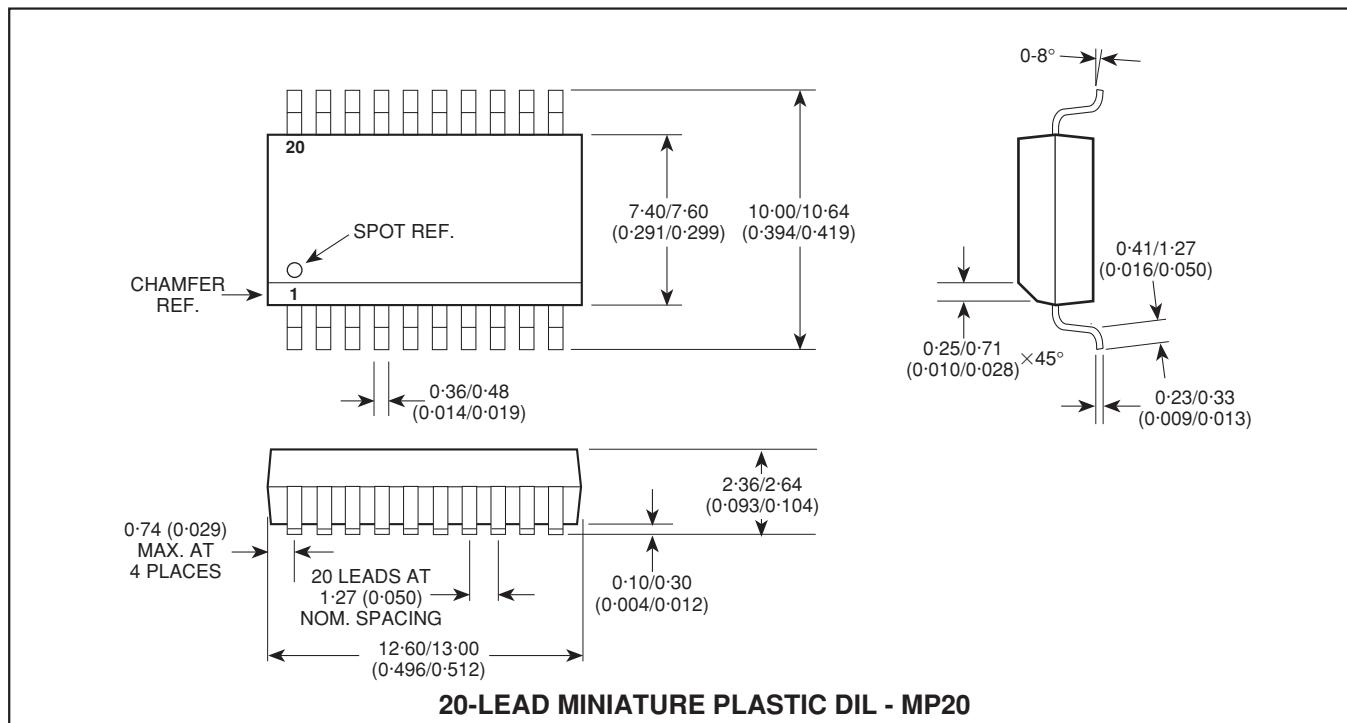

SL6442 NA MP Miniature Plastic DIL Package

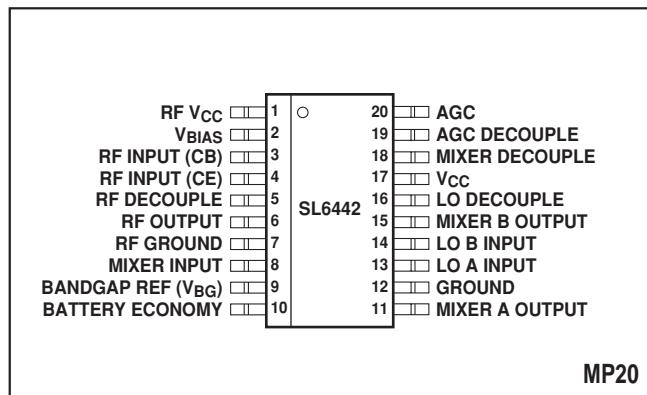

MP20

Fig.1 Pin connections - top view

### ABSOLUTE MAXIMUM RATINGS

|                       |                 |

|-----------------------|-----------------|

| Supply voltage        | 8V              |

| Storage temperature   | -55°C to +150°C |

| Operating temperature | 0°C to +70°C    |

This device has static-sensitive terminations, sensitivity measured as typically 400V using MIL-STD-883 Method 3015. Therefore, ESD handling precautions are essential in order to avoid degradation of performance or permanent damage to the device.

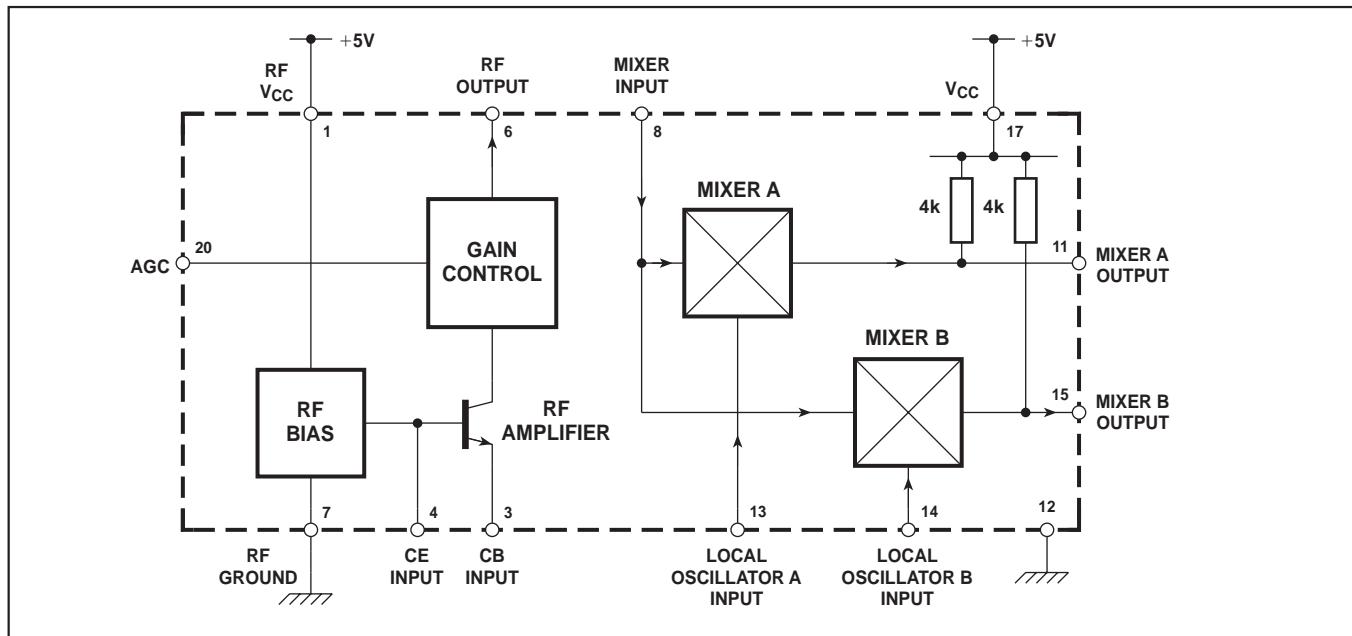

Fig.2 block diagram

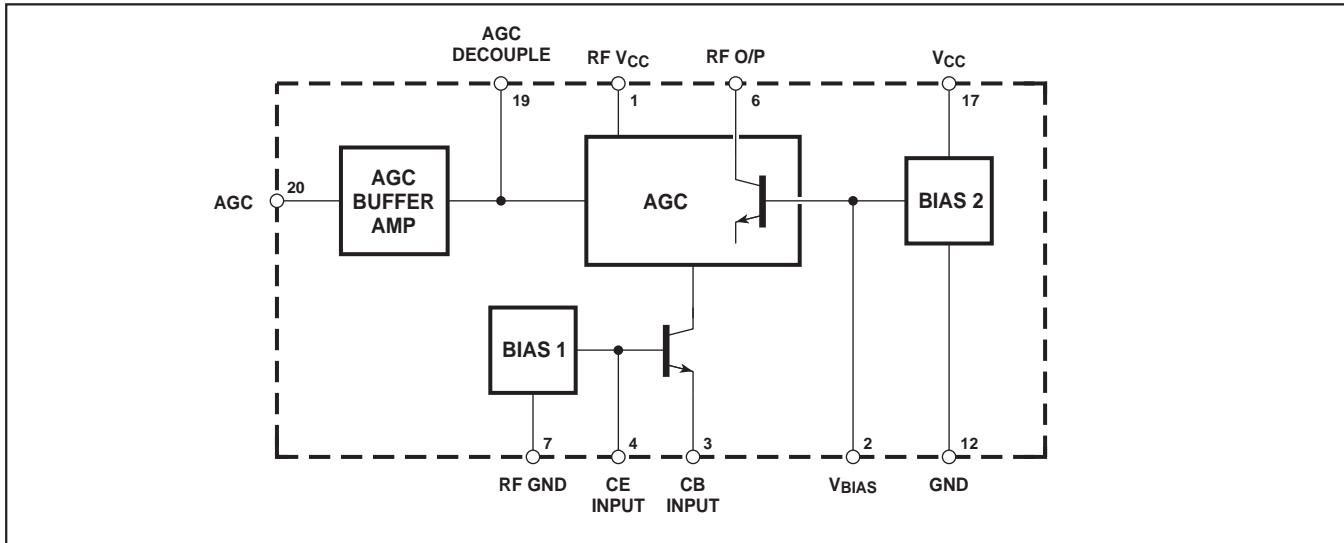

Fig.3 Circuit schematic of LNA

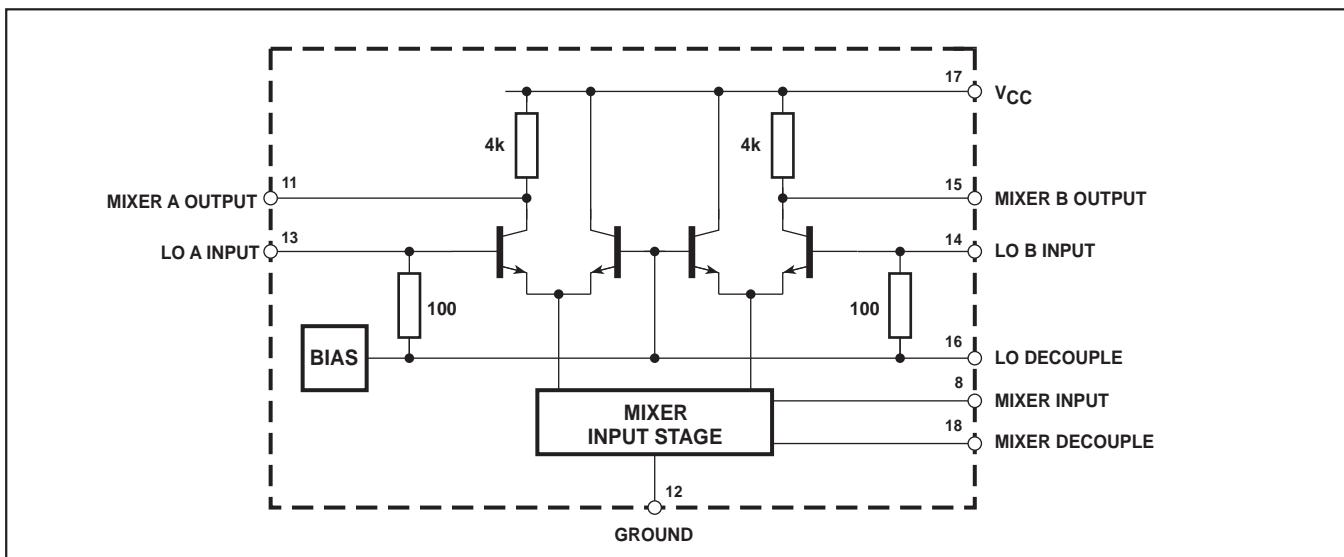

Fig.4 Circuit schematic of mixer

## PIN DESCRIPTIONS

| Pin no. | Name               | Description                                                                                                                                                                                                                  |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RF V <sub>CC</sub> | Power supply to the RF amplifier. Normally connected to +5V, it should be adequately bypassed.                                                                                                                               |

| 2       | V <sub>BIAS</sub>  | A 1.6V bias source capable of supplying up to 0.5mA.                                                                                                                                                                         |

| 3       | RF input (CB)      | Common base input to the emitter of the RF transistor. It should be returned to ground for DC using an RF choke or tuned circuit when in common base mode. In common emitter mode it should be connected directly to ground. |

| 4       | RF input (CE)      | Common emitter input to the base of the RF transistor. It is DC biased internally but should be decoupled in common base mode.                                                                                               |

| 5       | RF decouple        | Decoupling of DC bias line.                                                                                                                                                                                                  |

| 6       | RF output          | Output port of the RF amplifier. It should be returned to +5V via an RF load. A current of 2mA will flow if pin 20 (AGC) is connected to pin 9 (V <sub>BG</sub> ).                                                           |

## PIN DESCRIPTIONS (Continued)

| Pin no. | Name                      | Description                                                                                                                                                                                                                                                            |

|---------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | RF ground                 | A separate ground is provided for the RF amplifier to improve stability.                                                                                                                                                                                               |

| 8       | Mixer input               | This is coupled externally to the output of the RF amplifier (pin 6). It should be decoupled to $V_{BIAS}$ via an RF choke.                                                                                                                                            |

| 9       | Bandgap ref. ( $V_{BG}$ ) | Temperature compensated DC reference voltage. It should not be loaded.                                                                                                                                                                                                 |

| 10      | Battery economy           | Turns device 'off' when HIGH (>3V), 'on' when LOW (<1.5V).                                                                                                                                                                                                             |

| 11      | Mixer A output            | The output impedance is about 4k $\Omega$ ; quiescent voltage is approximately 4V ( $V_{CC}=5V$ ).                                                                                                                                                                     |

| 12      | Ground                    | Mixer and biasing ground.                                                                                                                                                                                                                                              |

| 13      | Local osc. A input        | Input level of -10dBm. DC level is approximately 2.3V.                                                                                                                                                                                                                 |

| 14      | Local osc. B input        | Input level of -10dBm. DC level is approximately 2.3V.                                                                                                                                                                                                                 |

| 15      | Mixer B output            | The output impedance is about 4k $\Omega$ ; quiescent voltage is approximately 4V ( $V_{CC}=5V$ ).                                                                                                                                                                     |

| 16      | LO decouple               | Decoupling of DC bias line.                                                                                                                                                                                                                                            |

| 17      | $V_{CC}$                  | +5V supply; it should be bypassed effectively.                                                                                                                                                                                                                         |

| 18      | Mixer decouple            | Decoupling of DC bias line.                                                                                                                                                                                                                                            |

| 19      | AGC decouple              | Decoupling of AGC input line.                                                                                                                                                                                                                                          |

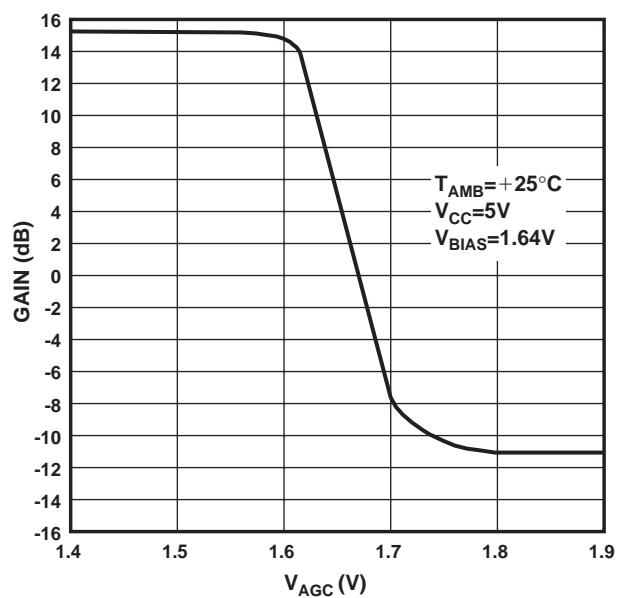

| 20      | AGC                       | Varies RF amplifier gain. Gain reduces with increasing voltage, with RF gain reduced by 6dB when $AGC=V_{BIAS}$ . Full range of AGC requires only typically 300mV DC range (see Fig. 9). This pin should be connected to $V_{BG}$ if the AGC facility is not required. |

## ELECTRICAL CHARACTERISTICS

These characteristics are guaranteed over the following conditions unless otherwise stated:

$T_{AMB}=25^{\circ}C$ ,  $V_{CC}=4.5V$  and at  $V_{CC}=6.5V$

| Characteristic                    | Pin              | Value |       |       | Units   | Conditions                                                                                                     |

|-----------------------------------|------------------|-------|-------|-------|---------|----------------------------------------------------------------------------------------------------------------|

|                                   |                  | Min.  | Typ.  | Max.  |         |                                                                                                                |

| Total supply current              | 1, 6, 11, 15, 17 | 3.5   | 4.6   | 5.5   | mA      | Pin 10 at 0V                                                                                                   |

| Total supply current (economised) | 1, 6, 11, 15, 17 |       | 11.0  | 15.0  | $\mu$ A | Pin 10 at $V_{CC}$                                                                                             |

| Battery economiser input current  | 10               | -1.0  | +1.0  |       | $\mu$ A |                                                                                                                |

| Total RF amplifier current        | 1, 5             |       | 2.0   | 2.75  | mA      |                                                                                                                |

| Maximum RF amplifier current      | 6                |       | 2.0   | 2.75  | mA      |                                                                                                                |

| Minimum RF amplifier current      | 6                |       |       | 10.0  | $\mu$ A |                                                                                                                |

| AGC amplifier offset voltage      | 20, 19           | -20.0 | 0     | +20.0 | mV      |                                                                                                                |

| Bandgap voltage, $V_{BG}$         | 9                | 1.00  | 1.23  | 1.40  | V       |                                                                                                                |

| $V_{BIAS}$                        | 2                | 1.40  | 1.64  | 1.80  | V       |                                                                                                                |

| $V_{BIAS}$ supply regulation      | 2                |       | +24.0 | +50   | mV      | Step $V_{CC}$ from 4.50V to 5.50V,                                                                             |

| $V_{BIAS}$ load regulation        | 2                |       | -17.0 | -50   | mV      | Step load from 0mA to 0.5mA,                                                                                   |

| Mixer conversion gain             | 11, 15           | 10.0  | 12.7  | 16.0  | dB      | $f_{CARRIER}=50MHz$ at -10dBm,<br>$f_{SIGNAL}=50.01MHz$ at -34dBm,<br>IF=10kHz, $Z_L$ (EXT)=1M $\Omega$ //20pF |

| Mixer A/B gain match              | 11, 15           | -1.0  | 0     | +1.0  | dB      | $f_{CARRIER}=50MHz$ at -10dBm,<br>$f_{SIGNAL}=50.01MHz$ at -34dBm,<br>IF=10kHz, $Z_L$ (EXT)=1M $\Omega$ //20pF |

NOTE: Typical figures are for a  $V_{CC}$  of 5.0V

# SL6442

## ELECTRICAL CHARACTERISTICS OF THE SL6442 DEMONSTRATION BOARD (PAGES 8-10)

These characteristics are guaranteed over the following conditions unless otherwise stated:

$T_{AMB} = 25^\circ C$ ,  $V_{CC} = 5.0V$ ,  $V_{AGC} = V_{BG}$ ,  $LO = -5dBm$ , Input/Output =  $50\Omega$ ,  $f_{IN} = 950MHz$ ,  $f_{LO} = 930MHz$  (IF = 20MHz),  $f_{LO} = 949-990MHz$  (IF = 10kHz)

| Overall performance         | Typ. | Units | Conditions                      |

|-----------------------------|------|-------|---------------------------------|

| Noise figure                | 8.3  | dB    | DSB (20MHz IF)                  |

| Third order input intercept | -22  | dBm   | 20MHz IF                        |

| Power gain                  | 7.5  | dB    | 20MHz IF                        |

| Voltage gain                | 30   | dB    | $Z_L > 100k\Omega$ , IF = 10kHz |

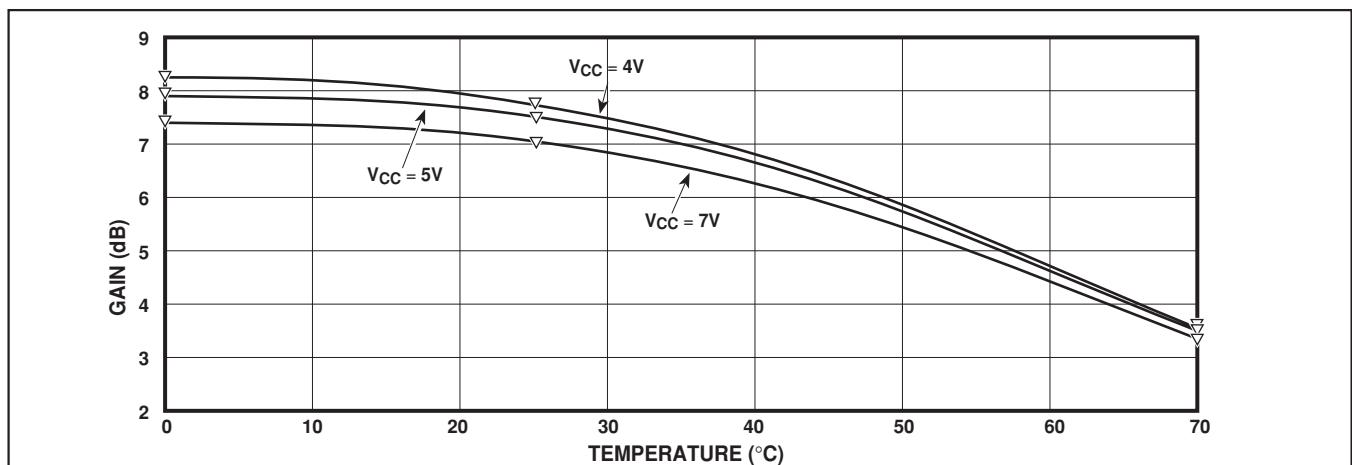

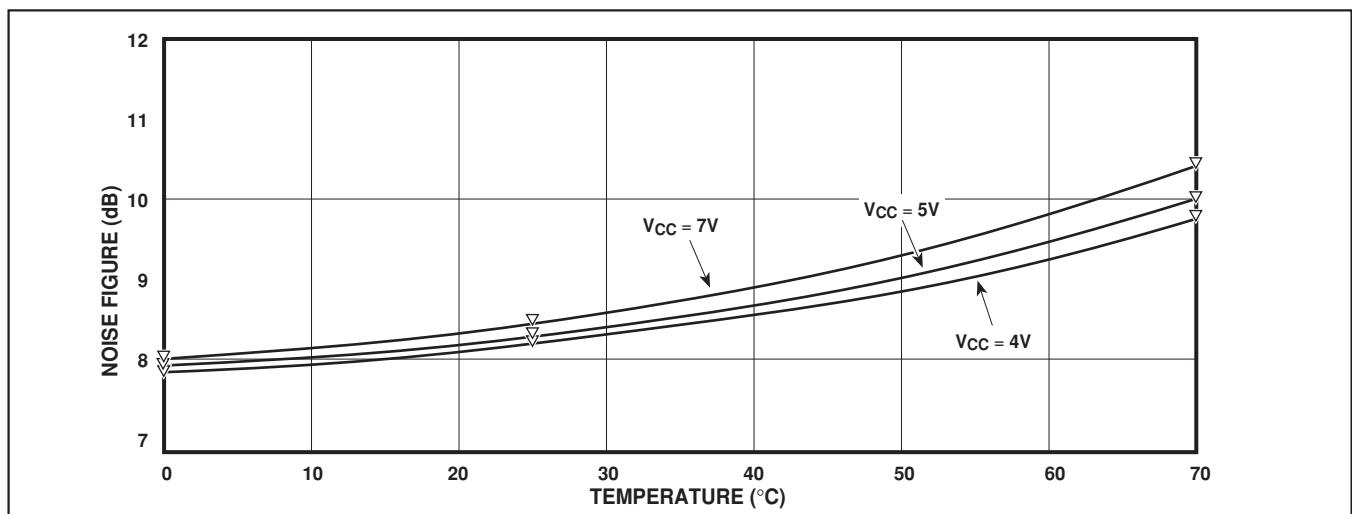

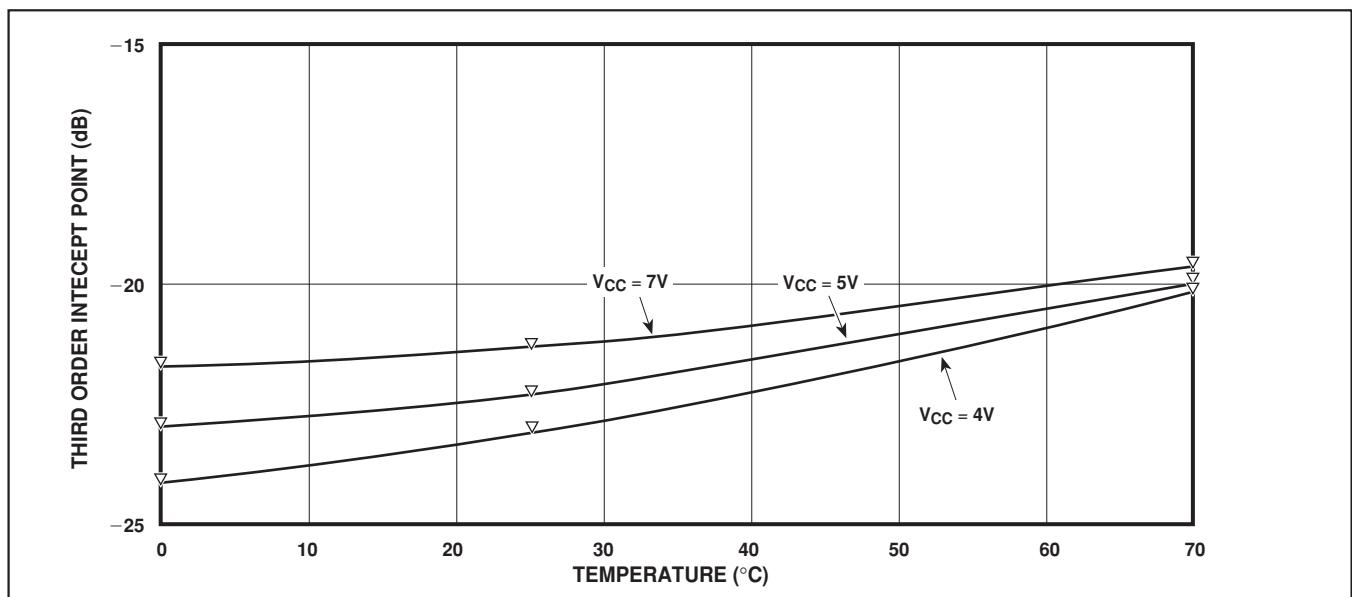

NOTE: Refer to Figs. 5, 6 and 7 for typical performance of overall low noise amplifier and mixer configuration (demonstration board) across temperature and supply voltage 4.0V, 5.0V and 7.0V).

## SUPPLEMENTARY INFORMATION

| Characteristic                           | Pin   | Value |           |      | Units      | Conditions                                                |

|------------------------------------------|-------|-------|-----------|------|------------|-----------------------------------------------------------|

|                                          |       | Min.  | Typ.      | Max. |            |                                                           |

| Operating supply voltage range           |       | 4.5   | 5.0       | 6.5  | V          |                                                           |

| <b>RF Amplifier Common emitter</b>       |       |       |           |      |            |                                                           |

| Power gain                               | 20    | 14    |           |      | dB         | Matched input and output.                                 |

| AGC range                                |       | 25    |           |      | dB         | $V_{BIAS} \pm 150mV$ typ. (see Fig. 9).                   |

| Input intercept                          |       | -9    |           |      | dBm        | Third order.                                              |

| 1dB gain compression                     |       | -23   |           |      | dBm        | At input                                                  |

| Noise figure                             |       | 4.5   |           |      | dB         | Common emitter.                                           |

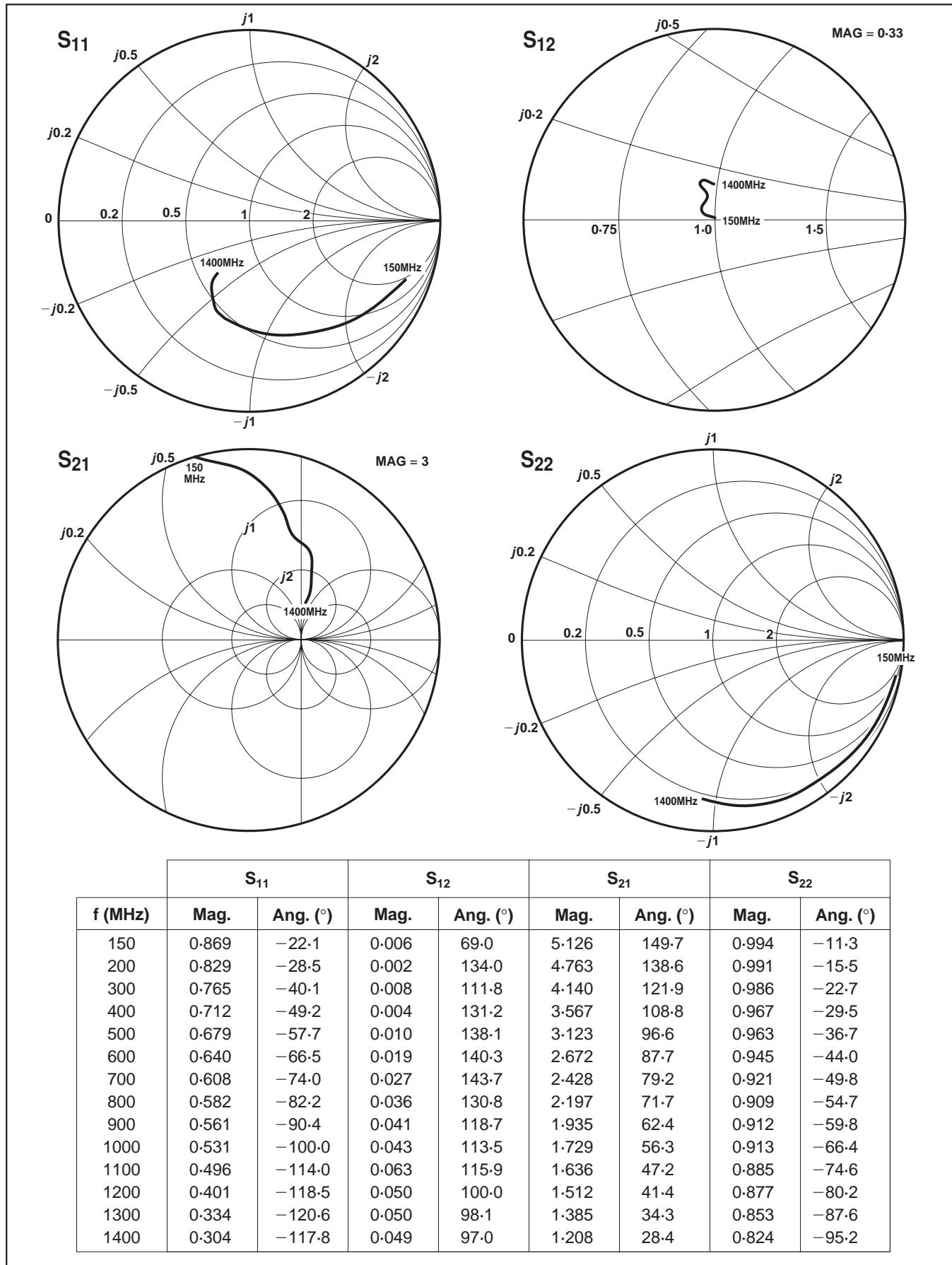

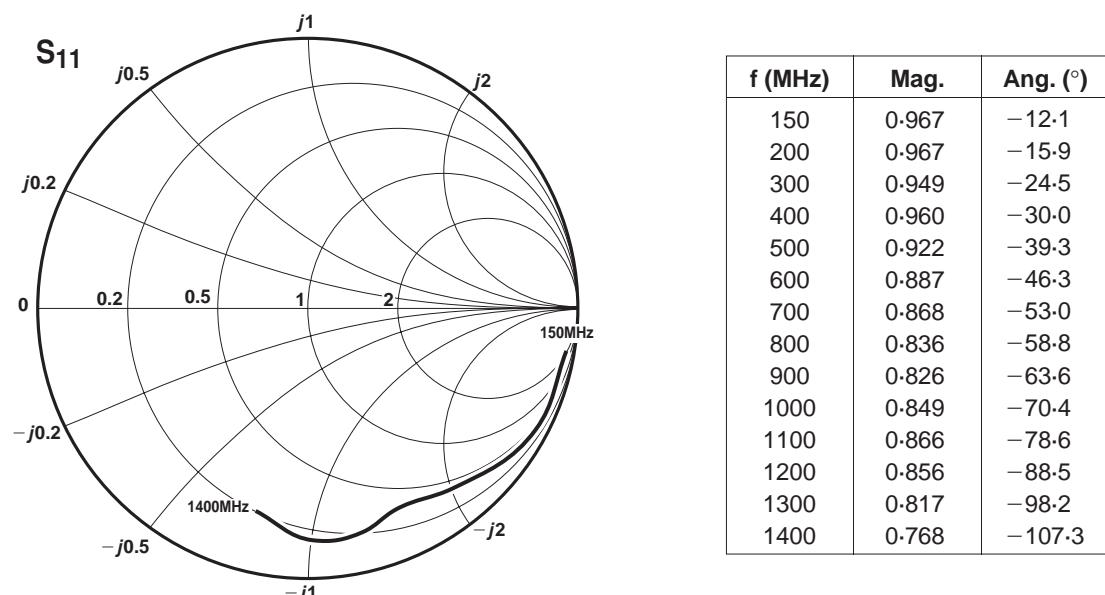

| Input impedance                          |       |       |           |      |            | See Fig. 8.                                               |

| Optimum operating frequency range        | 4     | 400   | 1000      |      | MHz        |                                                           |

| <b>Mixers (950MHz)</b>                   |       |       |           |      |            |                                                           |

| Voltage conversion gain                  |       | 19    |           |      | dB         | At IF = 50kHz, matched input.                             |

| Power conversion gain                    |       | -7    |           |      | dB         | At IF = 20kHz. Matched input and output.                  |

| LO drive level                           | 13,14 | -10   |           |      | dBm        | Measured at pins 13 and 14.                               |

| Input intercept point                    | 8     | -6    |           |      | dBm        | Third order.                                              |

| 1dB gain compression                     |       | -12   |           |      | dBm        | At input                                                  |

| Mixer 'A' to Mixer 'B' gain input match  |       |       | $\pm 1.0$ |      | dB         | Equal LO level at pins 13 and 14                          |

| Mixer 'A' to Mixer 'B' phase input match |       |       | +4        |      | deg        | LO inputs $90 \pm 0.1^\circ$ phase                        |

| Input impedance                          |       |       |           |      |            | See Fig. 10.                                              |

| Noise figure                             |       | 21    |           |      | dB         |                                                           |

| Optimum operating frequency range        | 8     | 1000  |           |      | MHz        | Low frequency operation dependent on external components. |

| IF output bandwidth                      | 11,15 | 20    |           |      | MHz        | Can be extended by external tuned circuit.                |

| Output impedance                         |       | 4     |           |      | k $\Omega$ |                                                           |

| Isolation LO to mix RF I/P               |       | 25    |           |      | dB         | All ports terminated with $50\Omega$                      |

| Reverse isolation of RF amp              |       | 14    |           |      | dB         | All ports terminated with $50\Omega$                      |

| Isolation LO to IF                       |       | 50    |           |      | dB         | All ports terminated with $50\Omega$                      |

| Isolation RF to IF                       |       | 37    |           |      | dB         | All ports terminated with $50\Omega$                      |

## PERFORMANCE CHARACTERISTICS OF THE SL6442 DEMONSTRATION BOARD

## Test conditions:

Input frequency = 950MHz, LO frequency = 930MHz, LO amplitude =  $-5\text{dBm}$ , intermediate frequency = 20MHz,  $V_{\text{AGC}} = V_{\text{BG}}$ , input/output  $50\Omega$  matched.

Fig. 5 Typical overall power gain

Fig. 6 Typical overall noise figure

Fig. 7 Typical overall third order intercept

Fig. 8 RF amplifier common emitter S-parameters

Fig. 9 SL6442 AGC characteristic

Fig. 10 Mixer RF input impedance,  $S_{11}$  (pin 8)

## APPLICATION CIRCUIT FOR USE AT 950MHz

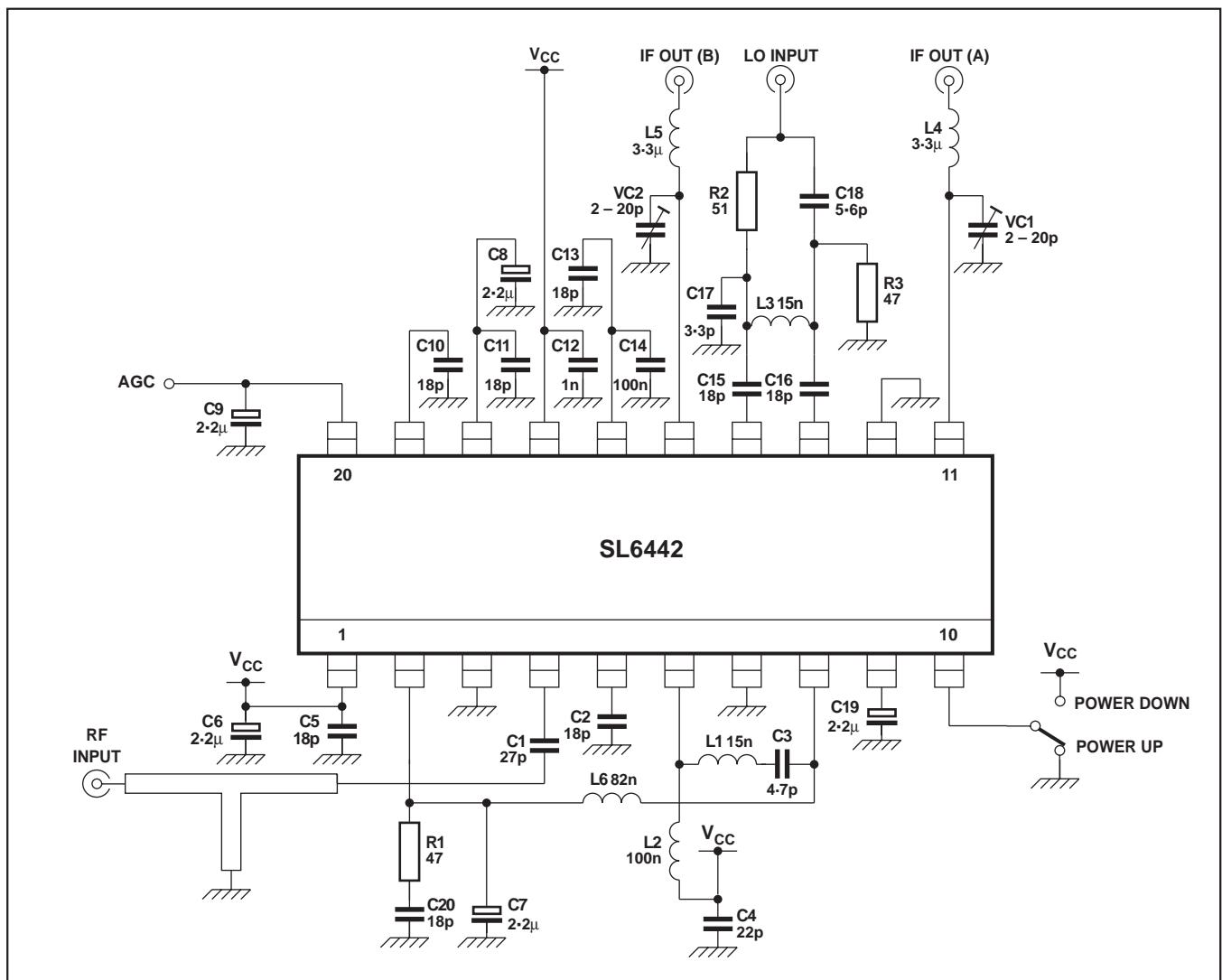

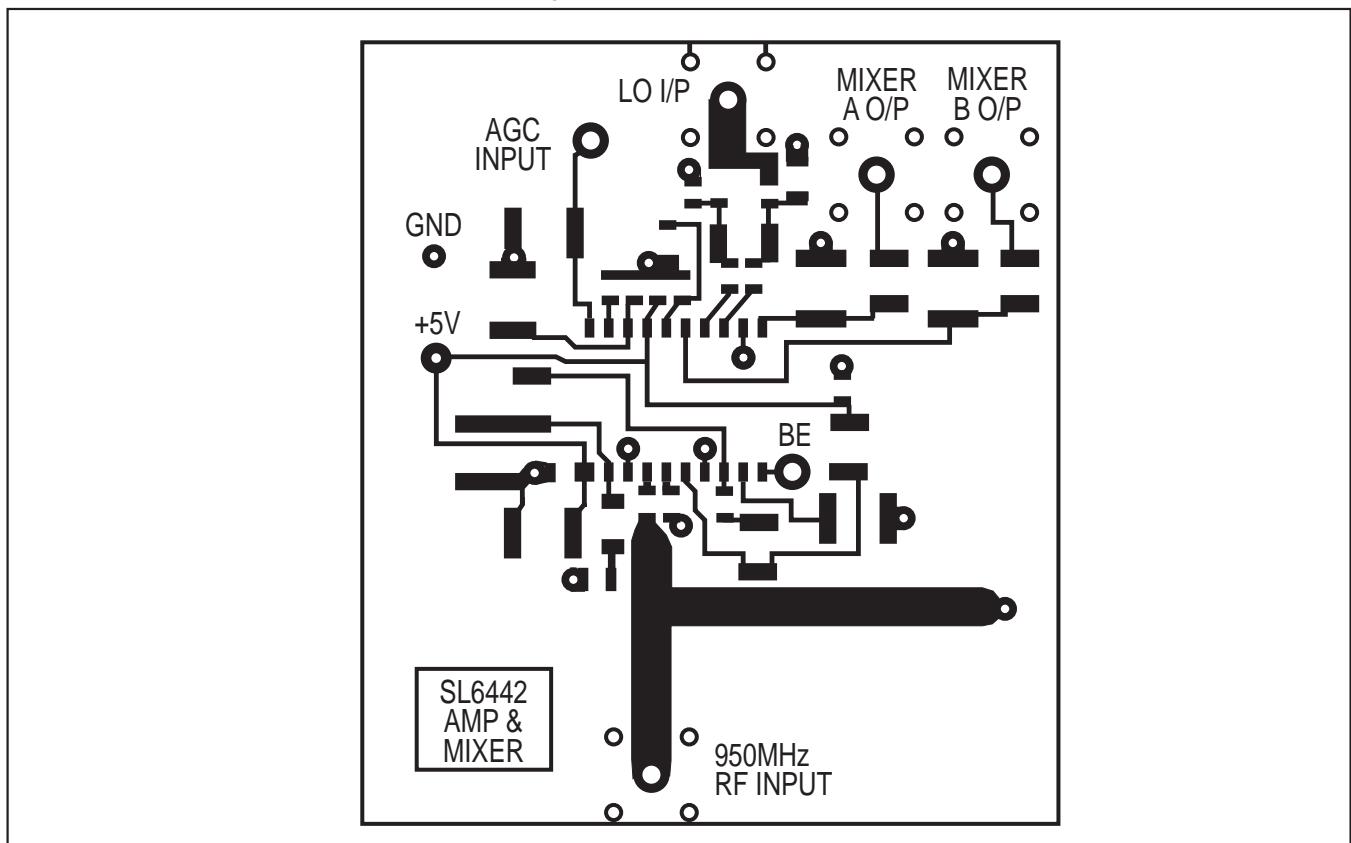

This Application Note describes a circuit which demonstrates the functions and performance of the SL6442 in a 950MHz amplifier/mixer receiver front end configuration.

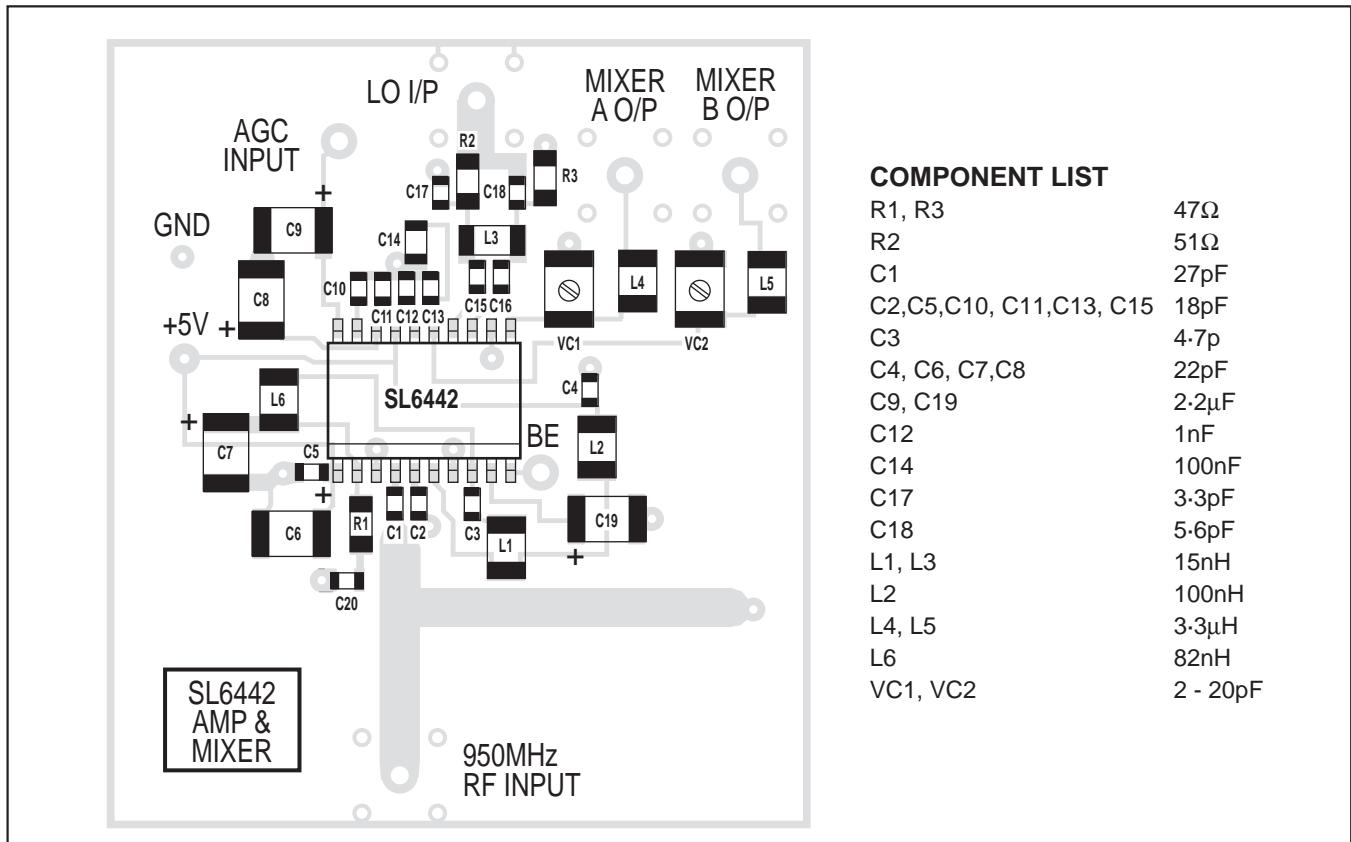

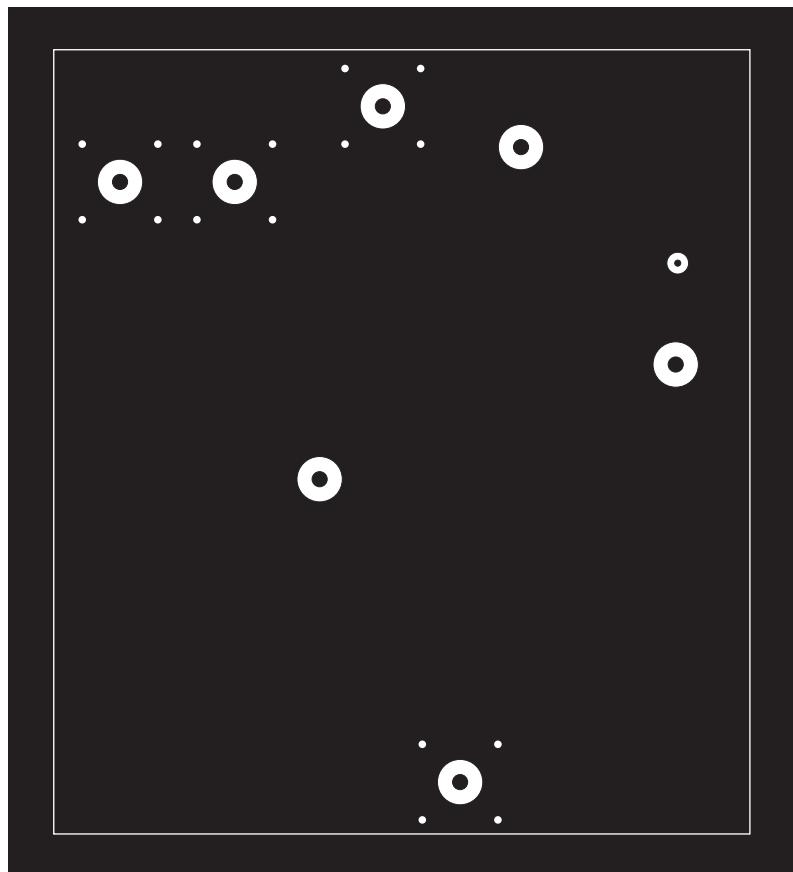

Fig. 11 is a schematic diagram which illustrates the arrangement of the ancillary components required for optimum performance at 950MHz. Component layout, PCB track and ground plane are shown in Figs. 12, 13 and 14, respectively. Approximate starting values for the components were obtained using Smith charts and data derived from S-parameter analysis (see Figs. 8 and 10).

The actual component values were determined by using a linear circuit simulator such as Touchstone™. In this case the circuit is optimised for maximum stable gain and minimum input reflection coefficient at the required frequency.

The input match is achieved using a stripline shorted-stub network. The LNA output to mixer input match is achieved by using a series inductor, and the mixer output to  $50\Omega$  match consists of a tunable LC network.

To prevent possible RF instability, pin 2 ( $V_{BIAS}$ ) is decoupled with a series RC network as well as a  $2.2\mu\text{F}$  capacitor.

The quadrature phase shift components consist of phase lead ( $R3$ ,  $C18$ ) and phase lag ( $R2$ ,  $C17$ ) networks, which are capacitively coupled to the LO input pins. Inductor  $L3$  serves to resonate out the parasitic capacitance between the two ports.

The exact values of the phase shift components were determined empirically and achieve a maximum amplitude and phase imbalance of about 1dB and 4 degrees respectively.

The variable capacitors  $VC1$  and  $VC2$  are adjusted to give a maximum output level at an IF of 20MHz. Other intermediate frequencies may require different values of  $VC1$  and  $VC2$  and/or  $L4$  and  $L5$ . At zero IF, as in direct conversion receivers, the output matching network is transparent.

If the AGC facility is not required it is necessary to connect pin 20 to pin 9 ( $V_{BG}$ ). The battery economy pin (10) may be connected directly to ground if the power down facility is not required.

*NOTE: Ensure adequate decoupling is used close to the chip, especially when designing for maximum power gain. Refer to LNA S-parameters to avoid possible stability problems when designing the LNA close to maximum gain.*

Fig. 11 SL6442 demonstration board circuit

Fig. 12 SL6442 demonstration board component layout. Scale=2 x full size. Input and output coaxial connectors are mounted on the ground plane side of the board.

Fig. 13 SL6442 demonstration board track. Scale=2 x full size

*Fig. 14 SL6442 demonstration board ground plane. Scale=2 x full size.*

**CUSTOMER NOTES**

## PACKAGE DETAILS

Dimensions are shown thus: mm (in). For further package information, please contact your local Customer Service Centre.

# GECPLESSEY

## SEMICONDUCTORS

**HEADQUARTERS OPERATIONS**

**GEC PLESSEY SEMICONDUCTORS**

Cheney Manor, Swindon,

Wiltshire SN2 2QW, United Kingdom.

Tel: (0793) 518000

Fax: (0793) 518411

**GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017

1500 Green Hills Road,

Scotts Valley, CA95067-0017

United States of America.

Tel (408) 438 2900

Fax: (408) 438 5576

#### Customer Service Centres

**FRANCE & BENELUX** Les Ulis Cedex Tel: (1) 64 46 23 45 Tx: 602858F

Fax : (1) 64 46 06 07

**GERMANY** Munich Tel: (089) 3609 06-0 Tx: 523980 Fax : (089) 3609 06-55

**ITALY** Milan Tel: (02) 66040867 Fax: (02) 66040993

**JAPAN** Tokyo Tel: (03) 3296-0281 Fax: (03) 3296-0228

**NORTH AMERICA Integrated Circuits and Microwave Products**, Scotts Valley, USA

Tel: (408) 438 2900 Fax: (408) 438 7023.

**Hybrid Products**, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061.

**SOUTH EAST ASIA** Singapore Tel: (65) 3827708 Fax: (65) 3828872

**SWEDEN** Stockholm Tel: 4687029770 Fax: 4686404736

**UK, EIRE, DENMARK, FINLAND & NORWAY**

Swindon Tel: (0793) 518510 Tx: 444410 Fax : (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1993 Publication No. DS3047 Issue No. 3.2 September 1993

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

**For more information about all Zarlink products

visit our Web Site at

[www.zarlink.com](http://www.zarlink.com)**

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in an I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

**TECHNICAL DOCUMENTATION - NOT FOR RESALE**