# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

### **SL2364**

#### **VERY HIGH PERFORMANCE TRANSISTOR ARRAYS**

The SL2364 is an array of transistors internally connected to form a dual long-tailed pair with tail transistors. This is a monolithic integrated circuit manufactured on a very high speed bipolar process which has a minimum useable  $f_T$  of 2.5GHz, (typically 5GHz).

The SL2364 is in a 14 SO package and a high performance Dilmon encapsulation.

#### **FEATURES**

- Complete Dual Long-Tailed Pair in One Package

- Very High f<sub>T</sub> Typically 5 GHz

- Very Good Matching Including Thermal Matching

#### **APPLICATIONS**

- Wide Band Amplification Stages

- 140 and 560 MBit PCM Systems

- Fibre Optic Systems

- High Performance Instrumentation

- Radio and Satellite Communications

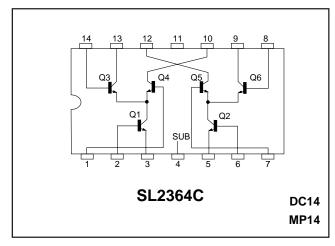

Fig. 1 Pin connections (top view)

#### **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed of the following conditions (unless otherwise stated):  $T_{amb} = 22^{\circ}C \pm 2^{\circ}C$

| Characteristics   Min.   Typ.                                                                                                                                                                                                                                                                                                                              | Max.            | Units                                   | Conditions                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                                                                                                                                                                                                          |                 |                                         |                                                                                                                                                                                                                                                                                                         |

| $ \begin{array}{ c c c c c c } & LV_{\text{CEO}} & & 6 & 9 \\ BV_{\text{EBO}} & & 2.5 & 5.0 \\ BV_{\text{CIO}} & & 16 & 40 \\ h_{\text{FE}} & & 50 & 80 \\ f_{\text{T}} & & 2.5 & 5 \\ \Delta V_{\text{BE}} (\text{See note 1}) & & 2 \\ \Delta V_{\text{BE}} / T_{\text{AMB}} & & -1.7 \\ C_{\text{CB}} & & 0.5 \\ C_{\text{CI}} & & 1.0 \\ \end{array} $ | 5<br>0.8<br>1.5 | V<br>V<br>V<br>GHz<br>mV<br>mV/°C<br>pF | $\begin{split} I_{c} &= 10 \mu A \\ I_{c} &= 5 m A \\ I_{E} &= 10 \mu A \\ I_{C} &= 10 \mu A \\ I_{C} &= 8 m A, \ V_{CE} = 2 V \\ I_{C} \ Tail) &= 8 m A, \ V_{CE} = 2 V \\ I_{C} \ Tail) &= 8 m A, \ V_{CE} = 2 V \\ I_{C} \ Tail) &= 8 m A, \ V_{CE} = 2 V \\ V_{CB} &= 0 \\ V_{CI} &= 0 \end{split}$ |

NOTE 1.  $\Delta V_{BE}$  applies to  $|V_{BEQ3} - V_{BEQ4}|$  and  $|V_{BEQ5} - V_{BEQ6}|$

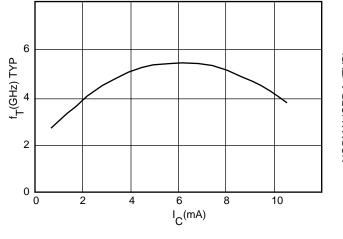

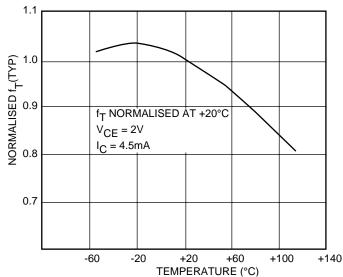

#### **TYPICAL CHARACTERISTICS**

Fig. 2 Collector current

Fig. 3 Chip temperature

#### **ABSOLUTE MAXIMUM RATINGS**

Maximum individual transistor dissipation 200mW

Storage temperature -55°C to + 150°C Maximum junction temperature + 150°C

Package thermal resistance (°C/W):

**Chip to case** 45 (MP14) 35 (DC14) **Chip to ambient** 123 (MP14) 120 (DC14)

VCBO = 10V, VEBO = 2 5V VCEO = 6V. VCIO = 15V IC (any one transistor) = 20mA

The substrate should be connected to the most negative point of the circuit to maintain electrical isolation between the transistors.

## For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE