# <u>S1F78520</u>

## **Charge-pump Step Down Regulator** with Power Saving Mode

#### **■ DESCRIPTION**

The S1F78520 is a power IC which can generate two stabilized output voltages of 3.3 V (or 2.9 V or 2.5 V) and 2.5 V (or 2.0 V or 1.8 V) using the Li-ion battery. The 3.3 V range output is being generated through the LDO (series regulator). The 2.5 V range output is being generated through the charge pump type DC/DC converter consisting of built-in CMOS transistors. Since the voltages are being stabilized by adjustments of the charge pump DC/DC switching frequencies, higher conversion efficiencies as compared with the conventional series regulators can be acquired. Since the S1F78520 does not require external transistors, coils nor diodes, it is most suitable for the down sizing purpose and for reduction of the current consumption.

#### **■ FEATURES**

| Supply voltage                                       | 3.6 V ((TBD) 2.8 V to 5.5 V) single power input          |

|------------------------------------------------------|----------------------------------------------------------|

| Voltage conversion method                            | < 3.3V range output > LDO (series regulator)             |

|                                                      | < 2.5V range output > Voltage dropping type charge pump  |

| Output voltages                                      | $<$ 3.3V range output > 3.3 V or 2.9 V or 2.5 V $\pm$ 3% |

|                                                      | < 2.5V range output > 2.5 V or 2.0 V or 1.8 V $\pm$ 4%   |

| Output current (Normal state/Standby state)          | < 3.3V range output > Max. (100 mA/1 mA)                 |

|                                                      | $<$ 2.5V range output $>$ Max. (80 mA/100 $\mu$ A)       |

| Conversion efficiency                                | < 3.3V range output > 90%                                |

|                                                      | < 2.5V range output > (TBD) 85% (Reference data: The     |

|                                                      | conversion efficiency from 3.3 V to 2.0 V by the series  |

|                                                      | regulator is 60%.)                                       |

| Shut down current                                    | 1 μΑ                                                     |

| Self-consumption current                             | (TBD) 100 μA (under no load state)                       |

| Built-in self-consumption current suppressing functi | on by use of standby (light load) signals                |

| Self-consumption current ······                      | (TBD) 20 µA (under no load state)                        |

- Self-consumption current ······ (TBD) 20 μA (under no load state)

- Built-in power good detector (equipped with the delay setting function)

- Built-in low voltage detecting circuit (For setting of the detecting voltages, either of the internal setting fixed to the IC or the external pin setting is selectable.)

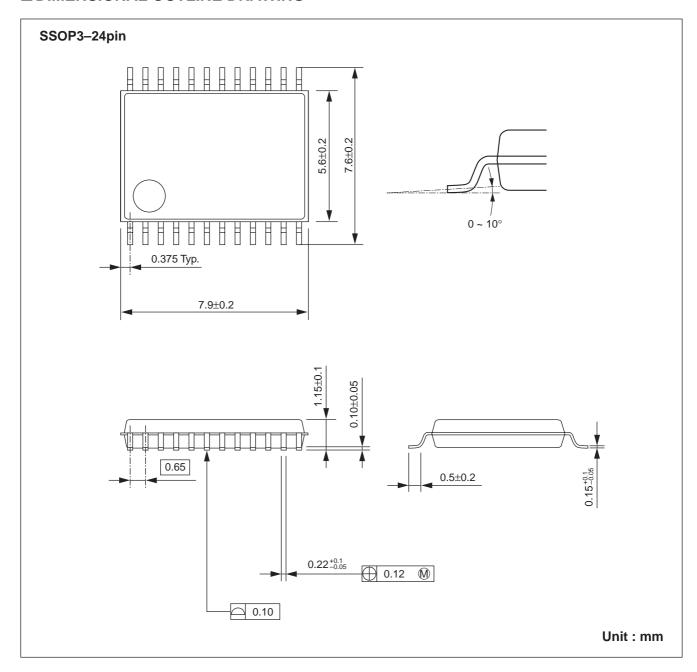

- Shipping state ······ SSOP3-24pin

- This IC is not of the radiation resistant design nor of the light resistance design.

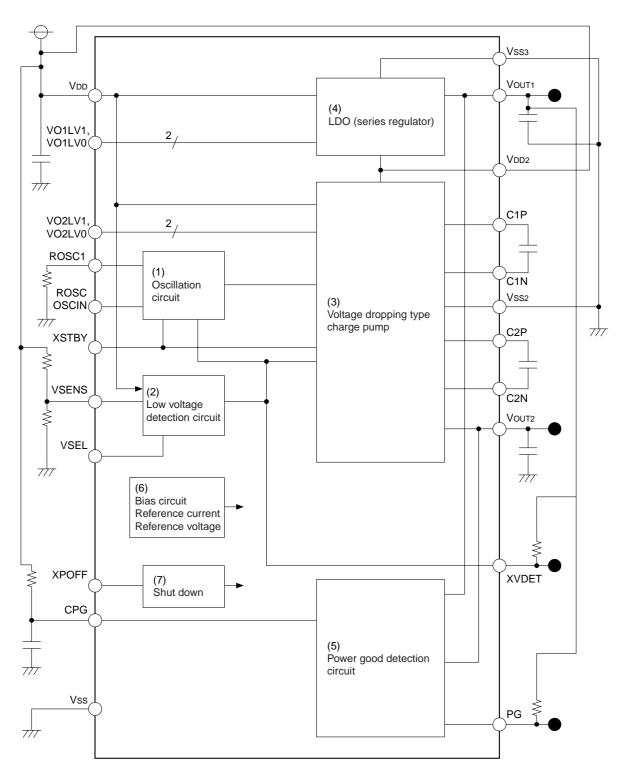

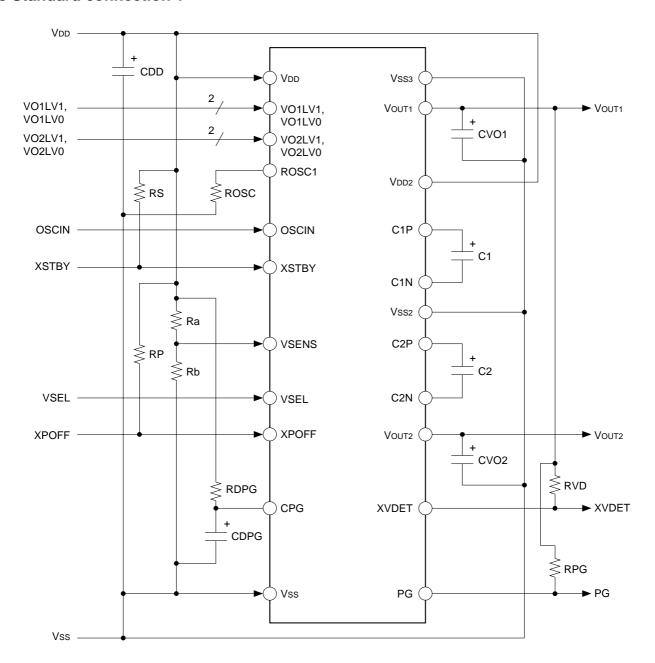

#### **■ BLOCK DIAGRAM**

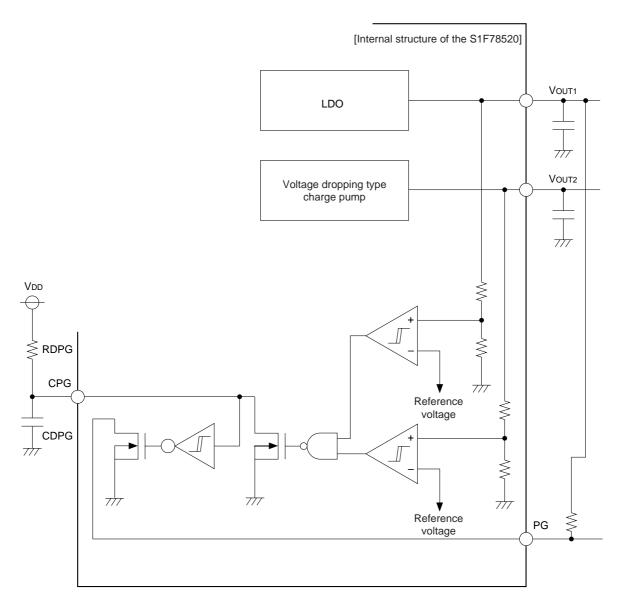

Fig. 1 Block diagram

#### ■ DESCRIPTIONS FOR THE BLOCK DIAGRAM

#### (1) Oscillation circuit

This is the circuit to make oscillations by connecting a resistance to the ROSC1 pin and by supplying a constant current.

#### (2) Low voltage detection circuit

This circuit makes low voltage detections by monitoring the input voltage through the VDD pin. Provision of a hysteresis width is effective to prevent occurrences of unstable outputs (causing oscillations) while performing low voltage detecting operations. For setting of the detecting voltages, use of either of the internal voltage setting fixed to the IC or the external voltage setting pin VSENS is selectable through the VSEL pin.

#### (3) Voltage dropping type charge pump

The specified voltage is being output by voltage drops effected by the charge pump upon the inputted supply voltage VDD\* - VSS\* and using the VSS\* potential as the reference voltage. The specified voltage is selectable (2.5 V or 2.0 V or 1.8 V) through the external pins VO2LV1, VO2LV0.

Also, the voltages are being stabilized by adjusting the switching frequencies of the charge pump. This circuit can drastically suppress the current consumption under the standby mode (light load).

#### (4) LDO (series regulator)

It stabilizes the voltage of the levels below the input supply voltage. The specified voltage is selectable (3.3 V or 2.9 V or 2.5 V) through the external pins VO1LV1, VO1LV0.

#### (5) Power good detection circuit

This circuit detects the power good signals when the output pins VouT1 and VouT2 are satisfying the specified voltage. Delay setting can be made for the power good signals by connecting a capacitor and a resistor to the external setting pin CPG.

#### (6) Bias circuit

This circuit generates the reference voltage and reference current which are necessary for this IC.

#### (7) Shut down

Operations of all the circuits can be interrupted by setting the shut down pin XPOFF to the Vss\* level.

<Note> VDD\* = VDD, VDD2, VSS\* = VSS, VSS2, VSS3

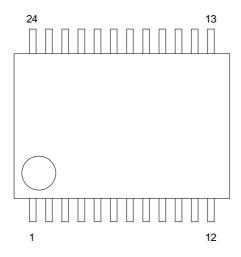

#### **■ PIN ASSIGNMENT**

SSOP3-24pin S1F78520M0A0

| Pin No. | Pin name | Pin No.  | Pin name |  |

|---------|----------|----------|----------|--|

| 1       | XPOFF    | 13       | XVDET    |  |

| 2       | VO2LV0   | 14       | VSENS    |  |

| 3       | VO2LV1   | 15       | VDD      |  |

| 4       | C1N      | 16       | VSEL     |  |

| 5       | C1P      | 17       | Vss3     |  |

| 6       | VOUT2    | 18       | VOUT1    |  |

| 7       | PG       | 19       | VDD2     |  |

| 8       | CPG      | PG 20 C2 |          |  |

| 9       | ROSC1    | 21       | C2N      |  |

| 10      | Vss      | 22       | VO1LV1   |  |

| 11      | OSCIN    | 23       | VO1LV0   |  |

| 12      | XSTBY    | 24       | VSS2     |  |

#### **■ PIN DESCRIPTION**

(1) Function pins

| Pin name       | I/O    | Pin No. |                         |               | Fun               | ection                                                                             |

|----------------|--------|---------|-------------------------|---------------|-------------------|------------------------------------------------------------------------------------|

| VO1LV1         | I      | 22      | Vout Output             | voltage level | designating       | pin.                                                                               |

|                |        |         | Pin se                  | etting        | Output            |                                                                                    |

|                |        |         | VO1LV1                  | VO1LV0        | voltage           |                                                                                    |

|                |        |         | Vss* level              | Vss* level    | 3.3V              |                                                                                    |

| VO1LV0         | I      | 23      | Vss* level              | VDD* level    | 2.9V              |                                                                                    |

|                |        |         | V <sub>DD</sub> * level | Vss* level    | 2.5V              |                                                                                    |

|                |        |         | VDD* level              | VDD* level    | Not for use       |                                                                                    |

| VO2LV1         | I      | 3       | Vout Output             | voltage level | designating       | pin.                                                                               |

|                |        |         | Pin se                  | etting        | Output            |                                                                                    |

|                |        |         | VO2LV1                  | VO2LV0        | voltage           |                                                                                    |

|                |        |         | Vss* level              | Vss* level    | 2.5V              |                                                                                    |

| VO2LV0         | I      | 2       | Vss* level              | VDD* level    | 2.0V              |                                                                                    |

|                |        |         | V <sub>DD</sub> ∗ level | Vss* level    | 1.8V              |                                                                                    |

|                |        |         | V <sub>DD</sub> ∗ level | VDD* level    | Not for use       |                                                                                    |

| DOCC4          |        | 0       |                         |               | l                 | division and of the application accuracy.                                          |

| ROSC1<br>XSTBY | 0<br>I | 9       |                         |               |                   | djustment of the oscillating current. by mode (light load), the internal structure |

| ASIBI          | '      | 12      |                         |               |                   | consumption when this signal is set to the                                         |

|                |        |         | Vss* level.             | o operated b  | y low ourront     | ochodinplion when the signal is set to the                                         |

| VSENS          | I      | 14      |                         | ge inputting  | pin for the lo    | w voltage detection circuit. This is effec-                                        |

|                |        |         | tive only when          | the eternal s | etting is bein    | g selected.                                                                        |

| VSEL           | I      | 16      | _                       | -             | •                 | w voltage detection circuit.                                                       |

|                |        |         | _                       | • .           | • .               | NS becomes valid when this pin is set to                                           |

|                |        |         |                         |               |                   | enerated inside the IC becomes valid                                               |

| XPOFF          | 1      | 1       | when this pin is        |               |                   | the VDD* level while the IC is in operation.                                       |

| XI OI I        | '      | '       |                         | •             | •                 | rupted when this signal is set to the VSS*                                         |

|                |        |         |                         |               |                   | state and making the output pins XVDET,                                            |

|                |        |         | PG to open sta          |               |                   | 3 1 1                                                                              |

| CPG            | I      | 8       | Delay time sett         |               |                   |                                                                                    |

| C1P            | 0      | 5       |                         |               | for the flying    | g capacitor C1 for generation of the Vout2                                         |

|                |        |         | output voltage.         |               |                   |                                                                                    |

| C1N            | 0      | 4       | _                       |               | n for the flying  | g capacitor C1 for generation of the Vout2                                         |

| C2P            | 0      | 20      | output voltage.         |               | for the flying    | capacitor C2 for generation of the Vout2                                           |

| CZF            |        | 20      | output voltage.         | •             | i ioi uie ilyilig | g capacitor G2 for generation of the VO012                                         |

| C2N            | 0      | 21      |                         |               | n for the flying  | g capacitor C2 for generation of the Vout2                                         |

|                |        |         | output voltage.         |               |                   | g g                                                                                |

| XVDET          | 0      | 13      |                         |               | output pin for    | the low voltage detection circuit. The                                             |

|                |        |         | output state is         | •             |                   |                                                                                    |

|                |        |         |                         |               | •                 | power pin VDD is at the low voltage level.                                         |

| PG             | 0      | 7       |                         |               |                   | output power pins POUT1 and POUT2.                                                 |

|                |        |         | The output stat         |               |                   | tput power pins are satisfying the speci-                                          |

|                |        |         | fied voltage.           | nen boln of l | ne above out      | that hower hiris are satisfying the sheet-                                         |

|                |        |         | nou voitage.            |               |                   |                                                                                    |

## S1F78520

#### (2) Power pins

| Pin name | I/O | Pin No. | Function                                            |

|----------|-----|---------|-----------------------------------------------------|

| VDD      | I   | 15      | Positive side input power pin.                      |

| VDD2     | I   | 19      | Positive side input power pin.                      |

| Vss      | I   | 10      | Negative side input power pin.                      |

| VSS2     | I   | 24      | Negative side input power pin.                      |

| Vss3     | I   | 17      | Negative side input power pin.                      |

| Vout1    | 0   | 18      | LDO (series regulator) put0put power pin.           |

| VOUT2    | 0   | 6       | Voltage dropping type charge pump output power pin. |

<sup>&</sup>lt;Note 1> Connect the VDD and VDD2 each other externally and keep them at the same potential level.

#### (3) Testing pin

| Pin name | I/O | Pin No. | Function       |

|----------|-----|---------|----------------|

| OSCIN    | I   | 11      | Normally open. |

<sup>&</sup>lt;Note 2> Connect the Vss < Vss2 and Vss3 each other externally and keep them at the same potential level.

#### **■ FUNCTIONAL DESCRIPTION**

#### Operational description

By use of the standby input signals, high conversion efficiencies can be acquired under heavy loads, while low current consumption operations can be realized under light load state.

Generating voltage levels are:

- LDO (series regulator) output voltage [3.3 V or 2.9 V or 2.5 V]\*1 (VOUT1)

- Voltage dropping type charge pump output voltage [2.5 V or 2.0 V or 1.8 V]\*2 (VOUT2)

- \*1: Selection of 3.3 V or 2.9 V or 2.5 V is to be designated by use of the external pins VO1LV1, VO1LV0.

- \*2: Selection of 2.5 V or 2.0 V or 1.8 V is to be designated by use of the external pins VO2LV1, VO2LV0.

The Vout1 output voltage is being generated by stabilizing the potential difference occurring between "VDD\* – Vss\*" using the Vss\* potential as the reference voltage.

While the Voutage is being generated after selection of the optimum voltage dropping ratio among different voltage dropping ratios for the voltage dropping type charge pump to let it work on the potential difference occurring between "VDD\* – VSS\*" using the VSS\* potential as the reference voltage and stabilizing the voltage by fine adjustments of the switching frequencies. Since an extra voltage stabilizing circuit is not being used for the output, high conversion efficiencies can be acquired.

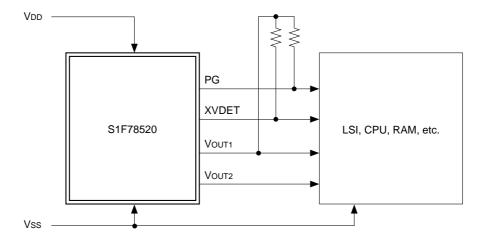

Indicated below is the system configuration diagram for the power circuit.

Fig. 2 System configuration diagram

#### Oscillation circuit

The S1F78520 incorporates an oscillation circuit for the voltage dropping clock. This circuit is to be used connecting the oscillation current adjusting external resistor ROSC between the ROSC1 pin and the Vss. The oscillation circuit will stop operation under shut down state (XPOFF = Vss\* level). Also, the oscillation will be interrupted by setting the ROSC1 pin to the VDD\* level or by making the pin into open state.

As the oscillation current adjusting external resistance, we recommend use of ROSC = (TBD)  $\Omega$ .

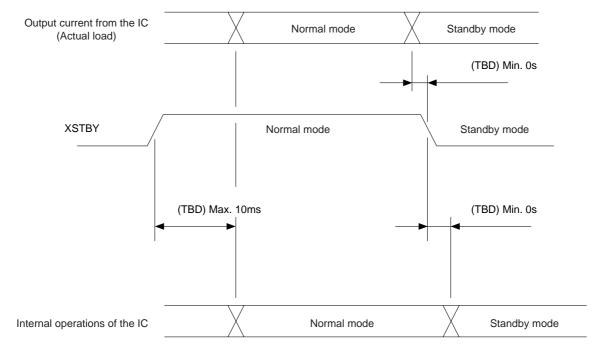

#### Standby mode

By setting the standby mode signal XSTBY externally, current consumption of this IC can be suppressed drastically.

The time required after the mode change is made with the standby pin until the internal mode of the IC is stabilized should be (TBS) max. 10ms to min. 0s. Complete timing design should be effected when using the standby mode.

| XSTBY pin  | Mode name                | Max. output current  | Self-consumption current |

|------------|--------------------------|----------------------|--------------------------|

|            |                          |                      | (Under no load state)    |

| VDD* level | Normal mode              | VOUT1:(100 mA) (TBD) | (TBD)                    |

|            | (Under heavy load state) | VOUT2:(80 mA) (TBD)  | 100 μΑ                   |

| Vss* level | Standby mode             | Vout1:(1 mA) (TBD)   | (TBD)                    |

|            | (Under light load state) | VOUT2:(100 μA) (TBD) | 20 μΑ                    |

Fig. 3 below indicates a mode changing timing example.

#### Low voltage detection circuit

This circuit makes low voltage detections by monitoring the input voltage through the VDD pin. For setting of the detecting voltages, use of either of the internal voltage setting fixed to the IC or the external voltage setting pin VSENS is selectable through the external input pin VSEL.

| VSEL pin   | Detecting voltage selection    | Detecting voltage value                 |

|------------|--------------------------------|-----------------------------------------|

| Vss* level | External pin VSENS             | -VDET: (According to the formula 7.4.2) |

|            |                                | +VDET: (According to the formula 7.4.4) |

| VDD* level | Internal voltage setting fixed | -VDET: 3.30 V (TBD)                     |

| or         | to the IC                      | +VDET: 3.39 V (TBD)                     |

| Open       |                                |                                         |

The detecting voltage (-VDET) in case of external voltage setting will be the VDD voltage value satisfying the following formulae.

$$\label{eq:VREF1} $$ VREF1 \ge VDD \bullet (Rb)/(Ra+Rb) = VSENS \dots (Formula~7.4.1)$$ Consequently, $$ VDD \le VREF1 \bullet (Ra+Rb)/(Rb)~[V] \dots (Formula~7.4.2)$$ can be established.$$

Also, the cancelling voltage (+VDET) in case of external voltage setting will be the VDD voltage value satisfying the following formulae.

$$\label{eq:VREF2} $$ VREF2 \le VDD \bullet (Rb)/(Ra+Rb) = VSENS ......(Formula 7.4.3)$$ Consequently, $$ VDD \ge VREF2 \bullet (Ra+Rb)/(Rb) [V] .....(Formula 7.4.4)$$ can be established.$$

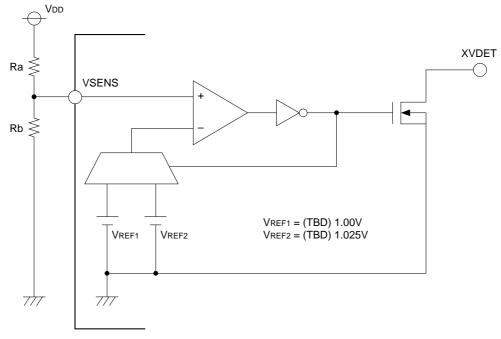

Fig. 4 below shows the block diagram for the external setting.

Fig. 4 Block diagram for the external setting

#### Power good detection circuit

Power good signals are detected when both of the output pins VOUT1 and VOUT2 are satisfying the specified voltage.

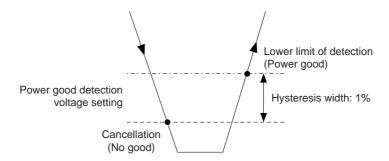

As for the power good detection range, provision of a hysteresis width for the lower limit value of detection according to Fig. 5 indicated below is effective to prevent occurrences of unstable power good signal outputs in the neighborhood of the detection limit value range.

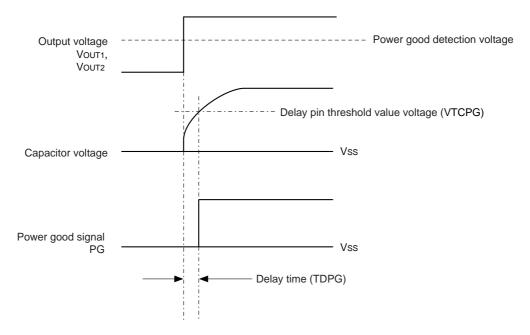

Also, delay setting can be made for the power good signals by use of the capacitor CDPG and the resistor RDPG. When the output voltage rises beyond the cancelling voltage, charge to the external capacitor will begin. When the capacitor voltage rises beyond the delaying threshold valve voltage, the power good signal changes from the Vss\* level to open state.

The delaying time can be calculated by (TBD).

Fig. 6 is an outline drawing for delay settings and Fig. 7 is the connection diagram in the neighborhood of the power good detection circuit.

Fig. 5 Power good detecting range

11

Graph indicating the correlation between the formula or the capacitor setting and the delay time

(TBD)

Fig. 6 Outline drawing for delay settings

Fig. 7 Connection diagram in the neighborhood of the power good detection circuit

#### ■ ABSOLUTE MAXIMUM RATINGS

| lt a ma                        | Cours In a l | Rat         | ing          | l loo!t | A mulicable min    | Damanla    |

|--------------------------------|--------------|-------------|--------------|---------|--------------------|------------|

| Item                           | Symbol       | Min.        | Max.         | Unit    | Applicable pin     | Remarks    |

| Input supply voltage           | VDD          | -0.3        | 7.0          | V       | VDD                | _          |

| Output voltage 1               | VOUT1        | -0.3        | 7.0          | V       | Vout1              | _          |

| Output voltage 2               | VOUT2        | -0.3        | 7.0          | V       | VOUT2              | _          |

| Input pin voltage              | VIN          | -0.3        | VDD+0.3      | V       | <note 1=""></note> | _          |

| Input current                  | IVDD         | _           | (TBD)<br>120 | mA      | VDD                | _          |

| Output current 1               | IVOUT1       | _           | (TBD)<br>60  | mA      | VOUT1              | _          |

| Output current 2               | IVOUT2       | _           | (TBD)<br>60  | mA      | VOUT2              | _          |

| Allowable dissipation          | PD           | _           | (TBD)        | mW      | _                  | Ta ≤ 55 °C |

| Operating temperature          | Topr         | -30         | 85           | °C      | _                  | _          |

| Storage temperature            | Tstg         | <b>-</b> 55 | 150          | °C      | _                  | _          |

| Soldering temperature and time | Tsol         | _           | 260 · 10     | °C·s    | _                  | At leads   |

<sup>&</sup>lt;Note 1> The applicable pins are VO1LV1, VO1LV0, VO2LV1, VO2LV0, XSTBY, VSENS, VSEL, XPOFF and OSCIN.

<sup>&</sup>lt;Note 2> Do not apply external voltage to the output pins and the pin connecting to the capacitor.

<sup>&</sup>lt;Note 3> Use of the IC under any conditions exceeding the above absolute maximum ratings may cause malfunctioning or permanent breakdown. Or, even if the IC may operate normally temporarily, the reliability may greatly drop.

#### **■ ELECTRICAL CHARACTERISTICS**

#### DC characteristics

## OLDO (series regulator), voltage dropping type charge pump

In case particular designations are not made (Note 1):  $Ta = 25 \, ^{\circ}C$

|                          | Symbol  | Conditions                                                                                 |         | Rating |              |      |         |

|--------------------------|---------|--------------------------------------------------------------------------------------------|---------|--------|--------------|------|---------|

| Item                     |         |                                                                                            | Min.    | Тур.   | Max.         | Unit | Remarks |

| Input supply voltage     | VDD     | Applicable pin: VDD                                                                        | _       | 3.6    | 5.5          | V    | _       |

| High level input voltage | VIH     | _                                                                                          | 0.7*VDD |        | VDD          | V    | 2       |

| Low level input voltage  | VIL     | _                                                                                          | 0       | _      | 0.3*VDD      | V    | 2       |

| Input leak current       | ILKI    | $Vss \le VI \le Vdd$<br>Vdd = (TBD) 3.6 V                                                  | -0.5    | _      | 0.5          | μΑ   | 2       |

| Output voltage 11        | VOUT11  | Applicable pin: Vout1 Output voltage setting: 3.3 V VDD = (TBD) 3.6 V IVOUT1 = (TBD) 10 mA | 3.20    | 3.30   | 3.40         | V    | _       |

| Output voltage 12        | VOUT12  | Applicable pin: Vout1 Output voltage setting: 2.9 V VDD = (TBD) 3.6 V IVOUT1 = (TBD)10 mA  | 2.81    | 2.90   | 2.99         | V    | _       |

| Output voltage 13        | VOUT13  | Applicable pin: Vout1 Output voltage setting: 2.5 V VDD = (TBD) 3.6 V IVOUT1 = (TBD)10 mA  | 2.42    | 2.50   | 2.58         | V    | _       |

| Output voltage 21        | VOUT21  | Applicable pin: Vout2 Output voltage setting: 2.5 V VDD = (TBD) 3.6 V IVOUT2 = (TBD)10 mA  | 2.40    | 2.50   | 2.60         | V    | _       |

| Output voltage 22        | VOUT22  | Applicable pin: Vout2 Output voltage setting: 2.0 V VDD = (TBD) 3.6 V IVout2 = (TBD)10 mA  | 1.92    | 2.00   | 2.08         | V    | _       |

| Output voltage 23        | VOUT23  | Applicable pin: VOUT2 Output voltage setting: 1.8 V VDD = (TBD) 3.6 V IVOUT2 = (TBD)10 mA  | 1.72    | 1.80   | 1.88         | V    | _       |

| Output voltage 11        | IVOUT11 | Applicable pin: Vouta<br>Output voltage setting: 3.3 V<br>VDD = (TBD) 3.6 V                | _       | _      | (TBD)<br>100 | mA   | _       |

| Output voltage 12        | IVOUT12 | Applicable pin: Vouta Output voltage setting: 2.9 V VDD = (TBD) 3.6 V                      | _       | _      | (TBD)<br>100 | mA   | _       |

| Output voltage 13        | IVOUT13 | Applicable pin: Vout1 Output voltage setting: 2.5 V VDD = (TBD) 3.6 V                      | _       | _      | (TBD)<br>100 | mA   | _       |

|                           |         | Conditions                    |       | Rating |            |          |         |

|---------------------------|---------|-------------------------------|-------|--------|------------|----------|---------|

| Item                      | Symbol  |                               | Min.  | Тур.   | Max.       | Unit     | Remarks |

|                           |         | Applicable pin: Vout2         |       |        | <b>/</b> \ |          |         |

| Output voltage 21         | IVOUT21 | Output voltage setting: 2.5 V | _     | _      | (TBD)      | mA       | _       |

|                           |         | VDD = (TBD) 3.6 V             |       |        | 80         |          |         |

|                           |         | Applicable pin: Vout2         |       |        | (====)     |          |         |

| Output voltage 22         | IVOUT22 | Output voltage setting: 2.0 V | _     | _      | (TBD)      | mA       | _       |

|                           |         | VDD = (TBD) 3.6 V             |       |        | 80         |          |         |

|                           |         | Applicable pin: Vout2         |       |        | (TDD)      |          |         |

| Output voltage 23         | IVOUT23 | Output voltage setting: 1.8 V | _     | _      | (TBD)      | mA       | _       |

|                           |         | VDD = (TBD) 3.6 V             |       |        | 80         |          |         |

| Lood atability 1          | ΔVOUT1  | (TBD)                         |       | (TDD)  | (TDD)      | >/       |         |

| Load stability 1          | ΔIOUT1  | (188)                         | _     | (TBD)  | (TBD)      | mV       | _       |

| Lood atability 2          | ΔVOUT2  | (TDD)                         |       | (TBD)  | (TBD)      | mV       | _       |

| Load stability 2          | ΔIOUT2  | (TBD)                         | _     |        |            |          |         |

| I/O voltage difference    | VDIF    | (TBD)                         |       | (TBD)  | (TBD)      |          |         |

| 1/O voltage difference    | VDIF    | (160)                         | _     | 0.2    | 0.3        | V        | _       |

| Output impedance          | RVOUT2  | (TBD)                         | (TBD) | (TBD)  | (TBD)      | Ω        | _       |

| Current consumption 1     | IOPR1   | VDD = 3.6 V, no load          | _     | (TBD)  | (TBD)      | μΑ       |         |

| Current consumption 1     |         | Normal mode                   |       | 100    | (100)      | μΑ       |         |

| Current consumption 2     | IOPR2   | VDD = 3.6 V, no load          | _     | (TBD)  | (TBD)      | μΑ       |         |

| Current consumption 2     | IUPR2   | Standby mode                  |       | 20     | (TBD)      | μΑ       |         |

| Resting current           | IQ      | VDD = 3.6 V                   |       | (TBD)  | μΑ         |          |         |

|                           | IQ      | Shut down mode                |       | 1.0    | μΑ         | _        | _       |

| Input stability 1         | ΔVOUT1  | (TBD)                         | _     | (TBD)  | (TBD)      | %/ V     |         |

| input stability 1         | ΔVDD    | (188)                         |       | (100)  | (TBD)      | 70/ V    |         |

| Input stability 2         | ΔVOUT2  | (TBD)                         | _     | (TBD)  | (TBD)      | %/ V     | _       |

| input stability 2         | ΔVDD    | , ,                           |       | (100)  | (100)      | 70/ V    |         |

| Power conversion          |         | VDD = 3.6 V                   | (TBD) | (TBD)  | (TBD)      |          |         |

| efficiency (Charge pump)  | Peff    | Normal mode                   | (100) | 85     | (155)      | %        | 3       |

| choichey (charge pamp)    |         | IVOUT2 = (TBD) mA             |       | 00     |            |          |         |

| Output voltage /          | ΔVOUT1  | IVOUT2 = (TBD) mA             | _     | (TBD)  | _          | ppm/°C   | _       |

| temperature coefficient 1 | ΔTopr   | –30 °C ≤ Topr ≤ 85°C          |       | (100)  | _          | ppiii/ C | _       |

| Output voltage /          | ΔVOUT2  | IVOUT2 = (TBD) mA             | _     | (TBD)  | _          | ppm/°C   | _       |

| temperature coefficient 2 | ∆Topr   | -30 °C ≤ Topr ≤ 85°C          |       | (155)  |            | 77, 0    |         |

<Note 1> Conditions on the operation mode, external parts constant, pins, etc. in case particular designations are not made are as follows:

Connection and parts constant : Standard connection 1, 10.1

XPOFF pin : XPOFF = HIGH (Normal mode)

XSTBY pin : XSTBY = HIGH (Normal mode)

<Note 2> The applicable pins are V01LV1, V01LV0, V02LV1, V02LV0, XSTBY, VSENS, VSEL, XPOFF and OSCIN.

<Note 3> The power conversion efficiency of the voltage dropping type charge pump only.

#### OLow voltage detection

In case particular designations are not made (Note 1):  $Ta = 25 \, ^{\circ}C$

| Itam                    | Cumbal  | Conditions                                  |       | Rating | 11    | Damanla     |         |

|-------------------------|---------|---------------------------------------------|-------|--------|-------|-------------|---------|

| Item                    | Symbol  | Conditions                                  | Min.  | Тур.   | Max.  | Unit        | Remarks |

| Detection voltage       | VDET    | VSEL pin = VDD* level                       | (TBD) | (TBD)  | (TBD) | V           |         |

| Detection voltage       | -VDET   | (Internal voltage setting fixed to the IC)  | 3.20  | 3.30   | 3.40  | · •         |         |

| Llyotoropio width       | VHVC    | VSEL pin = VDD* level                       | (TBD) | (TBD)  | (TBD) | V           |         |

| Hysteresis width        | VHYS    | (Internal voltage setting fixed to the IC)  |       | 0.09   |       | · •         |         |

| Reference detection     | \/5==.  | VSEL pin = Vss* level                       | (TBD) | (TBD)  | (TBD) | V           |         |

| voltage 1               | VREF1   | (External voltage setting to the VSENS pin) |       | 1.00   |       | · •         |         |

| Reference detection     | \/5===  | VSEL pin = Vss* level                       | (TBD) | (TBD)  | (TBD) | V           |         |

| voltage 2               | VREF2   | (External voltage setting to the VSENS pin) |       | 1.025  |       | · •         |         |

| NA:                     | VVDDL   | Topr = 25 °C                                | _     | _      | (TBD) |             |         |

| Min. operating voltage  |         | –30 °C ≤ Topr ≤ 85 °C                       | _     | _      | (TBD) | \ \ \ \ \ \ | 2       |

| Output current          | NADET   | (TDD)                                       | (TDD) |        |       | Л           |         |

| (Driver output pin)     | IVDET   | (TBD)                                       | (TBD) | _      | _     | mA          | _       |

| Off leak current        | IVDOFF  | (TRD)                                       |       |        | (TBD) |             |         |

| (Driver output pin)     | IVDOFF  | (TBD)                                       | _     | _      | 1.0   | μΑ          | _       |

| Tropofor dolovítimo     | TDLLI   |                                             |       |        | (TBD) |             | 2       |

| Transfer delay time     | TPLH    | _                                           | _     | _      | 100   | μs          | 3       |

| Detection voltage /     | A VIDET | VSEL pin = VDD* level                       |       |        |       |             |         |

| Detection voltage /     | Δ-VDET  | (Internal voltage setting fixed to the IC)  | _     | (TBD)  | _     | ppm/°C      | _       |

| temperature coefficient | ΔTopr   | -30 °C ≤ Topr ≤ 85 °C                       |       |        |       |             |         |

<Note 1> Conditions on the operation mode, external parts constant, pins, etc. in case particular designations are not made are as follows:

Connection and parts constant : Standard connection 1, 10.1

XPOFF pin : XPOFF = HIGH (Normal mode)

XSTBY pin : XSTBY = HIGH (Normal mode)

<Note 2> The supply voltage value where the output voltage becomes 0.1V or less. (TBD)

<Note 3> (TBD)

## OPower good detection

In case particular designations are not made (Note 1):  $Ta = 25 \, ^{\circ}C$

| ltom                                                        | Cumbal                              | Conditions                                                                  |               | Rating        | Unit          | Remarks |         |

|-------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------|---------------|---------------|---------------|---------|---------|

| Item                                                        | Symbol                              | Conditions                                                                  | Min.          | Тур.          | Max.          | Unit    | Remarks |

| Lower limit detection voltage 11                            | VDLPG11                             | Applicable pin = Vout1 Output voltage setting: 3.3 V Hysteresis width: 1%   | (TBD)<br>2.82 | (TBD)<br>2.91 | (TBD)<br>3.00 | V       | _       |

| Lower limit detection voltage 12                            | VDLPG12                             | Applicable pin = Voutant Output voltage setting: 2.9 V Hysteresis width: 1% | (TBD)<br>2.54 | (TBD)<br>2.62 | (TBD)<br>2.70 | V       | _       |

| Lower limit detection voltage 13                            | VDLPG13                             | Applicable pin = Vout1 Output voltage setting: 2.5 V Hysteresis width: 1%   | (TBD)<br>2.16 | (TBD)<br>2.23 | (TBD)<br>2.30 | V       | _       |

| Lower limit detection voltage 21                            | VDLPG21                             | Applicable pin = Vout2 Output voltage setting: 2.5 V Hysteresis width: 1%   | (TBD)<br>2.16 | (TBD)<br>2.23 | (TBD)<br>2.30 | V       | _       |

| Lower limit detection voltage 22                            | VDLPG22                             | Applicable pin = Vout2 Output voltage setting: 2.0 V Hysteresis width: 1%   | (TBD)<br>1.68 | (TBD)<br>1.74 | (TBD)<br>1.80 | V       | _       |

| Lower limit detection voltage 23                            | VDLPG23                             | Applicable pin = Vout2 Output voltage setting: 1.8 V Hysteresis width: 1%   | (TBD)<br>1.55 | (TBD)<br>1.60 | (TBD)<br>1.65 | V       | _       |

| PG output current (Driver output pin)                       | IPG                                 | (TBD)                                                                       | (TBD)         | (TBD)         | _             | mA      | _       |

| PG off leak current (Driver output pin)                     | IPGOFF                              | (TBD)                                                                       | _             | _             | (TBD)<br>1.0  | μΑ      | _       |

| Delay pin Threshold value voltage                           | VTCPG                               | VDD = (TBD)                                                                 | (TBD)         | (TBD)         | (TBD)         | V       | _       |

| CPG output current (Delay pin)                              | ICPG                                | (TBD)                                                                       | (TBD)         | (TBD)         | _             | mA      | _       |

| Lower limit detection voltage/<br>temperature coefficient 1 | $\frac{\Delta VDLPG1}{\Delta Topr}$ | Applicable pin: VouT1 -30 °C ≤ Topr ≤ 85 °C                                 | _             | (TBD)         | _             | ppm/°C  | _       |

| Lower limit detection voltage/<br>temperature coefficient 2 | ΔVDLPG21<br>ΔTopr                   | Applicable pin: Vout2 Output voltage setting: 2.0 V -30 °C ≤ Topr ≤ 85 °C   | _             | (TBD)         | _             | ppm/°C  | _       |

<Note 1> Conditions on the operation mode, external parts constant, pins, etc. in case particular designations are not made are as follows:

Connection and parts constant : Standard connection 1, 10.1

XPOFF pin : XPOFF = HIGH (Normal mode)

XSTBY pin : XSTBY = HIGH (Normal mode)

#### ■ REFERENCE EXTERNAL CONNECTION (AN EXAMPLE)

#### Standard connection 1

Recommended values for the external parts

ROSC = (TBD)  $\Omega$

Ra = (Make the detection voltage setting according to the formulae 7.4.2 and 7.4.4.)

Rb = (Make the detection voltage setting according to the formulae 7.4.2 and 7.4.4.)

$RS = RP = RVD = RPG = (TBD) 470 \text{ k}\Omega$

$CDD = (TBD) \mu F$

CDPG = (TBD)  $\mu$ F [(TBD) In case a delay time setting of 100ms is made.]

RDPG = (TBD) M $\Omega$  [(TBD) In case a delay time setting of 100ms is made.]

$CV01 = CV02 = 47 (TBD) \mu F$

$C1 = C2 = 0.47 (TBD) \mu F$

#### **■ DIMENSIONAL OUTLINE DRAWING**

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2001, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

#### **SEIKO EPSON CORPORATION**

ELECTRONIC DEVICES MARKETING DIVISION

IC Marketing & Engineering Group

ED International Marketing Department Europe & U.S.A

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5812 FAX: 042-587-5564

**ED International Marketing Department Asia**

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5110

■ EPSON Electronic Devices Website http://www.epson.co.jp/device/