## ■ DESCRIPTION

The gate driver LSI SED1794 is designed to drive an active matrix LCD panel.

It enables high-voltage operation, positive and negative output voltages and is compatible with various TFT-LCD panel driving methods.

By switching the number of outputs between 200 and 192, it is compatible with the XGA/SXGA panel (192 outputs) and the SVGA panel (200 outputs)

Thanks to its slim TCP shape, it enables a small-architected LCD module to be realized.

## ■ FEATURES

- Number of gate driving outputs: 200/192

- Super slim chip: Slim TCP

- Low voltage operation available: 2.7 V (min.)

- Output switching function available (200/192 outputs)

- Gate output voltage  $V_{ON} - V_{OFF1}$  amplitude: 40 V (max.)

- Output shift direction-pin selection.

- Output enable function

- Package to be shipped

Au bump chip: SED1794D0B

TCP: SED1794T\*\*

- This LSI is not designed to resist radiation or light.

# SED1794D0B

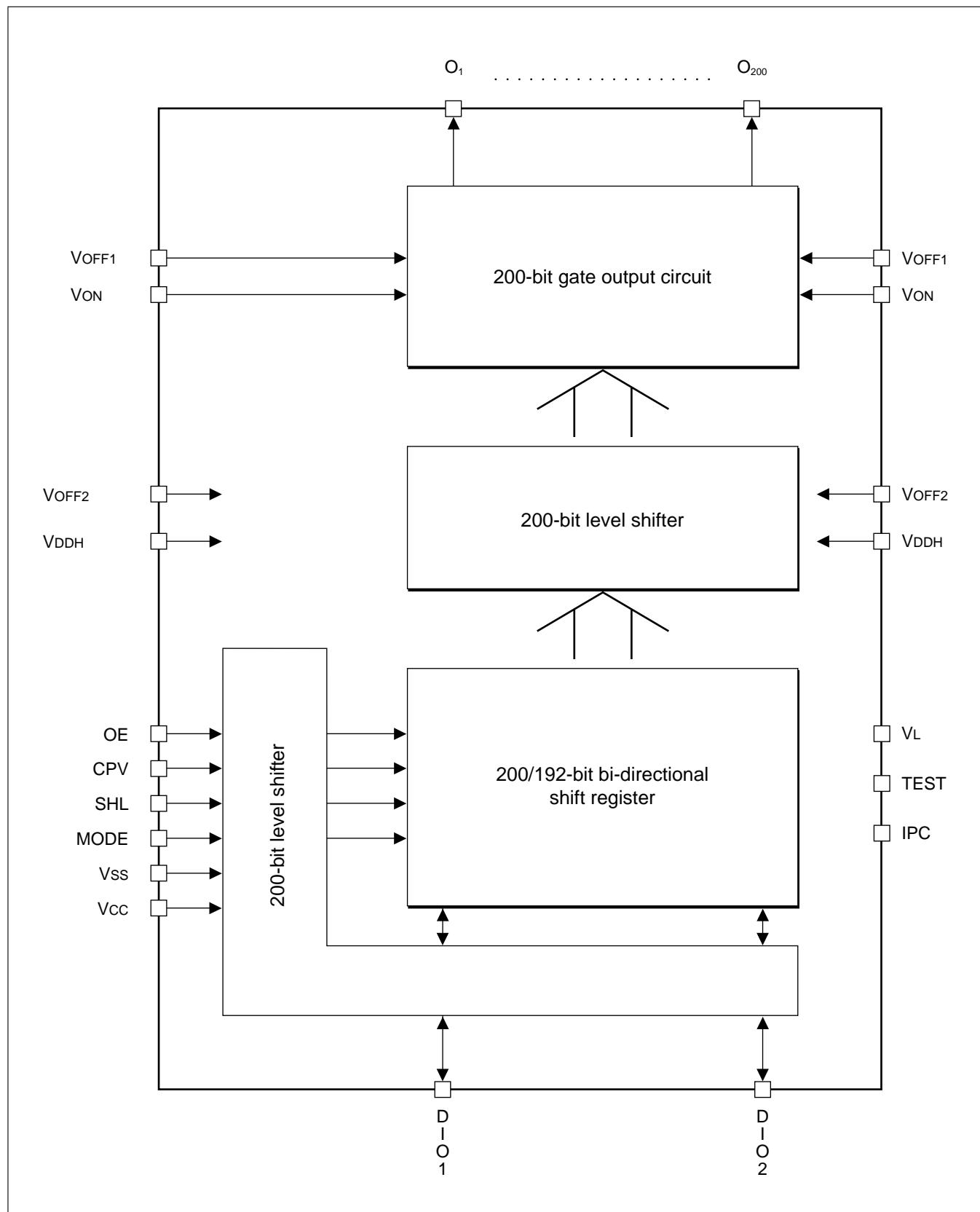

## ■ BLOCK DIAGRAM

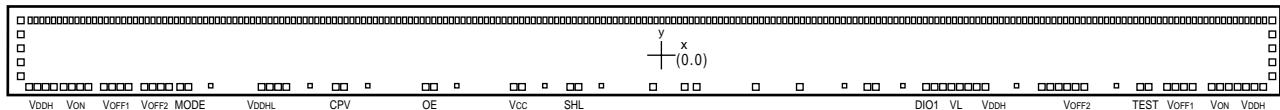

## ■ PAD LAYOUT

Chip size: 16.00 mm × 1.08 mm

Pad pitch: Output pin = 79  $\mu$ m (min.) \*1

Same input pin = 99  $\mu$ m (min.) \*2

Between input pins = 119  $\mu$ m (min.) \*2

Chip thickness: 625  $\mu$ m (typical)

Au bump specifications: SED1794D0B (reference)

(X direction) (Y direction)

Bump size A: 50.4  $\mu$ m × 80.0  $\mu$ m \*1

Bump size B: 77.6  $\mu$ m × 78.4  $\mu$ m \*2

Bump size C: 49.6  $\mu$ m × 56.0  $\mu$ m \*3

Bump size D: 50.4  $\mu$ m × 60.0  $\mu$ m \*4

Bump size E: 58.4  $\mu$ m × 59.2  $\mu$ m \*5

### Notes

1. Pad # 81 to 280.

2. Pad # 1 to 18, 20 to 23, 25, 26, 28, 29, 31, 32, 34, 35, 37 to 41, 43, 44, 46 to 53, 55 to 60 and 62 to 75.

3. Pad # 76 to 79 and 282 to 285.

4. Pad # 80 and 281.

5. Pad # 19, 24, 27, 30, 33, 36, 42, 45, 54 and 61.

# SED1794D0B

## ■ ABSOLUTE MAXIMUM RATINGS

(Vss = 0V)

| Parameter                     | Symbol                      | Rating            | Unit |

|-------------------------------|-----------------------------|-------------------|------|

| Supply voltage (1)            | Vcc                         | -0.5 to +7.0      | V    |

| Supply voltage (2)            | VDDH                        | -0.5 to +45.0     | V    |

| Supply voltage (3)            | VOH                         | -0.5 to VDDH +0.5 | V    |

| Supply voltage (4)            | VOFF1, VOFF2                | -23.0 to +0.5     | V    |

| Supply voltage (5)            | VDDH - VOFF2<br>VON - VOFF1 | -0.5 to +45.0     | V    |

| Input voltage                 | VIN                         | -0.5 to Vcc +0.5  | V    |

| Input current                 | IIN                         | ±10               | mA   |

| Output current                | Io                          | ±10               | mA   |

| Ambient operating temperature | Ta                          | -25 to +85        | °C   |

| Storing temperature           | Tstg2                       | -55 to +125       | °C   |

### Notes

1. All power supplies refer to Vss unless otherwise specified.

2. The LSI may permanently break if used outside the absolute maximum ratings shown above.

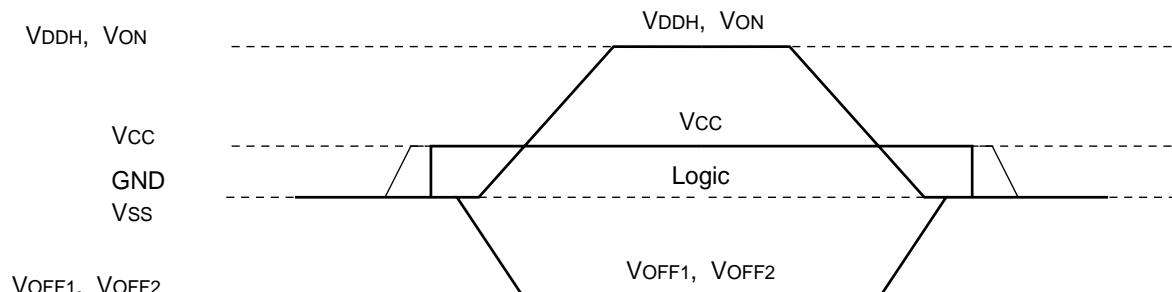

3. For voltages Vcc, Vss, VDDH, VON, VOFF1 and VOFF2, be sure to keep the condition of "VOFF2 ≤ VOFF1 ≤ Vss ≤ Vcc ≤ VDDH".

4. Turn Vcc, VOFF2/VOFF1 and VON/VDDH on in this order and follow the opposite order when turning the power off.

5. Never float Vcc while a voltage of 10 V or higher is applied to VDDH - VOFF2 and VON - VOFF1 or allow Vcc to go under 2.6 V, otherwise, an overcurrent may flow, disadvantageously affecting the LSI reliability.

## ■ RECOMMENDED OPERATING CONDITIONS

(Vss = 0 V)

| Parameter           | Symbol                      | Rating        | Unit |

|---------------------|-----------------------------|---------------|------|

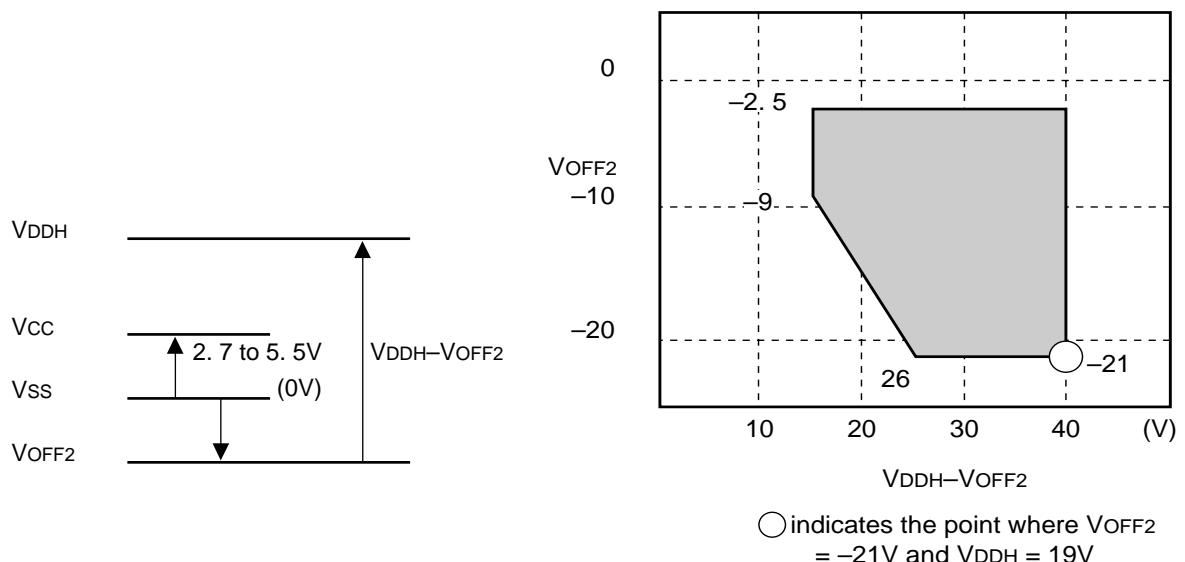

| Supply voltage (1)  | Vcc                         | 2.7 to 5.5    | V    |

| Supply voltage (2)  | VDDH                        | 10.0 to 40.0  | V    |

| Supply voltage (3)  | VON                         | 10.0 to 40.0  | V    |

| Supply voltage (4)  | VOFF1, VOFF2                | -21.0 to -2.5 | V    |

| Supply voltage (5)  | VDDH - VOFF2<br>VON - VOFF1 | 15 to 40.0    | V    |

| Operating frequency | fCPV                        | DC to 400     | kHz  |

### Notes

1. LSI operation is guaranteed within the recommended operating condition range.

2. Allowing for the power supply impedance in the mounted status, insert a bypass capacitor for noiseproof measures near the Vss, VOFF1 and VOFF2 pins.

3. Unless swinging the VOFF1 supply voltage, make the electric potential the same as that of VOFF2.

4. When swinging the VOFF1 supply voltage, keep the range within "VOFF2 ≤ VOFF1 ≤ VON - 15 V". In this case, the guaranteed output resistance and fall time ratings will differ.

- **Recommended operating voltage range**

The recommended operating voltage is based on the combination of the high-dielectric strength logic system power supply conditions and the logic system power supply conditions (the hatched portion in the figure below on the right).

## ■ ELECTRICAL CHARACTERISTICS

- **DC Characteristics**

Within the recommended operating voltage range when  $V_{SS} = 0$  V and  $T_a = -25$  to  $85^\circ\text{C}$  unless otherwise specified.

| Parameter               | Symbol    | Condition                       | Rating                             |      |                     | Units         | Pin used             |            |

|-------------------------|-----------|---------------------------------|------------------------------------|------|---------------------|---------------|----------------------|------------|

|                         |           |                                 | Min.                               | Typ. | Max.                |               |                      |            |

| “L” input voltage       | $V_{IL}$  | —                               | $V_{SS}$                           | —    | $0.3 \times V_{CC}$ | V             | All input pins       |            |

| “H” input voltage       | $V_{IH}$  | —                               | $0.7 \times V_{CC}$                | —    | $V_{CC}$            | V             | All input pins       |            |

| “L” output voltage      | $V_{OL}$  | $I_{OL} = 40 \mu\text{A}$       | $V_{SS}$                           | —    | $V_{SS} + 0.4$      |               | DIO1, 2              |            |

| “H” output voltage      | $V_{OH}$  | $I_{OH} = 40 \mu\text{A}$       | $V_{CC} - 0.4$                     | —    | $V_{CC}$            |               | DIO1, 2              |            |

| Output resistance       | $R_{ON}$  | $\Delta V_{ON} = 1.0 \text{ V}$ | $V_{ON} - V_{OFF1} = 40 \text{ V}$ | —    | 0.6                 | 0.9           | $\text{k}\Omega$     | O1 to O200 |

|                         |           |                                 | $V_{ON} - V_{OFF1} = 30 \text{ V}$ | —    | 0.7                 | 1.0           |                      |            |

|                         |           |                                 | $V_{ON} - V_{OFF1} = 15 \text{ V}$ | —    | 0.9                 | 1.5           |                      |            |

| Input leakage current   | $I_{LI}$  | —                               | -1.0                               | —    | 1.0                 | $\mu\text{A}$ | All input pins       |            |

| Input capacity          | $C_{IN}$  | $T_a = 25^\circ\text{C}$        | —                                  | —    | 15                  | pF            | All input pins       |            |

| Current consumption (1) | $I_{CC}$  | $f_{CPV} = 60 \text{ kHz}$      | —                                  | 5    | 10                  | $\mu\text{A}$ | $V_{CC}$             |            |

| Current consumption (2) | $I_{DDH}$ |                                 | —                                  | 380  | 990                 | $\mu\text{A}$ | $V_{DDH}$            |            |

| Current consumption (3) | $I_{OFF}$ |                                 | —                                  | -380 | -990                | $\mu\text{A}$ | $V_{OFF1}, V_{OFF2}$ |            |

# SED1794D0B

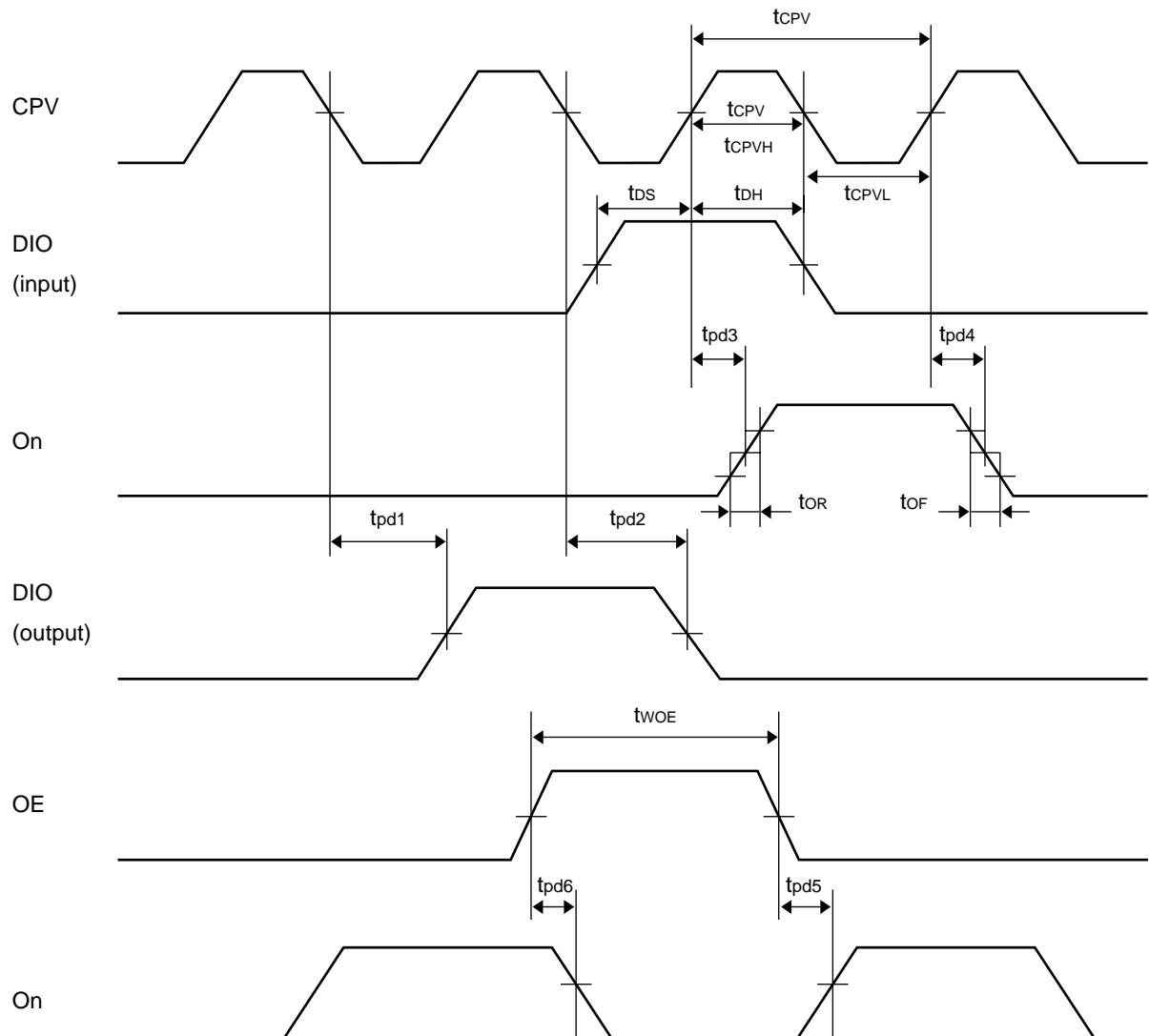

## ● AC Characteristics

### Notes

The input and output signal timings refer to 50% of the signal amplitude.

On output signal  $t_{OR}$  and  $t_{OF}$  refer to 10% and 90%.

- **Input Timing Characteristics**

Within the recommended operating voltage range when  $V_{SS} = 0$  V and  $T_a = -25$  to  $85^\circ\text{C}$  unless otherwise specified.

| Parameter                              | Symbol     | Condition                 | Min. | Max. | Unit          |

|----------------------------------------|------------|---------------------------|------|------|---------------|

| CPV cycle                              | $t_{CPV}$  | During cascade connection | 2.5  | —    | $\mu\text{s}$ |

| CPV high-level pulse width             | $t_{CPVH}$ | —                         | 400  | —    | ns            |

| CPV low-level pulse width              | $t_{CPVL}$ | —                         | 500  | —    | ns            |

| Data setup time                        | $t_{DS}$   | —                         | 100  | —    | ns            |

| Data hold time                         | $t_{DH}$   | —                         | 100  | —    | ns            |

| $\overline{OE}$ high-level pulse width | $t_{OE}$   | —                         | 700  | —    | ns            |

The logic input rise/fall times ( $t_r$  and  $t_f$ ) are specified at 30 ns or less.

- **Output Timing Characteristics**

Within the recommended operating voltage range when  $V_{SS} = 0$  V and  $T_a = -25$  to  $85^\circ\text{C}$  unless otherwise specified.

| Parameter                               | Symbol    | Condition                                                                                           | Min. | Max. | Unit |

|-----------------------------------------|-----------|-----------------------------------------------------------------------------------------------------|------|------|------|

| CPV to DIO output delay time            | $t_{pd1}$ | $CL = 20 \text{ pF}$                                                                                | —    | 600  | ns   |

|                                         | $t_{pd2}$ |                                                                                                     | —    | 600  | ns   |

| CPV to On output delay time             | $t_{pd3}$ | $CL = 220 \text{ pF}$<br>$V_{DDH} = V_{ON} = 20 \text{ V}$<br>$V_{OFF2} = V_{OFF1} = -20 \text{ V}$ | —    | 550  | ns   |

|                                         | $t_{pd4}$ |                                                                                                     | —    | 550  | ns   |

| $\overline{OE}$ to On output delay time | $t_{pd5}$ | $CL = 220 \text{ pF}$<br>$V_{DDH} = V_{ON} = 20 \text{ V}$<br>$V_{OFF2} = V_{OFF1} = -20 \text{ V}$ | —    | 550  | ns   |

|                                         | $t_{pd6}$ |                                                                                                     | —    | 550  | ns   |

| On output rise time                     | $t_{OR}$  | $CL = 220 \text{ pF}$<br>$V_{DDH} = V_{ON} = 20 \text{ V}$<br>$V_{OFF2} = V_{OFF1} = -20 \text{ V}$ | —    | 600  | ns   |

| On output fall time                     | $t_{OF}$  |                                                                                                     | —    | 600  | ns   |

# SED1794D0B

## NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

IBM is registered trademark of International Business Machines Corporation, U.S.A.

© Seiko Epson Corporation 1996 All right reserved.

## **SEIKO EPSON CORPORATION**

**ELECTRONIC DEVICE MARKETING DEPARTMENT**

**IC Marketing & Engineering Group**

421-8 Hino, Hino-shi, Tokyo 191, JAPAN

Phone: 0425-87-5816 FAX: 0425-87-5624

**International Marketing Department I (Europe, U.S.A.)**

421-8 Hino, Hino-shi, Tokyo 191, JAPAN

Phone: 0425-87-5812 FAX: 0425-87-5564

**International Marketing Department II (Asia)**

421-8 Hino, Hino-shi, Tokyo 191, JAPAN

Phone: 0425-87-5814 FAX: 0425-87-5110

Printed Feb. 1998 in Japan ®