# **IEEE1394 PHY LSI**

- IEEE1394-1995, 1394a-2000 compliant

- 400Mbps high-speed transfer supported

- 2 port

#### **■ DESCRIPTION**

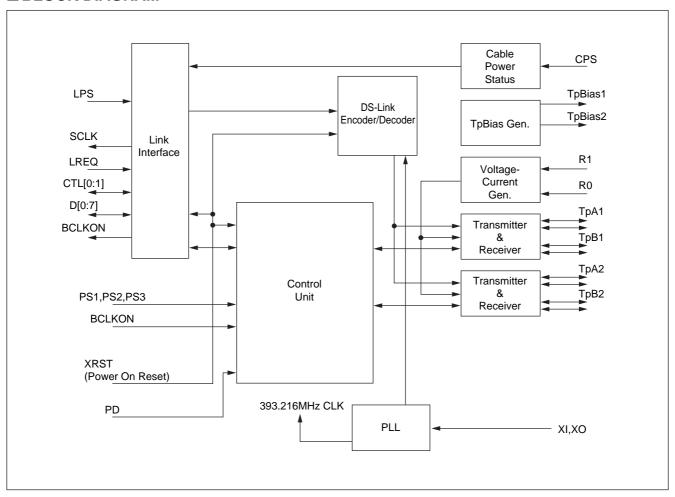

The S1R72900F00A is an IEEE 1394-1995 Standard and the IEEE 1394a-2000 Standard compliant physical layer.

The S1R72900F00A has two 1394 ports and supports transfer speeds of 400/200/100 Mbit/sec. It incorporates a 400 MHz PLL, a reference voltage generation circuit, a high-speed transceiver, a LINK layer interface, and a state machine circuit for a bus initialization and arbitration functions.

Making combination with our LINK layer S1R72801F00A, High speed 1394 transfer system can be easily realized.

#### **■ FEATURES**

- IEEE 1394-1995 Standard and IEEE 1394a-2000 Standard compliant

- Transfer speeds of S400 (393.216 Mbit/sec), S200 (196.608 Mbit/sec) and S100 (98.304 Mbit/sec) are supported.

- Incorporates on-chip 400 MHz PLL that enables data transmissions of S400/S200/S100 and SCLK output at 50 MHz.

- Independent TpBias output for each port

- The Cable Power Status function which detects decline in cable power supply is supported.

- Built-in PHY/LINK interface circuit.

- Both DC and AC PHY/LINK interface connection are supported.

- A oscillation circuit is built in.

- High-precision, small-amplitude-differential, high-speed transceiver

- Control state machine circuit for bus initialization, arbitration and port connection

- High-speed DS encoder

- 3.3 V single power supply

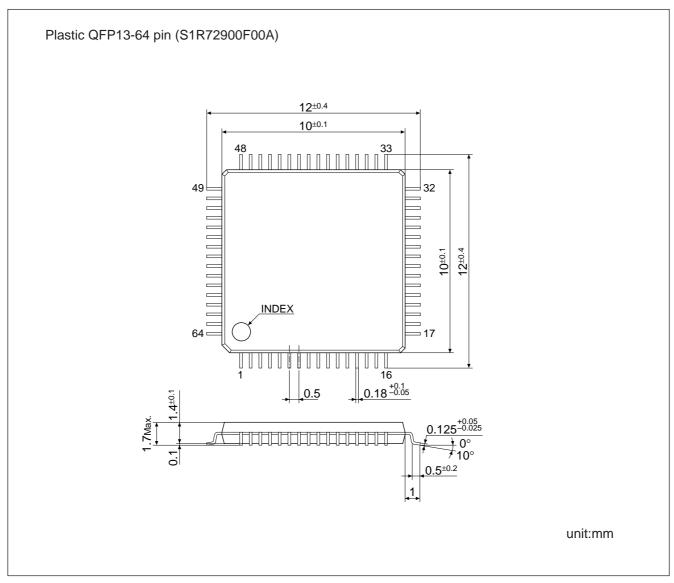

- Plastic QFP 13-64 pin

- Low power CMOS technology

- The S1R72900F00A is not designed to be radiation-proof.

## **■ BLOCK DIAGRAM**

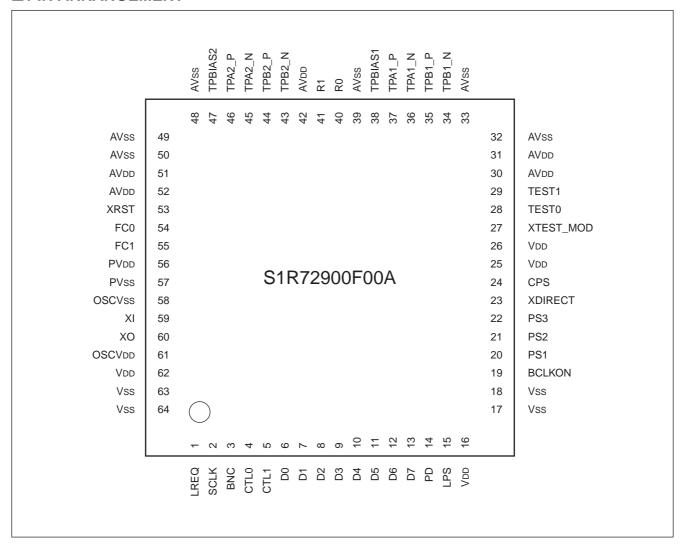

### **■ PIN ARRANGEMENT**

## **■ PIN DESCRIPTION**

| Pin Name          | Function                                                                                                                                                                                                                                                  | Pin No.             | Pin Type     | I/O |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|-----|

| AVDD              | Analog circuit power supply pin                                                                                                                                                                                                                           | 30,31,42,51,52      | Supply       | _   |

| AVss              | Analog circuit ground pin                                                                                                                                                                                                                                 | 32,33,39,48,49,50   | Supply       | _   |

| PVDD              | PLL circuit power supply pin                                                                                                                                                                                                                              | 56                  | Supply       | _   |

| PVss              | PLL circuit ground pin                                                                                                                                                                                                                                    | 57                  | Supply       | _   |

| VDD               | Digital circuit power supply pin                                                                                                                                                                                                                          | 16,25,26,62         | Supply       | _   |

| Vss               | Digital circuit ground pin                                                                                                                                                                                                                                | 17,18,63,64         | Supply       | _   |

| OSCVDD            | Oscillation circuit power supply pin                                                                                                                                                                                                                      | 61                  | Supply       | _   |

| OSCVss            | Oscillation circuit ground pin                                                                                                                                                                                                                            | 58                  | Supply       | _   |

| TPA1_P            | Port 1, TPA + input/output signal                                                                                                                                                                                                                         | 37                  | Differential | I/O |

| TPA1_N            | Port 1, TPA - input/output signal                                                                                                                                                                                                                         | 36                  | Differential | I/O |

| TPB1_P            | Port 1, TPB + input/output signal                                                                                                                                                                                                                         | 35                  | Differential | I/O |

| TPB1_N            | Port 1, TPB - input/output signal                                                                                                                                                                                                                         | 34                  | Differential | I/O |

| TPBIAS1           | Port 1, TP bias voltage supply pin                                                                                                                                                                                                                        | 38                  | Supply       | 0   |

| TPA2_P            | Port 2, TPA + input/output signal                                                                                                                                                                                                                         | 46                  | Differential | I/O |

| TPA2_N            | Port 2, TPA - input/output signal                                                                                                                                                                                                                         | 45                  | Differential | I/O |

| TPB2_P            | Port 2, TPB + input/output signal                                                                                                                                                                                                                         | 44                  | Differential | I/O |

| TPB2_N            | Port 2, TPB - input/output signal                                                                                                                                                                                                                         | 43                  | Differential | I/O |

| TPBIAS2           | Port 2, TP bias voltage supply pin                                                                                                                                                                                                                        | 47                  | Supply       | 0   |

| R1, R0            | 6.0kW (±1.0%) external basic resistance connection pin                                                                                                                                                                                                    | 41,40               | Analog       | 0   |

| PD                | Test pin                                                                                                                                                                                                                                                  | 14                  | Hysteresis   | ı   |

|                   | Connect it to Vss in normal operation.                                                                                                                                                                                                                    |                     | •            |     |

| BCLKON            | Bus Manager Contender / LINK-On Pin On hardware resetting, whether or not the bus manager function is employed is decided by the condition of this pin. On receiving the LINK-On packet, this signal is used to make the LINK layer controller IC active. | 19                  | CMOS         | I/O |

| LREQ              | Request signal from the LINK layer controller IC                                                                                                                                                                                                          | 1                   | Hysteresis   |     |

| CTL0, CTL1        | LINK interface interactive control signal                                                                                                                                                                                                                 | 4,5                 | Hysteresis   | I/O |

| D0 to D7          | LINK interface interactive data signal                                                                                                                                                                                                                    | 6,7,8,9,10,11,12,13 | Hysteresis   | 1/0 |

| SCLK              | 49.152 MHz system clock to the LINK layer controller IC                                                                                                                                                                                                   | 2                   | Tiysteresis  | 0   |

| LPS               | LINK power status pin                                                                                                                                                                                                                                     | 15                  | Hysteresis   | Ī   |

| Li S              | This signal monitors whether the LINK layer controller IC is active or not.                                                                                                                                                                               | 13                  | Trysteresis  | '   |

| PS1<br>PS2<br>PS3 | Power Status pin These pins set the power class bit of the Self-ID packet. PS1, PS2 and PS3 correspond to bits 21, 22 and 23 of the Self_ID packet.                                                                                                       | 20,21,22            | CMOS         | I   |

| XDIRECT           | This signal selects either DC or AC connection depending on whether or not the isolation barrier exists between PHY and LINK. Connect this pin to Vss for DC connection, and to VDD for AC connection.                                                    | 23                  | CMOS         | I   |

| XTEST_MODE        | Test pin Connect this pin to VDD in normal operation.                                                                                                                                                                                                     | 27                  | CMOS         | I   |

| XRST              | Reset pin This pin initializes S1R72900F00A when '0'. Set it to '1' in normal operation.                                                                                                                                                                  | 53                  | Hysteresis   | I   |

| CPS               | Cable Power Status detection pin Connect this pin to the cable power via the 240 $k\Omega$ resistance.                                                                                                                                                    | 24                  | Hysteresis   | I   |

EPSON

4

| Pin Name | Function                                               | Pin No. | Pin Type | I/O |

|----------|--------------------------------------------------------|---------|----------|-----|

| BNC      | This signal indicates the cable condition.             | 3       | CMOS     | 0   |

|          | It outputs HIGH when all ports do not receive the bias |         |          |     |

|          | voltage from the matched node.                         |         |          |     |

| FC0      | Filter connection pin for PLL                          | 54      | Analog   | 0   |

|          | S1R72900F00A does not require an external capacitor.   |         |          |     |

|          | Do not connect anything to this pin.                   |         |          |     |

| FC1      | Filter connection pin for PLL                          | 55      | Analog   | 0   |

|          | S1R72900F00A does not require an external capacitor.   |         |          |     |

|          | Do not connect anything to this pin.                   |         |          |     |

| XI       | Crystal oscillator 24.576 MHz input                    | 59      |          |     |

| XO       | Crystal oscillator 24.576 MHz input                    | 60      |          |     |

| TEST0    | Test pin                                               | 28      | CMOS     | I   |

|          | Connect it to Vss in normal operation.                 |         |          |     |

| TEST1    | Test pin                                               | 29      | CMOS     | I   |

|          | Connect it to Vss in normal operation.                 |         |          |     |

## **■ DIMENSIONAL OUTLINE DRAWING**

THIS PAGE IS BLANK.

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2001, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

#### **SEIKO EPSON CORPORATION**

**ELECTRONIC DEVICES MARKETING DIVISION**

IC Marketing & Engineering Group

**ED International Marketing Department Europe, U.S.A**

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5812 FAX: 042-587-5564

**ED International Marketing Department ASIA**

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5110

■ EPSON Electronic Devices Website http://www.epson.co.jp/device/