# S3090

## DEVICE SPECIFICATION DATA SHEET

## 10 Gbps Transimpedance Amplifier

## **FEATURES**

- 10 GHz Bandwidth

- 1.4 kΩ Differential Transimpedance

- 5.2 V Power Supply

- 15 pA/rt Hz Typical Noise Current Density

- 2.2 mA p-p Max Input Current

- · Low Pulse Width Distortion

- Source Terminated Differential Outputs

- · Adjustable Output Offset

- Maximum Die Size: 1.946 mm by 1.946 mm

## **APPLICATIONS**

- SONET OC-192

- Fiber Optic Data Links

- HDTV/CATV Fiber Links

- Fiber Optics Access Boxes

- 10 G Ethernet Fiber Links

## **GENERAL DESCRIPTION**

The S3090 is a high-speed transimpedance amplifier for 10 Gbps applications. Input currents as high 2.2 mA can be amplified with low duty cycle distortion. The low input noise allows signals down to 19  $\mu$ A (peak) to be detected with a signal to noise ratio of 21.5 dB (allows for BER < 1E-9).

The outputs are voltage limited to 1400 mV, differential, in order to allow a wide input dynamic range without exceeding the input voltage range of the limiting amplifier.

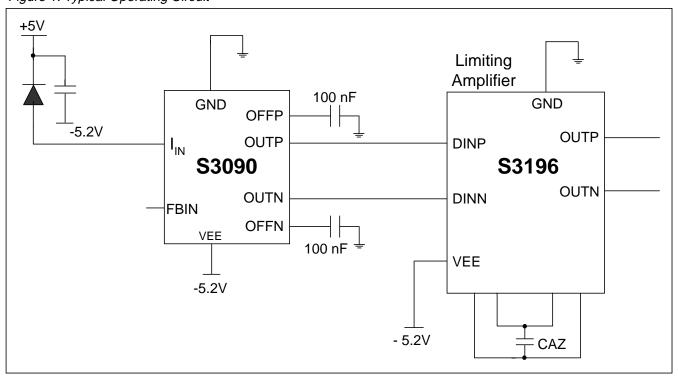

Also, the offset between the data outputs is adjustable, in order to provide adjustable decision threshold in the limiting amplifier. Figure 1 shows a typical application.

Figure 1. Typical Operating Circuit

## **DETAILED DESCRIPTION**

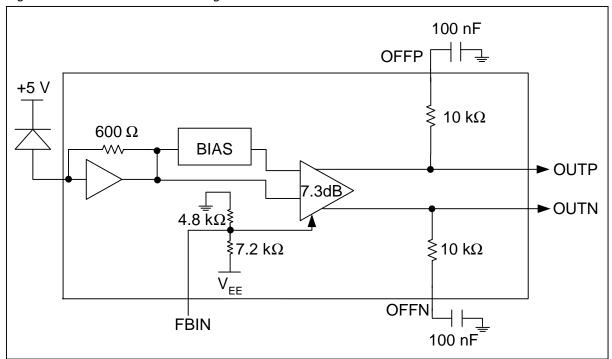

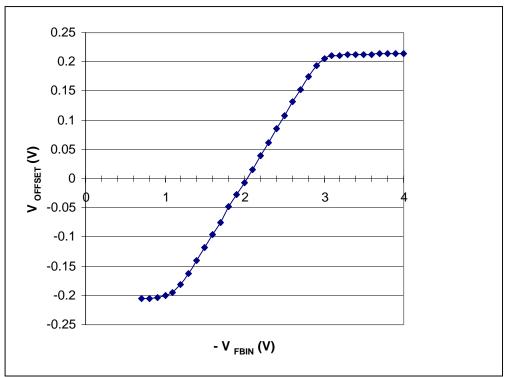

Figure 2 depicts the block diagram of the S3090 transimpedance amplifier. The amplifier circuitry consists of a transimpedance stage and an output stage with a gain of 7.3 dB. The output is linear for inputs of up to 1000  $\mu$ A (peak). For higher inputs the output will limit at a level of 1400 mV, differential.

The S3090 provides a feature which enables the adjustment of the decision threshold at the input of the limiting amplifier by allowing the adjustment of the DC

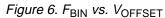

offset between the two complimentary data outputs, OUTP and OUTN. The OFFP and OFFN outputs provide the DC levels for the data outputs OUTP and OUTN. They can be used as inputs to a circuit that would control the DC offset, V<sub>OFFSET</sub>, between OUTP and OUTN. This offset can be controlled by adjusting a DC voltage at the FBIN input. OFFP and OFFN should be connected to ground through capacitors. A plot of FBIN vs. V<sub>OFFSET</sub> is provided in Figure 6.

Figure 2. S3090 Detailed Block Diagram

## **DEVICE SPECIFICATION DATA SHEET**

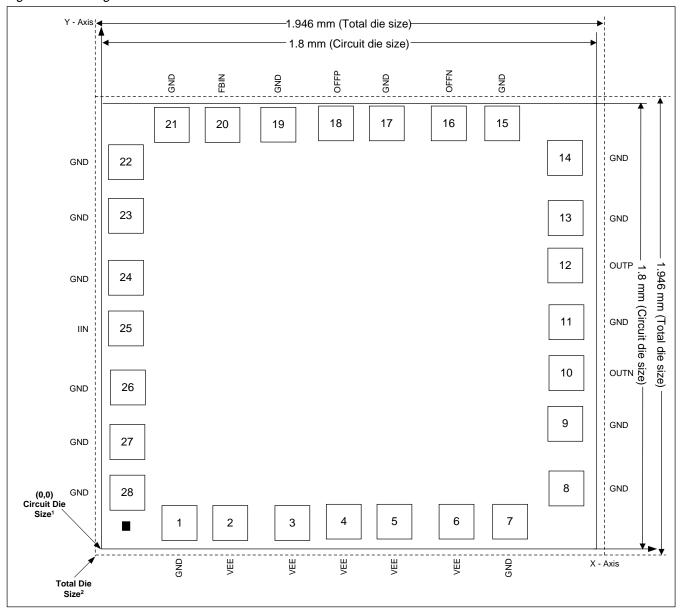

Table 1. Pad Assignment and Description

| Pin Name        | I/O | Pad #                                                                                          | Coordinate (X,Y) <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                               | Description                                                                                                   |

|-----------------|-----|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| GND             | S   | 1<br>7<br>8<br>9<br>11<br>13<br>14<br>15<br>17<br>19<br>21<br>22<br>23<br>24<br>26<br>27<br>28 | [292.175, 88.925]<br>[1485.375, 88.925]<br>[1689.075, 253.000]<br>[1689.075, 519.125]<br>[1689.075, 889.050]<br>[1689.075, 1258.975]<br>[1689.075, 1524.975]<br>[1485.375, 1689.075]<br>[1087.650, 1689.075]<br>[689.925, 1689.075]<br>[292.175, 1689.075]<br>[99.075, 1524.975]<br>[99.075, 1524.975]<br>[99.075, 1326.100]<br>[99.075, 650.725]<br>[99.075, 451.850]<br>[99.075, 252.975] | Ground                                                                                                        |

| VEE             | S   | 2<br>3<br>4<br>5<br>6                                                                          | [491.050, 88.925]<br>[689.925, 88.925]<br>[888.800, 88.925]<br>[1087.650, 88.925]<br>[1286.500, 88.925]                                                                                                                                                                                                                                                                                     | Negative power supply                                                                                         |

| I <sub>IN</sub> | I   | 25                                                                                             | [99.075, 889.050]                                                                                                                                                                                                                                                                                                                                                                           | PIN diode input                                                                                               |

| OUTP            | 0   | 12                                                                                             | [1689.075, 1087.925]                                                                                                                                                                                                                                                                                                                                                                        | Positive output                                                                                               |

| OUTN            | 0   | 10                                                                                             | [1689.075, 690.175]                                                                                                                                                                                                                                                                                                                                                                         | Negative output                                                                                               |

| OFFP            | 0   | 18                                                                                             | [888.800, 1689.075]                                                                                                                                                                                                                                                                                                                                                                         | DC level of OUTP. This pad should be connected to ground through a 100 nF capacitor.                          |

| OFFN            | 0   | 16                                                                                             | [1286.500, 1689.075]                                                                                                                                                                                                                                                                                                                                                                        | DC level of OUTN. This pad should be connected to ground through a 100 nF capacitor.                          |

| FBIN            | I   | 20                                                                                             | [491.050, 1689.075]                                                                                                                                                                                                                                                                                                                                                                         | A DC voltage at this pin controls the offset between OUTP and OUTN2V corresponds to no offset. (See Table 5). |

- 1. The coordinates are in  $\mu m$  from the lower left corner of the circuit die to the center of the pad.

- Total pad size is 94 μm x 94 μm. The size of the exposed area is 80 μm x 80 μm.

The back of the die is not metallized and should be connected to V<sub>EE</sub> or left electrically unconnected.

## Die Issues

Die level test only. Test includes wafer probe, low frequency functional test, parametric test on I/O and power pins, and visual inspection.

Figure 3. Bonding Pad Location

Note: Die thickness is 0.254 mm (10 mils).

- 1. The circuit die size is the smallest possible size of the die. The lower left-hand corner of the circuit die is the origin of the xy-coordinate system. Pad coordinates indicated in Table 1 are measured from this origin to the pad's center.

- 2. The total die size is the largest possible size of the die. It includes a splicing area around the circuit die. The actual size of any given die may vary in size from the minimum (circuit die) size to the maximum (total die) size.

### **DEVICE SPECIFICATION DATA SHEET**

The following are the absolute maximum stress ratings for the S3090 device. Stresses beyond those listed may cause permanent damage to the device. Absolute maximum ratings are stress ratings only and operation of the device at the maximums stated or any other

conditions beyond those indicated in the "Recommended Operating Conditions" of the document are not inferred. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Recommended Operating Conditions

| Parameter      | Min  | Тур  | Max  | Units | Description                        |

|----------------|------|------|------|-------|------------------------------------|

| Tj             | -20  |      | 100  | °C    | Junction temperature under bias    |

| T <sub>A</sub> | -40  |      | 85   | °C    | Ambient temperature under bias     |

| VEE            | -4.9 | -5.2 | -5.5 | V     | Voltage on VEE with respect to GND |

Table 3. Absolute Maximum Ratings

| Parameter                 | Min | Тур | Max | Units |

|---------------------------|-----|-----|-----|-------|

| Storage Temperature Range | -55 |     | 150 | °C    |

| Power Supply VEE          | -6  |     | 0.5 | V     |

#### **Electrostatic Discharge (ESD) Ratings**

The S3090 is rated to the following ESD voltages based on the human body model:

Table 4. AC Electrical Characteristics

| Parameter            | Description                          | Min  | Тур       | Max       | Units          | Conditions                                                        |

|----------------------|--------------------------------------|------|-----------|-----------|----------------|-------------------------------------------------------------------|

| Z <sub>T</sub>       | AC Transimpedance                    | 550  | 700       | 825       | V/A            | Single-ended, 50 $\Omega$ load                                    |

| Z <sub>T</sub>       | AC Transimpedance                    | 1100 | 1400      | 1650      | V/A            | Differential, 100 $\Omega$ load, line to line                     |

| BW <sub>-3dB</sub>   | -3 dB Bandwidth                      | 7.5  | 10        | 13        | GHz            | See Note 1.                                                       |

| BW <sub>LF</sub>     | Low Frequency -3dB Cutoff            |      | 25        | 40        | kHz            |                                                                   |

| I <sub>PK</sub>      | Peak Input Current                   |      |           | 2.2       | mA             |                                                                   |

| I <sub>ND</sub>      | Input Noise Current Density          |      | 15        | 18        | pA/rt Hz       | 0 - 11 GHz                                                        |

| I <sub>NOISE</sub>   | Input Noise Current Power            |      | 2.5E - 12 | 3.5E - 12 | A <sup>2</sup> | 0 - 11 GHz                                                        |

| V <sub>OD</sub>      | Maximum Output Swing                 |      |           | 1400      | mV             | Peak to peak differential. 100 $\Omega$ line-to-line termination. |

| V <sub>OS</sub>      | Maximum Output Swing                 |      |           | 700       | mV             | Single-ended, 50 $\Omega$ line termination to GND.                |

| I <sub>IN, LIM</sub> | Input Current at which Output Limits |      | 1000      |           | μΑ             |                                                                   |

| R <sub>OUT</sub>     | Output Impedance                     | 42   | 50        | 58        | Ω              | 0 - 11 GHz, single ended                                          |

<sup>1.</sup> All pins are rated at or above 400 V, except the IIN pin. The IIN pin is rated at 100 V.

Table 4. AC Electrical Characteristics (Continued)

| Parameter       | Description                                         | Min  | Тур | Max  | Units | Conditions                                   |

|-----------------|-----------------------------------------------------|------|-----|------|-------|----------------------------------------------|

| S <sub>22</sub> | Output Reflection Coefficient                       |      |     | -10  | dB    | 1 - 7 GHz, < 800 pH bond wire inductance     |

| Ripple          | Output Ripple                                       | -0.5 | 0   | 0.5  | dB    | 1 - 8 GHz. See Note 1.                       |

| Group<br>Delay  | Group Delay Deviation<br>(100 MHz to 8 GHz)         |      |     | 20   | ps    | Input Current = 10 - 1000 μA.<br>See Note 1. |

| Group<br>Delay  | Group Delay Deviation (8 GHz to F <sub>-3dB</sub> ) |      |     | 40   | ps    | Input Current = 10 - 1000 μA.<br>See Note 1. |

| Peak            | Peaking                                             |      |     | 1.2  | dB    | 25 kHz to 11 GHz. See Note 1.                |

| JT              | Total Jitter (Pk to Pk)<br>(At 1E-12 BER)           |      |     | 0.12 | UI    | I <sub>IN</sub> = 2.2 mA                     |

Note 1. Assuming a total input bond wire inductance (between the photodiode and IIN pin) of 0.7 nH and photodiode capacitance of 0.2 pF.

Table 5. Output Offset Adjustment

| Parameter                | Description                                                         | Min | Тур  | Max | Units | Conditions                    |

|--------------------------|---------------------------------------------------------------------|-----|------|-----|-------|-------------------------------|

| V <sub>OFFSET</sub>      | V <sub>DOUTP</sub> - V <sub>DOUTN</sub>                             | 200 |      |     | mV    | DC Voltage                    |

| V <sub>OFFSET, NEG</sub> | V <sub>DOUTN</sub> - V <sub>DOUTP</sub>                             | 200 |      |     | mV    | DC Voltage                    |

| V <sub>FBIN</sub> , MIN  | V <sub>FBIN</sub> corresponding to max positive V <sub>OFFSET</sub> |     | -3   |     | V     | V <sub>OFFSET</sub> = +200 mV |

| V <sub>FBIN,NOM</sub>    | V <sub>FBIN</sub> corresponding to zero V <sub>OFFSET</sub>         |     | -2.0 |     | V     | V <sub>OFFSET</sub> = 0       |

| V <sub>FBIN</sub> , MAX  | V <sub>FBIN</sub> corresponding to max negative V <sub>OFFSET</sub> |     | -1   |     | V     | V <sub>OFFSET</sub> = -200 mV |

| R <sub>FBIN</sub>        | FBIN Input Impedance                                                |     | 2.88 |     | kΩ    |                               |

Table 6. DC Characteristics

| Parameter           | Description                   | Min       | Тур                  | Max       | Units | Conditions                             |

|---------------------|-------------------------------|-----------|----------------------|-----------|-------|----------------------------------------|

| I <sub>EE</sub>     | Supply Current                |           | 80                   | 90        | mA    |                                        |

| V <sub>INBIAS</sub> | Input Bias Voltage            |           | V <sub>EE</sub> +1.7 |           | V     |                                        |

| V <sub>OCM</sub>    | Common Mode Output<br>Voltage | Gnd - 0.7 | GND - 0.45           | Gnd - 0.2 | V     | 50 $\Omega$ line termination to GND.   |

| V <sub>OCM</sub>    | Common Mode Output<br>Voltage | Gnd - 1.4 | GND - 0.9            | Gnd - 0.4 | V     | 100 $\Omega$ line-to-line termination. |

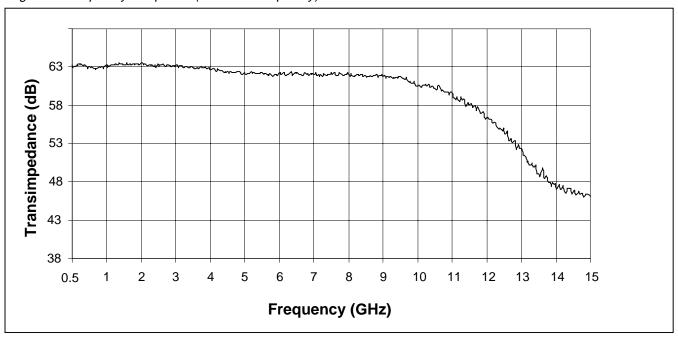

## **Typical Operating Characteristics**

Figure 4. Frequency Response (Gain vs. Frequency)

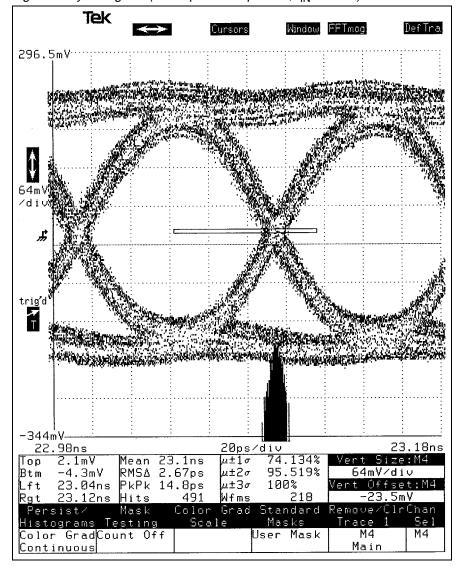

Figure 5. Eye Diagram (10 Gbps PRBS pattern,  $I_{IN} = 1 \text{ mA}$ )

Figure 7. Output Voltage vs. Input Current

#### **DEVICE SPECIFICATION DATA SHEET**

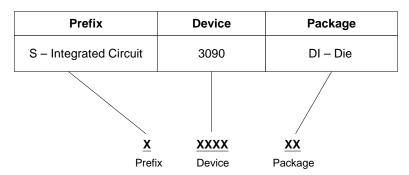

## **Ordering Information**

Applied Micro Circuits Corporation 6290 Sequence Dr., San Diego, CA 92121

Phone: (858) 450-9333 — (800) 755-2622 — Fax: (858) 450-9885 http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation. Copyright © 2000 Applied Micro Circuits Corporation.

D54/R221