### **APPLICATION NOTES AND REFERENCE DIAGRAMS**

S2060

#### **FEATURES**

- · Operating rate

- 1250 MHz (Gigabit Ethernet) line rates

- Half and full VCO output Rates

- Functionally compliant IEEE 802.3z Gigabit Ethernet Standard

- Transmitter incorporating phase-locked loop (PLL) clock synthesis from low speed reference

- · Receiver PLL provides clock and data recovery

- 10 bit parallel TTL compatible interface

- Low-jitter serial LVPECL compatible interface

- Local Loopback

- · Continuous downstream clocking from receiver

- Drives 30m of Twinax cable directly

#### **APPLICATIONS**

- Workstation

- · Frame buffer

- · Switched networks

- · Data broadcast environments

- Proprietary extended backplanes

#### **GENERAL DESCRIPTION**

The S2060 transmitter and receiver chip facilitates high-speed serial transmission of data over fiber optic, coax, or twinax interfaces. The device conforms to the requirements of the IEEE 802.3z Gigabit Ethernet specification, and runs at 1250.0 Mbps data rates with an associated 10-bit data word.

The chip provides parallel-to-serial and serial-to-parallel conversion, clock generation/recovery, and framing for block encoded data. The on-chip transmit PLL synthesizes the high-speed clock from a low-speed reference. The on-chip receive PLL performs clock recovery and data re-timing on the serial bit stream. The transmitter and receiver each support differential LVPECL compatible I/O for copper or fiber optic component interfaces with excellent signal integrity. Local loopback mode allows for system diagnostics. The chip requires a 3.3V power supply.

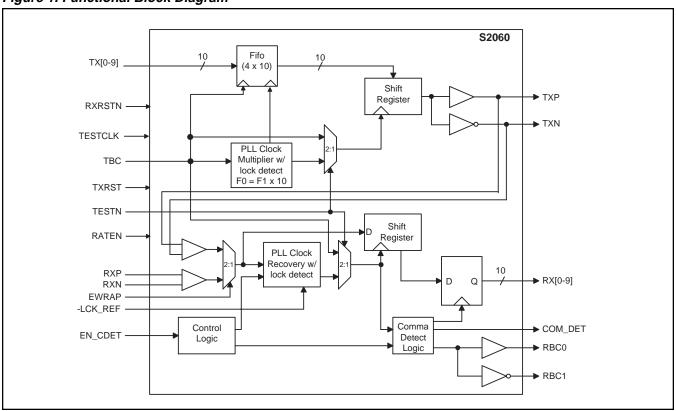

The S2060 can be used for a variety of applications including Gigabit Ethernet, serial backplanes, and proprietary point to point links. Figure 1 shows the functional block diagram.

Figure 1. Functional Block Diagram

July 8, 1999 1

#### **Power and Ground Connections**

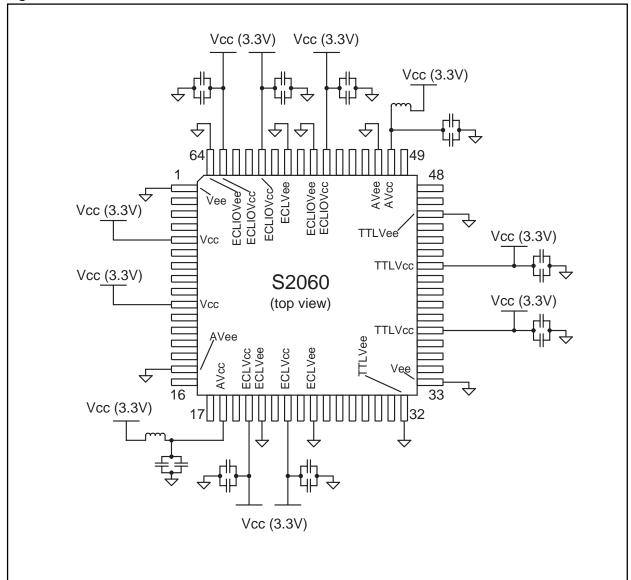

Recommended power and ground connections are shown below in Figure 2 and Table 1.

Figure 2. Power and Ground Connections

2 July 8, 1999

# APPLICATION NOTES AND REFERENCE DIAGRAMS

S2060

Table 1. Power and Ground Application Information

| Function   | Pinout<br><b>Name</b> | Instructions                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG     | AVCC                  | Connect to low noise or filtered 3.3V supply through a ferrite bead (600 $\Omega$ at 100 MHz: Murrata BLM31B601S or equivalent). Provide dual local HF bypassing to AVEE (0.1 $\mu$ f, 100 pf) for low inductance and resistance. A single low inductance 0.1 $\mu$ f capacitor can be substituted for the pair (Vishay VJ0612 or equivalent, < 0.5 nH max inductance). |

|            | AVEE                  | Connect to ground plane.                                                                                                                                                                                                                                                                                                                                                |

| LVPECL I/O | ECLIOVCC              | Provide low impedance connection to 3.3V. Provide dual local bypassing to GND plane (0.1 $\mu$ f and 100 pf in parallel, or a single low inductance Vishay VJ0612 or equivalent 0.1 $\mu$ f cap).                                                                                                                                                                       |

|            | ECLIOVEE              | Connect to ground plane.                                                                                                                                                                                                                                                                                                                                                |

| CORE       | ECLVCC                | Provide low impedance connection to 3.3V. Provide dual local bypassing to GND plane (0.1 $\mu$ f and 100 pf in parallel, or a single low inductance Vishay VJ0612 or equivalent 0.1 $\mu$ f cap).                                                                                                                                                                       |

|            | ECLVEE                | Connect to ground plane.                                                                                                                                                                                                                                                                                                                                                |

| TTL I/O    | TTLVCC                | Provide low impedance connection to 3.3V. Provide dual local bypassing to GND plane (0.1 $\mu$ f and 100 pf in parallel, or a single low inductance Vishay VJ0612 or equivalent 0.1 $\mu$ f cap).                                                                                                                                                                       |

|            | TTLVEE                | Connect to ground plane.                                                                                                                                                                                                                                                                                                                                                |

July 8, 1999 3

#### **Serial Input/Output Connections**

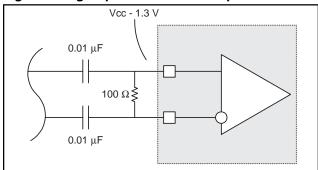

Figures 3 shows the basic coupling termination scheme for the S2060 high-speed serial inputs. The serial inputs are internally dc biased to Vcc -1.3 V. External connections include 0.01 µF AC coupling capacitors and a line-line termination resistor. The termination resistor is required for lines lengths > ~1 cm, which exhibit transmission line effects at these high speeds. The termination must match the characteristic impedance of the differential lines to minimize signal reflections. The  $100\Omega$  value shown assumes characteristic line impedance of  $50\Omega$  (if the lines are 75 $\Omega$ , the line-to-line termination resistor should be 150 $\Omega$ ). The AC coupling capacitors allow the dc bias point to be set internally by the input stage. The dc bias can be set externally by implementing a resistor divider network on each line, but this is not recommended since it increases the part count and does not provide performance improvement.

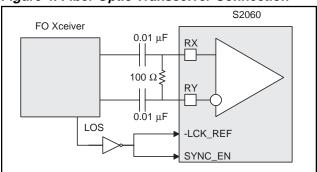

The biasing scheme in Figure 3 should be used for copper interface applications – the pull-up resistor utilized with the S2052 should not be included in the S2060 circuit. FO transceivers require a different approach. When the fiber is disengaged, the noise from the FO device is often nearly as large in amplitude as a good signal. Figure 4 shows a connection to a fiber optic transceiver. The Loss-of-Signal output of the FO transceiver drives the SYNC\_EN and – LCK\_REF inputs of the S2060. This insures that the PLL will lock to the reference clock and the RBC output clocks will not stretch due to false comma characters. Alternately, the ASIC controller may govern these inputs.

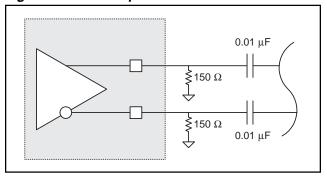

Figure 5 shows the connection diagram for high-speed serial outputs. The  $150\Omega$  pull-down resistors set the drive current of the output stage. The value of  $150\Omega$  provides compatibility with competing products from other manufacturers. As a CMOS design, the S2060 will perform well with pull-down resistor values as large as 1.5K  $\Omega,$  which would reduce power consumption on the board. The output stage can drive 30m of twinax cable directly.

Figure 3. High Speed Differential Inputs

Figure 4. Fiber Optic Transceiver Connection

Figure 5. Serial Output Load

4 July 8, 1999

#### **Reference Designs**

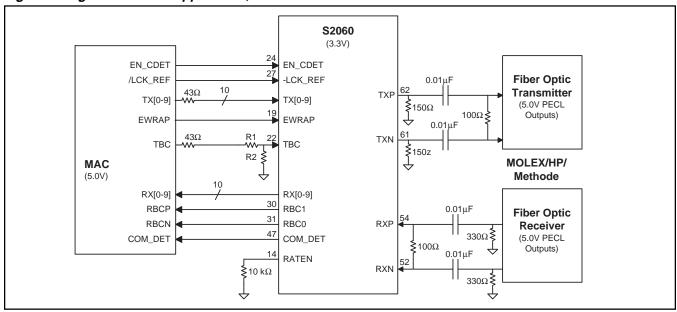

Figure 6 shows a reference design with a 5V MAC. The TBC input to the S2060 will not tolerate signals above the VCC voltage rail, so it may be necessary to reduce the voltage of the TBC output of the MAC: if the output levels are CMOS, set R1 = 180 ohms, R2 = 330 ohms. If the levels are out of the MAC are TTL, R1 should be zero ohms and R2 should be removed. The 43 ohm series resistors on the TX and TBC outputs of the MAC provide 50 ohm termination

(43 ohm + ~7 ohm output impedance) for any reflections coming from the S2060 inputs. These resistors should be placed as close to the MAC as possible.

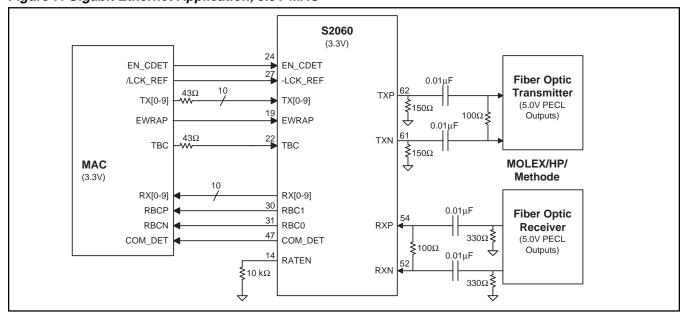

Figure 7 shows the 3.3V reference design. The difference between the 5.0V and 3.3V application is the removal of R1 and R2.

Termination into the Fiber Optic transmitter is shown as 100 ohms line-line. Refer to the data sheet or application notes of your FO transmitter of choice for input connection recommendations.

Figure 6. Gigabit Ethernet Application, 5.0V MAC

Figure 7. Gigabit Ethernet Application, 3.3V MAC

July 8, 1999 5

#### S2060

## **APPLICATION NOTES AND REFERENCE DIAGRAMS**

#### S2070 Compatibility with Existing Products

The S2060 is the CMOS equivalent of the S2052. The bulleted items below outline the functional differences between the two parts.

- S2060 typical power dissipation is 660 mW. S2052 dissipates 800 mW.

- S2060 serial input bias voltage is VCC-1.3V (standard LVPECL). This complies with both HP and Vitesse.

S2052 serial input bias voltage is VCC-0.65.

- With the recommended AC coupled input connection, the bias voltage is irrelevant (see previous section on serial input/output connections); however, designers who wish to set the bias voltage externally should take note of the difference in bias voltage.

- S2060 serial input should not have a pull-up offset resistor. S2052 pull-up resistor value is  $10k\Omega$  (for applications where input data goes away).

- When EWRAP is active, TXP/N outputs are static (High). This complies with the S2052. HP holds both pins High. Vitesse holds the P output High and the N output Low.

- S2060 pin 14 is rate selection pin, held low for normal (full rate) operation. S2052 pin 14 is ground.

- S2060 pin 27 (-LCKREF) can be either floated or held high to lock to input data (normal operation). S2052 pin 27 (-LCKREF) must be held high to lock to input data.

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (858) 450-9333 • (800) 755-2622 • Fax: (858) 450-9885 http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1999 Applied Micro Circuits Corporation

6 July 8, 1999