# SCANSTA111 Enhanced SCAN bridge Multidrop Addressable IEEE 1149.1 (JTAG) Port

# **General Description**

The SCANSTA111 extends the IEEE Std. 1149.1 test bus into a multidrop test bus environment. The advantage of a multidrop approach over a single serial scan chain is improved test throughput and the ability to remove a board from the system and retain test access to the remaining modules. Each SCANSTA111 supports up to 3 local IEEE1149.1 scan rings which can be accessed individually or combined serially. Addressing is accomplished by loading the instruction register with a value matching that of the Slot inputs. Backplane and inter-board testing can easily be accomplished by parking the local TAP Controllers in one of the stable TAP Controller states via a Park instruction. The 32-bit TCK counter enables built in self test operations to be performed on one port while other scan chains are simultaneously tested.

#### **Features**

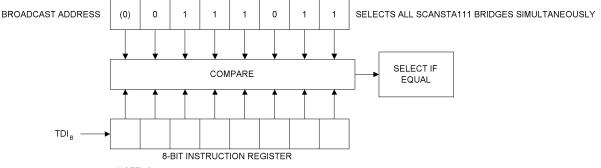

- True IEEE 1149.1 hierarchical and multidrop addressable capability

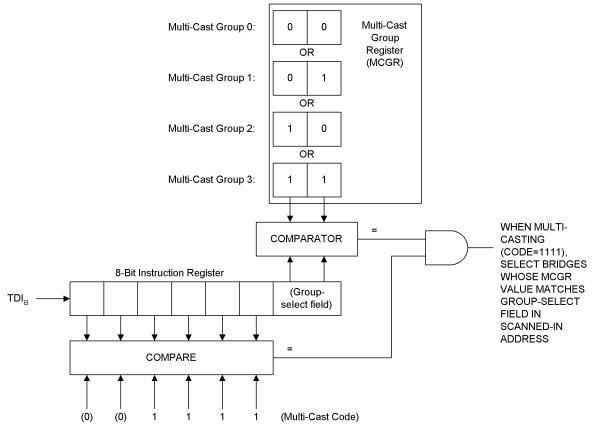

- The 7 slot inputs support up to 121 unique addresses, an Interrogation Address, Broadcast Address, and 4 Multi-cast Group Addresses (address 000000 is reserved)

- 3 IEEE 1149.1-compatible configurable local scan ports

- Mode Register<sub>o</sub> allows local TAPs to be bypassed, selected for insertion into the scan chain individually, or serially in groups of two or three

- Transparent Mode can be enabled with a single instruction to conveniently buffer the backplane IEEE 1149.1 pins to those on a single local scan port

- LSP ACTIVE outputs provide local port enable signals for analog busses supporting IEEE 1149.4.

- General purpose local port passthrough bits are useful for delivering write pulses for FPGA programming or monitoring device status.

- Known Power-up state

- TRST on all local scan ports

- 32-bit TCK counter

- 16-bit LFSR Signature Compactor

- Local TAPs can become TRI-STATE via the  $\overline{OE}$  input to allow an alternate test master to take control of the local TAPs (LSP<sub>0-2</sub> have a TRI-STATE notification output)

- 3.0-3.6V V<sub>CC</sub> Supply Operation

- Power down high impedance inputs and outputs

- Supports live insertion/withdrawal

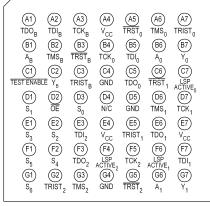

# **Connection Diagrams**

10124516

|                      | TABLE 1 Classery                                                                                                                                   |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | TABLE 1. Glossary                                                                                                                                  |  |

| LFSR                 | Linear Feedback Shift Register. When enabled, will generate a 16-bit signature of sampled serial test                                              |  |

|                      | data.                                                                                                                                              |  |

| LSP                  | Local Scan Port. A four signal port that drives a local (i.e. non-backplane) scan chain. (e.g., TCK <sub>0</sub> , TMS <sub>0</sub> ,              |  |

|                      | $TDO_0$ , $TDI_0$ ).                                                                                                                               |  |

| Local                | Local is used to describe IEEE Std. 1149.1 compliant scan rings and the SCANSTA111 Test Access Port                                                |  |

|                      | that drives them. The term local was adopted from the system test architecture that the 'STA111 will most                                          |  |

|                      | commonly be used in; namely, a system test backplane with a 'STA111 on each card driving up to 3 local                                             |  |

|                      | scan rings per card. (Each card can contain multiple 'STA111s, with 3 local scan ports per 'STA111.)                                               |  |

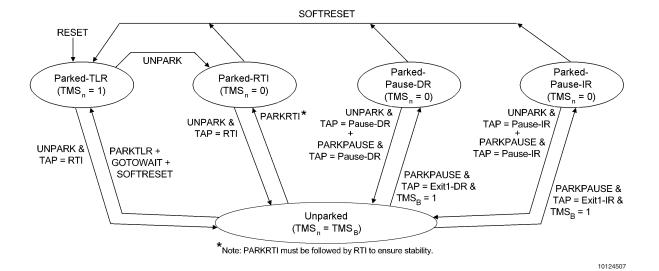

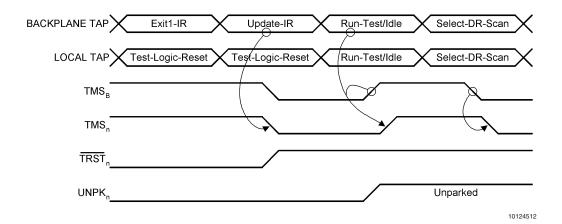

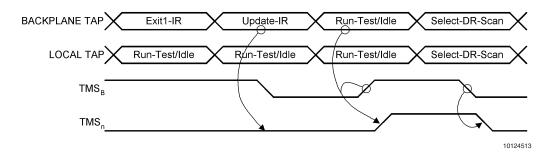

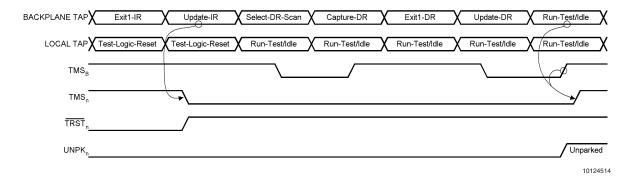

| Park/Unpark/Unparked | Parked, unpark, and unparked, are used to describe the state of the LSP controller and the state of the                                            |  |

|                      | local TAP controllers (the local TAP controllers refers to the TAP controllers of the scan components that                                         |  |

|                      | make up a local scan ring). Park is also used to describe the action of parking a LSP (transitioning into                                          |  |

|                      | one of the Parked LSP controller states). It is important to understand that when a LSP controller is in                                           |  |

|                      | one of the parked states, TMS <sub>n</sub> is held constant, thereby holding or parking the local TAP controllers in a                             |  |

|                      | given state.                                                                                                                                       |  |

| TAP                  | Test Access Port as defined by IEEE Std. 1149.1.                                                                                                   |  |

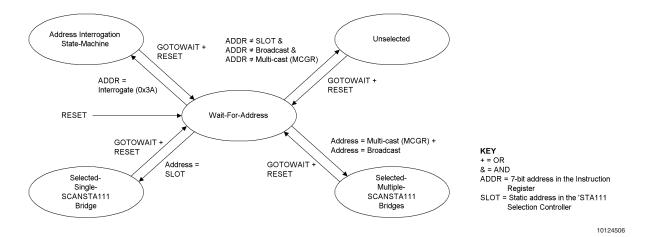

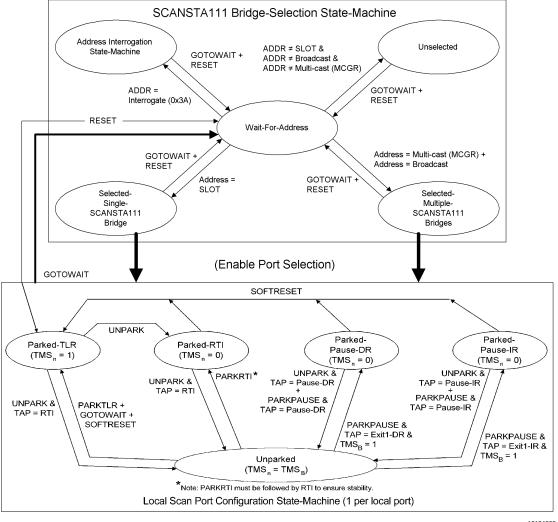

| Selected/Unselected  | Selected and Unselected refers to the state of the 'STA111 Selection Controller. A selected 'STA111 has                                            |  |

|                      | been properly addressed and is ready to receive Level 2 protocol. Unselected 'STA111s monitor the                                                  |  |

|                      | system test backplane, but do not accept Level 2 protocol (except for the GOTOWAIT instruction). The                                               |  |

|                      | data registers and LSPs of unselected 'STA111s are not accessible from the system test master.                                                     |  |

| Active Scan Chain    | The Active Scan Chain refers to the scan chain configuration as seen by the test master at a given                                                 |  |

|                      | moment. When a 'STA111 is selected with all of its LSPs parked, the active scan chain is the current                                               |  |

|                      | scan register only. When a LSP is unparked, the active scan chain becomes: $TDI_B \rightarrow$ the current 'STA111                                 |  |

|                      | register $\rightarrow$ the local scan ring registers $\rightarrow$ a PAD bit $\rightarrow$ TDO <sub>B</sub> . Refer to <i>Table 7</i> for Unparked |  |

|                      | configurations of the LSP network.                                                                                                                 |  |

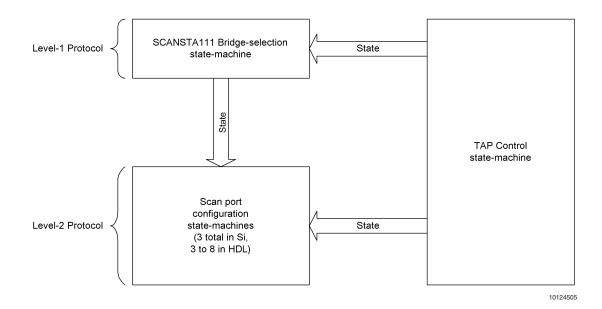

| Level 1 Protocol     | Level 1 is the protocol used to address a 'STA111.                                                                                                 |  |

| Level 2 Protocol     | Level 2 is the protocol that is used once a 'STA111 is selected. Level 2 protocol is IEEE Std. 1149.1                                              |  |

|                      | compliant when an individual 'STA111 is selected.                                                                                                  |  |

| PAD                  | A one bit register that is placed at the end of each local scan port scan-chain. The PAD bit eliminates the                                        |  |

|                      | prop delay that would be added by the 'STA111 LSPN logic between TDI <sub>n</sub> and TDO <sub>(n+1)</sub> or TDO <sub>B</sub> by                  |  |

|                      | buffering and synchronizing the LSP TDI inputs to the falling edge of TCK <sub>B</sub> , thus allowing data to be                                  |  |

|                      | scanned at higher frequencies without violating set-up and hold times.                                                                             |  |

| LSB                  | Least Significant Bit, the right-most position in a register (bit 0).                                                                              |  |

| MSB                  | Most Significant Bit, the left-most position in a register.                                                                                        |  |

|                      | ·                                                                                                                                                  |  |

#### **Architecture**

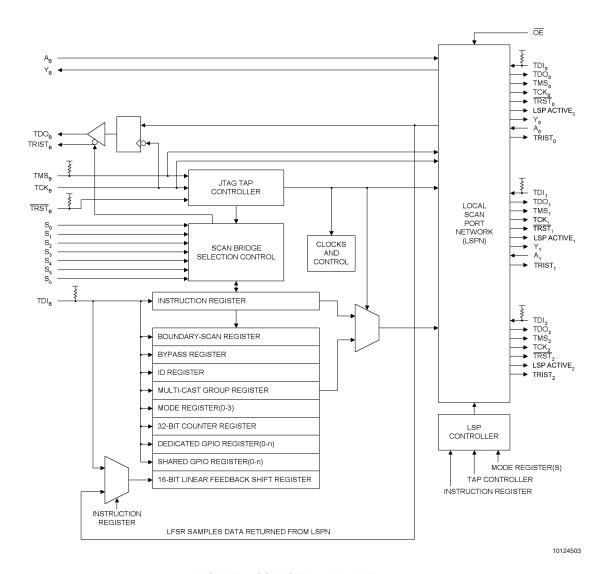

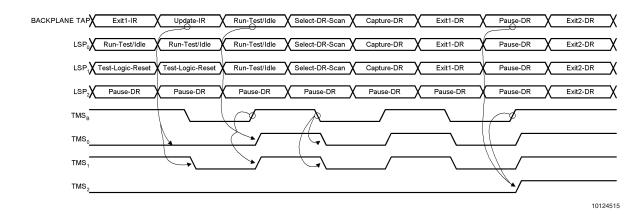

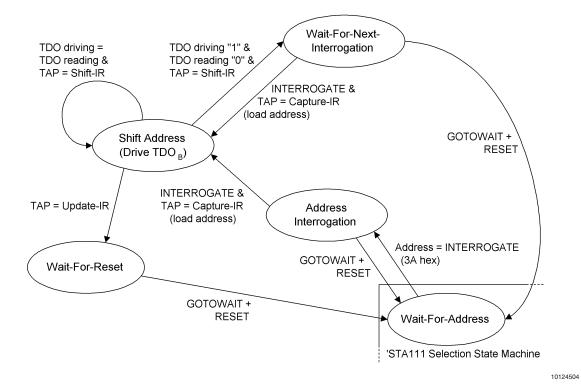

Figure 1 shows the basic architecture of the 'STA111. The device's major functional blocks are illustrated here. The TAP Controller, a 16-state state machine, is the central control for the device. The instruction register and various test data registers can be scanned to exercise the various functions of the 'STA111 (these registers behave as defined in IEEE Std. 1149.1). The 'STA111 selection controller provides the functionality that allows the 1149.1 protocol to be used in a multi-drop environment. It primarily compares the address

input to the slot identification and enables the 'STA111 for subsequent scan operations. The Local Scan Port Network (LSPN) contains multiplexing logic used to select different port configurations. The LSPN control block contains the Local Scan Port Controllers (LSPC) for each Local Scan Port (LSP $_0$ , LSP $_1$  ... LSP $_n$ ). This control block receives input from the 'STA111 instruction register, mode registers, and the TAP controller. Each local port contains all four boundary scan signals needed to interface with the local TAPs plus the optional Test Reset signal (TRST).

FIGURE 1. SCANSTA111 Block Diagram

# **TABLE 2. Pin Descriptions**

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No.<br>Pins | 1/0  | Description                                                                                                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3           | N/A  | Power                                                                                                                                                               |  |

| GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3           | N/A  | Ground                                                                                                                                                              |  |

| TMS <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1           | 19/7 |                                                                                                                                                                     |  |

| I IVI 3 <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '           | '    | BACKPLANE TEST MODE SELECT: Controls sequencing through the TAP Controller of the 'STA111. Also controls sequencing of the TAPs which are on the local scan chains. |  |

| TDI <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1           | ı    | BACKPLANE TEST DATA INPUT: All backplane scan data is supplied to the 'STA111 through                                                                               |  |

| I DIB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | '           | '    | this input pin.                                                                                                                                                     |  |

| TDO <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1           | 0    | BACKPLANE TEST DATA OUTPUT: This output drives test data from the 'STA111 and the                                                                                   |  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      | local TAPs, back toward the scan master controller. This output has 24mA of drive current.                                                                          |  |

| TCK <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1           | I    | TEST CLOCK INPUT FROM THE BACKPLANE: This is the master clock signal that controls                                                                                  |  |

| , and the second |             |      | all scan operations of the 'STA111 and of the local scan ports.                                                                                                     |  |

| TRST <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1           | I    | TEST RESET: An asynchronous reset signal (active low) which initializes the 'STA111 logic.                                                                          |  |

| TRIST <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1           | 0    | BACKPLANE TRI-STATE NOTIFICATION OUTPUT: This signal is high when the backplane                                                                                     |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |      | scan port is TRI-STATEd. This pin is used for backplane physical layer changes (i.e.; TTL to                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | LVDS). This output has 12mA of drive current.                                                                                                                       |  |

| A <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1           | I    | BACKPLANE PASS-THROUGH INPUT: A general purpose input which is driven to the Y <sub>n</sub> of                                                                      |  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |      | a single selected LSP. (Not available when multiple LSPs are selected). This input has an                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | internal pull-up resistor.                                                                                                                                          |  |

| Y <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1           | 0    | BACKPLANE PASS-THROUGH OUTPUT: A general purpose output which is driven from the                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | A <sub>n</sub> of a single selected LSP. (Not available when multiple LSPs are selected). This output                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | has 24mA of drive current.                                                                                                                                          |  |

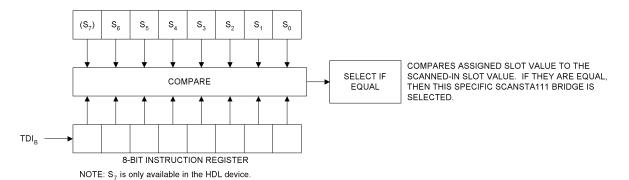

| S <sub>(0-6)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7           | I    | SLOT IDENTIFICATION: The configuration of these pins is used to identify (assign a unique                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | address to) each 'STA111 on the system backplane (Note 1).                                                                                                          |  |

| ŌĒ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1           | I    | OUTPUT ENABLE for the Local Scan Ports, active low. When high, this active-low control                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | signal TRI-STATEs all local scan ports on the 'STA111, to enable an alternate resource to                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | access one or more of the three local scan chains.                                                                                                                  |  |

| TDO <sub>(0-2)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3           | 0    | TEST DATA OUTPUTS: Individual output for each of the local scan ports (Note 2). These                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      | outputs have 24mA of drive current.                                                                                                                                 |  |

| TDI <sub>(0-2)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3           | I    | TEST DATA INPUTS: Individual scan data input for each of the local scan ports (Note 2).                                                                             |  |

| TMS <sub>(0-2)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3           | 0    | TEST MODE SELECT OUTPUTS: Individual output for each of the local scan ports. TMS <sub>n</sub>                                                                      |  |