# **SED1753**

# **CMOS LCD COMMON DRIVER**

### **■** DESCRIPTION

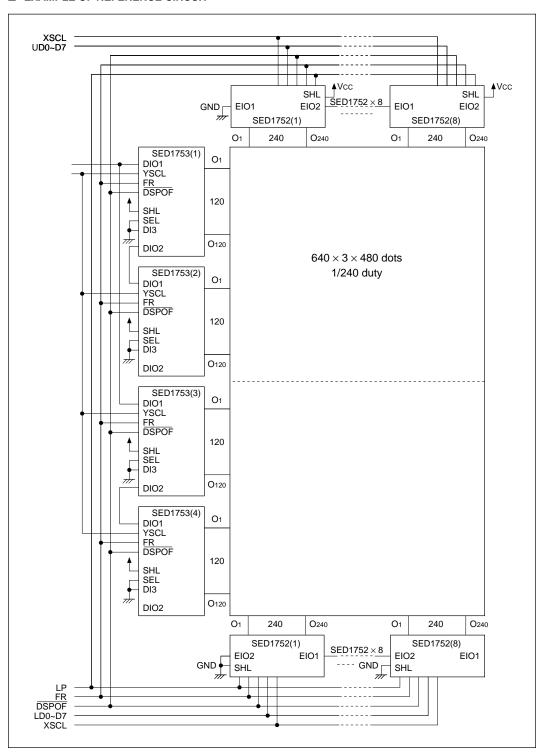

The SED1753 is an LCD common (row) driver designed for extremely high-capacity dot matrix liquid crystal panels. It incorporates 120 high-voltage, low-impedance common drivers in a  $2 \times 60$  format, enabling high driver effectiveness with displays of 1/240, 1/300 and 1/480 duty cycles. It is designed for use in conjunction with the SED1752 and SED1758 segment (column) drivers.

The SED1753 features a wide range of liquid crystal drive voltages, an LCD display of high quality and slim configuration to minimize the LCD panel. It offers a wide range of applications.

#### **■ FEATURES**

- 120 (60 × 2) LCD common drive outputs

- 0.3K $\Omega$  (typ.) low output impedance

- High-duty drive available ...... 1/480

- Pin-selectable output shift direction

- Zero-bias display disable function

- Slim configuration

- Adjustable LCD drive voltage

- Liquid crystal drive in wide range of voltage: 8 to 42V

- 2.7 to 5.5V supply

- Package: ..... D0B ...... Au bump die T0A ...... TAB package

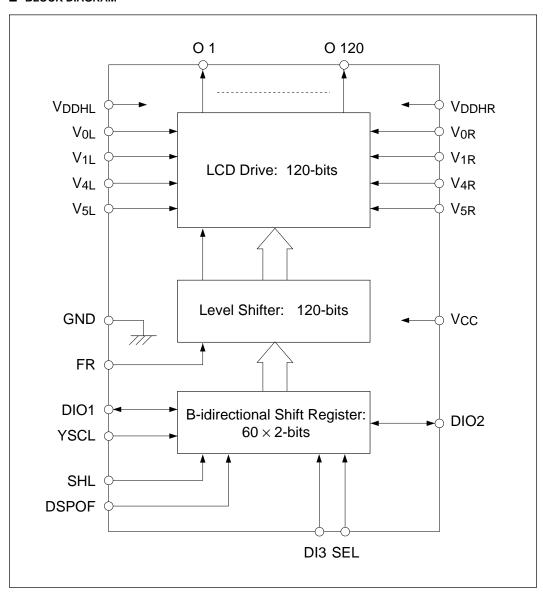

### **■ BLOCK DIAGRAM**

### **■ FUNCTIONS**

### Shift Register

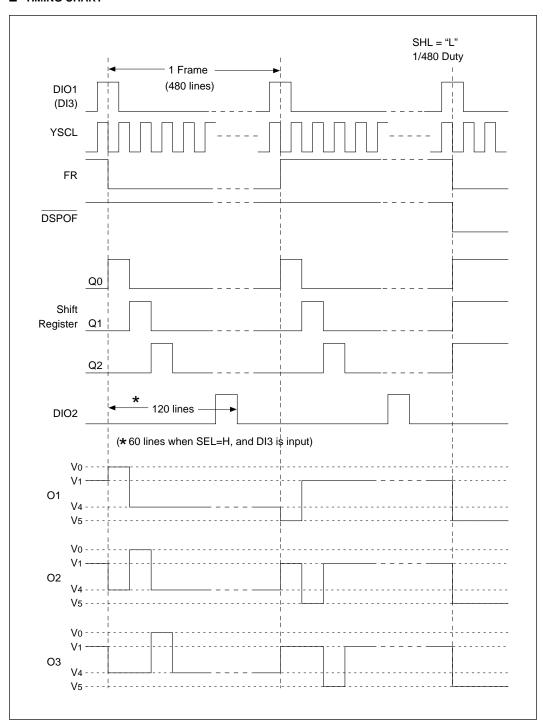

This is a bi-directional shift register for transmitting common data. The shift register has a  $60 \times 2$  bit structure, and a  $60 \times 2$  bit or 120-bit structure can be selected depending on the state of SEL.

When a  $60 \times 2$  bit structure is selected, the lower-stage 60-bit shift register input becomes DI3.

#### Level Shifter

This is a voltage level interface circuit for converting the signal voltage level from a logic-system level to an LCD drive-system level.

#### LCD Driver

These output the LCD driver voltages.

The relationship between the display blanking signal DSPOF, the contents of the shift register, the alternating signal FR, and the common output voltage is as shown below:

| DSPOF | Contents of<br>Shift Register | FR | ON Output<br>Voltage |                  |  |  |

|-------|-------------------------------|----|----------------------|------------------|--|--|

|       | 1.1                           | Н  | V <sub>5</sub>       | (Selected level) |  |  |

| Н     | Н                             | L  |                      |                  |  |  |

|       |                               | Н  | V <sub>1</sub>       | (Non-selected    |  |  |

|       | L                             |    |                      | level)           |  |  |

|       |                               | L  | V <sub>4</sub>       |                  |  |  |

| L     | _                             | _  | V <sub>5</sub>       | _                |  |  |

# **■ TIMING CHART**

# **■ EXPLANATION OF TERMINALS**

| Terminal Name                                                 | I/O          | Function                                                                                                                                                                 | No. of Terminals |

|---------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| O 1 to<br>O 120                                               | 0            | LCD drive common (row) output. Changes on the falling edge of YSCL                                                                                                       | 120              |

| DIO1<br>DIO2                                                  | I/O          | Set to input or to output by the scanning pulse SHL Input of the 60 x 2 bit bi-directional shift register.  The output changes on the falling edge of YSCL               | 2                |

| DI3                                                           | I            | DI3 is a scan pulse input when a 60 x 2 structure is used.<br>When SEL = L, DI3 is connected to ground.                                                                  | 1                |

| SEL                                                           | I            | Bi-directional shift register operating mode select input.<br>H: 60 x 2 (DI3 input); L: 120                                                                              | 1                |

| YSCL                                                          | I            | Serial data shift clock input. The scan data is shifted with the falling edge.                                                                                           | 1                |

| SHL                                                           | I            | Shift direction select and DIO terminal input/output control output                                                                                                      |                  |

|                                                               |              | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                  |                  |

|                                                               |              | L 120 → 61 60 → 1 Output Input                                                                                                                                           |                  |

| DSPOF                                                         | I            | LCD display blanking control input. When "L", all common outputs are set to the V5 level.                                                                                | 1                |

| FR                                                            | I            | LCD drive output alternating signal input.                                                                                                                               | 1                |

| GND, Vcc                                                      | Power supply | Power supply for logic: GND: 0V Vcc + 2.7 to 5.5V                                                                                                                        | 2                |

| Vol, VIL, V4L,<br>V5L, VDDH,<br>VOR, V1R, V4R,<br>V5R, VDDHR, | Power supply | Power supply LCD drive GND: 0V, V <sub>DDH</sub> : 8V to 42V V <sub>DDH</sub> $\geq$ V0 $\geq$ 8/9V <sub>DDH</sub> 1/9V <sub>DDH</sub> $\leq$ V4 $\geq$ V5 $\geq$ GND *1 | 10               |

|                                                               | 1            | Total                                                                                                                                                                    | 140 pins         |

\*1.  $V_{\text{DDH}}$  and  $V_0$  to  $V_5$  pairs must be connected to their respective LC power supplies. The LC drive circuit power supply voltage ranges are specification recommended values.

# **■ ELECTRICAL CHARACTERISTICS**

### Absolute Maximum Rating

| Parameters                      | Symbol               | Rating                             | Units |

|---------------------------------|----------------------|------------------------------------|-------|

| Power supply voltage (1)        | Vcc                  | -0.3 to +7.0                       | V     |

| Power supply voltage (2)        | V <sub>DDH</sub>     | -0.3 to +45.0                      | V     |

| Power supply voltage (3)        | $V_0, V_1, V_4, V_5$ | GND - 0.3 to V <sub>DDH</sub> +0.3 | V     |

| Input voltage                   | Vı                   | GND - 0.3 to Vcc +0.3              | V     |

| Output voltage                  | Vo                   | GND - 0.3 to Vcc +0.3              | V     |

| DIO output current              | <b>l</b> 01          | 20                                 | mA    |

| Operating temperature           | Topr                 | -40 to +85                         | °C    |

| Chip storage temperature        | Tstg <sup>1</sup>    | -65 to +150                        | °C    |

| TCP product storage temperature | Tstg <sup>2</sup>    | -55 to +125                        | °C    |

Note 1. All the above voltages are based on GND = 0V.

Note 2.  $V_0$ ,  $V_1$ ,  $V_4$  and  $V_5$  voltages must always fulfill the following relationship:  $V_{DDH} \ge V_0 \ge V_1 \ge V_4 \ge V_5 \ge GND$

Note 3. Permanent damage to the LSI may result if the logic power supply is floating or falls below Vcc = 2.6V when the LCD drive power supply is supplied. Special caution is required during the System Power OFF and System Power ON sequencing.

# • DC Characteristics Unless otherwise designated, GND = $V_5 = 0V$ , $V_{CC} = 5.0V \pm 10\%$ , $T_a = -40$ to $85^{\circ}C$

| 5 .                                       |                  |                                                                                                                                        |                                                                                                               |                                    | Applicable                          |                      |      | l                    |      |

|-------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------|----------------------|------|----------------------|------|

| Parameter                                 | Symbol           |                                                                                                                                        | Condition                                                                                                     |                                    | Pin                                 | Min                  | Тур  | Max                  | Unit |

| Electrical voltage (1)                    | Vcc              | _                                                                                                                                      |                                                                                                               |                                    | Vcc                                 | 2.7                  | 5.0  | 5.5                  | V    |

| Recommended working voltage               | V <sub>DDH</sub> | $V_{CC} = 2.7 \text{ to } 5.5 \text{ V}$                                                                                               |                                                                                                               | VDDHL, VDDHL                       | 14.0                                | _                    | 40.0 | V                    |      |

| Possible operating voltage                | V <sub>DDH</sub> | Function                                                                                                                               |                                                                                                               | V <sub>0</sub> L, V <sub>O</sub> R | 8.0                                 | _                    | 42.0 | V                    |      |

| Power supply voltage (2)                  | V <sub>1</sub>   | Recomme                                                                                                                                | Recommended value                                                                                             |                                    | V <sub>1</sub> L, V <sub>1</sub> R  | 8/9 V <sub>DDH</sub> | _    | V <sub>DDH</sub>     | V    |

| Power supply voltage (3)                  | V <sub>4</sub>   | Recomme                                                                                                                                | nde                                                                                                           | d value                            | V <sub>4</sub> L, V <sub>4</sub> R  | GND                  | _    | 1/9 V <sub>DDH</sub> | V    |

| High level input voltage                  | ViH              | Vcc= 2.7~                                                                                                                              | 5.5\                                                                                                          | /                                  | DIO1,DIO2, FR                       | 0.8 Vcc              | _    | _                    | V    |

| Low level input voltage                   | VIL              |                                                                                                                                        |                                                                                                               |                                    | YSCL, SHL, DI3<br>DSPOF, SEL        |                      | _    | 0.2 Vcc              | V    |

| High level output voltage                 | Vон              | Vcc =                                                                                                                                  | Іон =                                                                                                         | = -0.3mA                           | EIO1, EIO2,                         | Vcc-0.4              |      | _                    | V    |

| Low level output voltage                  | Vol              | 2.7~5.5V                                                                                                                               | lol =                                                                                                         | = 0.3mA                            |                                     | I                    | _    | GND+0.4              | V    |

| Input leakage current                     | lu               | GND ≤ V <sub>IN</sub>                                                                                                                  | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                       |                                    | YSCL, SHL, DI3<br>DSPOF, FR,<br>SEL |                      | _    | 2.0                  | μΑ   |

| I/O leak current                          | ILI/O            | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                                |                                                                                                               | EIO1, EIO2                         | _                                   | _                    | 5.0  | μΑ                   |      |

| Static current                            | I <sub>GND</sub> | V <sub>DDH</sub> = 14.0 ~ 42.0V<br>V <sub>IH</sub> = V <sub>CC</sub> , V <sub>IL</sub> = GND                                           |                                                                                                               | GND                                | _                                   | _                    | 25   | μΑ                   |      |

| Output resistance                         | Rсом             | $\Delta V_{ON} = 0.5$                                                                                                                  |                                                                                                               | V <sub>DDH</sub> = +36.0V,<br>1/24 | 01~                                 | _                    | 0.29 | 0.48                 | ΚΩ   |

|                                           |                  | Ta = 25°C                                                                                                                              |                                                                                                               | $V_{DDH} = +26.0V,$ $1/20$         | O120                                | _                    | 0.3  | 0.5                  |      |

| Resistance chip-internal BIOS             | ΔRсом            | VDDH = +36                                                                                                                             | V <sub>DDH</sub> = +36.0V, 1/24                                                                               |                                    |                                     | _                    | _    | 50                   | Ω    |

| Average operating current consumption (1) | Icc              | VIL = GND<br>fLP = 70Hz<br>Input data                                                                                                  | Vcc = +5.0V, ViH = Vcc<br>ViL = GND, frscL = 33.6KHz<br>fLP = 70Hz,<br>Input data: 1/480<br>Ta = 25°C No load |                                    | Vcc                                 | _                    | TBD  | TBD                  | μА   |

|                                           |                  |                                                                                                                                        | ondi                                                                                                          | tons are the                       |                                     | _                    | TBD  | TBD                  |      |

| Average operating current consumption (2) | Іодн             | $V_{DDH} = V_0 = 30.0 V V_1 = 28.0 V$ $V_4 = 2.0 V, V_5 = 0.0 V,$ $V_{CC} = 5.0 V$ Other conditions are the same as with the item lcc. |                                                                                                               | VDDHL, VDDHR                       | _                                   | TBD                  | TBD  | μА                   |      |

| Input terminal capacity                   | CI               | Ta = 25°C                                                                                                                              | Freq. = 1 MHz YSCL, SHL, DS<br>Ta = 25°C DI3, SEL                                                             |                                    | SPOF, FR,                           | _                    | _    | 8                    | pF   |

| I/O terminal capacity                     | Ci/o             | Chips alor                                                                                                                             | ne                                                                                                            | DIO1, DIO2                         |                                     | _                    |      | 15                   | pF   |

|                                           |                  |                                                                                                                                        |                                                                                                               |                                    |                                     |                      |      |                      |      |

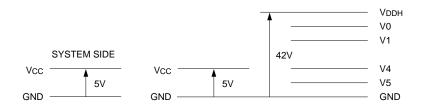

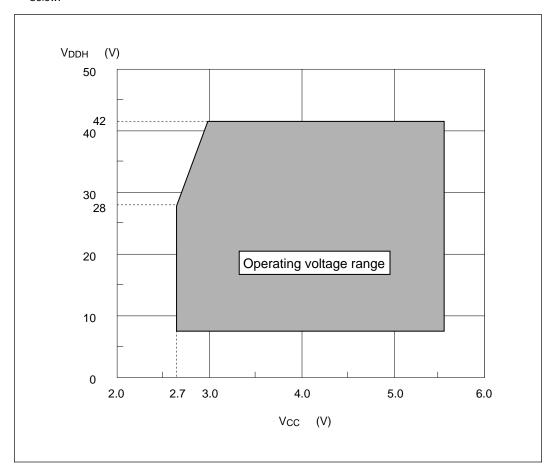

# ● Range of Operating Voltages: Vcc - VDDH

It is necessary to set the voltage for  $V_{\text{DDH}}$  within the  $V_{\text{CC}} - V_{\text{DDH}}$  operating voltage range shown in the diagram below.

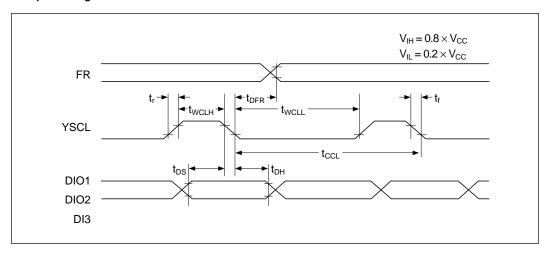

# AC CharacteristicsInput Timing Characteristics

Vcc = +5.0V  $\pm$  10%,  $T_a$  = -40 to 85°C

| Parameter                      | Symbol         | mbol Conditions |     | Max. | Units |

|--------------------------------|----------------|-----------------|-----|------|-------|

| YSCL cycle                     | tccl           | _               | 400 | _    | ns    |

| YSCL high level pulse duration | twclh          | _               | 60  | _    | ns    |

| YSCL low level pulse duration  | twcll          | _               | 330 | _    | ns    |

| Data setup time                | tos            | _               | 50  | _    | ns    |

| Data hold time                 | tон            | _               | 40  | _    | ns    |

| Input signal rise time         | tr             | _               | _   | 50   | ns    |

| Input signal fall time         | t <sub>f</sub> | _               | _   | 50   | ns    |

Vcc = 2.7 to 4.5V,  $T_a$  = -40 to 85°C

| Parameter                      | Symbol     | Conditions | Min. | Max. | Units |

|--------------------------------|------------|------------|------|------|-------|

| YSCL cycle                     | tccl       | _          | 800  | _    | ns    |

| YSCL high level pulse duration | twclh      | _          | 80   | _    | ns    |

| YSCL low level pulse duration  | twcll      | _          | 660  | _    | ns    |

| Data setup time                | tos        | _          | 90   | _    | ns    |

| Data hold time                 | tон        | _          | 70   | _    | ns    |

| Input signal rise time         | tr         | _          | _    | 50   | ns    |

| Input signal fall time         | <b>t</b> f | _          | _    | 50   | ns    |

Note: \*1. The timing for the FR signal transition point (toFR: FR) and the LP signal falling edge is, essentially, 0 ns; set these in a range where the ON output wave form is not distorted.

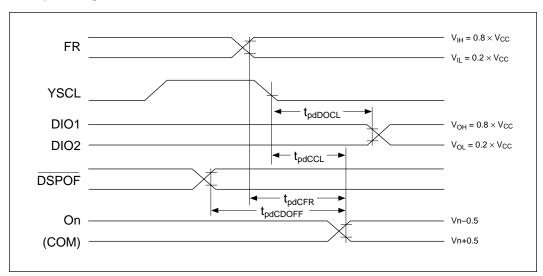

### o Output Timing Characteristics

$V_{\text{CC}}$  = 5.0V  $\pm$  10%,  $V_{\text{DDH}}$  = 14.0 to 42.0V, ta = –40 to +85°C

| Parameter                                      | Symbol                      | Conditions  | Min. | Max. | Units |

|------------------------------------------------|-----------------------------|-------------|------|------|-------|

| Delay time from YSCL falling edge to DIO       | tpdDOCL                     | C∟ = 15 pf  | _    | 100  | ns    |

| Delay time from YSCL falling edge to ON output | <b>t</b> pdCCL              |             |      | 200  | 20    |

| Delay time from DSPOF to ON output             | <b>t</b> <sub>pdCDOFF</sub> | C∟ = 100 pf | _    | 200  | ns    |

| Delay time from FR to ON output                | <b>t</b> <sub>pdCFR</sub>   |             | _    | 300  | ns    |

$V_{CC} = 2.7V$  to 4.5V,  $V_{DDH} = 14.0$  to 28.0V, ta = -40 to +85°C

| Parameter                                      | Symbol         | Conditions              | Min. | Max. | Units |

|------------------------------------------------|----------------|-------------------------|------|------|-------|

| Delay time from YSCL falling edge to DIO       | tpdDOCL        | C∟ = 15 pf              | _    | 200  | ns    |

| Delay time from YSCL falling edge to ON output | <b>t</b> pdCCL |                         |      | 400  | ne    |

| Delay time from DSPOF to ON output             | tpdCDOFF       | C <sub>L</sub> = 100 pf |      | 400  | ns    |

| Delay time from FR to ON output                | tpdCFR         |                         | _    | 600  | ns    |

$\textbf{Notes:} \quad {}^{\star}\textbf{1}. \quad \text{The input signal $t_r$, $t_f$ is fixed to 20ns.}$

\*2. High speed operation of the shift clocks (XSCL) should be made only under a condition of  $t_i$  or  $t_i \le \{t_C - (t_{DCL} + t_{SUE})\}/2$ .

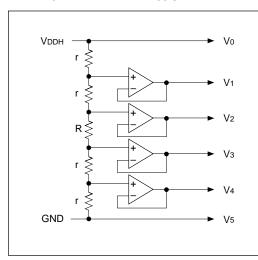

# ■ THE LIQUID CRYSTAL DRIVE POWER SUPPLY

#### Forming the Various Voltage Levels

The most appropriate method for obtaining the various voltage levels for driving the LCD is to use resistive voltage dividers for the voltage levels between  $V_{\text{DDH}}$  and GND, and to drive the voltage levels using voltage followers employing op amps.

Considering the use of the op amp,  $V_{DDH}$  and  $V_0$ , the lowest voltage level for driving the LCD, and GND and  $V_5$ , the lowest voltage for driving the LCD, are separated from each other and given separate pins.

Normally,  $V_0$  and  $V_{\text{DDH}}$  are connected, as are  $V_5$  and GND, and  $V_1$  and  $V_4$  are driven using voltage followers. When  $V_0$  is driven using a voltage follower, the ability of the LSI to drive the LCD outputs diminishes when the level of  $V_0$  is higher than that of  $V_{\text{DDH}}$  and the difference in the voltage levels is great; thus the voltage difference between  $V_{\text{DDH}}$  and  $V_0$  should be kept in the range of 0V to 2.5V.

When there is a serial resistance between the GND and  $V_{DDH}$  power supply lines, the voltage between GND and  $V_{DDH}$  is reduced at the LSI power terminals because of the  $I_{DDH}$  when the signals change, which may lead to permanent damage to the LSI if the relationships between the LCD voltage levels does not follow the formula:  $V_{DDH} \ge V_0 \ge V_1 \ge V_4 \ge V_5 \ge GND$ .

When a guard resistance is used, it is necessary to stabilize the voltage with a capacitor.

#### Power Supply Stabilization

When necessary to prevent the effects of noise arising from the power supply signal line leads in packaging on the circuit board, a bypass capacitor between the power supplies  $(GND - V_{CC}, GND - V_{DDH})$  may be required in order to stabilize the voltages.

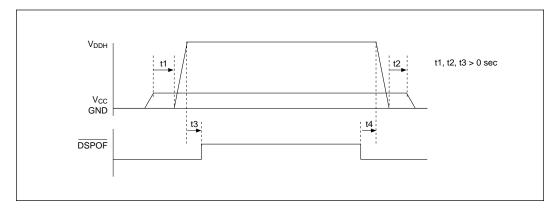

#### Cautions Regarding Turning the Power Supply ON and OFF

Because the voltage in the LCD drive system of this LSI is high, the LSI may be permanently damaged by an overcurrent situation when LCD drive signals are output before the LCD drive system applied voltage is stabilized, or when the LCD drive system high-voltage is applied while the logic system power supply is floating or when  $V_{CCS}$  is less than 2.6V. It is recommended that the display OFF function  $\overline{DSPOFF}$  be used until the LCD drive system voltage stabilized, and that the LCD drive output voltage level be at the  $V_5$  level.

Please follow the following sequences when turning the power supplies ON and OFF:

Power Supply ON:

Logic system ON  $\rightarrow$  LCD drive system ON (or simultaneous)

Power Supply OFF:

LCD drive system OFF → Logic system OFF (or simultaneous)

### **■ EXAMPLE OF REFERENCE CIRCUIT**

#### • Example of LCD Power Supply Circuits

- The LCD drive power supply (V₀ V₅) requires the addition of smoothing capacitors on the appropriate places in the LCD module.

- $V_0$ ,  $V_1$ ,  $V_4$  and  $V_5$  are supplied to SED1753, and  $V_0$ ,  $V_2$ ,  $V_3$  and  $V_5$  are supplied to SED1752.

- The logic power supply Vcc is supplied to all ICs

- It is necessary to add bypass capacitors to the appropriate locations between GND – Vcc and GND – VDDH to eliminate noise, thereby stabilizing the power supply voltage. It is recommended that the power supplies for high-voltage application (GNDR, GNDL) use a different system than the lines for the power supplies for logic (GND).

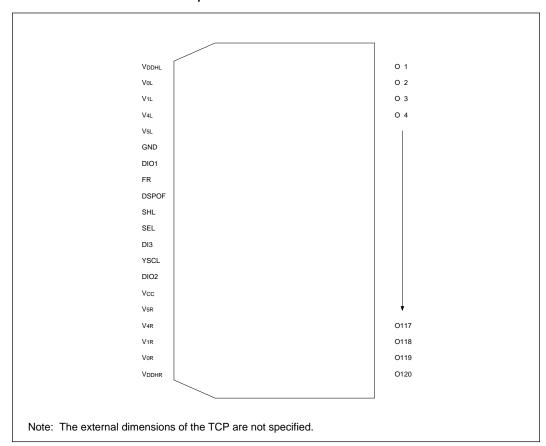

#### TCP

### ○ An SED1753T\*\* TCP Pinout Example

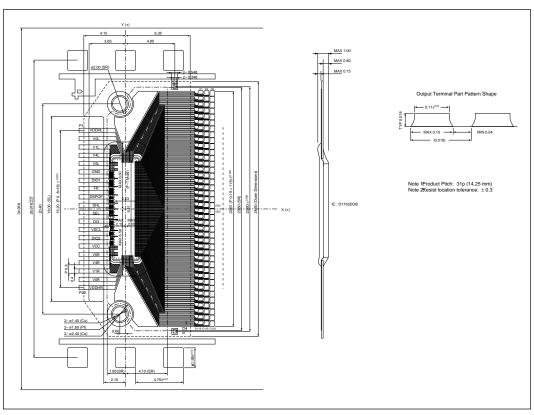

# • External Dimension Diagram