#### **Features**

- Integrates a 64-slot Digital Signal Processor (DSP), 16-bit Processor, 24K x 16 On-chip Flash Memory, 2K x 16 RAM, 64 Individually Programmable I/O Pins

- Alternate Group Selectable I/O Pins Allow External Memory Expansion, Host Parallel I/O, Serial MIDI IN/OUT, Additional Digital Audio-in/out

- Up to 64 Voices Polyphony, 24 dB Resonant Filter Per Voice, User Programmable Synthesis/Processing Algorithms

- Three Timers, One Timer Being Available for Orchestrations Tempo Control

- Ideal for Battery Operation

- 3V to 4.5V Power Supply

- Power-down Mode

- Parameters Can Be Saved Into Built-in Flash Memory on a Single Word Write Basis.

- Compatible with SAM97xx Series Design Tools and Debugger

- Quick Time to Market

- Proven Reliable Synthesis Drivers

- In-circuit Emulation with Code View Debugger for Easy Prototype Development

- Built-in Flash Programming Algorithm

- Low frequency Input Clock at 256xFs Minimizes RFI, Built-in PLL Raises Frequency Internally

- PQFP100 Easy Mount Standard Package (Pitch 0.65 mm)

- Atmel Standard Flash Technology

## **Description**

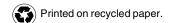

The SAM9743 integrates into a single chip a SAM97xx core (64-slot DSP + 16-bit processor), a 24K x 16 Flash memory, a 2K x 16 RAM, and up to 64 individually programmable I/O pins. With the addition of a single external digital-to-analog converter or a codec, the SAM9743 can be used in a variety of musical and sound processing applications, like low-cost keyboards, equalizers and effect processors.

I/O pins can be configured for external memory expansion, allowing more sophisticated products with up to 4M bytes RAM or ROM.

Figure 1. Typical Application of the SAM9743

## Single-chip Music System

**SAM9743**

Rev. 1773A-10/01/0M

#### **Principal Elements**

## Key Circuitry in a Single Chip

The SAM9743 provides a new generation of integrated solutions for electronic musical instruments and sound processors. The SAM9743 places all key circuitry onto a single silicon chip: sound synthesizer/processor, 16-bit control processor, 24K x 16 Flash memory, 2K x 16 RAM, and up to 64 individually programmable I/O pins allowing direct interface with keyboard, switches, LCD display, etc.

#### SAM97xx Series Processing Core

The synthesis/sound processing core of the SAM9743 is taken from the SAM97xx series, whose quality has already been demonstrated through dozens of different musical products such as electric pianos, home keyboards, professional keyboards, classical organs, sound expanders and effect devices. The maximum polyphony is 64 voices without effects. A typical application will be 38-voice polyphony with reverb, chorus, 4-band equalizer and surround.

#### External Memory Expansion

Configuration options allow the SAM9743 to cover a wide range of products, from the lowest cost keyboard to the high range multi-effect processor. Thanks to flexible external memory expansion, up to 4M bytes additional external memory can be used for firmware, orchestrations, PCM data or delay lines. The external memory can be ROM, RAM or Flash. The internal Flash memory can be programmed on-board from the SAM9743 itself by a Flash programming algorithm, which resides in internal ROM on chip.

#### Standard Compliance Made Easier

The SAM9743 operates from a single 8 MHz crystal. A built-in PLL multiplies by 4 the crystal frequency for internal processing. This minimizes radio frequency interference (RFI), making it easier to comply with FCC, CSA and CE standards.

# Battery Powered Usage

The SAM9743 is very suitable for battery-operated products:

- A power-down feature is included which can be controlled externally (PDWN/ pin).

- Built-in Flash memory words can be individually programmed by the firmware itself.

- Operational voltage is from 3V to 5.5V (I/O).

#### **Quick Time to Market**

The SAM9743 has been designed with final instrument quick time-to-market in mind. The SAM9743 product development program includes key features to minimize product development efforts:

- Specialized debug interface, providing on-target software development with a source code CodeView debugger.

- Standard sound generation/processing firmware.

- Windows<sup>®</sup> tools for sounds, soundbanks and orchestration developments.

- Standard soundbanks.

- Comprehensive technical support available directly from Atmel.

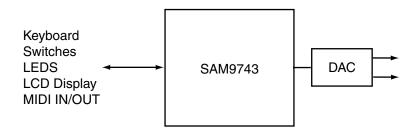

## Internal Architecture

The highly-integrated architecture of the SAM9743 combines a specialized high-performance RISC-based digital signal processor (DSP) and a general-purpose 16-bit CISC-based control processor (P16). An on-chip memory management unit (MMU) allows the DSP and the control processor to share an internal 24K x 16 Flash memory, 2K x 16 RAM, as well as optional external ROM and/or RAM memory devices configured through the Ports & Flash control registers.

An intelligent peripheral I/O interface function handles other I/O interfaces, such as the on-chip MIDI UART and three timers, with minimum intervention from the control processor.

Four 16-bit I/O ports can have their bits individually configured as inputs or outputs, they can also be assigned alternate functions such as external memory access (address, data and control signals), 8-bit parallel MIDI port, serial MIDI IN/OUT, and additional digital audio-in/out.

Figure 2. Diagram of the Internal Architecture of the SAM9743

#### **DSP Engine**

The DSP engine operates on a frame-timing basis with the frame subdivided into 64 process slots. Each process is itself divided into 16 microinstructions known as "algorithms". Up to 32 DSP algorithms can be stored on-chip in the Alg RAM memory, allowing the device to be programmed for a number of audio signal generation/processing applications.

The DSP engine is capable of generating 64 simultaneous voices using algorithms such as wavetable synthesis with interpolation, alternate loop and 24 dB resonant filtering for each voice. Slots may be linked together (ML RAM) to allow implementation of more complex synthesis algorithms.

A typical musical instrument application will use a little more than half the capacity of the DSP engine for synthesis, thus providing state-of-the-art 38-voice synthesis polyphony. The remaining processing power may be used for typical functions like reverberation, chorus, surround effect, equalizer, etc.

Frequently accessed DSP parameter data are stored in five banks of on-chip RAM memory. Sample data, which is accessed relatively infrequently, can be stored in the built-in Flash memory, or in external ROM. The combination of localized micro-program memory and localized parameter data allows microinstructions to execute in 31 ns (32 MIPS). Separate buses

from each of the on-chip parameter RAM memory banks allow highly parallel data movement to increase the effectiveness of each microinstruction. With this architecture, a single microinstruction can accomplish up to 6 simultaneous operations (add, multiply, load, store, etc.), providing a potential throughput of 192 million operations per second (MOPS).

#### P16 Control Processor and I/O Functions

The P16 control processor is a general-purpose 16-bit CISC processor core, which runs from external memory. A debug ROM is included on-chip for easy development of firmware directly on the target system. This ROM also contains the necessary code to directly program the built-in Flash memory. The P16 includes 256 words of local RAM data memory for use as registers, scratchpad data and stack.

The P16 control processor writes to the parameter RAM blocks within the DSP core in order to control the synthesis process. In a typical application, the P16 control processor parses and interprets incoming commands from the MIDI UART and then controls the DSP by writing into the parameter RAM banks in the DSP core. Slowly changing synthesis functions, such as LFOs, are implemented in the P16 control processor by periodically updating the DSP parameter RAM variables.

The P16 control processor interfaces with other peripheral devices, such as the system control and status registers, the on-chip MIDI UART, the on-chip timers and the Ports & Flash control registers through specialized "intelligent" peripheral I/O logic. This I/O logic automates many of the system I/O transfers to minimize the amount of overhead processing required from the P16.

## Memory Management Unit (MMU)

The Memory Management Unit (MMU) block allows Flash and/or RAM memory resources to be shared between the synthesis/DSP and the P16 control processor. This allows the single built-in Flash memory to serve as sample memory storage for the DSP and as program storage for the P16 control processor. An internal 2K x 16 RAM is also connected to the MMU, allowing RAM resources to be shared between the DSP and the P16. Similarly, when using external memory, corresponding memory resources can be shared between the DSP and the P16.

## **Pin Description**

## **Pins by Function**

Table 1. Power Supply

| Pin Name | Pin Number                                    | Туре | Function                                                                  |

|----------|-----------------------------------------------|------|---------------------------------------------------------------------------|

| GND      | 5, 10, 18, 22, 33, 45, 47, 59, 62, 75, 88, 99 | PWR  | Digital Ground: All pins should be connected to a ground plane            |

| VC3      | 3, 11, 21, 27, 61                             | PWR  | Core Power Supply, 3V to 3.8V: All pins should be connected               |

| VCC      | 17, 31, 46, 57, 73, 87, 100                   | PWR  | I/O Power Supply, 3V to 5.5V: All pins should be connected to a VCC plane |

Note: Power supply decoupling: Like all high speed HCMOS ICs, proper decoupling is mandatory for reliable operation and RFI reduction. The recommended decoupling is 100 nF at each corner of the IC with an additional 10 µFT bulk capacitor close to the X1, X2 pins.

Table 2. Single Function Pins

| Pin Name      | Pin Number | Туре         | Function                                                                                                                                                                                                       |

|---------------|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLBD          | 26         | OUT          | External DAC serial bit clock                                                                                                                                                                                  |

| WSBD          | 37         | OUT          | External DAC left/right clock                                                                                                                                                                                  |

| DABD0         | 35         | OUT          | External DAC serial stereo audio data                                                                                                                                                                          |

| P3.12 - P3.14 | 81, 23, 24 | Programmable | General purpose I/O                                                                                                                                                                                            |

| X1            | 13         | IN           | Crystal connection, or external clock input at 256*Fs, Fs being the sampling frequency. When used as an input, a 330 ohms serial resistor should be inserted. Typical crystal frequency is 8 MHz (Fs = 32 kHz) |

| X2            | 14         | OUT          | Other end of crystal connection. Cannot be used to drive external circuitry.                                                                                                                                   |

| CKOUT         | 95         | OUT          | Buffered X2 output, can be used to drive external circuits, such as Sigma/Delta DACs                                                                                                                           |

| LFT           | 12         | Analog       | Built-in PLL compensation filter input                                                                                                                                                                         |

| RESET         | 15         | IN           | Master reset, active low, has built-in Schmitt trigger.                                                                                                                                                        |

| PDWN          | 16         | IN           | Power down, active low                                                                                                                                                                                         |

| TEST0-TEST2   | 42 - 44    | IN           | Test pins. Should be grounded for normal operation. TEST0 is used to start the built-in debugger. In this case TEST2 specifies the communication baud rate.                                                    |

Table 3. Double Function Pins

| Name #1      | Name #2     | Pin Number                                   | Function                                                                                                                                                |  |

|--------------|-------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P0.0 - P0.15 | WA0 - WA15  | 48, 51, 52, 55, 56, 58, 60, 63 - 65, 67 - 72 | #1 – General-purpose I/O<br>#2 – External expansion memory address (output)                                                                             |  |

| P1.0 - P1.15 | WD0 - WD15  | 83 - 86, 89 - 92, 96 - 98, 1,<br>2, 6, 8, 9  | #1 – General-purpose I/O<br>#2 – External expansion memory data (I/O)                                                                                   |  |

| P2.0         | WCS0        | 39                                           | #1 – General Purpose I/O<br>#2 – Expansion ROM chip select (output, active low)                                                                         |  |

| P2.1         | WCS1        | 40                                           | #1 – General-purpose I/O<br>#2 – Expansion RAM chip select (output, active low)                                                                         |  |

| P2.2         | WOE         | 41                                           | #1 – General-purpose I/O<br>#2 – Expansion memory enable (output, active low)                                                                           |  |

| P2.3         | WWE         | 38                                           | #1 – General-purpose I/O<br>#2 – Expansion RAM write enable (output, active low)                                                                        |  |

| P2.4         | RBS         | 29                                           | #1 – General-purpose I/O #2 – Expansion RAM byte select, allows connection of 8-bit external SRAM with 16-bit access in two cycles (output, active low) |  |

| P2.5 - P2.9  | WA16 - WA20 | 74, 78 - 80, 82                              | #1 – General-purpose I/O #2 – Expansion memory address, allows up to 2M x 16 external memory (output)                                                   |  |

| P2.10        | CS          | 94                                           | #1 – General-purpose I/O<br>#2 – Host processor chip select (input, active low)                                                                         |  |

| P2.11        | RD          | 77                                           | #1 – General-purpose I/O<br>#2 – Host processor read (input, active low)                                                                                |  |

| P2.12        | WR          | 76                                           | #1 – General-purpose I/O<br>#2 – Host processor write (input, active low)                                                                               |  |

| P2.13        | A0          | 66                                           | #1 – General-purpose I/O<br>#2 – Host processor data (0) – command/status (1)<br>select (input)                                                         |  |

| P2.14        | DABD1       | 36                                           | #1 - General-purpose I/O<br>#2 - Secondary DAC serial stereo audio data (output)                                                                        |  |

| P2.15        | DAAD0       | 34                                           | #1 - General-purpose I/O<br>#2 - External ADC serial stereo audio data (input)                                                                          |  |

| P3.0 - P3.7  | D0 - D7     | 25, 28, 30, 32, 49, 50, 53,<br>54            | #1 – General-purpose I/O<br>#2 – Host processor data bus (I/O)                                                                                          |  |

| P3.8         | IRQ         | 4                                            | #1 – General-purpose I/O #2 – Host processor interrupt request, active high, tri- state output                                                          |  |

| P3.9         | RUN         | 20                                           | #1 – General-purpose I/O<br>#2 – High indicates that DSP synthesis is up and<br>running                                                                 |  |

Table 3. Double Function Pins (Continued)

| Name #1 | Name #2  | Pin Number | Function                                                                        |

|---------|----------|------------|---------------------------------------------------------------------------------|

| P3.10   | MIDI IN  | 19         | #1 - General-purpose I/O<br>#2 - Serial MIDI IN (input)                         |

| P3.11   | MIDI OUT | 7          | #1 - General-purpose I/O<br>#2 - Serial MIDI OUT (output)                       |

| P3.15   | DAAD1    | 93         | #1 - General-purpose I/O<br>#2 - Secondary ADC serial stereo audio data (input) |

Table 4. Pinout by Pin Number

| Pin# | Signal Name    |

|------|----------------|

| 1    | P1.11/WD11     |

| 2    | P1.12/WD12     |

| 3    | VC3            |

| 4    | P3.8/IRQ       |

| 5    | GND            |

| 6    | P1.13/WD13     |

| 7    | P3.11/MIDI OUT |

| 8    | P1.14/WD14     |

| 9    | P1.15/WD15     |

| 10   | GND            |

| 11   | VC3            |

| 12   | LFT            |

| 13   | X1             |

| 14   | X2             |

| 15   | RESET          |

| 16   | PDWN           |

| 17   | VCC            |

| 18   | GND            |

| 19   | P3.10/MIDI IN  |

| 20   | P3.9/RUN       |

| 21   | VC3            |

| 22   | GND            |

| 23   | P3.13          |

| 24   | P3.14          |

| 25   | P3.0/D0        |

| ; [ |       |             |

|-----|-------|-------------|

|     | Pin # | Signal Name |

|     | 26    | CLBD        |

|     | 27    | VC3         |

|     | 28    | P3.1/D1     |

|     | 29    | P2.4/RBS    |

|     | 30    | P3.3/D2     |

|     | 31    | VCC         |

|     | 32    | P3.3/D3     |

|     | 33    | GND         |

|     | 34    | P2.15/DAAD0 |

|     | 35    | DABD0       |

|     | 36    | P2.14/DABD1 |

|     | 37    | WSBD        |

|     | 38    | P2.3/WWE    |

|     | 39    | P2.0/WCS0   |

|     | 40    | P2.1/WCS1   |

|     | 41    | P2.2/WOE    |

|     | 42    | TEST0       |

|     | 43    | TEST1       |

|     | 44    | TEST2       |

|     | 45    | GND         |

|     | 46    | VCC         |

|     | 47    | GND         |

|     | 48    | P0.0/WA0    |

|     | 49    | P3.4/D4     |

|     | 50    | P3.5/D5     |

|     |       |             |

| Pin # | Signal Name |

|-------|-------------|

| 51    | P0.1/WA1    |

| 52    | P0.2/WA2    |

| 53    | P3.6/D6     |

| 54    | P3.7/D7     |

| 55    | P0.3/WA3    |

| 56    | P0.4/WA4    |

| 57    | VCC         |

| 58    | P0.5/WA5    |

| 59    | GND         |

| 60    | P0.6/WA6    |

| 61    | VC3         |

| 62    | GND         |

| 63    | P0.7/WA7    |

| 64    | P0.8/WA8    |

| 65    | P0.9/WA9    |

| 66    | P2.13/A0    |

| 67    | P0.10/WA10  |

| 68    | P0.11/WA11  |

| 69    | P0.12/WA12  |

| 70    | P0.13/WA13  |

| 71    | P0.14/WA14  |

| 72    | P0.15/WA15  |

| 73    | VCC         |

| 74    | P2.5/WA16   |

| 75    | GND         |

| Pin # | Signal Name |

|-------|-------------|

| 76    | P2.12/WR    |

| 77    | P2.11/RD    |

| 78    | P2.6/WA17   |

| 79    | P2.7/WA18   |

| 80    | P2.8/WA19   |

| 81    | P3.12       |

| 82    | P2.9/WA20   |

| 83    | P1.0/WD0    |

| 84    | P1.1/WD1    |

| 85    | P1.2/WD2    |

| 86    | P1.3/WD3    |

| 87    | VCC         |

| 88    | GND         |

| 89    | P1.4/WD4    |

| 90    | P1.5/WD5    |

| 91    | P1.6 /WD6   |

| 92    | P1.7/WD7    |

| 93    | P3.15/DAAD1 |

| 94    | P2.10/CS/   |

| 95    | CKOUT       |

| 96    | P1.8/WD8    |

| 97    | P1.9/WD9    |

| 98    | P1.10/WD10  |

| 99    | GND         |

| 100   | VCC         |

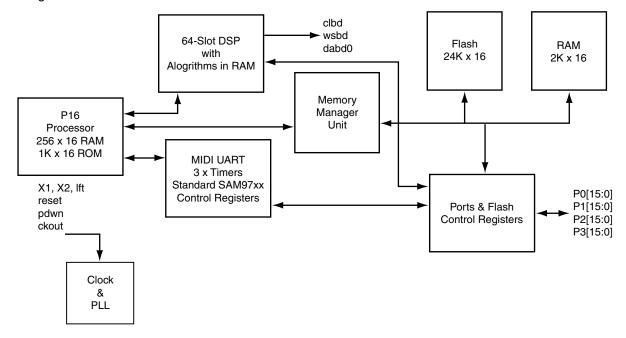

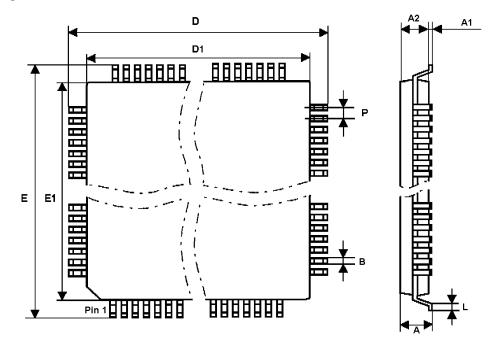

Figure 3. Package Description: PQFP100, Pitch = 0.65 mm

## **Absolute Maximum Ratings**

**Table 5.** Absolute Maximum Ratings (All Voltages with Respect to 0V, GND = 0V)

| Symbol          | Parameter                           | Min  | Тур | Max                   | Unit |

|-----------------|-------------------------------------|------|-----|-----------------------|------|

|                 | Ambient temperature (Power applied) | -40  |     | +85                   | °C   |

|                 | Storage temperature                 | -65  |     | +150                  | °C   |

|                 | Voltage on any pin (except X1)      | -0.5 |     | V <sub>CC</sub> + 0.5 | V    |

|                 | Voltage on X1 pin                   | -0.5 |     | V <sub>C3</sub> + 0.5 | V    |

| V <sub>CC</sub> | Supply voltage                      | -0.5 |     | 6.5                   | V    |

| V <sub>C3</sub> | Supply voltage                      | -0.5 |     | 4.5                   | V    |

|                 | Maximum I <sub>OL</sub> per I/O pin | _    |     | 4.4                   | mA   |

## **Recommended Operating Conditions**

Table 6. Recommended Operating Conditions

| Symbol          | Parameter                     | Min | Тур     | Max | Unit |

|-----------------|-------------------------------|-----|---------|-----|------|

| V <sub>CC</sub> | Supply voltage (I/O)          | 3   | 3.3/5.0 | 5.5 | V    |

| V <sub>C3</sub> | Supply voltage (Core)         | 3   | 3.3     | 3.8 | V    |

| t <sub>A</sub>  | Operating ambient temperature | 0   |         | 70  | °C   |

### **DC Characteristics**

**Table 7.** DC Characteristics ( $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$ ,  $V_{C3} = 3.3V \pm 10\%$ )

| Symbol          | Parameter                                             | V <sub>cc</sub> | Min  | Тур | Max       | Unit |

|-----------------|-------------------------------------------------------|-----------------|------|-----|-----------|------|

| $V_{IL}$        | Low-level input voltage                               | 3.3             | -0.5 |     | 1.0       | V    |

|                 |                                                       | 5.0             | -0.5 |     | 1.7       |      |

| V <sub>IH</sub> | High-level input voltage                              | 3.3             | 2.3  |     | VCC + 0.5 | V    |

|                 |                                                       | 5.0             | 3.3  |     | VCC + 0.5 |      |

| V <sub>OL</sub> | Low-level output voltage at I <sub>OL</sub> = -3.2 mA | 3.3             |      |     | 0.45      | V    |

|                 |                                                       | 5.0             |      |     | 0.45      |      |

| V <sub>OH</sub> | High-level output voltage at I <sub>OH</sub> = 0.8 mA | 3.3             | 2.8  |     |           | V    |

|                 |                                                       | 5.0             | 4.5  |     |           |      |

| I <sub>cc</sub> | Power supply current                                  | 3.3             |      | 60  | 80        | mA   |

|                 | (crystal frequency = 8 MHz)                           | 5.0             |      | TBD | TBD       |      |

|                 | Power down supply current                             |                 |      | TBD | 150       | μΑ   |

# Timing Diagrams

All timing conditions:  $V_{CC}$  = 5V,  $V_{C3}$  = 3.3V,  $T_A$  = 25°C, 30 pF load capacitance on all outputs except X2. All timings refer to  $t_{CK}$ , which is the internal master clock period.

$t_{CK} = t_{XTAL}/4$  (typ 31.25 ns).

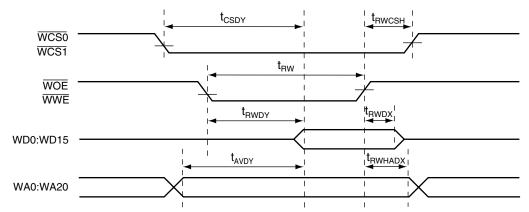

# External Memory (16 bits)

Figure 4. External ROM/RAM (16 bits)

Table 8. Parameters for External Memory Read/Write Cycle (16 bits)

| Symbol              | Parameter                             | Min                     | Тур                 | Max | Unit |

|---------------------|---------------------------------------|-------------------------|---------------------|-----|------|

| t <sub>CSDV</sub>   | Access time from WCSx low             | 5 * t <sub>CK</sub> - 5 |                     |     | ns   |

| t <sub>RWDV</sub>   | Access time from WOE, WWE low         | 3 * t <sub>CK</sub> - 5 |                     |     | ns   |

| $t_{AVDV}$          | Access time from address valid        | 5 * t <sub>CK</sub> - 5 |                     |     | ns   |

| t <sub>RW</sub>     | WOE, WWE pulse width                  |                         | 4 * t <sub>CK</sub> |     | ns   |

| t <sub>RWHCSH</sub> | WCSx high from rising WOE or WWE      | 10                      |                     |     | ns   |

| t <sub>RWHADX</sub> | Address valid after rising WOE or WWE | 10                      |                     |     | ns   |

| t <sub>RWDX</sub>   | Data hold time from rising WOE or WWE | 10                      | 6 * t <sub>CK</sub> |     | ns   |

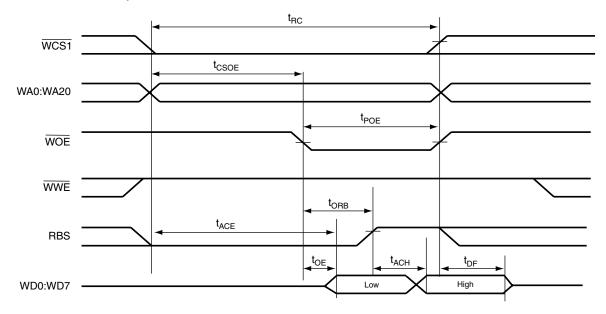

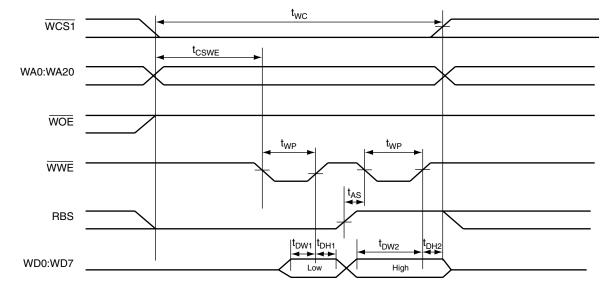

## **External Ram (8 bits)**

Figure 5. 8-bit SRAM Read Cycle

Note: By setting the SRAM 8-bit in the P16 control word, external RAM can be configured to read 16-bit with 2 x 8-bit accesses.

Figure 6. 8-bit SRAM Write Cycle

Table 9. Parameters for External 8-bit SRAM Read/Write

| Symbol            | Parameter                                  | Min                        | Тур                 | Max                     | Unit |

|-------------------|--------------------------------------------|----------------------------|---------------------|-------------------------|------|

| t <sub>RC</sub>   | Word (2 x bytes) read cycle time           | 5 * t <sub>CK</sub>        |                     | 6 * t <sub>CK</sub>     | ns   |

| t <sub>CSOE</sub> | Chip select low. Address valid to WOE low  | 2 * t <sub>CK</sub> - 5    |                     | 3 * t <sub>CK</sub> + 5 | ns   |

| t <sub>POE</sub>  | Output enable pulse width                  |                            | 3 * t <sub>CK</sub> |                         | ns   |

| t <sub>ACE</sub>  | Chip select. Access low byte access time.  | 3 * t <sub>CK</sub> - 5    |                     |                         | ns   |

| t <sub>OE</sub>   | Output enable low byte access time         | t <sub>CK</sub> - 5        |                     |                         | ns   |

| t <sub>ORB</sub>  | Output enable low to byte select high      |                            | t <sub>CK</sub>     |                         | ns   |

| t <sub>ACH</sub>  | Byte select high byte access time          | 2 * t <sub>CK</sub> - 5    |                     |                         | ns   |

| t <sub>DF</sub>   | Chip select or WOE high to input data HI-Z | 0                          |                     | 2 * t <sub>CK</sub> - 5 | ns   |

| t <sub>WC</sub>   | Write (2 x bytes) write cycle time         | 5 * t <sub>CK</sub>        |                     | 6 * t <sub>CK</sub>     | ns   |

| t <sub>CSWE</sub> | 1st WWE low from CS or address or WOE      | 2 * t <sub>CK</sub> - 10   |                     |                         | ns   |

| t <sub>WP</sub>   | Write (low and high byte) pulse width      | 1.5 * t <sub>CK</sub> - 5  |                     |                         | ns   |

| t <sub>DW1</sub>  | Data out low byte setup time               | 1.5 * t <sub>CK</sub> - 10 |                     |                         | ns   |

| t <sub>DH1</sub>  | Data out low byte hold time                | 0.5 * t <sub>CK</sub> + 10 |                     |                         | ns   |

| t <sub>AS</sub>   | RBS high to second write pulse             | 0.5 * t <sub>CK</sub> - 5  |                     |                         | ns   |

| t <sub>DW2</sub>  | Data out high byte setup time              | 2 * t <sub>CK</sub> - 10   |                     |                         | ns   |

| t <sub>DH2</sub>  | Data out high byte hold time               | 10                         |                     |                         | ns   |

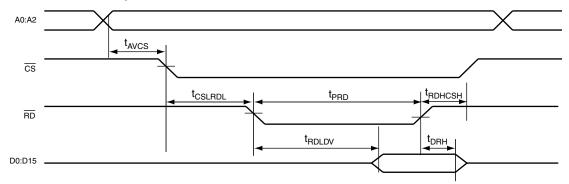

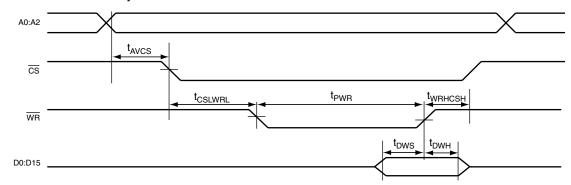

#### **Parallel Interface**

Figure 7. Host Interface Read Cycle

Figure 8. Host Interface Write Cycle

Table 10. Parameters for the Parallel Interface

| Symbol               | Parameter                                 | Min | Тур | Max | Unit |

|----------------------|-------------------------------------------|-----|-----|-----|------|

| t <sub>AVCS</sub>    | Address valid to chip select low          | 0   |     |     | ns   |

| t <sub>CSLRDL</sub>  | Chip select low to $\overline{RD}$ low    | 5   |     |     | ns   |

| t <sub>RDHCSH</sub>  | RD high to CS high                        | 5   |     |     | ns   |

| t <sub>PRD</sub>     | RD pulse width                            | 50  |     |     | ns   |

| t <sub>RDLDV</sub>   | Data out valid from RD                    |     |     | 20  | ns   |

| t <sub>DRH</sub>     | Data out hold from $\overline{\text{RD}}$ | 5   |     | 10  | ns   |

| t <sub>CSLRWRL</sub> | Chip select low to WR low                 | 5   |     |     | ns   |

| t <sub>WRHCSH</sub>  | WR high to CS high                        | 5   |     |     | ns   |

| t <sub>PWR</sub>     | WR pulse width                            | 50  |     |     | ns   |

| t <sub>DWS</sub>     | Write data setup time                     | 10  |     |     | ns   |

| t <sub>DWH</sub>     | Write data hold time                      | 0   |     |     | ns   |

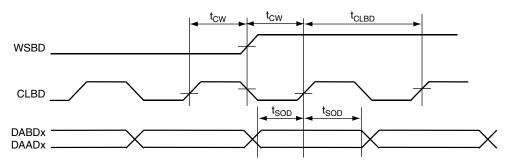

## **Digital Audio Timing**

Figure 9. Digital Audio Timing Diagram

Figure 10. Digital Audio Frame Format

Table 11. Digital Audio Timing Parameters

| Symbol            | Parameter                                 | Min                      | Тур                  | Max | Unit |

|-------------------|-------------------------------------------|--------------------------|----------------------|-----|------|

| t <sub>CW</sub>   | CLBD rising to WSBD change                | 8 *t <sub>CK</sub> - 10  |                      |     | ns   |

| t <sub>SOD</sub>  | DABDx/DAADx valid prior/after CLBD rising | 8 * t <sub>CK</sub> - 10 |                      |     | ns   |

| t <sub>CLBD</sub> | CLBD cycle time                           |                          | 16 * t <sub>CK</sub> |     | ns   |

# Overview of Operation

This section limits its contents to a description of the operation and registers specific to the SAM9743. A familiar understanding of the SAM97xx series operation is required.

## Normal Operation Mode

TEST2 = TEST1 = TEST0 = O:

In this mode, the built-in Flash is assumed to be already programmed. After RESET, all pins are in configuration #1 and all general purpose I/Os (64 pins) are in input mode with a weak pull-down resistor.

The P16 program starts at address 8000H, which is the first word of the internal Flash.

The program coded in Flash or into external memory has access to nine specific 16-bit registers as follows.

#### I/O Configuration Register (Read/Write), Address 20:0808H

| D15 | D14 | D13         | D12        | D11 | D10   | D9    | D8  | D7   | D6   | D5   | D4   | D3   | D2   | D1  | D0  |

|-----|-----|-------------|------------|-----|-------|-------|-----|------|------|------|------|------|------|-----|-----|

| Х   | Х   | MIDI<br>OUT | MIDI<br>IN | RUN | DAAD0 | DAAD1 | IRQ | HOST | AD20 | AD19 | AD18 | AD17 | AD16 | ROM | RAM |

This register is cleared at reset. A one written to the register indicates that the corresponding alternate configuration #2 is selected as follows:

- RAM: WA0 WA15, WD0 WD7, WCS1, WOE, WWE, RBS

- ROM: WCS0, W8 W15

- AD16 to AD20: Respective AD16 to AD20 signals

- HOST: CS, RD, WR, A0, D0 D7

- IRQ: IRQ

- DABD1, DABD0, RUN, MIDI IN, MIDI OUT: Corresponding pins

## I/O Direction Registers (Read/Write), Address 20:0804H to 20:0807H

These four registers (one for each General-purpose I/O port P0 to P3) are cleared at reset, thus putting all port bits in input mode.

A one in a given bit position configures the corresponding port bit in output mode (assuming that no alternate function is selected for the port bit).

#### I/O Data Write Registers (Read/Write), Address 20:0800H to 20:803H

These four registers (one for each General Purpose I/O port P0 to P3) are cleared at power-up. A 0/1 written in a given bit position sets the corresponding port bit to 0/1, assuming that no alternate function is selected for the port bit and that the port bit is in output mode.

A read from the register always returns the value written to the register independently of the actual port configuration.

#### I/O Data Reads Registers (read only), address 20:810H to 20:0813H

A read from these registers always returns the value of the pins independently of the configuration. For example, suppose that P3.10 is configured as MIDI IN, then setting the direction to output and writing data to P3.10 will have no effect. However, the actual value of the MIDI IN pin would be read.

### On Board Flash Program/Debug Mode

TEST1 = 0, TEST0 = 1:

In this mode, the P16 program starts in the built-in debug ROM. All ports are set to input mode with a weak pull-down, except P3.10 and P3.11 which are set to MIDI IN and MIDI OUT, respectively.

If TEST2 = 0, the baud rate is set to the MIDI standard (31250 baud). If TEST2 = 1 the baud rate is set to 57600 baud. This later setting is useful when Flash programming time is a production cost issue.

Programming the built-in Flash, or debugging a P16 program, occurs exclusively through the MIDI IN and MIDI OUT pins, which means that any firmware can be debugged except the MIDI part of the firmware (note that as the SAM9743 is compatible with the SAM97xx series, it is easy to debug the MIDI with another development board such as 97PNP2).

#### **MIDI IN Commands**

The following is only given for information purposes, as the CV9743 CodeView debugger takes care of all the protocol handling between a PC and the SAM9743 target board.

Commands are received through MIDI IN, all commands except GO and GR are acknowledged. A new command should not be sent until the acknowledge from a previous command is received.

Note that the commands are compatible with the standard Debug program from the SAM97xx series.

The first command sent to the SAM9743 after reset should be INIT (0F0H).

Table 12. Parameters for MIDI IN/MIDI OUT Commands and Answers

| MIDI IN<br>Command | Byte<br>Parameters                   | MIDI OUT<br>Answer | Description                                                                                                                                                                                                     |

|--------------------|--------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT 0F0H          | _                                    | Ack (0ACH)         | Establish link. This should be the first command sent after reset.                                                                                                                                              |

| RDIRAM 00H         | ad                                   | dl, dh             | Read P16 IRAM at ad                                                                                                                                                                                             |

| WRIRAM 01H         | ad, dl, dh                           | Ack (0ACH)         | Write dh/dl at P16 IRAM address ad                                                                                                                                                                              |

| RDXTMEM<br>02H     | adl, adh, pl, ph                     | dl, dh             | Read word of P16 external memory at address ph/pl:adh/adl. Note that from a P16 point of view, the built-in Flash and 2K x 16 SRAM are external memory.                                                         |

| WRXTMEM<br>03H     | adl, adh, pl,<br>ph, dl, dh          | Ack (0ACH)         | Write dh/dl word of data to P16 external memory at address ph/pl:adh/adl. If the address falls into the Flash range, then Flash-programming algorithm is applied. Ack is returned after the write is completed. |

| RDIO 04H           | ioad                                 | dl, dh             | Read P16 I/O at ioad                                                                                                                                                                                            |

| WRIO 05H           | ioad, dl, dh                         | Ack (0ACH)         | Write dh/dl at I/O address ioad                                                                                                                                                                                 |

| RDSAML 06H         | samadl,<br>samadh                    | dl, dh             | Read low word of synthesis DSP RAM at samadh/samadl                                                                                                                                                             |

| RDSAMH 07H         | samadl,<br>samadh                    | dl, dh             | Read high word of synthesis DSP RAM at samadh/samadl                                                                                                                                                            |

| WRSAM 08H          | samadl,<br>samadh, d0,<br>d1, d2, d3 | Ack (0ACH)         | Write 32 bits (d3/d2/d1/d0) of data to Synthesis DSP RAM at address samadh/samadl                                                                                                                               |

| GO 09H             | adl, adh                             | See note           | Jump to adh/adl (start firmware)                                                                                                                                                                                |

| GR 0AH             | Dummy                                | See note           | Restore firmware context                                                                                                                                                                                        |

| RDBLOCK<br>0BH     | adl, adh, pl,<br>ph, sizel, sizeh    | 2*size bytes       | Read size words of external memory starting at address ph/pl/adh/adl                                                                                                                                            |

**Table 12.** Parameters for MIDI IN/MIDI OUT Commands and Answers (Continued)

| WRBLOCK<br>0CH  | adl, adh, pl,<br>ph, sizel,<br>sizeh, 2*size<br>data bytes | Ack (0ACH) | Write size words to external memory starting at address ph/pl:adh/adl. This will NOT work if the address is in the Flash range. Use WRFLASH command for block programming of the built-in Flash.                                                                                          |

|-----------------|------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRFLASH<br>0DH  | adl, adh, size,<br>2*size bytes                            | Ack (0ACH) | Write size words (max 32) to Flash, starting at address 8000H + adh/adl. The block written shall not cross a 32 words Flash page. Before actually writing to the Flash, Ack is returned immediately after the last data byte is received, thereby allowing masked time Flash programming. |

| CHKFLASH<br>0EH | Dummy                                                      | Ack (0ACH) | Ack is returned when the current Flash write has been completed, thus allowing monitoring of the completion of the last WRFLASH.                                                                                                                                                          |

#### **Breakpoint Settings**

Breakpoint is set by replacing a firmware instruction by the single word ROM Debug instruction. This instruction jumps into the ROM debug code, saves the caller program context and sends data AAH, 55H to MIDI OUT. This signals the 9743CV program that a breakpoint has been reached. Further program execution will be done by restoring the instruction at the breakpoint address, modifying the context stack (IP = IP-1) and issuing a GR command. The GR command restores the user program context and resumes execution at the restored instruction.

#### Debugger Requirements

The debugger needs the following resources to operate:

- One word at address 18H in IRAM

- 18 words of stack

- 8 words starting at address 20:0000H in built-in SRAM for FIFO

An additional 32 words of SRAM (20:0008H to 20:0027H) are needed for block Flash programming (WRFLASH).

Specific Flash functions such as chip erase, signature fuse, etc. can be externally triggered by using combinations of the above commands.

## **Flash Program and Test Registers**

Three additional write I/O registers and two read I/O registers are implemented for the built-in Flash program and test, as follows.

#### FADDTEST Register (Read/Write), Address 0020:080AH

This 15-bit register provides the addtest<14:0> address bus to the Flash block. This is the address register when programming the Flash.

### FDI Register (Read/Write), Address 0020:080BH

This 16-bit register provides the di<15:0> data bus to the Flash block. This is the data register when programming the Flash.

#### FCOMMAND Register (Read/Write), Address 0020:0809H

(Cleared at RESET time)

| D15 | D14 | D13 | D12 | D11 | D10  | D9  | D8 | D7    | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|------|-----|----|-------|-------|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     | Rstt | Cen | We | Pagem | Page1 | Tm5 | Tm4 | Tm3 | Tm2 | Tm1 | Tm0 |

<sup>•</sup> Rstt,Cen, We, Pagem, Page1,Tm5–Tm0: Signals sent to corresponding Flash block inputs. These signals, with proper timing, provide Flash programming.

#### FSTATUS Register (Read-only), Address 0020:0809H

| D15 | D14 | D13 | D12 | D11 | D10   | D9    | D8    | D7 | D6 | D5 | D4 | D3 | D2 | D1     | D0      |

|-----|-----|-----|-----|-----|-------|-------|-------|----|----|----|----|----|----|--------|---------|

| Х   | Х   | Х   | Х   | Х   | Test2 | Test1 | Test0 | Х  | Х  | Х  | Χ  | Х  | Х  | Douten | Rdybsyn |

- Rdybsyn and Douten: These Flash signals provide write-progress monitoring respectively.

- Test0-Test2: Input pins, respectively.

#### **FDOTEST Register (Read-only)**

Reads the dotest <15:0> Flash data output bus for test modes.

## **Memory Map**

Table 13. Description of the SAM97'3 Memory Map

| Address low | Address High | Access                                          |

|-------------|--------------|-------------------------------------------------|

| 0000:0000   | 0000:00FF    | SAM97xx Standard Routine ROM                    |

| 0000:0100   | 0000:03FF    | Built-in ROM for Flash program & debug routines |

| 0000:400    | 0000:7FFF    | Optional external ROM                           |

| 0000:8000   | 0000:DFFF    | Built-in Flash (24K x 16)                       |

| 0000:E000   | 001F:FFFF    | Optional external ROM (WCSO)                    |

| 0020:0000   | 0020:07FF    | Built-in SRAM (2K x 16)                         |

| 0020:0800   | 0020:0815    | SAM9743 specific I/Os                           |

| 0020:0816   | 01FF:FFFF    | Not used                                        |

| 0200:0000   | 021F:FFFF    | Optional external RAM (WCS1)                    |

Note: If programmed as an alternate function,  $\overline{WCSO}$  is generated even if the firmware accesses the built-in Flash or ROM. In this case the external ROM data is not used.

## Flash Programing Performance

Typical programming times for the 24K x 16 Flash are as follows:

MIDI baud rate 31250 bauds, TEST0 = 1, TEST2 =0: 33 seconds

57600 bauds, TEST0 = 1, TEST2= 1: 19 seconds

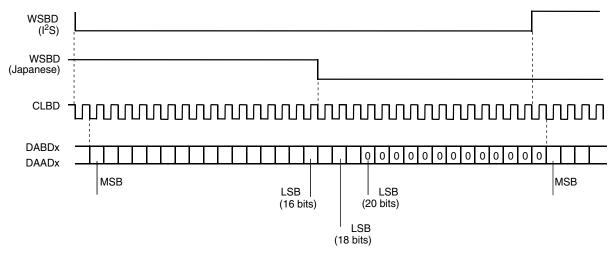

## Crystal Compensation/ LFT Filter

Figure 11. Recommended Crystal Compensation and LFT Filter

Note: The SAM9743 uses a low power oscillator. No compensation capacitor is necessary. However, because the crystal drive is very small, it is mandatory to keep the X1/X2 traces as small as possible.

## **Mechanical Dimensions**

Figure 12. SAM9743 Mechanical Dimensions

Table 14. SAM9743 Plastic Lead Quad Flat Pack (PQFP100)

|    | Min  | Nom  | Max  |

|----|------|------|------|

| Α  |      |      | 3.4  |

| A1 | 0.25 |      |      |

| A2 | 2.55 | 2.8  | 3.05 |

| D  |      | 17.9 |      |

| D1 |      | 14.0 |      |

| Е  |      | 23.9 |      |

| E1 |      | 20   |      |

| L  | 0.65 | 0.88 | 1.03 |

| Р  |      | 0.65 |      |

| В  | 0.22 |      | 0.38 |

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd.

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimhatsui

East Kowloon

Hong Kong

TEL (852) 2721-9778

FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

#### **Atmel Nantes**

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### **Atmel Smart Card ICs**

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

e-mail literature@atmel.com

Web Site http://www.atmel.com

*BBS* 1-(408) 436-4309

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® is the registered trademark of Atmel. Windows® is the registered trademark of Microsoft Corporation.

Other terms and product names may be the trademarks of others.