# SH7707 Reference Platform

for Microsoft® Windows® CE (PFM-DS4)

Application Notes (Hardware Guide)

# HITACHI

ADE-000-000 Rev.0.1 12/10/98 Hitachi Company or Division

### **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# Contents

| Secti | on 1    | Overview                                         | 1  |

|-------|---------|--------------------------------------------------|----|

| Secti | on 2    | Basic Specifications                             | 5  |

| Secti | on 3    | System Configuration                             | 9  |

| 3.1   | System  | Configuration Diagram                            | 11 |

| 3.2   | Memor   | y Map                                            | 12 |

| 3.3   | Mode S  | Setting                                          | 13 |

| 3.4   | Interru | pts                                              | 14 |

| 3.5   | SH770   | 7 Register Initial Values in Reference Platform  | 15 |

| 3.6   | SH770   | 7 Pin Assignment                                 | 22 |

| 3.7   | Connec  | ctor Pin Arrangement                             | 27 |

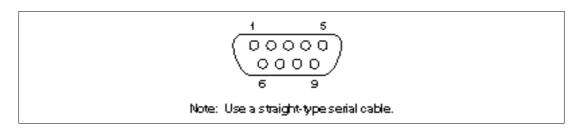

|       | 3.7.1   | Serial Connector                                 | 27 |

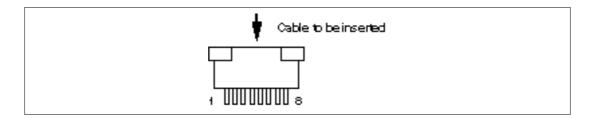

|       | 3.7.2   | Touch Panel Connector                            | 27 |

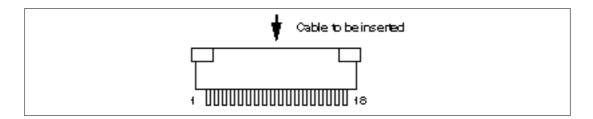

|       | 3.7.3   | LCD Connector                                    | 28 |

|       | 3.7.4   | Keyboard Connectors                              | 28 |

|       | 3.7.5   | Expansion Bus Connector                          | 29 |

| 3.8   | Referen | nce Platform Start-Up                            | 32 |

|       | 3.8.1   | Starting Microsoft® Windows® CE Operating System | 32 |

|       | 3.8.2   | Starting Monitor Program                         | 32 |

|       | 3.8.3   | Installing Flash Memory                          | 34 |

| Secti | on 4    | Function Specifications                          | 35 |

| 4.1   | Memor   | y                                                | 37 |

|       | 4.1.1   | DRAM                                             | 37 |

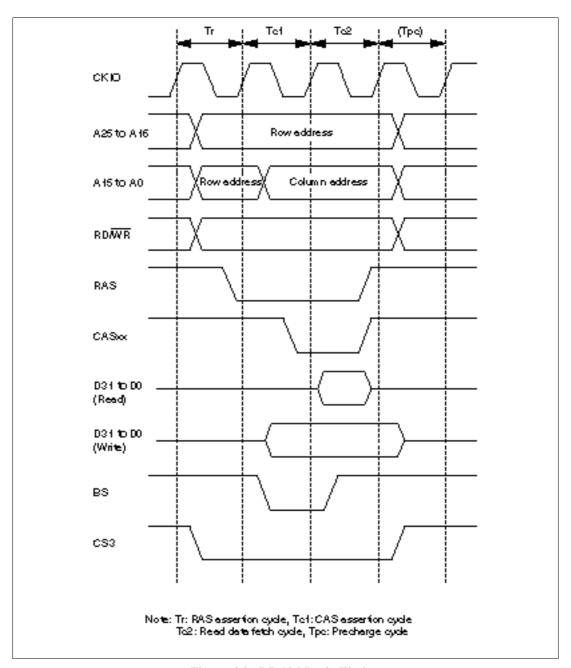

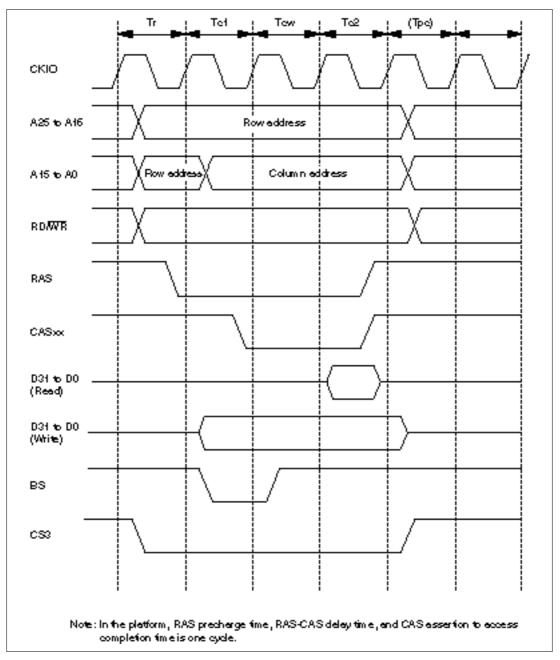

|       | 4.1.2   | Timing Chart                                     | 39 |

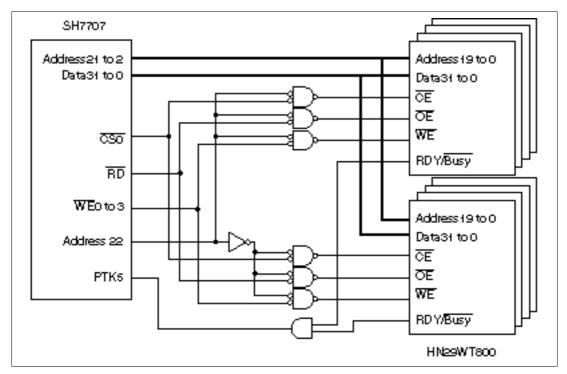

|       | 4.1.3   | Flash Memory                                     | 41 |

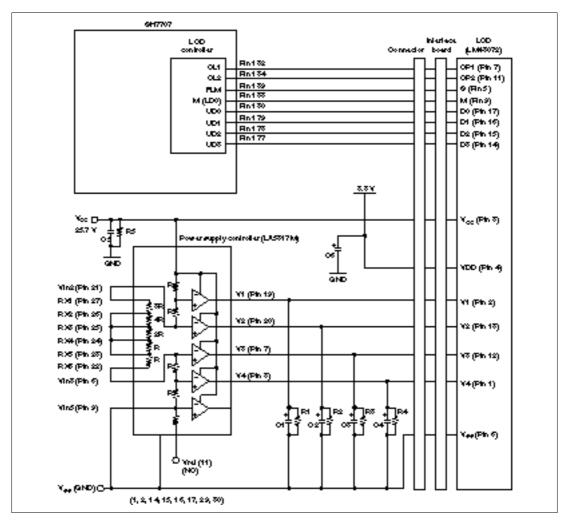

| 4.2   | LCD     |                                                  | 43 |

|       | 4.2.1   | Interface Block Diagram                          | 43 |

|       | 4.2.2   | Display Mode                                     | 44 |

|       | 4.2.3   | SH7707/LCDC Pin Configuration                    | 44 |

|       | 4.2.4   | Register Configuration                           | 45 |

|       | 4.2.5   | LCD Pin Configuration                            | 45 |

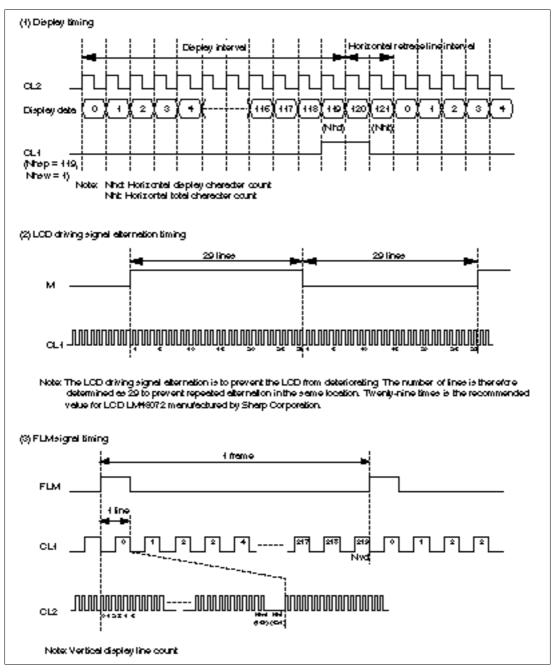

|       | 4.2.6   | LCDC Interface Timing                            | 46 |

|       | 4.2.7   | Setting LCDC Register                            | 47 |

| 4.3   | PCMC:   | IA                                               | 59 |

|       | 4.3.1   | PC Card Controller (PCC)                         | 59 |

|       | 4.3.2   | Features                                         | 59 |

|       | 4.3.3   | Physical Areas                                   | 59 |

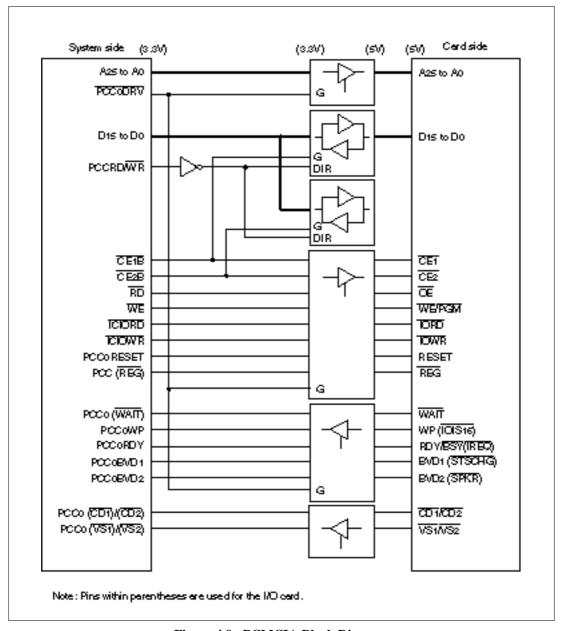

|     | 4.3.4  | PCMCIA Block Diagram                                                | 61  |

|-----|--------|---------------------------------------------------------------------|-----|

|     | 4.3.5  | PCMCIA Pin Function (Control Signal)                                | 62  |

|     | 4.3.6  | Register Configuration                                              | 63  |

|     | 4.3.7  | Pin Description                                                     | 72  |

|     | 4.3.8  | Card Detection                                                      | 73  |

|     | 4.3.9  | Battery Voltage Detection                                           | 74  |

|     | 4.3.10 | Wait Cycle Insertion                                                | 74  |

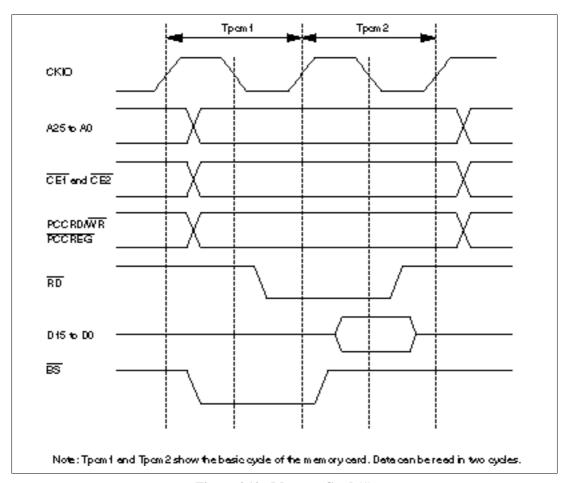

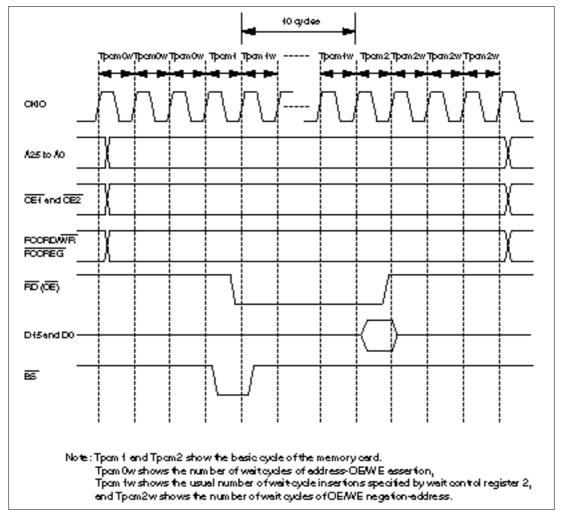

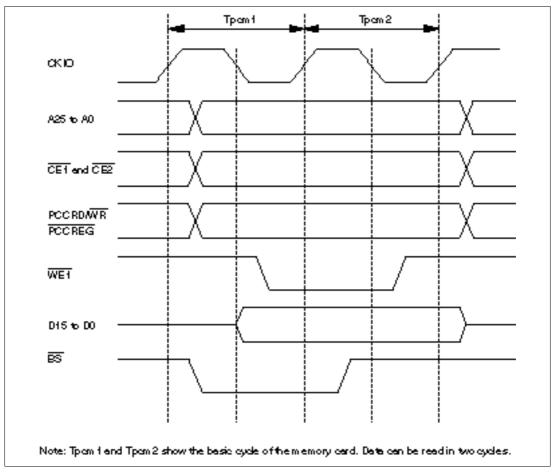

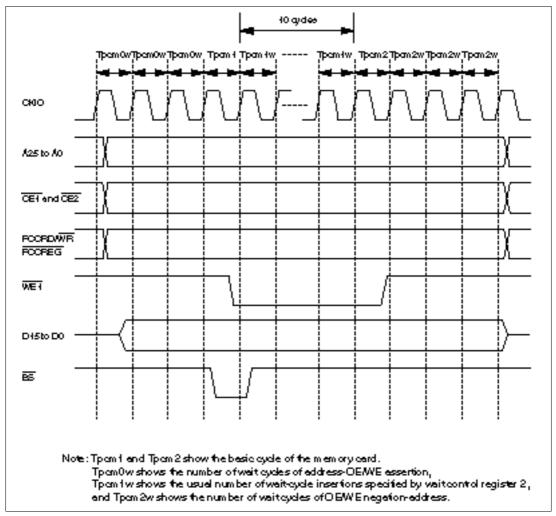

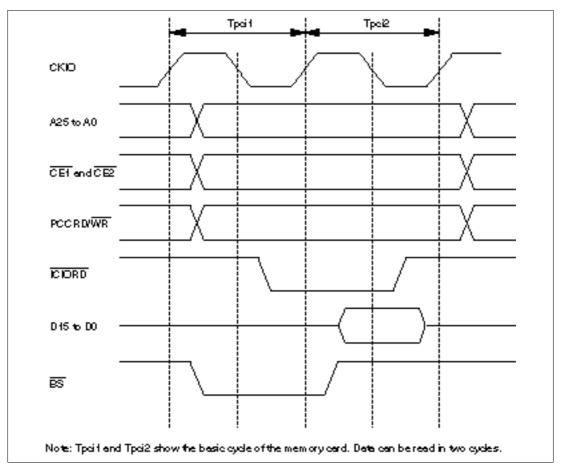

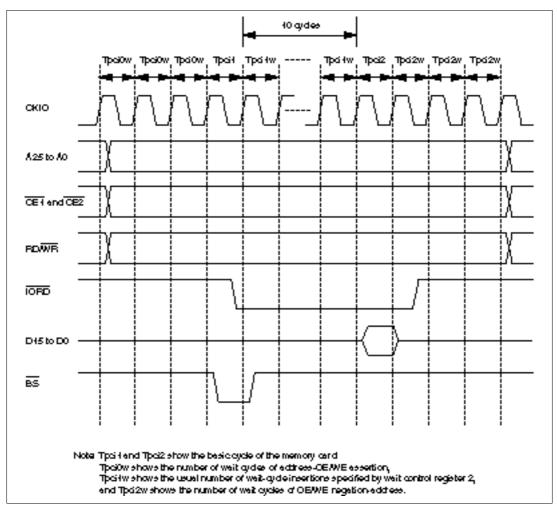

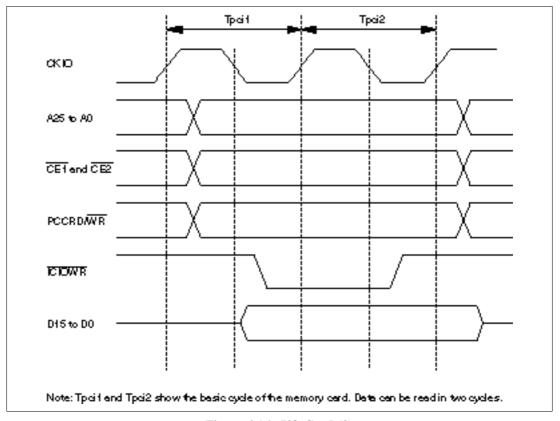

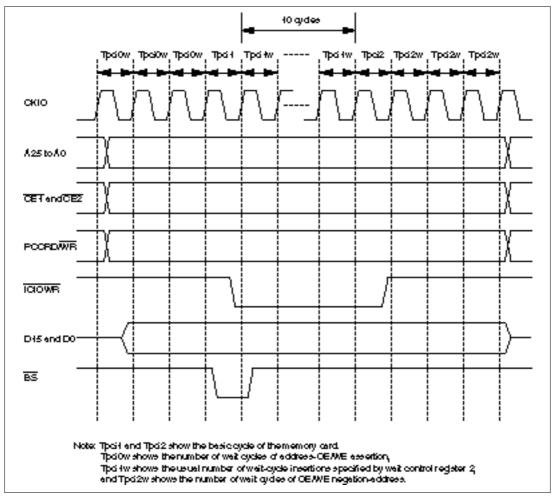

|     | 4.3.11 | Timing Chart                                                        | 76  |

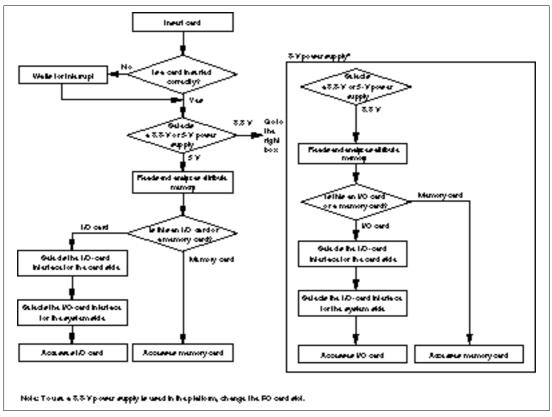

|     | 4.3.12 | Operation for Inserting the Card and Accessing the Card             | 84  |

|     | 4.3.13 | Voltage Detection                                                   | 85  |

|     | 4.3.14 | Card Access Mode Selection                                          | 86  |

|     | 4.3.15 | Power-Supply Control                                                | 86  |

|     | 4.3.16 | Power-Supply Control for Programming                                | 86  |

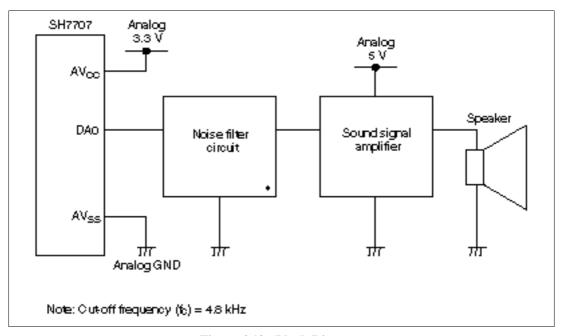

| 4.4 |        | Play-Back                                                           | 87  |

|     | 4.4.1  | Audio-Play-Back Block Diagram                                       | 87  |

|     | 4.4.2  | SH7707 DAC Output Specification                                     | 87  |

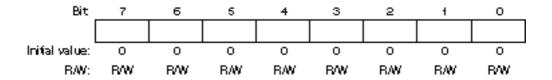

|     | 4.4.3  | SH7707 Pin Specification                                            | 88  |

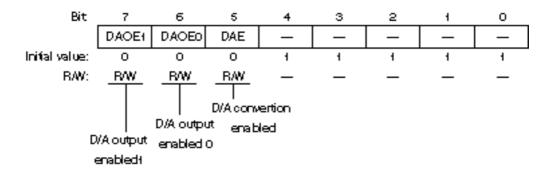

|     | 4.4.4  | List of SH7707 D/A Converter Registers                              | 88  |

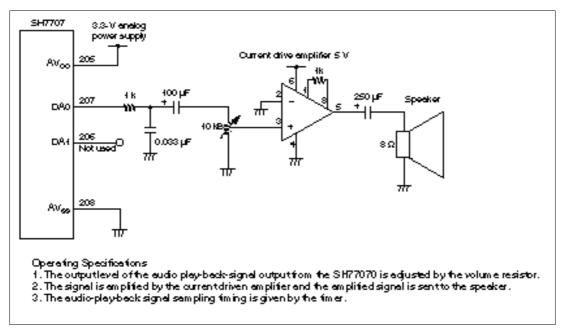

|     | 4.4.5  | Circuit Diagram                                                     | 90  |

| 4.5 | Touch  | Panel Section                                                       | 91  |

|     | 4.5.1  | Features                                                            | 91  |

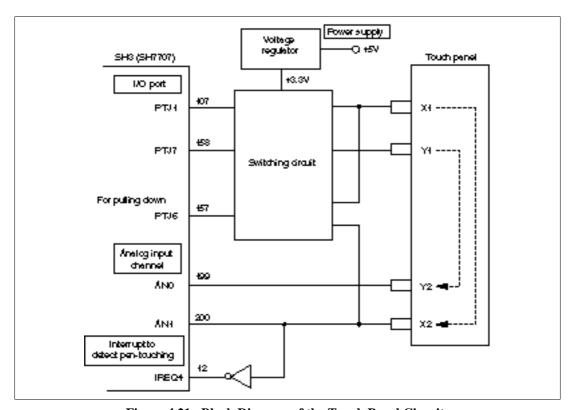

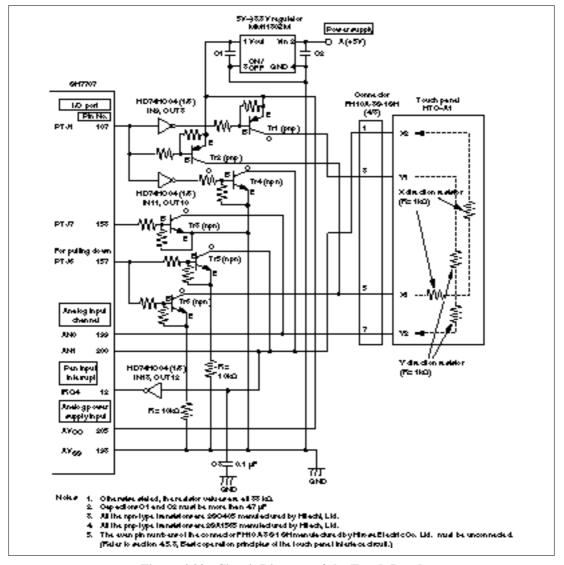

|     | 4.5.2  | Block Diagram                                                       | 91  |

|     | 4.5.3  | Pin Function of the A/D Converter                                   | 92  |

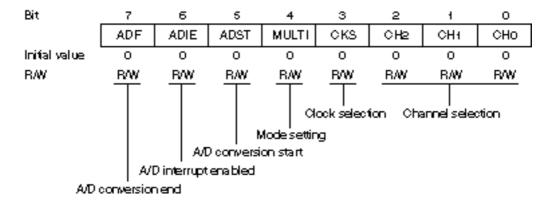

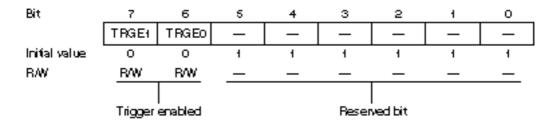

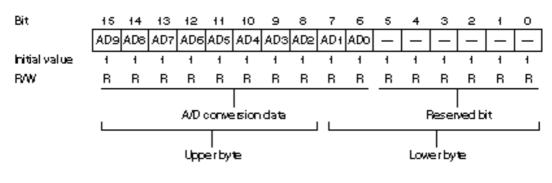

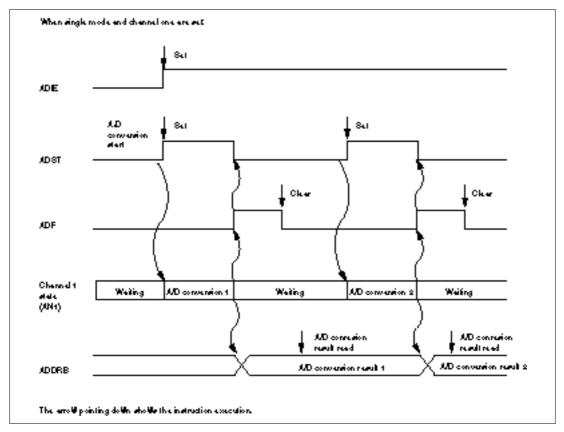

|     | 4.5.4  | Registers for the A/D converter                                     | 93  |

|     | 4.5.5  | Circuit Diagram                                                     | 96  |

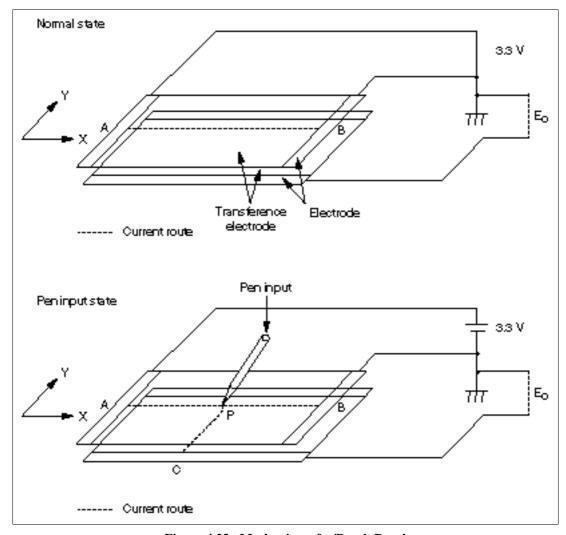

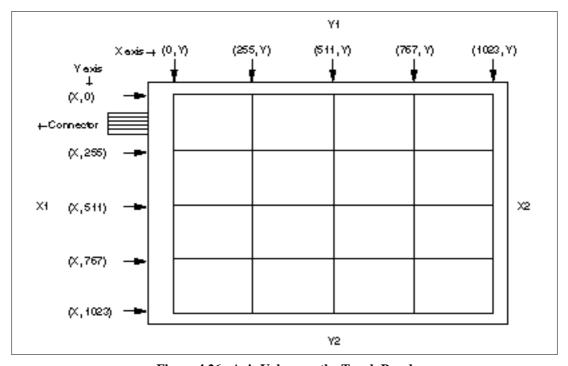

|     | 4.5.6  | Touch Panel Mechanism                                               | 97  |

|     | 4.5.7  | Operation of the A/D Converter                                      | 98  |

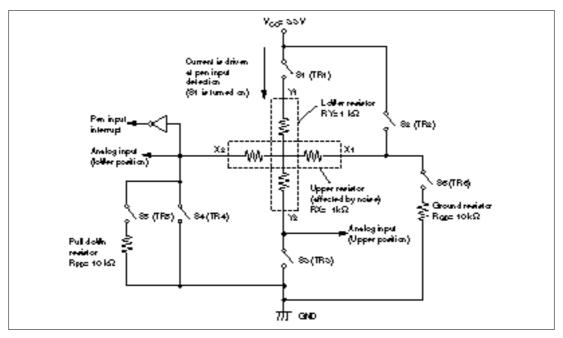

|     | 4.5.8  | The Basic Operation Principle of the Touch Panel Interface Circuits |     |

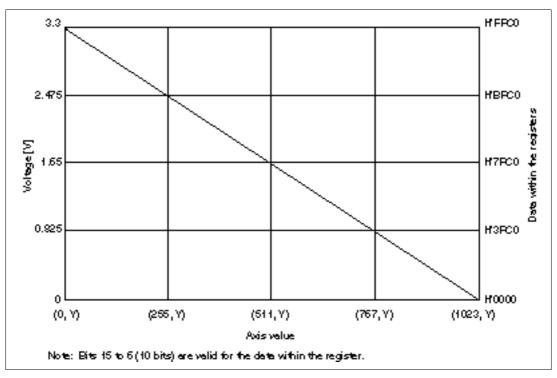

|     | 4.5.9  | The Relation between the Touch Panel Axes and the Output Voltage    |     |

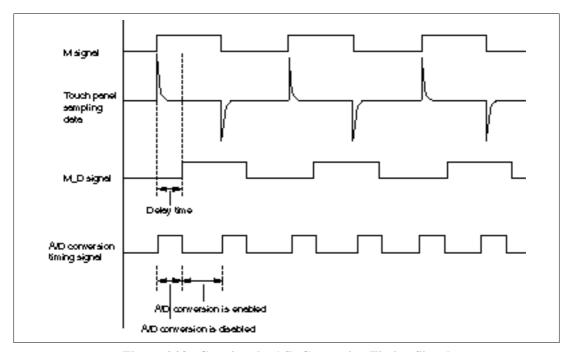

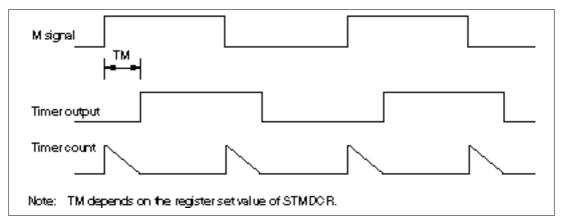

|     | 4.5.10 | Canceling the Noise Using the LCD M Signal                          | 101 |

| 4.6 | SCI Se | ction                                                               |     |

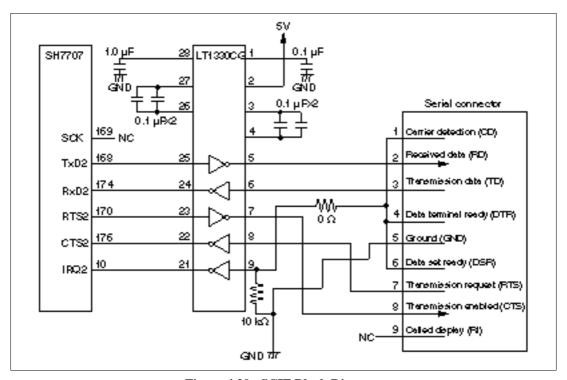

|     | 4.6.1  | Interface Block Diagram                                             | 103 |

|     | 4.6.2  | Pin Configuration.                                                  | 103 |

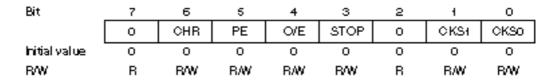

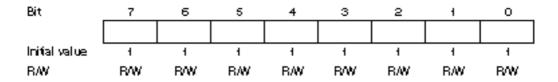

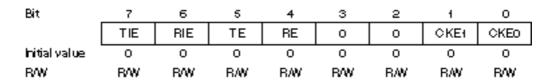

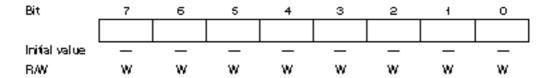

|     | 4.6.3  | Register Configuration                                              | 104 |

| 4.7 | IrDA S | ection                                                              |     |

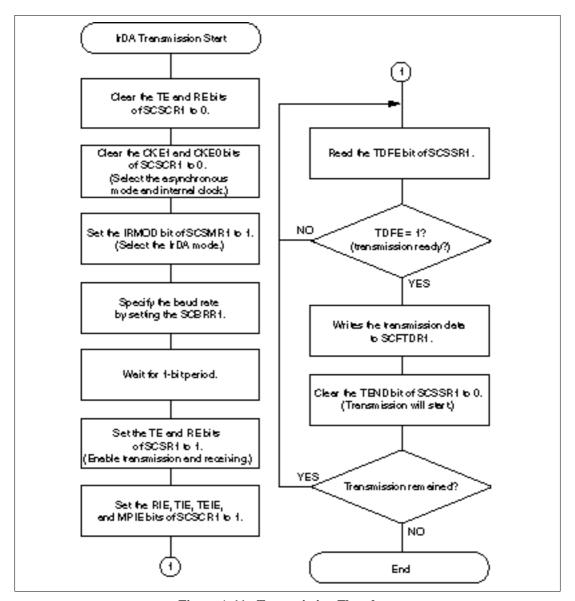

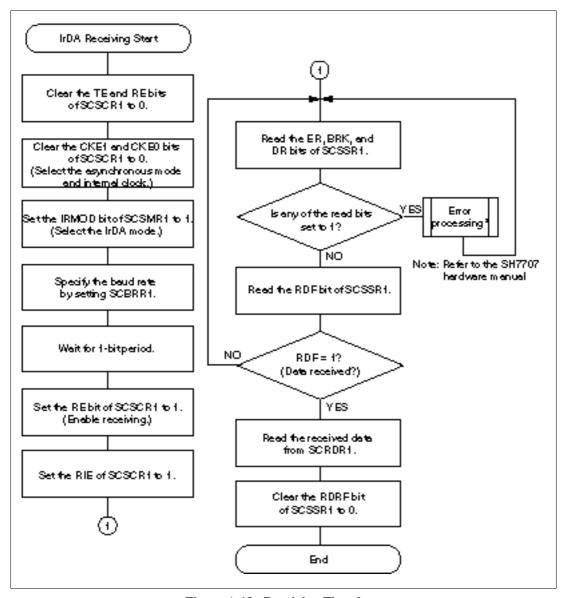

|     | 4.7.1  | Features                                                            | 112 |

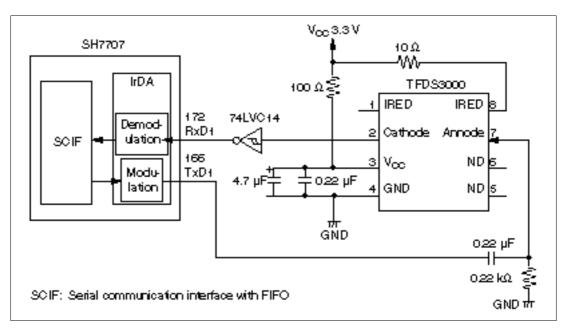

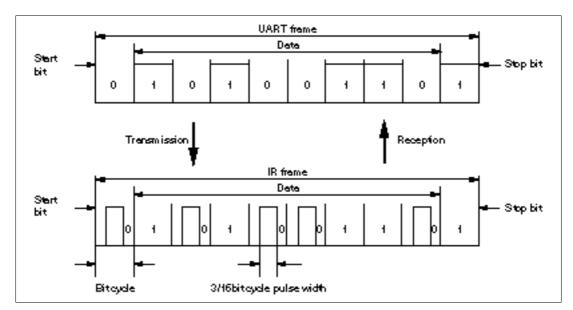

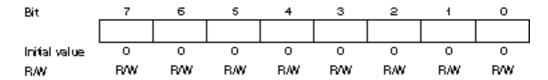

|     | 4.7.2  | IrDA Interface Block Diagram                                        | 112 |

|     | 4.7.3  | Pin Configuration                                                   |     |

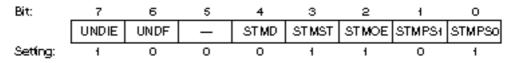

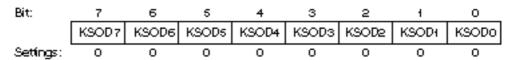

|     | 4.7.4  | Register Configuration                                              |     |

|     | 4.7.5  | Description of Each Register                                        |     |

|     | 4.7.6  | Operation Description                                               |     |

| 4.8 |        | Section                                                             |     |

|     |        |                                                                     | 116 |

|      | 4.8.2   | Register Address Map and IRQ Allocation | 117 |

|------|---------|-----------------------------------------|-----|

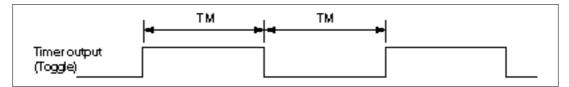

|      | 4.8.3   | Timer                                   | 118 |

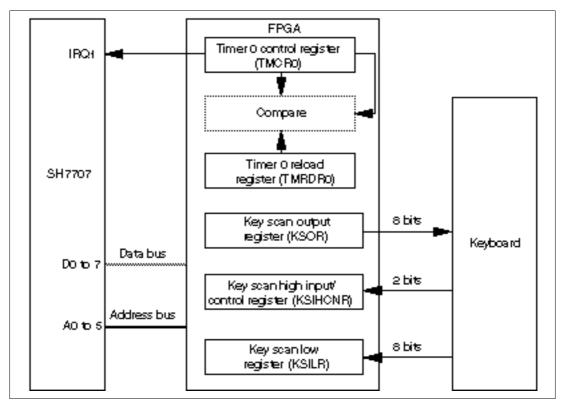

|      | 4.8.4   | Key Scan Control                        | 121 |

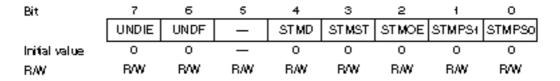

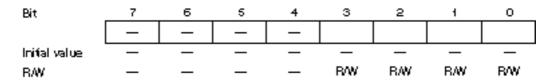

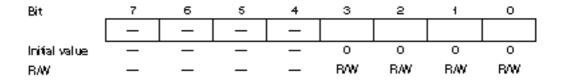

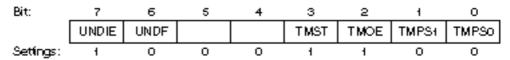

|      | 4.8.5   | Touch-Panel Sampling Timer              | 123 |

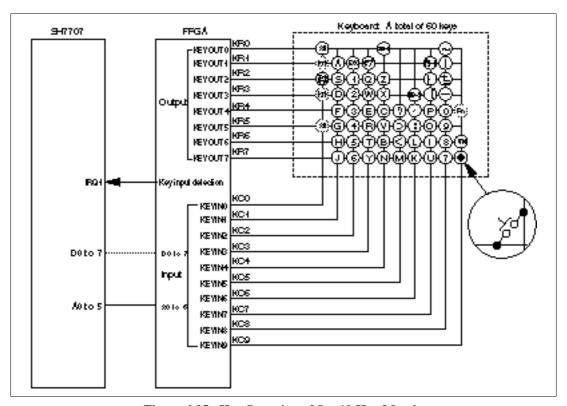

| 4.9  | Keyboa  | ard Section                             | 128 |

|      | 4.9.1   | Features                                | 128 |

|      | 4.9.2   | Key Scan Block Diagram                  | 129 |

|      | 4.9.3   | Pin Configuration                       | 129 |

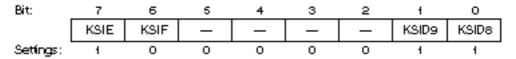

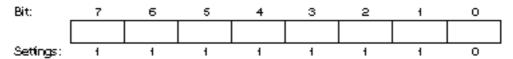

|      | 4.9.4   | Used Internal Register Description      | 130 |

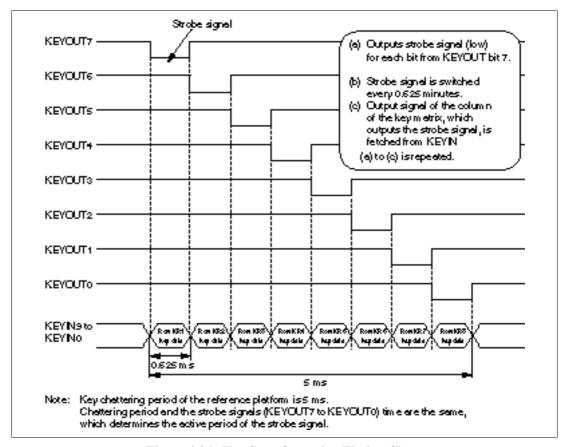

|      | 4.9.5   | FPGA Key Scan Control                   | 131 |

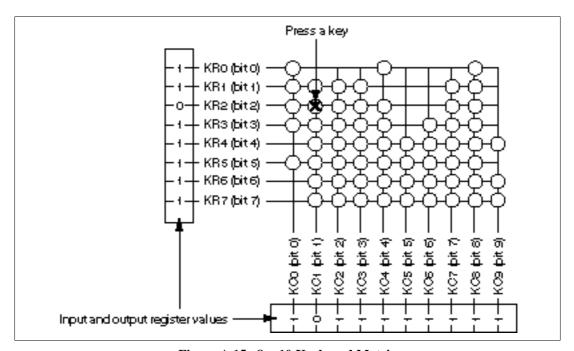

|      | 4.9.6   | Key Matrix                              | 133 |

|      | 4.9.7   | Key Scan Procedures                     | 134 |

|      | 4.9.8   | Key Scan Operation                      | 135 |

| Appe | endix A | Test Specifications                     | 139 |

| 11   | A.1     | Monitor Program.                        |     |

|      | A.2     | DRAM                                    |     |

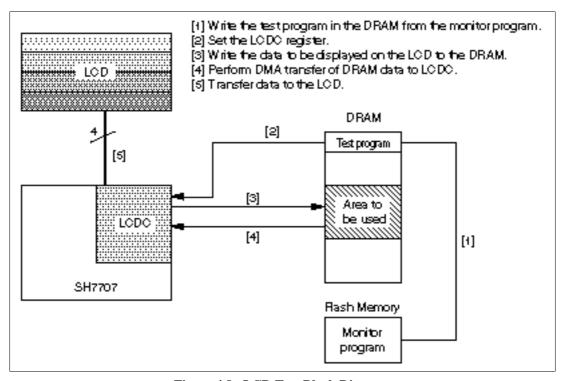

|      | A.3     | LCD                                     | 153 |

|      | A.4     | PCMCIA                                  | 161 |

|      | A.5     | Audio Play-Back                         | 171 |

|      | A.6     | Touch Panel                             |     |

|      | A.7     | SCI                                     |     |

|      | A.8     | IrDA                                    | 185 |

|      | A.9     | FPGA                                    | 192 |

|      | A.10    | Keyboard                                |     |

| Appe | endix B | Circuit Diagrams                        | 198 |

| rr   | B.1     | CPU Section                             |     |

|      | B.2     | FPGA and Peripheral Sections            |     |

|      | B.3     | Flash Memory Section                    |     |

|      | B.4     | DRAM, Touch Panel, and Audio Sections   |     |

|      | B.5     | Serial, LCD, and IrDA Sections          |     |

|      | B.6     | PCMCIA Section                          |     |

|      | B.7     | 200-Pin Connector                       |     |

| Appe | endix C | Component List                          | 205 |

| Appe | endix D | Pull-Up Resistors                       | 207 |

### Section 1 Overview

Microsoft<sup>®</sup> Windows<sup>®</sup> CE operating system has been produced for use with mobile computing and multimedia products. The handheld PC (H/PC) is one of the applications of Windows<sup>®</sup> CE, and it attracts a great deal of attention because its infrared communication and RS-232C interface make data transfer possible between a handheld PC and a notebook or desktop computer.

The mobile computer market needs a processor incorporating the peripheral functions necessary for Windows® CE, in addition to need for high performance, low power consumption, and high integration. To meet this demand, Hitachi has developed the SH7707, a member of the SuperH RISC engine family, based on the 32-bit SuperH RISC CPU core SH-3, which has been adopted by many application systems because of its well-balanced performance and power consumption, and high code efficiency due to 16-bit fixed-length instructions. The SH7707 operates at a maximum frequency of 60 MHz and achieves a high performance of 60 MIPS. It includes an 8-kbyte cache and the interface circuits required to use Windows® CE, and allows more compact application systems to be produced easily at lower cost.

Hitachi has also developed the SH7707 reference platform PFM-DS4 for Windows® CE (hereafter called the reference platform). This reference platform provides the functions necessary for Windows® CE by making the best use of the SH7707 on-chip functions.

The reference platform includes the device driver software for Windows® CE Version 1.01 and Version 2.0 (LCD, IrDA, keyboard, touch panel, audio replay, PCMCIA, and RS-232C drivers). In addition, sample programs for hardware debugging are also supplied for use as a reference when the user makes programs.

Note: Microsoft<sup>®</sup> and Windows<sup>®</sup> are registered trademarks of Microsoft Corporation in the United States and/or other countries.

# Section 2 Basic Specifications

Table 2.1 shows the basic specifications of the reference platform PFM-DS4, which supports the functions necessary for the Microsoft<sup>®</sup> Windows<sup>®</sup> CE operating system Version 1.01 and Version 2.0. Table 2.2 shows the design specifications.

**Table 2.1 Basic Specifications**

| Item          |                                          | Specifications                                            |                     |  |

|---------------|------------------------------------------|-----------------------------------------------------------|---------------------|--|

| CPU           | Operating frequency                      | Internal operating frequency                              | : 58.9824 MHz       |  |

|               |                                          | Internal bus frequency:                                   | 14.7456 MHz         |  |

|               |                                          | External bus frequency:                                   | 29.4912 MHz         |  |

|               | Bus width                                | 32 bits                                                   |                     |  |

| DRAM          | Capacity, configuration, and access time | 16 Mbytes (4 Mwords × 16 b                                | its × 2), 60 ns     |  |

| Flash memory  | Capacity, configuration, and access time | 8 Mbytes (128 kwords × 8 bi                               | ts × 8), 80 ns      |  |

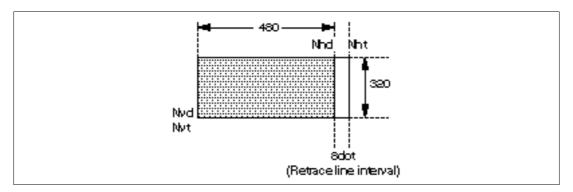

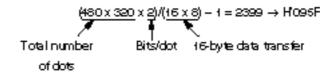

| Display (LCD) | Display format                           | 480 (W) × 240 (H) dots                                    |                     |  |

|               | Color                                    | Monochrome, four grayscales                               |                     |  |

| Interface     | RS-232C serial interface                 | Baud rate: 38400 bps max. monitor program is used)        | (9600 bps when the  |  |

|               |                                          | <b>Synchronization mode:</b> As synchronous mode can be s | =                   |  |

|               | PCMCIA                                   | Conforms to PCMCIA Rev. 2                                 | 2.1/JEIDA Ver. 4.2* |  |

|               | Touch panel                              | Resolution: Vertical: 84 mm                               | /1024 dots          |  |

|               |                                          | Horizontal: 115                                           | mm/1024 dots        |  |

|               | Audio                                    | Sampling frequency: 22 kHz max.                           |                     |  |

|               | Keyboard                                 | 8 × 10 key matrix                                         |                     |  |

|               | IrDA                                     | Conforms to IIR-SIR Ver. 1.0                              | )                   |  |

Note: The card slot is for 5-V operation. To use a 3.3-V power suply, change the PC card slot.

**Table 2.2 Design Specifications**

| Item                           |                     |            | Specifications                                                                                        |

|--------------------------------|---------------------|------------|-------------------------------------------------------------------------------------------------------|

| CPU                            |                     |            | SH7707 (HD6417707)                                                                                    |

| Memory                         | DRAM                |            | HM5165165ATT-6 (8 Mbytes × 2)                                                                         |

|                                | Flash               | memory     | HN29WT800T8 (1 Mbyte × 8)                                                                             |

| Display                        | LCD                 | Controller | On-chip LCD controller of SH7707                                                                      |

|                                |                     | Panel      | Maximum display size: 480 dots (W) × 360 dots (H)                                                     |

|                                |                     |            | Displaying area: 118.6 mm (W) × 80 mm (H)                                                             |

|                                |                     |            | Dot size: 0.22 mm (W) × 0.22 mm (H)                                                                   |

|                                |                     |            | Dot interval: 0.02 mm                                                                                 |

| Interface                      | SCI                 |            | On-chip serial interface of the SH7707 and RS-232C driver                                             |

|                                | PCMCIA              |            | On-chip PC card controller of the SH7707,<br>HD151015T (level shifter), and a slot (5 V)              |

|                                | Touch panel         |            | On-chip 10-bit A/D converter (two channels) of SH7707                                                 |

|                                | Sound               |            | On-chip 8-bit D/A converter (one channel) of SH7707 and current-driven amplifier                      |

|                                | Keybo               | ard        | Scan-type 60-key keyboard unit                                                                        |

|                                | IrDA                |            | On-chip serial interface and IrDA interface of SH7707, and light-receiving and light-emitting devices |

| Keyboard and touch panel timer | FPGA                |            | EPM7160-EQC100-10 manufactured by Altera Corporation                                                  |

| Board                          | External dimensions |            | 230 mm (W) × 120 mm (D)                                                                               |

|                                | Specifications      |            | Glass-epoxy 6-layer printed board                                                                     |

# Section 3 System Configuration

# 3.1 System Configuration Diagram

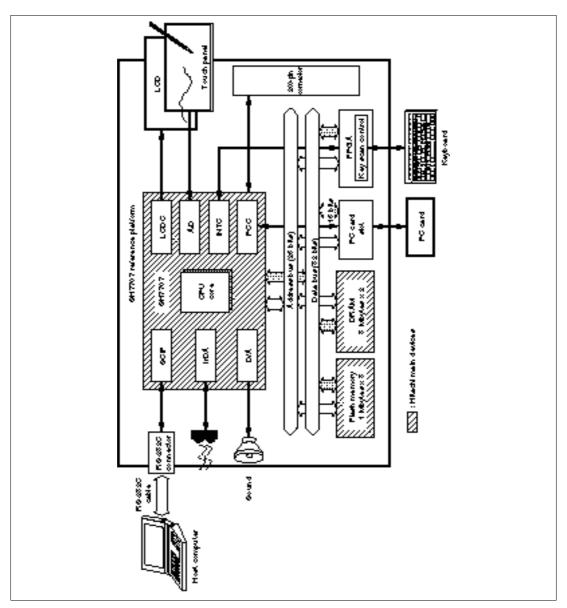

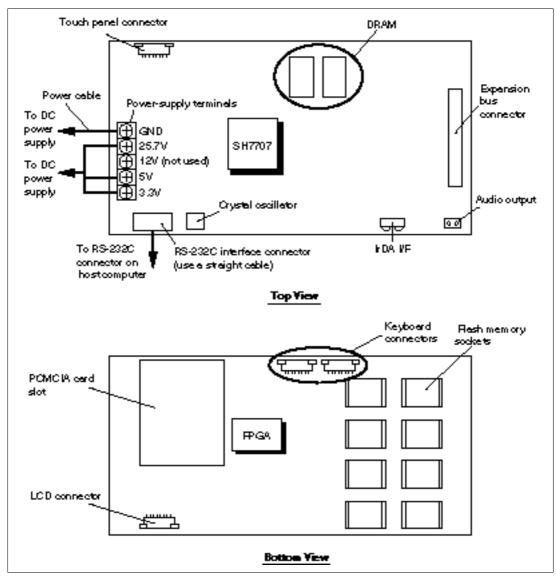

Figure 3.1 shows the configuration of the reference platform.

Figure 3.1 Reference Platform Configuration

# 3.2 Memory Map

In the reference platform, the physical space is divided into seven areas, to which memory devices and a PC card are connected, as shown in figure 3.2.

| Area No. | Physical Address | Function                                      | Size     |

|----------|------------------|-----------------------------------------------|----------|

| 0        | H00000000        | Flash memory (8 Mbytes)                       | 6+Mbytes |

|          | H007 FFFFF       |                                               |          |

|          |                  |                                               |          |

|          | Hosee effe       |                                               |          |

| 1        | H04000000        | Orrahip VO                                    | 6+Mbytes |

|          | Ho+FFFFFF        |                                               |          |

|          | <u></u>          |                                               |          |

|          | Ho7FF FFFF       |                                               |          |

| 2        | H08000000        | (Not used)                                    | 6+Mbytes |

|          |                  |                                               |          |

|          | HoBFF FFFF       |                                               |          |

|          |                  | EDAM III-LE I                                 |          |

| 3        | HoCooooo         | DRAM (16 Mbytes)                              | 6+Mbytes |

|          | Hooff FFFF       |                                               |          |

|          | HOFFFFF          |                                               |          |

| +        | H10000000        | Compenion FPGA                                | 6+Mbytes |

|          |                  |                                               |          |

|          |                  |                                               |          |

|          | H*13FF FFFFF     |                                               |          |

| s        | H 1400 0000      | (Not used)                                    | 6+Mbytes |

|          |                  |                                               |          |

|          |                  |                                               |          |

|          | H 17FF FFFF      |                                               |          |

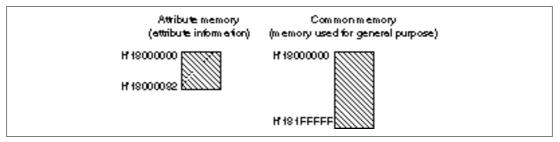

| 6        | H18000000        | PCMCIA interface<br>(for memory and VO cards) | 6+Mbytes |

|          |                  | *                                             |          |

|          | H 18FF FFFF      |                                               |          |

|          | H1BFF FFFF       |                                               |          |

Figure 3.2 Memory Map

## 3.3 Mode Setting

Specify the reference platform mode by using the jumpers on the board. Figure 3.3 shows the mode setting.

| Jumper | Description        | DefaultSetting |

|--------|--------------------|----------------|

| SW1    | Reset              | Open           |

| SW2    | Clock mode         | Open           |

| SM3    | Clock mode         | Closed         |

| SW 4   | Clock mode         | Closed         |

| SWS    | Buswidth of area 0 | Open           |

| SW6    | Buswidth of area 0 | Open           |

| SW7    | Endien             | Open           |

#### (1) Clock Mode:

| SW4 | SM3 | SW2 | Mode |

|-----|-----|-----|------|

| 0   | 0   | 1   | 1    |

| FROCR | Clock Retio<br>(I:B:P) |

|-------|------------------------|

| 0112  | 8:4:2                  |

Note: The FRQCR is the register for specifying the ratio of internal clock (f), external bus clock (B), and internal peripheral clock (P).

For other mode setting and how to set the FRQCR, refer to the SH7707 Hardware Manual.

#### (2) Bus Width of Area 0:

| SW6  | SW5    | Memory Size                   |

|------|--------|-------------------------------|

| 0    | 0      | Reserved<br>(illegal setting) |

| 0    | 1      | 8 bits                        |

| 1    | 0      | 16bi <del>ts</del>            |

| **** | ****** | 326 <b>6</b> 5                |

#### (3) Endien

| SW7           | Endien     |

|---------------|------------|

| 0             | Big enden  |

| :::: <b>:</b> | fink ender |

Note: When the endian is changed, the OS must also be changed.

:The shaded parts show the settings of the reference platform.

Figure 3.3 Reference Platform Mode and Jumper Setting

## 3.4 Interrupts

Table 3.1 shows the interrupts.

**Table 3.1** Interrupts

| Interrupt<br>Pin | SH7707<br>Pin No. | Module Using the<br>Interrupt | Description                                                                                                         |

|------------------|-------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------|

| NMI              | 7                 | Not used                      | _                                                                                                                   |

| IREQ0            | 8                 | Not used                      | _                                                                                                                   |

| IREQ1            | 9                 | FPGA                          | A/D conversion start for the keyboard or touch panel                                                                |

| IREQ2            | 10                | SCI                           | CD carrier detection (when a modem is connected)                                                                    |

| IREQ3            | 11                | Not used                      | _                                                                                                                   |

| IREQ4            | 12                | Touch panel                   | Detection of pen pressed down on the touch panel                                                                    |

| IREQ5            | 176               | Must not be used              | This pin is used for a special purpose by the reference board and must not be used as an interrupt pin by the user. |

| PCC0RDY          | 127               | PCMCIA                        | I/O card inserted                                                                                                   |

The NMI, IREQ0, and IREQ3 pins are not used in the reference platform; these pins can be used by the user from outside the reference platform through the expansion bus connector on the board.

# 3.5 SH7707 Register Initial Values in Reference Platform

Table 3.2 shows the initial values of the SH7707 registers in the reference platform.

Table 3.2

Register Initial Values

| Module | Register | Size | Address    | Initial Value in<br>SH7707 | Initial Value in<br>Reference Platform |

|--------|----------|------|------------|----------------------------|----------------------------------------|

| CCN    | PTEH     | 32   | H'FFFFFF0  | Undefined                  | <b>←</b>                               |

| CCN    | PTEL     | 32   | H'FFFFFFF4 | Undefined                  | <b>←</b>                               |

| CCN    | TTB      | 32   | H'FFFFFF8  | Undefined                  | $\leftarrow$                           |

| CCN    | TEA      | 32   | H'FFFFFFC  | Undefined                  | <b>←</b>                               |

| CCN    | MMUCR    | 32   | H'FFFFFE0  | H'00000000                 | ←                                      |

| CCN    | BASRA    | 32   | H'FFFFFE4  | Undefined                  | <b>←</b>                               |

| CCN    | BASRB    | 32   | H'FFFFFE8  | Undefined                  | <b>←</b>                               |

| CCN    | CCR      | 32   | H'FFFFFEC  | H'00000000                 | H'00000000                             |

| CCN    | TRA      | 32   | H'FFFFFD0  | Undefined                  | <b>←</b>                               |

| CCN    | EXPEVT   | 32   | H'FFFFFD4  | H'00000000                 | <b>←</b>                               |

| CCN    | INTEVT   | 32   | H'FFFFFD8  | Undefined                  | ←                                      |

| UBC    | BARA     | 32   | H'FFFFFB0  | Undefined                  | <b>←</b>                               |

| UBC    | BAMRA    | 8    | H'FFFFFB4  | Undefined                  | ←                                      |

| UBC    | BBRA     | 16   | H'FFFFFB8  | H'0000                     | ←                                      |

| UBC    | BARB     | 32   | H'FFFFFFA0 | Undefined                  | ←                                      |

| UBC    | BAMRB    | 8    | H'FFFFFFA4 | Undefined                  | <b>←</b>                               |

| UBC    | BBRB     | 16   | H'FFFFFFA8 | H'0000                     | ←                                      |

| UBC    | BDRB     | 32   | H'FFFFFF90 | Undefined                  | <b>←</b>                               |

| UBC    | BDMRB    | 32   | H'FFFFFF94 | Undefined                  | $\leftarrow$                           |

| UBC    | BRCR     | 16   | H'FFFFFF98 | H'0000                     | ←                                      |

| CPG    | FRQCR    | 16   | H'FFFFFF80 | H'0102                     | H'0112                                 |

| CPG    | STBCR    | 8    | H'FFFFFF82 | H'00                       | <b>←</b>                               |

| CPG    | STBCR2   | 8    | H'FFFFFF88 | H'00                       | ←                                      |

| CPG    | STBCR3   | 8    | H'FFFFFF8A | H'00                       | ←                                      |

| CPG    | WTCNT    | 8/16 | H'FFFFFF84 | H'00                       | H'A500                                 |

| CPG    | WTCSR    | 8/16 | H'FFFFFF86 | H'00                       | H'A500                                 |

Table 3.2

Register Initial Values (cont)

| Module | Register | Size | Address    | Initial Value in<br>SH7707 | Initial Value in<br>Reference Platform |

|--------|----------|------|------------|----------------------------|----------------------------------------|

| BCN    | BCR1     | 16   | H'FFFFFF60 | H'0000                     | H'1011                                 |

| BCN    | BCR2     | 16   | H'FFFFFF62 | H'3FF0                     | H'2EF0                                 |

| BCN    | WCR1     | 16   | H'FFFFF64  | H'3FF3                     | H'3F71                                 |

| BCN    | WCR2     | 16   | H'FFFFFF66 | H'FFFF                     | H'FFB9                                 |

| BCN    | MCR      | 16   | H'FFFFFF68 | H'0000                     | H'0034                                 |

| BCN    | DCR      | 16   | H'FFFFFF6A | H'0000                     | <b>←</b>                               |

| BCN    | PCR      | 16   | H'FFFFFF6C | H'0000                     | H'FFFF                                 |

| BCN    | RTCSR    | 16   | H'FFFFF6E  | H'0000                     | H'A518                                 |

| BCN    | RTCNT    | 16   | H'FFFFFF70 | H'0000                     | H'A500                                 |

| BCN    | RTCOR    | 16   | H'FFFFFF72 | H'0000                     | H'A507                                 |

| BCN    | RFCR     | 16   | H'FFFFFF74 | H'0000                     | <b>←</b>                               |

| BCN    | BCR3     | 16   | H'FFFFFF7E | H'0000                     | <b>←</b>                               |

| RTC    | R64CNT   | 8    | H'FFFFFEC0 | Undefined                  | <b>←</b>                               |

| RTC    | RSECCNT  | 8    | H'FFFFFEC2 | Undefined                  | <b>←</b>                               |

| RTC    | RMINCNT  | 8    | H'FFFFFEC4 | Undefined                  | <b>←</b>                               |

| RTC    | RHRCNT   | 8    | H'FFFFFEC6 | Undefined                  | <b>←</b>                               |

| RTC    | RWKCNT   | 8    | H'FFFFFEC8 | Undefined                  | <b>←</b>                               |

| RTC    | RDAYCNT  | 8    | H'FFFFFECA | Undefined                  | <b>←</b>                               |

| RTC    | RMONCNT  | 8    | H'FFFFFECC | Undefined                  | ←                                      |

| RTC    | RYRCNT   | 8    | H'FFFFFECE | Undefined                  | <b>←</b>                               |

| RTC    | RSECAR   | 8    | H'FFFFFED0 | Undefined                  | <b>←</b>                               |

| RTC    | RMINAR   | 8    | H'FFFFFED2 | Undefined                  | ←                                      |

| RTC    | RHRAR    | 8    | H'FFFFFED4 | Undefined                  | <b>←</b>                               |

| RTC    | RWKAR    | 8    | H'FFFFFED6 | Undefined                  | H'00                                   |

| RTC    | RDAYAR   | 8    | H'FFFFFED8 | Undefined                  | <b>←</b>                               |

| RTC    | RMONAR   | 8    | H'FFFFFEDA | Undefined                  | <b>←</b>                               |

| RTC    | RCR1     | 8    | H'FFFFFEDC | H'00                       | <b>←</b>                               |

| RTC    | RCR2     | 8    | H'FFFFFEDE | H'09                       | ←                                      |

| INTC   | ICR0     | 16   | H'FFFFFEE0 | H'8000/H'0000              | ←                                      |

| INTC   | IPRA     | 16   | H'FFFFFEE2 | H'0000                     | ←                                      |

| INTC   | IPRB     | 16   | H'FFFFFEE4 | H'0000                     | <b>←</b>                               |

Table 3.2

Register Initial Values (cont)

| Module | Register | Size | Address    | Initial Value in<br>SH7707 | Initial Value in<br>Reference Platform |

|--------|----------|------|------------|----------------------------|----------------------------------------|

| TMU    | TOCR     | 8    | H'FFFFFE90 | H'00                       | <b>←</b>                               |

| TMU    | TSTR     | 8    | H'FFFFFE92 | H'00                       | <b>←</b>                               |

| TMU    | TCOR0    | 32   | H'FFFFFE94 | H'FFFFFFF                  | <b>←</b>                               |

| TMU    | TCNT0    | 32   | H'FFFFFE98 | H'FFFFFFF                  | <b>←</b>                               |

| TMU    | TCR0     | 16   | H'FFFFFE9C | H'0000                     | <b>←</b>                               |

| TMU    | TCOR1    | 32   | H'FFFFFEA0 | H'FFFFFFF                  | <b>←</b>                               |

| TMU    | TCNT1    | 32   | H'FFFFFEA4 | H'FFFFFFF                  | <b>←</b>                               |

| TMU    | TCR1     | 16   | H'FFFFFEA8 | H'0000                     | <b>←</b>                               |

| TMU    | TCOR2    | 32   | H'FFFFFEAC | H'FFFFFFF                  | <b>←</b>                               |

| TMU    | TCNT2    | 32   | H'FFFFFEB0 | H'FFFFFFF                  | <b>←</b>                               |

| TMU    | TCR2     | 16   | H'FFFFFEB4 | H'0000                     | <b>←</b>                               |

| TMU    | TCPR2    | 32   | H'FFFFFEB8 | Undefined                  | <b>←</b>                               |

| SCI    | SCSMR    | 8    | H'FFFFFE80 | H'00                       | <b>←</b>                               |

| SCI    | SCBRR    | 8    | H'FFFFFE82 | H'FF                       | <b>←</b>                               |

| SCI    | SCSCR    | 8    | H'FFFFFE84 | H'00                       | <b>←</b>                               |

| SCI    | SCTDR    | 8    | H'FFFFFE86 | H'FF                       | <b>←</b>                               |

| SCI    | SCSSR    | 8    | H'FFFFFE88 | H'84                       | <b>←</b>                               |

| SCI    | SCRDR    | 8    | H'FFFFFE8A | H'00                       | <b>←</b>                               |

| SCI    | SCSPTR   | 8    | H'FFFFFF7C | H'00                       | <b>←</b>                               |

| INT    | INTEVT2  | 32   | H'04000000 | Undefined                  | <b>←</b>                               |

| INT    | IRR0     | 8    | H'04000004 | H'00                       | <b>←</b>                               |

| INT    | IRR1     | 8    | H'04000006 | H'00                       | <b>←</b>                               |

| INT    | IRR2     | 8    | H'04000008 | H'00                       | <b>←</b>                               |

| INT    | IRR3     | 8    | H'0400000A | H'00                       | <b>←</b>                               |

| INT    | IRR4     | 8    | H'0400000C | H'00                       | <b>←</b>                               |

| INT    | ICR1     | 16   | H'04000010 | H'0000                     | H'8000                                 |

| INT    | ICR2     | 16   | H'04000012 | H'0000                     | H'0000                                 |

| INT    | PINTER   | 16   | H'04000014 | H'0000                     | H'0000                                 |

| INT    | IPRC     | 16   | H'04000016 | H'0000                     | H'0280                                 |

| INT    | IPRD     | 16   | H'04000018 | H'0000                     | H'0017                                 |

| INT    | IPRE     | 16   | H'0400001A | H'0000                     | H'9456                                 |

| INT    | IPRF     | 16   | H'0400001C | H'0000                     | H'0030                                 |

Table 3.2

Register Initial Values (cont)

| Module | Register | Size | Address    | Initial Value in<br>SH7707 | Initial Value in<br>Reference Platform |

|--------|----------|------|------------|----------------------------|----------------------------------------|

| DMAC   | SAR0     | 32   | H'04000020 | Undefined                  | H'AC002000                             |

| DMAC   | DAR0     | 32   | H'04000024 | Undefined                  | H'A40000A0                             |

| DMAC   | DMATCR0  | 32   | H'04000028 | Undefined                  | H'00000800                             |

| DMAC   | CHCR0    | 32   | H'0400002C | H'00000000                 | H'00001F04                             |

| DMAC   | SAR1     | 32   | H'04000030 | Undefined                  | <b>←</b>                               |

| DMAC   | DAR1     | 32   | H'04000034 | Undefined                  | <b>←</b>                               |

| DMAC   | DMATCR1  | 32   | H'04000038 | Undefined                  | <b>←</b>                               |

| DMAC   | CHCR1    | 32   | H'0400003C | H'00000000                 | <b>←</b>                               |

| DMAC   | SAR2     | 32   | H'04000040 | Undefined                  | $\leftarrow$                           |

| DMAC   | DAR2     | 32   | H'04000044 | Undefined                  | $\leftarrow$                           |

| DMAC   | DMATCR2  | 32   | H'04000048 | Undefined                  | $\leftarrow$                           |

| DMAC   | CHCR2    | 32   | H'0400004C | H'00000000                 | $\leftarrow$                           |

| DMAC   | SAR3     | 32   | H'04000050 | Undefined                  | ←                                      |

| DMAC   | DAR3     | 32   | H'04000054 | Undefined                  | ←                                      |

| DMAC   | DMATCR3  | 32   | H'04000058 | Undefined                  | ←                                      |

| DMAC   | CHCR3    | 32   | H'0400005C | H'00000000                 | ←                                      |

| DMAC   | DMAOR    | 16   | H'04000060 | H'0000                     | H'0001                                 |

| A/D    | ADDRAH   | 8    | H'04000080 | H'00                       | $\leftarrow$                           |

| A/D    | ADDRAL   | 8    | H'04000082 | H'00                       | ←                                      |

| A/D    | ADDRBH   | 8    | H'04000084 | H'00                       | ←                                      |

| A/D    | ADDRBL   | 8    | H'04000086 | H'00                       | $\leftarrow$                           |

| A/D    | ADDRCH   | 8    | H'04000088 | H'00                       | $\leftarrow$                           |

| A/D    | ADDRCL   | 8    | H'0400008A | H'00                       | $\leftarrow$                           |

| A/D    | ADDRDH   | 8    | H'0400008C | H'00                       | ←                                      |

| A/D    | ADDRDL   | 8    | H'0400008E | H'00                       | $\leftarrow$                           |

| A/D    | ADCSR    | 8    | H'04000090 | H'00                       | $\leftarrow$                           |

| A/D    | ADCR     | 8    | H'04000092 | H'3F                       | $\leftarrow$                           |

| D/A    | DADR0    | 8    | H'040000A0 | H'00                       | <b>←</b>                               |

| D/A    | DADR1    | 8    | H'040000A2 | H'00                       | $\leftarrow$                           |

| D/A    | DACR     | 8    | H'040000A4 | H'1F                       | H'5F                                   |

Table 3.2

Register Initial Values (cont)

| Module | Register   | Size | Address    | Initial Value in<br>SH7707 | Initial Value in<br>Reference Platform |

|--------|------------|------|------------|----------------------------|----------------------------------------|

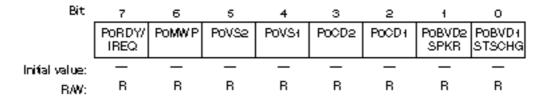

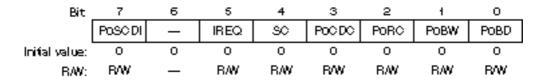

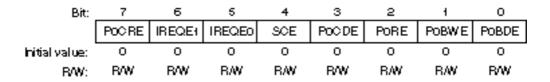

| PCMCIA | PCC0ISR0   | 8    | H'040000E0 | Undefined                  | <b>←</b>                               |

| PCMCIA | PCC0GCR    | 8    | H'040000E2 | H'00                       | H'88                                   |

| PCMCIA | PCC0CSCR   | 8    | H'040000E4 | H'00                       | H'00                                   |

| PCMCIA | PCC0CSCIEF | 8 8  | H'040000E6 | H'00                       | H'68                                   |

| PCMCIA | PCC1ISR0   | 8    | H'040000F0 | Undefined                  | <b>←</b>                               |

| PCMCIA | PCC1GSR    | 8    | H'040000F2 | H'00                       | <b>←</b>                               |

| PCMCIA | PCC1CSCR   | 8    | H'040000F4 | H'00                       | $\leftarrow$                           |

| PCMCIA | PCC1CSCIEF | 8 8  | H'040000F6 | H'00                       | <b>←</b>                               |

| PORT   | PACR       | 16   | H'04000100 | H'0000                     | <b>←</b>                               |

| PORT   | PBCR       | 16   | H'04000102 | H'0000                     | <b>←</b>                               |

| PORT   | PCCR       | 16   | H'04000104 | H'AAAA                     | H'0010                                 |

| PORT   | PDCR       | 16   | H'04000106 | H'AAAA                     | H'A801                                 |

| PORT   | PECR       | 16   | H'04000108 | H'AAAA                     | H'0205                                 |

| PORT   | PFCR       | 16   | H'0400010A | H'AAAA                     | <b>←</b>                               |

| PORT   | PGCR       | 16   | H'0400010C | H'AAAA                     | H'0000                                 |

| PORT   | PHCR       | 16   | H'0400010E | H'AAAA                     | H'88A2                                 |

| PORT   | PJCR       | 16   | H'04000110 | H'0000                     | H'5004                                 |

| PORT   | PKCR       | 16   | H'04000112 | H'0000                     | <b>←</b>                               |

| PORT   | PLCR       | 16   | H'04000114 | H'0000                     | <b>←</b>                               |

| PORT   | SCPCR      | 16   | H'04000116 | H'A888                     | H'1888                                 |

| PORT   | PADR       | 8    | H'04000120 | H'00                       | <b>←</b>                               |

| PORT   | PBDR       | 8    | H'04000122 | H'00                       | ←                                      |

| PORT   | PCDR       | 8    | H'04000124 | H'00                       | H'00                                   |

| PORT   | PDDR       | 8    | H'04000126 | H'00                       | H'00                                   |

| PORT   | PEDR       | 8    | H'04000128 | H'00                       | H'02                                   |

| PORT   | PFDR       | 8    | H'0400012A | H'00                       | <b>←</b>                               |

| PORT   | PGDR       | 8    | H'0400012C | H'00                       | <b>←</b>                               |

| PORT   | PHDR       | 8    | H'0400012E | H'00                       | ←                                      |

| PORT   | PJDR       | 8    | H'04000130 | H'00                       | H'42                                   |

| PORT   | PKDR       | 8    | H'04000132 | H'00                       | ←                                      |

| PORT   | PLDR       | 8    | H'04000134 | H'00                       | <b>←</b>                               |

| PORT   | SCPDR      | 8    | H'04000136 | H'00                       | <b>←</b>                               |

Table 3.2

Register Initial Values (cont)

| Module | Register | Size | Address    | Initial Value in SH7707 | Initial Value in<br>Reference Platform |

|--------|----------|------|------------|-------------------------|----------------------------------------|

| SCIF   | SCSMR2   | 8    | H'04000150 | H'00                    | <b>←</b>                               |

| SCIF   | SCBRR2   | 8    | H'04000152 | H'FF                    | $\leftarrow$                           |

| SCIF   | SCSCR2   | 8    | H'04000154 | H'00                    | $\leftarrow$                           |

| SCIF   | SCFTDR2  | 8    | H'04000156 | -                       | $\leftarrow$                           |

| SCIF   | SCSSR2   | 16   | H'04000158 | H'0060                  | $\leftarrow$                           |

| SCIF   | SCFRDR2  | 8    | H'0400015A | -                       | $\leftarrow$                           |

| SCIF   | SCSFCR2  | 8    | H'0400015C | H'00                    | $\leftarrow$                           |

| SCIF   | SCFDR2   | 16   | H'0400015E | H'0000                  | $\leftarrow$                           |

| IrDA   | SCSMR1   | 8    | H'04000140 | H'00                    | H'80                                   |

| IrDA   | SCBRR1   | 8    | H'04000142 | H'FF                    | $\leftarrow$                           |

| IrDA   | SCSCR1   | 8    | H'04000144 | H'00                    | H'00                                   |

| IrDA   | SCFTDR1  | 8    | H'04000146 | -                       | $\leftarrow$                           |

| IrDA   | SCSSR1   | 16   | H'04000148 | H'0060                  | $\leftarrow$                           |

| IrDA   | SCFRDR1  | 8    | H'0400014A | -                       | $\leftarrow$                           |

| IrDA   | SCSFCR1  | 8    | H'0400014C | H'00                    | $\leftarrow$                           |

| IrDA   | SCFDR1   | 16   | H'0400014E | H'0000                  | $\leftarrow$                           |

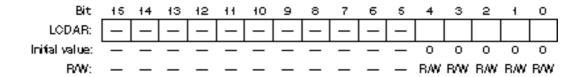

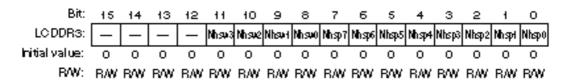

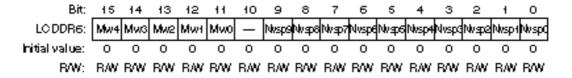

| LCD    | LCDAR    | 16   | H'040000C0 | H'0000                  | $\leftarrow$                           |

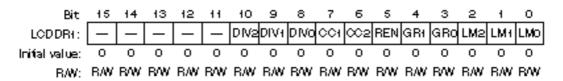

| LCD    | LCDDR    | 16   | H'040000C2 | H'0000                  | *1                                     |

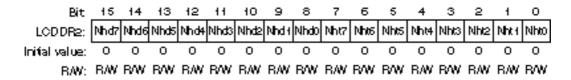

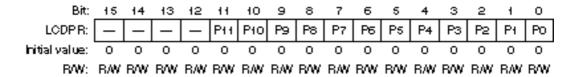

| LCD    | LCDPR    | 16   | H'040000C6 | H'0000                  | *2                                     |

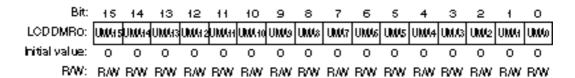

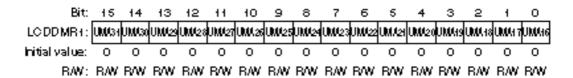

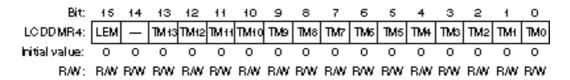

| LCD    | LCDDMR   | 16   | H'040000CE | H'0000                  | *3                                     |

### Notes: 1.

| Register | Size | Address<br>(LCDAR) | Address<br>(LCDDR) | Initial Value in<br>Reference Platform |

|----------|------|--------------------|--------------------|----------------------------------------|

| LCDDR1   | 16   | H'0001             | H'040000C2         | H'0230                                 |

| LCDDR2   | 16   | H'0002             | H'040000C2         | H'7779                                 |

| LCDDR3   | 16   | H'0003             | H'040000C2         | H'0177                                 |

| LCDDR4   | 16   | H'0004             | H'040000C2         | H'013F                                 |

| LCDDR5   | 16   | H'0005             | H'040000C2         | H'013F                                 |

| LCDDR6   | 16   | H'0006             | H'040000C2         | H'E000                                 |

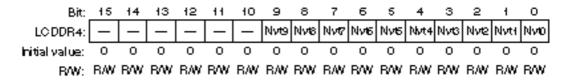

2.

| Register | Size | Address<br>(LCDAR) | Address<br>(LCDDR) | Initial Value in<br>Reference Platform |

|----------|------|--------------------|--------------------|----------------------------------------|

| LCDPR0   | 16   | H'0000             | H'040000C6         | H'000F                                 |

| LCDPR1   | 16   | H'0001             | H'040000C6         | H'000A                                 |

| LCDPR2   | 16   | H'0002             | H'040000C6         | H'0005                                 |

| LCDPR3   | 16   | H'0003             | H'040000C6         | H'0000                                 |

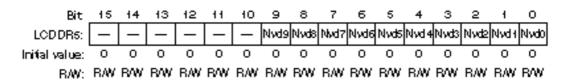

3.

| Register | Size | Address<br>(LCDAR) | Address<br>(LCDDR) | Initial Value in<br>Reference Platform |

|----------|------|--------------------|--------------------|----------------------------------------|

| LCDDMR0  | 16   | H'0000             | H'040000CE         | H'8000                                 |

| LCDDMR1  | 16   | H'0001             | H'040000CE         | H'AC00                                 |

| LCDDMR4  | 16   | H'0004             | H'040000CE         | H'895F                                 |

The registers other than the above will not be initialized.

# 3.6 SH7707 Pin Assignment

Table 3.3 shows the assignment of pin functions and pin numbers on the 200-pin expansion bus connector in the reference platform.

**Table 3.3 Pin Assignment**

| SH7707<br>Pin No. | SH7707<br>Pin Name    | Function in Reference Platform                                                | Pin No. on Expansion Bus Connector |

|-------------------|-----------------------|-------------------------------------------------------------------------------|------------------------------------|

| 1                 | MD1                   | Mode pin                                                                      | 196                                |

| 2                 | MD2                   | Mode pin                                                                      | 146                                |

| 3                 | Vcc                   | RTC oscillator power supply (3.3 V)                                           | _                                  |

| 4                 | XTAL2                 | NC                                                                            | 195                                |

| 5                 | EXTAL2                | Crystal oscillator pin (on-chip RTC; 32.768 kHz                               | z) 145                             |

| 6                 | V <sub>SS</sub> (RTC) | RTC oscillator power supply (0 V)                                             | _                                  |

| 7                 | NMI                   | Interrupt from FPGA (must be pulled up)                                       | 194                                |

| 8                 | IRQ0                  | Interrupt from FPGA (must be pulled up)                                       | 144                                |

| 9                 | IRQ1                  | Interrupt from FPGA (keyboard/touch panel/<br>sound timer; must be pulled up) | 193                                |

| 10                | IRQ2                  | External interrupt request (SCI; must be pulled up)                           | 143                                |

| 11                | IRQ3                  | External interrupt request (parallel interface; must be pulled up)            | 192                                |

| 12                | IRQ4                  | External interrupt request (touch panel; must b pulled up)                    | e 142                              |

| 13                | D31                   | Data bus 31 (must be pulled up)                                               | 191                                |

| 14                | D30                   | Data bus 30 (must be pulled up)                                               | 141                                |

| 15                | D29                   | Data bus 29 (must be pulled up)                                               | 190                                |

| 16                | D28                   | Data bus 28 (must be pulled up)                                               | 140                                |

| 17                | D27                   | Data bus 27 (must be pulled up)                                               | 189                                |

| 18                | D26                   | Data bus 26 (must be pulled up)                                               | 139                                |

| 19                | V <sub>SS</sub>       | GND                                                                           | _                                  |

| 20                | D25                   | Data bus 25 (must be pulled up)                                               | 188                                |

| 21                | Vcc                   | Power supply (3.3 V)                                                          | _                                  |

| 22                | D24                   | Data bus 24 (must be pulled up)                                               | 138                                |

Table 3.3 Pin Assignment (cont)

| SH7707<br>Pin No. | SH7707<br>Pin Name | Function in Reference Platform  | Pin No. on Expansion<br>Bus Connector |

|-------------------|--------------------|---------------------------------|---------------------------------------|

| 23                | D23                | Data bus 23 (must be pulled up) | 187                                   |

| 24                | D22                | Data bus 22 (must be pulled up) | 137                                   |

| 25                | D21                | Data bus 21 (must be pulled up) | 186                                   |

| 26                | D20                | Data bus 20 (must be pulled up) | 136                                   |

| 27                | V <sub>SS</sub>    | GND                             | _                                     |

| 28                | D19                | Data bus 19 (must be pulled up) | 185                                   |

| 29                | V <sub>CC</sub>    | Power supply (3.3 V)            | _                                     |

| 30                | D18                | Data bus 18 (must be pulled up) | 135                                   |

| 31                | D17                | Data bus 17 (must be pulled up) | 184                                   |

| 32                | D16                | Data bus 16 (must be pulled up) | 134                                   |

| 33                | V <sub>SS</sub>    | GND                             | _                                     |

| 34                | D15                | Data bus 15 (must be pulled up) | 183                                   |

| 35                | V <sub>CC</sub>    | Power supply (3.3 V)            | _                                     |

| 36                | D14                | Data bus 14 (must be pulled up) | 133                                   |

| 37                | D13                | Data bus 13 (must be pulled up) | 182                                   |

| 38                | D12                | Data bus 12 (must be pulled up) | 132                                   |

| 39                | D11                | Data bus 11 (must be pulled up) | 181                                   |

| 40                | D10                | Data bus 10 (must be pulled up) | 131                                   |

| 41                | D9                 | Data bus 9 (must be pulled up)  | 180                                   |

| 42                | D8                 | Data bus 8 (must be pulled up)  | 130                                   |

| 43                | D7                 | Data bus 7 (must be pulled up)  | 179                                   |

| 44                | D6                 | Data bus 6 (must be pulled up)  | 129                                   |

| 45                | V <sub>SS</sub>    | GND                             | _                                     |

| 46                | D5                 | Data bus 5 (must be pulled up)  | 178                                   |

| 47                | Vcc                | Power supply (3.3 V)            | _                                     |

| 48                | D4                 | Data bus 4 (must be pulled up)  | 128                                   |

| 49                | D3                 | Data bus 3 (must be pulled up)  | 177                                   |

| 50                | D2                 | Data bus 2 (must be pulled up)  | 127                                   |

| 51                | D1                 | Data bus 1 (must be pulled up)  | 176                                   |

|                   |                    |                                 |                                       |

Table 3.3

Pin Assignment (cont)

| SH7707<br>Pin No. | SH7707<br>Pin Name | Function in Reference Platform     | Pin No. on Expansion Bus Connector |

|-------------------|--------------------|------------------------------------|------------------------------------|

| 52                | D0                 | Data bus 0 (must be pulled up)     | 126                                |

| 53                | A0                 | Address bus 0                      | 175                                |

| 54                | A1                 | Address bus 1                      | 125                                |

| 55                | A2                 | Address bus 2                      | 174                                |

| 56                | A3                 | Address bus 3                      | 124                                |

| 57                | Vss                | GND                                | _                                  |

| 58                | A4                 | Address bus 4                      | 173                                |

| 59                | Vcc                | Power supply (3.3 V)               | _                                  |

| 60                | A5                 | Address bus 5                      | 123                                |

| 61                | A6                 | Address bus 6                      | 172                                |

| 62                | A7                 | Address bus 7                      | 122                                |

| 63                | A8                 | Address bus 8                      | 171                                |

| 64                | A9                 | Address bus 9                      | 121                                |

| 65                | A10                | Address bus 10 (must be pulled up) | 170                                |

| 66                | A11                | Address bus 11                     | 120                                |

| 67                | A12                | Address bus 12                     | 169                                |

| 68                | A13                | Address bus 13                     | 119                                |

| 69                | V <sub>SS</sub>    | GND                                | _                                  |

| 70                | A14                | Address bus 14                     | 168                                |

| 71                | V <sub>CC</sub>    | Power supply (3.3 V)               | _                                  |

| 72                | A15                | Address bus 15                     | 118                                |

| 73                | A16                | Address bus 16                     | 167                                |

| 74                | A17                | Address bus 17                     | 117                                |

| 75                | A18                | Address bus 18                     | 166                                |

| 76                | A19                | Address bus 19                     | 116                                |

| 77                | A20                | Address bus 20                     | 165                                |

| 78                | A21                | Address bus 21                     | 115                                |

| 79                | Vss                | GND                                | _                                  |

| 80                | A22                | Address bus 22                     | 164                                |

Table 3.3 Pin Assignment (cont)

| SH7707<br>Pin No. | SH7707<br>Pin Name | Function in Reference Platform                         | Pin No. on Expansion Bus Connector |

|-------------------|--------------------|--------------------------------------------------------|------------------------------------|

| 81                | Vcc                | Power supply (3.3 V)                                   | _                                  |

| 82                | A23                | Address bus 23                                         | 114                                |

| 83                | V <sub>SS</sub>    | GND                                                    | _                                  |

| 84                | A24                | Address bus 24                                         | 163                                |

| 85                | Vcc                | Power supply (3.3 V)                                   | _                                  |

| 86                | A25                | Address bus 25                                         | 113                                |

| 87                | BS                 | SHBS of FPGA                                           | 162                                |

| 88                | RD                 | Read strobe                                            | 112                                |

| 89                | WE0                | D7—D0 select signal                                    | 161                                |

| 90                | WE1/WE             | D15—D8 select signal/PCMCIA WE signal                  | 111                                |

| 91                | WE2/ICIORD         | D23—D16 select signal/PCMCIA IORD signal               | 160                                |

| 92                | WE3/ICIOWR         | D31—D24 select signal/PCMCIA IOWR signal               | 110                                |

| 93                | RDWR               | Read/write switching signal                            | 159                                |

| 94                | PCCRD/WR/<br>PTE7  | PCMCIA read/write switching signal (must be pulled up) | 109                                |

| 95                | V <sub>SS</sub>    | GND                                                    | _                                  |

| 96                | CS0                | Chip selection 0 (flash memory)                        | 158                                |

| 97                | Vcc                | Power supply (3.3 V)                                   | _                                  |

| 98                | CS2                | Chip selection 2 (FPGA)                                | 108                                |

| 99                | CS3                | Chip selection 3 (FPGA)                                | 157                                |

| 100               | CS4                | Chip selection 4 (FPGA)                                | 107                                |

| 101               | CE1A               | Not used (must be pulled up)                           | 156                                |

| 102               | CE1B               | PCMCIA CE1B                                            | 106                                |

| 103               | CE2A               | Not used (must be pulled up)                           | 155                                |

| 104               | CE2B               | PCMCIA CE2B                                            | 105                                |

| 105               | PTK5               | Flash/RDY/BSY signal (must be pulled up)               | 57                                 |

| 106               | RAS                | RAS for area 3                                         | 56                                 |

| 107               | PTJ1               | I/O port (touch panel; must be pulled up)              | 8                                  |

| 108               | CASLL              | D7—D0 selection CAS (DRAM)                             | 58                                 |

Table 3.3

Pin Assignment (cont)

| SH7707<br>Pin No. | SH7707<br>Pin Name | Function in Reference Platform       | Pin No. on Expansion Bus Connector |

|-------------------|--------------------|--------------------------------------|------------------------------------|

| 109               | Vss                | GND                                  | _                                  |

| 110               | CASLH              | D15—D8 selection CAS (DRAM)          | 9                                  |

| 111               | Vcc                | Power supply (3.3 V)                 | _                                  |

| 112               | CASHL              | D23—D16 selection CAS (DRAM)         | 59                                 |

| 113               | CASHH              | D31—D24 selection CAS (DRAM)         | 10                                 |

| 114               | PTD5               | I/O port (FPGA)                      | 60                                 |

| 115               | PTD7               | I/O port (FPGA)                      | 11                                 |

| 116               | PCCREG             | PCMCIA REG                           | 61                                 |

| 117               | PCC0DRV            | PCMCIA0 buffer control               | 12                                 |

| 118               | PCC0RESET          | PCMCIA0 reset output                 | 62                                 |

| 119               | PTE1               | I/O port (PCMCIA; must be pulled up) | 13                                 |

| 120               | PTE0               | I/O port (PCMCIA; must be pulled up) | 63                                 |

| 121               | BACK               | Not used                             | 14                                 |

| 122               | BREQ               | Not used (must be pulled up)         | 64                                 |

| 123               | WAIT               | Not used (must be pulled up)         | 15                                 |

| 124               | PCC0WAIT           | PCMCIA0 hardware wait request        | 65                                 |

| 125               | PTH5               | I/O port (FPGA; must be pulled up)   | 16                                 |

| 126               | PCC0WP             | PCMCIA0 WP                           | 66                                 |

| 127               | PCC0READY          | PCMCIA0 BUSY.READ                    | 17                                 |

| 128               | PCC0BVD1           | PCMCIA0 BVD1                         | 67                                 |

| 129               | PCC0BVD2           | PCMCIA0 BVD2                         | 18                                 |

| 130               | PCC0CD1            | PCMCIA0 CD1                          | 68                                 |

| 131               | PCC0CD2            | PCMCIA0 CD2                          | 19                                 |

| 132               | V <sub>SS</sub>    | GND                                  | _                                  |

| 133               | PCC0VS1            | PCMCIA0 VS1                          | 69                                 |

| 134               | Vcc                | Power supply (3.3 V)                 | _                                  |

| 135               | PCC0VS2            | PCMCIA0 VS2                          | 20                                 |

| 136               | PTF7               | Keyboard input 7 (FPGA)              | 70                                 |

| 137               | PTF6               | Keyboard input 6 (FPGA)              | 21                                 |

Table 3.3 Pin Assignment (cont)

| SH7707<br>Pin No. | SH7707<br>Pin Name       | Function in Reference Platform              | Pin No. on Expansion Bus Connector |

|-------------------|--------------------------|---------------------------------------------|------------------------------------|

| 138               | PTF5                     | Keyboard input 5 (FPGA)                     | 71                                 |

| 139               | PTF4                     | Keyboard input 4 (FPGA)                     | 22                                 |

| 140               | PTF3                     | Keyboard input 3 (FPGA)                     | 72                                 |

| 141               | PTF2                     | Keyboard input 2 (FPGA)                     | 23                                 |

| 142               | PTF1                     | Keyboard input 1 (FPGA)                     | 73                                 |

| 143               | PTF0                     | Keyboard input 0 (FPGA)                     | 24                                 |

| 144               | MD0                      | Mode pin                                    | 74                                 |

| 145               | V <sub>CC</sub> (PLL1)   | Power supply for PLL (3.3 V)                | _                                  |

| 146               | CAP1                     | 470 pF                                      | _                                  |

| 147               | V <sub>SS</sub> (PLL1)   | Power supply for PLL (0V)                   | _                                  |

| 148               | V <sub>SS</sub> (PLL2)   | Power supply for PLL (0V)                   | _                                  |

| 149               | CAP2                     | 470 pF                                      | _                                  |

| 150               | V <sub>CC</sub> (PLL2/3) | Power supply for PLL (3.3 V)                | _                                  |

| 151               | V <sub>SS</sub> (PLL2/3) | Power supply for PLL (0V)                   | _                                  |

| 152               | V <sub>SS</sub> (PLL3)   | Power supply for PLL (0V)                   | _                                  |

| 153               | V <sub>SS</sub>          | GND                                         | _                                  |

| 154               | V <sub>CC</sub>          | Power supply (3.3 V)                        | _                                  |

| 155               | XTAL                     | Not used                                    | 25                                 |

| 156               | EXTAL                    | External clock (8 MHz is currently input)   | 75                                 |

| 157               | PTJ6                     | I/O port (touch panel; must be pulled up)   | 26                                 |

| 158               | PTJ7                     | I/O port (touch panel; must be pulled down) | 76                                 |

| 159               | TCLK                     | Not used (must be pulled up)                | 27                                 |

| 160               | IRQOUT                   | Not used                                    | 77                                 |

| 161               | Vss                      | GND                                         | _                                  |

| 162               | CKIO                     | Internal clock output                       | 28                                 |

| 163               | Vcc                      | Power supply (3.3 V)                        | _                                  |

| 164               | TxD0                     | Not used                                    | 78                                 |

| 165               | SCK0                     | Not used (must be pulled up)                | 29                                 |

| 166               | TxD1                     | Data output from serial port 1 (IrDA)       | 79                                 |

Table 3.3

Pin Assignment (cont)

| SH7707<br>Pin No. | SH7707<br>Pin Name | Function in Reference Platform                                  | Pin No. on Expansion Bus Connector |

|-------------------|--------------------|-----------------------------------------------------------------|------------------------------------|

| 167               | SCK1               | Not used (must be pulled up)                                    | 30                                 |

| 168               | TxD2               | Data output from serial port 2 (SCIF)                           | 80                                 |

| 169               | SCK2               | Not used (must be pulled up)                                    | 31                                 |

| 170               | RTS2               | Transmit request for serial port 2 (SCIF)                       | 81                                 |

| 171               | RxD0               | Not used (must be pulled up)                                    | 32                                 |

| 172               | RxD1               | Serial port 1 data input (IrDA; must be pulled up)              | 82                                 |

| 173               | V <sub>SS</sub>    | GND                                                             | _                                  |

| 174               | RxD2               | Data input from serial port 2 (SCIF)                            | 33                                 |

| 175               | Vcc                | Power supply (3.3 V)                                            | _                                  |

| 176               | CT2                | Transfer acknowledge for serial port 2 (SCIF)                   | 83                                 |

| 177               | UD3                | LCD data output                                                 | 34                                 |

| 178               | UD2                | LCD data output                                                 | 84                                 |

| 179               | UD1                | LCD data output                                                 | 35                                 |

| 180               | UD0                | LCD data output                                                 | 85                                 |

| 181               | V <sub>SS</sub>    | GND                                                             | _                                  |

| 182               | CL1                | LCD clock output (LCD, FPGA; must be pulled up)                 | 36                                 |

| 183               | V <sub>CC</sub>    | Power supply (3.3 V)                                            | _                                  |

| 184               | CL2                | LCD clock output                                                | 86                                 |

| 185               | LD3                | Not used (must be pulled up)                                    | 37                                 |

| 186               | PTC2               | I/O port (PCMCIA; must be pulled up)                            | 87                                 |

| 187               | LD1                | Not used (must be pulled up)                                    | 38                                 |

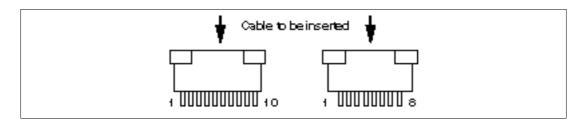

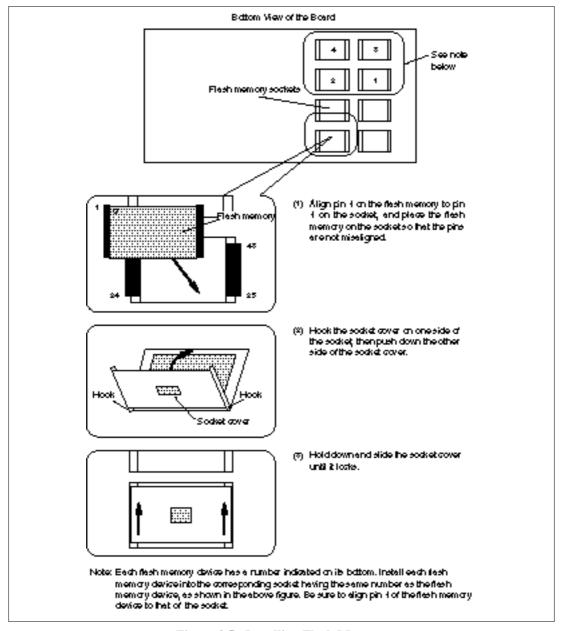

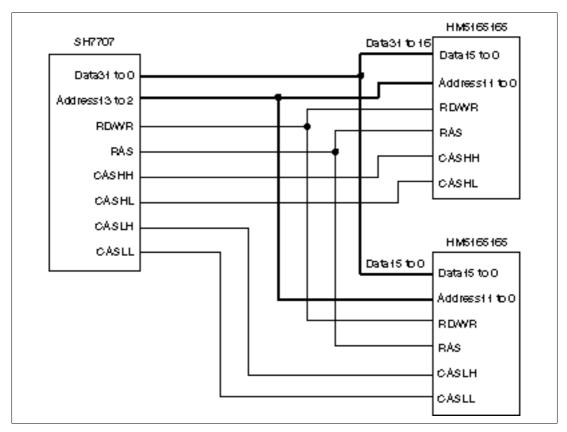

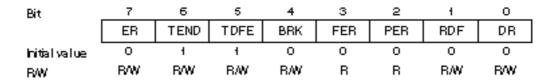

| 188               | LD0                | LCD data output (must be pulled up)                             | 88                                 |