S2028

### **FEATURES**

- 33 x 32 differential crosspoint switch

- Full broadcast switching capability

- Differential 10K PECL data path

- Configurable differential output driver controls

- Up to 1.25 Gbit/s NRZ data rate

- TTL configuration controls

- Reconfigurable without disturbing operation

- Single cycle broadcast configuration

- High-speed multicast and fast unicast configuration (100 MHz)

- "Break" feature to disable previous multicast configuration

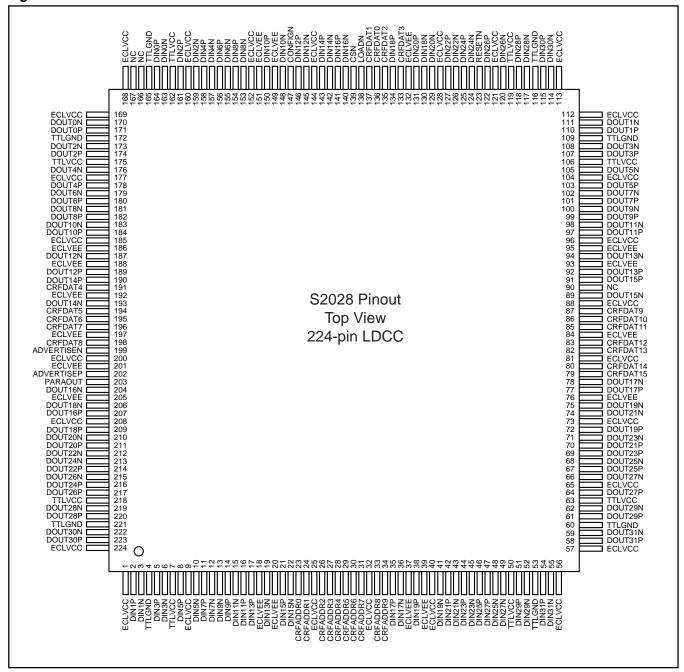

- 224-pin LDCC package

## **APPLICATIONS**

- Internet Switches

- Datacom or telecom switching

- Digital demultiplexing

- Microwave or fiber-optic data distribution

- High-speed automatic test equipment

- Digital video

#### GENERAL DESCRIPTION

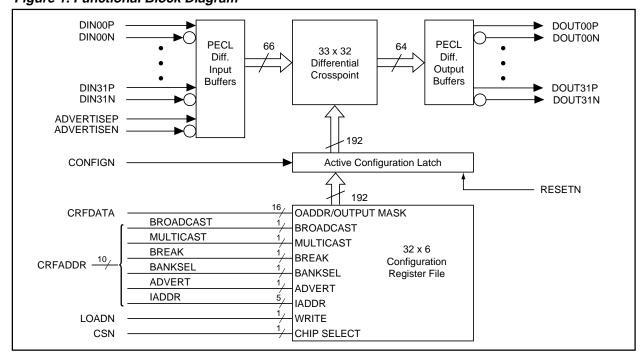

The S2028 is a very high-speed 33 x 32 differential crosspoint switch with fast multicast and broadcast capabilities. It consists of 32 differential PECL input signal pairs that can be connected to any or all of its 32 differential PECL output signal pairs. In addition, the differential output drivers can be individually configured to gate in an additional broadcast channel. This channel can be used as a default advertise channel, or to supply a signal such as a clock to simplify interface design.

Along with a single cycle reconfiguration of the entire 33 x 32 crosspoint switch, the S2028 features single cycle broadcast and fast two cycle multicast configuration. A "break" feature allows fast unicast or multicast disable of the previous configuration.

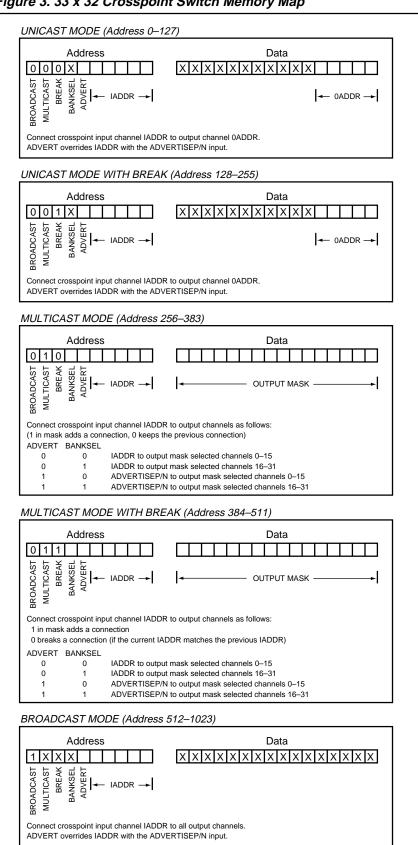

The S2028 contains a unique memory map, which provides full support of the broadcast, multicast, and unicast modes.

The differential 10K PECL logic data path makes the part ideal for high-speed applications. The differential nature of the data path is retained throughout the crosspoint structure, to minimize data distortion and to handle NRZ data rates up to 1.25 gigabits per second.

Figure 1. Functional Block Diagram

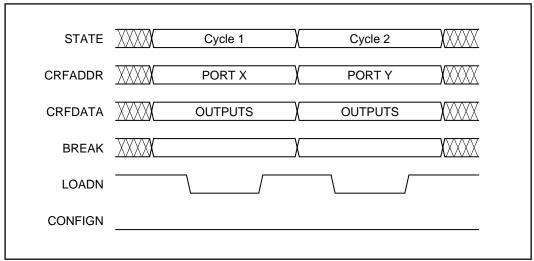

TTL configuration controls simplify interfacing to slower speed circuitry. Once a new configuration has been entered into the configuration register file, the S2028 can be completely reconfigured in only 10 ns without disturbing switch operations.

The configuration register can also be put into transparent mode, reconfiguring all addressed outputs within 10ns after the LOADN signal goes low.

#### **Data Transfer**

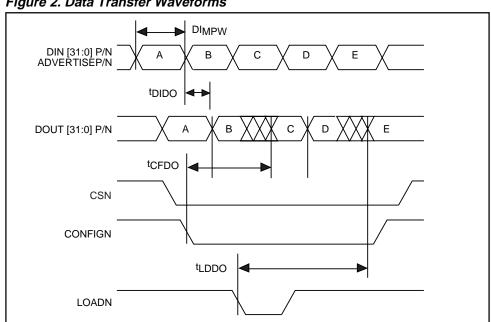

For each configured connection between a differential input pair and an enabled output pair, any data appearing at the input pair and switching at up to 1.25 Gb/s will be passed immediately through to the output pair.

## Configuration

The S2028 can be selectively reconfigured one output channel at a time in unicast mode. 16 output channels at a time in multicast mode, and all 32 output channels simultaneously in broadcast mode. Any number of output channels can be reconfigured simultaneously using the CONFIGN control. Configuration data is stored in all 32 registers, one register for each output channel. As shown in Figure 1, the configuration data is passed in parallel from all 32 registers to a bank of latches which hold the active switch configuration. This two-state arrangement allows any number of output channels to be reconfigured simultaneously.

Each output configuration register holds 6 bits. Five bits are used to select which input channel will be connected to the output channel, and one bit is used to override the input address and instead channel the ADVERTISEP/N input to that output.

The S2028A 33 X 32 Crosspoint Switch interface is designed to connect directly to a microprocessor's address and data bus and R/W signal. A CS input (CSN) is provided to simplify interfacing to the microprocessor's address bus. Most of the device's functions can be programmed by a single instruction in firmware. See the memory map in Figure 3. The memory map depends on the hardware interface. and can be mapped to any 1024 byte address range. In general, the address bus will specify the crosspoint switch input channel, and the data bus will specify the crosspoint switch output channel. The microprocessor or host hardware presents the address and data to the S2028A, the decoder logic enables CSN, and then the microprocessor strobes the Read/Write\* signal (LOADN). (See Figure 2.)

#### **Broadcast Mode**

Writing to any address in the Broadcast Address Space (512-1023) will broadcast the input channel specified on the address bus (IADDR) to all 32 output channels. If the ADVERT bit is set to a 1, IADDR is ignored and the ADVERTISE input is broadcast to all 32 output channels. Broadcasting is a single cycle operation, and does not require strobing of CONFIGN.

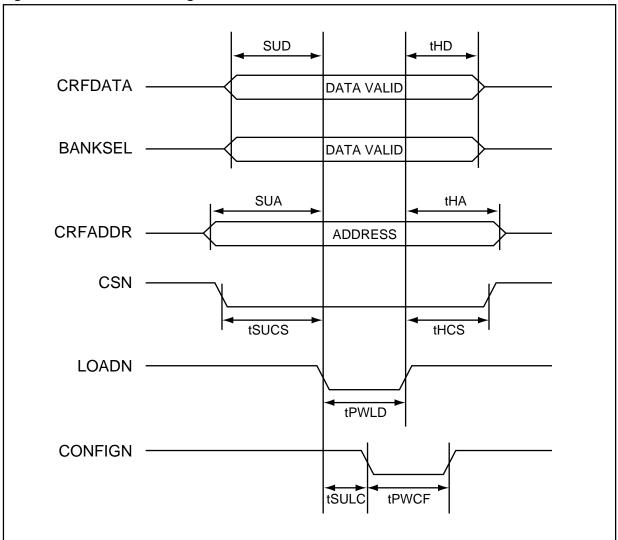

Figure 2. Data Transfer Waveforms

### **Multicast Mode**

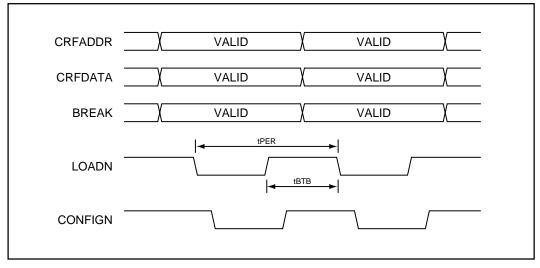

In Multicast Mode, a group of 16 output channels can be configured to connect to one input channel in a single cycle. There are two output channel groups, so all 32 output channels can be configured in two cycles. Each group has its own addess range. Group 0 configures output channels 0-15 while Group 1 configures output channels 16-31. Each bit of the 16 bit data bus (CRFDATA) specifies which of the 16 output channels in the group are to be configured to connect to the input channel.

The address bus IADDR specifies the input channel, and the ADVERT input specifies whether to override that input channel with the ADVERTISEP/N input. The BANKSEL bit specifies which of the two sets of 16 output channels is being addressed. For example, if the address bus contains "0101011001" and the data bus contains "01000110 101011001", then output channels 18, 19, 21, 23, 25, 26 and 30 are configured for connection to input channel 25. If the address bus contains "0101111001" and the data bus is unchanged, then output channels 18, 19, 21, 23, 25, 26 and 30 are configured for connection to the ADVERTISEP/N input.

The Multicast Address Range is from 256-511. Writing to address range 256-383 will maintain the prior configuration for a particular channel, if that channel's output mask bit is set to a "0". The address range 384-511 activates the "break" feature of the S2028A 33X32 Crosspoint Switch. In this mode, for each output channel whose mask bit is set to 0, if the prior configured input channel matches the new requested input channel, the prior configuration is broken and the ADVERTISE input is connected to that output.

### **Unicast Mode**

Writing to the Unicast Address Range (0-255) will configure the input channel specified on the address bus (IADDR) to connect to the output channel specified on the lower 5 bits of the data bus (OADDR). However, if the ADVERT bit is set to a 1, IADDR is ignored and the output channel OADDR is configured to connect to the ADVERTISEP/N input.

Writing to Address Range 0-127 will maintain the prior configuration for a particular channel, if that channel's output mask bit is set to a "0". The address range 128-255 activates the "break" feature. In this mode, for each output channel whose mask bit is set to 0, if the prior configured input channel matches the new requested input channel, the prior configuration is broken and the ADVERTISE input is connected to that output.

## Reconfiguration

When the differential switch is to be reconfigured, the S2028A minimizes the time required through the use of an active configuration latch. While the switch is operational, and prior to the time at which it must be reconfigured, a new configuration can be loaded into the output pair configuration registers. Once the 32 output pair configuration registers contain the desired connection and output pair driver control information, the contents of the registers are transferred in parallel to the active configuration latch by the CONFIGN strobe. This allows multiple connections to be simultaneously changed. Broadcast mode is a single cycle operation and does not require strobing CONFIGN.

The configuration latch can be made transparent by tying the CONFIGN input to a logic 0. When this is done, changes strobed into the output pair configuration registers by the LOADN input will be passed immediately to the switch.

#### **Reset Behavior**

When the RESETN input is asserted, the S2028A assumes a configuration where the ADVERTISEP/N channel is broadcast to all of the differential output drivers. Individual output drivers then remain in this state after RESETN is deasserted, until they are explicitly reconfigured to a new input address.

Figure 3. 33 x 32 Crosspoint Switch Memory Map

**S2028**

Table 1. Pin Assignment and Descriptions

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Level         | I/O            | Pin #                                                                                                                                                                                                                                                                                                                                                                                                    | Description                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| DIN31P DIN31N DIN30P DIN30N DIN29P DIN29N DIN28P DIN28N DIN27P DIN27N DIN26P DIN26P DIN25P DIN25P DIN25P DIN224P DIN23N DIN22P DIN221P DIN221P DIN221P DIN21N DIN20P DIN21N DIN20P DIN21N DIN20P DIN21N DIN19P DIN19N DIN18P DIN18P DIN18P DIN16P DIN16P DIN15N DIN15P DIN15N DIN14P DIN14P DIN15N DIN15P DIN15N DIN15P DIN11N DIN15P DIN11N DIN16P DIN11N DIN11P DIN11 | Diff.<br>PECL | Input<br>Pairs | 54<br>55<br>115<br>114<br>51<br>52<br>118<br>117<br>47<br>49<br>122<br>120<br>46<br>48<br>125<br>124<br>44<br>45<br>127<br>126<br>42<br>43<br>131<br>129<br>38<br>41<br>130<br>35<br>36<br>141<br>140<br>21<br>22<br>143<br>142<br>17<br>19<br>146<br>147<br>149<br>140<br>140<br>141<br>141<br>142<br>143<br>144<br>145<br>150<br>160<br>17<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18 | Input data. Differential. Can be used as single-ended input pairs with V <sub>BB</sub> tied to one side of each differential pair. |

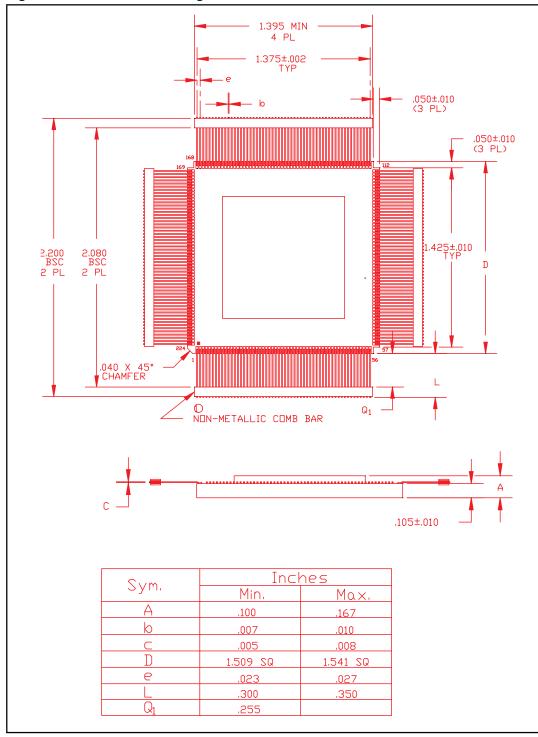

Note: Cavity up counter clockwise pin numbering orientation. (See Figure 5). For cavity down mounting, pin numbering will have clockwise orientation.

# 33 x 32 1.25 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

Table 1. Pin Assignment and Descriptions (Continued)

| Pin Name                                                                                                                         | Level         | I/O             | Pin #                                                                                           | Description                                                                                                                                                 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIN7P DIN7N DIN6P DIN6N DIN5P DIN5N DIN4P DIN4N DIN3P DIN3N DIN2P DIN2N DIN1P DIN1N DIN1P DIN1N DIN0P DIN0N                      | Diff.<br>PECL | Input<br>Pairs  | 11<br>12<br>156<br>155<br>8<br>10<br>158<br>157<br>5<br>6<br>161<br>159<br>2<br>3<br>164<br>163 | Differential PECL input data. Differential inputs can be used as single-ended inputs with V <sub>BB</sub> tied to one side of each differential input pair. |  |  |

| ADVERTISEP<br>ADVERTISEN                                                                                                         | Diff.<br>PECL | Input<br>Pair   | 202<br>199                                                                                      | A 33rd input channel that can be mapped to any or all output channels. Gets mapped to selected outputs when ADVERT is high.                                 |  |  |

| LOADN                                                                                                                            | TTL           | I               | 138                                                                                             | Load strobe, active Low. When low, writes into the crosspoint switch memory when CSN is asserted.                                                           |  |  |

| CONFIGN                                                                                                                          | TTL           | Ī               | 147                                                                                             | Configuration strobe, active Low. When low, parallel loads the contents of the configuration register file into the active configuration latch.             |  |  |

| RESETN                                                                                                                           | TTL           | I               | 123                                                                                             | Reset. Active Low. Sets all the outputs to be tied to the ADVERTISEP/N input.                                                                               |  |  |

| CSN                                                                                                                              |               |                 | 139                                                                                             | Chip select.                                                                                                                                                |  |  |

| PARAOUT                                                                                                                          |               |                 | 203                                                                                             | AMCC test pin. (No connect.)                                                                                                                                |  |  |

| DOUT31P<br>DOUT31N<br>DOUT30P<br>DOUT30N<br>DOUT29P<br>DOUT29N<br>DOUT28P<br>DOUT28N<br>DOUT27P<br>DOUT27N<br>DOUT26P<br>DOUT26N | Diff.<br>PECL | Output<br>pairs | 58<br>59<br>223<br>222<br>61<br>62<br>220<br>219<br>64<br>66<br>217<br>215                      | Output data. Differential.                                                                                                                                  |  |  |

Note: Cavity up counter clockwise pin numbering orientation. (See Figure 5). For cavity down mounting, pin numbering will have clockwise orientation.

S2028

Table 1. Pin Assignment and Descriptions (Continued)

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Level         | I/O          | Pin #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| DOUT25P DOUT24N DOUT24P DOUT24N DOUT23P DOUT23N DOUT22P DOUT21N DOUT21P DOUT21N DOUT20P DOUT20N DOUT19P DOUT18N DOUT18P DOUT17N DOUT16P DOUT15N DOUT15P DOUT15N DOUT14P DOUT14N DOUT14P DOUT14N DOUT14P DOUT14N DOUT14P DOUT11N DOUT12P DOUT11N DOUT11P DOUT11N DOUT10P DOUT10N DOUT19P DOUT10N DOUT5P DOUT5N DOUT6P DOUT6N DOUT6P DOUT6N DOUT6P DOUT6N DOUT6P DOUT6N DOUT6P DOUT7N DOUT6P DOUT1N | Diff.<br>PECL | Output Pairs | 67<br>68<br>216<br>213<br>69<br>71<br>214<br>212<br>70<br>74<br>211<br>210<br>72<br>75<br>209<br>206<br>77<br>78<br>207<br>204<br>91<br>89<br>190<br>193<br>92<br>94<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>190<br>189<br>189<br>100<br>189<br>189<br>100<br>189<br>101<br>102<br>180<br>179<br>178<br>178<br>178<br>178<br>179<br>178<br>178<br>178<br>179<br>179<br>178<br>178<br>179<br>179<br>179<br>179<br>179<br>179<br>179<br>179 | Output data. Differential. |

Note: Cavity up counter clockwise pin numbering orientation. (See Figure 5). For cavity down mounting, pin numbering will have clockwise orientation.

# 33 x 32 1.25 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

Table 1. Pin Assignment and Descriptions (Continued)

| Pin Name                                                                                                                                       | Level | I/O | Pin #                                                                                                 | Description                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CRFDAT0 CRFDAT1 CRFDAT2 CRFDAT3 CRFDAT4 CRFDAT5 CRFDAT6 CRFDAT7 CRFDAT8 CRFDAT9 CRFDAT10 CRFDAT11 CRFDAT11 CRFDAT12 CRFDAT13 CRFDAT14 CRFDAT15 | TTL   | I   | 136<br>137<br>135<br>133<br>191<br>194<br>195<br>196<br>198<br>87<br>86<br>85<br>83<br>82<br>80<br>79 | 16-Bit Data Bus used to specitfy the output channel(s) and direct the ADVERTISE INPUT.                                                         |

| CRFADDR0 CRFADDR1 CRFADDR2 CRFADDR3 CRFADDR4 CRFADDR5 CRFADDR6 CRFADDR7 CRFADDR8 CRFADDR9                                                      | TTL   | I   | 23<br>24<br>26<br>27<br>28<br>29<br>30<br>31<br>33<br>34                                              | 10-Bit Address Bus used to memory map the various operating functions of the device, including Broadcast, Multicast, Break, and Unicast modes. |

Note: Cavity up counter clockwise pin numbering orientation. (See Figure 5). For cavity down mounting, pin numbering will have clockwise orientation.

S2028

Table 1. Pin Assignment and Descriptions (Continued)

| Pin Name | Level | I/O | Pin #                                                                                                                                                       | Description      |

|----------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ECLVCC   | +5V   |     | 1, 9, 25,<br>32, 40,<br>56, 57,<br>65, 73,<br>81, 88,<br>96, 104,<br>112, 113,<br>121, 128,<br>144, 152,<br>160, 168,<br>169, 177,<br>185, 200,<br>208, 224 | ECL Power Supply |

| TTLGND   | GND   |     | 4, 53, 60,<br>109, 116,<br>165, 172,<br>221                                                                                                                 | TTL Ground       |

| TTLVCC   | +5V   |     | 7, 50, 63,<br>106, 119,<br>162, 175,<br>218                                                                                                                 | TTL Power Supply |

| ECLVEE   | GND   |     | 18, 20,<br>37, 39,<br>76, 84,<br>93, 95,<br>132, 149,<br>151, 186,<br>188, 192,<br>197, 201,<br>205                                                         | ECL Ground       |

| NC       |       |     | 90, 166,<br>167                                                                                                                                             | No Connect       |

Note: Cavity up counter clockwise pin numbering orientation. (See Figure 5). For cavity down mounting, pin numbering will have clockwise orientation.

Figure 4. S2028 Pinout

Figure 5. 224-Pin LDCC Package

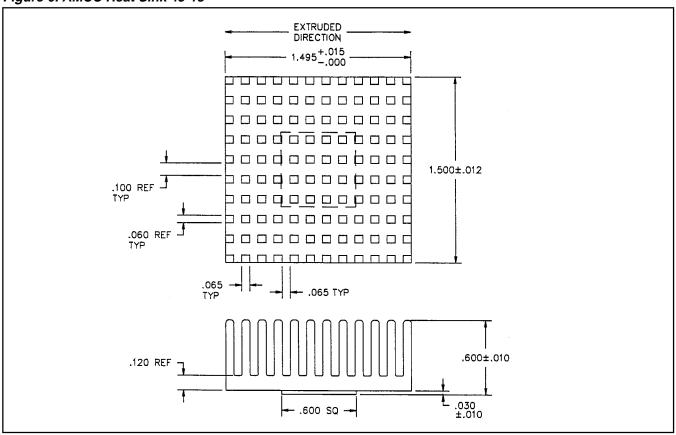

Figure 6. AMCC Heat Sink 45-18

## **Thermal Management**

The S2028A device requires sufficient thermal management for proper functionality and reliability. It is recommended that the user investigate, define, and implement correct techniques in managing the power of this product. Techniques to consider include: headspreading through metal layers within your PCB in addition to heatsinking with mounted heatsink and moving; fluid controlled thermal management.

Table 2. S2028 Thermal Data

AMCC Recommended: Calculation of required  $T_{ja}$  for S2028:  $T_{Jmax} = 130^{\circ}C$   $T_{ja} = (130-70)/16 = 3.75^{\circ}C/W$  Since:  $T_{ja} = T_{jc} + T_{ca}$  Heatsink must meet:  $T_{ca} = 3.75-1.8 = 1.95^{\circ}C/W$

Note: The best heatsink currently available at AMCC is rated 2.1 °C/W with 1000 LFPM airflow. (See Figure 6).

## Table 3. Absolute Maximum Ratings

| Supply Voltage V <sub>cc</sub>                | 7.0V                               |

|-----------------------------------------------|------------------------------------|

| PECL Input Voltage                            | $V_{\rm cc}$ -2.5V to $V_{\rm cc}$ |

| PECL Output Source Current (continuous)       | -50mA DC                           |

| TTL Input Voltage                             | 5.5V                               |

| Operating Junction Temperature T <sub>J</sub> | +150°C                             |

| Storage Temperature                           | -65° to +150°C                     |

## Table 4. Recommended Operating Conditions

| Parameter                      | Min  | Nom | Max  | Units |

|--------------------------------|------|-----|------|-------|

| Supply Voltage V <sub>cc</sub> | 4.75 | 5.0 | 5.25 | V     |

| Ambient Temperature            | 0    |     | 70   | °C    |

| Junction Temperature           |      |     | 130  | °C    |

| I <sub>cc</sub>                |      | 3.5 | 4.50 | А     |

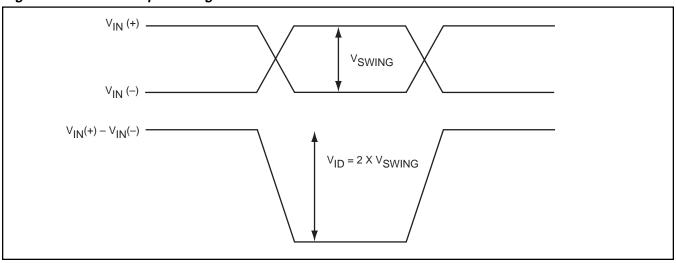

Figure 7. Differential Input Voltage

Note:  $V_{IN}(+) - V_{IN}(-)$  is the algebraic difference of the input signals.

Table 5. PECL DC Characteristics<sup>3</sup>

| Symbol                       | Min       | Тур       | Max       | Units |

|------------------------------|-----------|-----------|-----------|-------|

| V <sub>IH</sub> <sup>2</sup> | Vcc -1145 |           | Vcc -600  | mV    |

| V <sub>IL</sub> <sup>2</sup> | Vcc -2000 |           | Vcc -1450 | mV    |

| V <sub>BIAS</sub> 1,2        |           | Vcc -1300 |           | mV    |

| I <sub>IH</sub> <sup>2</sup> |           |           | 30        | μΑ    |

| 1 <sub> L</sub> 2            |           |           | -0.5      | μΑ    |

<sup>1.</sup> Internal bias point.

### Table 6. Differential PECL Characteristics

| Symbol            | Min | Тур | Max  | Units |

|-------------------|-----|-----|------|-------|

| V <sub>ID</sub> 1 | 500 |     | 2800 | mV    |

1. Differential input voltage - algebraic difference.

<sup>2.</sup> Single-ended connection.

<sup>3.</sup> DC is considered to be an input signal between 0Hz and 1KHz.

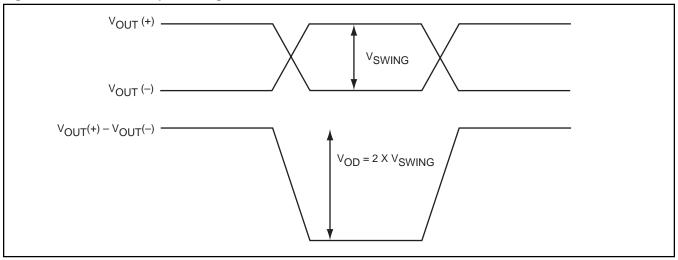

Figure 8. Differential Output Voltage

Note:  $V_{OUT}(+) - V_{OUT}(-)$  is the algebraic difference of the input signals.

Table 7. PECL DC Characteristics<sup>2</sup>

| Symbol                       | Min       | Тур | Max       | Units |

|------------------------------|-----------|-----|-----------|-------|

| V <sub>OH</sub> <sup>1</sup> | Vcc -1095 |     | Vcc –695  | mV    |

| V <sub>OL</sub> <sup>1</sup> | Vcc –1900 |     | Vcc -1365 | mV    |

| I <sub>OH</sub>              |           | 20  |           | mA    |

| I <sub>OL</sub>              |           | 5   |           | mA    |

<sup>1.</sup> All outputs are loaded with  $50\Omega$  to Vcc –2V.

Table 8. Differential PECL Characteristics

| Symbol            | Min | Тур | Max  | Units |

|-------------------|-----|-----|------|-------|

| V <sub>OD</sub> 1 | 700 |     | 2330 | mV    |

<sup>1.</sup> Differential output voltage - algebraic difference.

<sup>2.</sup> DC is considered to be an output signal between 0Hz and 1KHz.

# 33 x 32 1.25 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

## Table 9. TTL Input DC Characteristics

|                              |                              |                                                   | Comm | Commercial 0° to 70°C |      |      |

|------------------------------|------------------------------|---------------------------------------------------|------|-----------------------|------|------|

| Symbol                       | Parameter                    | Conditions                                        | Min  | Typ <sup>1</sup>      | Max  | Unit |

| V <sub>IH</sub> <sup>2</sup> | Input HIGH Voltage           | Guaranteed Input HIGH Voltage for all input pairs | 2.0  |                       |      | V    |

| V <sub>IL</sub> <sup>2</sup> | Input LOW Voltage            | Guaranteed Input LOW Voltage for all input pairs  |      |                       | 0.8  | V    |

| VIK                          | Input Clamp Diode<br>Voltage | $V_{CC} = MIN, I_{IN} = -18 \text{ mA}$           |      | -0.8                  | -1.2 | V    |

| Ι <sub>ΙΗ</sub>              | Input HIGH Current           | $V_{CC} = MAX, V_{IN} = 2.7V$                     |      |                       | 50   | μА   |

| l <sub>l</sub>               | Input HIGH Current at Max.   | $V_{CC} = MAX$ , $V_{IN} = V_{CC} + 0.3V$         |      |                       | 1    | mA   |

| Ι <sub>ΙL</sub>              | Input LOW Current            | $V_{CC} = MAX, V_{IN} = 0.5V$                     |      |                       | -0.4 | mA   |

## Table 10. Data Transfer Timing<sup>1</sup>

| Symbol            | Description                                                                                     | Min.  | Max. | Units  |

|-------------------|-------------------------------------------------------------------------------------------------|-------|------|--------|

| <sup>t</sup> DIDO | Propagation delay from DIN[31:0] P/N or ADVERTISEP/N to DOUT[31:0] P/N                          |       | 3    | ns     |

| <sup>t</sup> CFDO | Propagation delay from falling edge of CONFIGN to DOUT[31:0] P/N valid                          |       | 6    | ns     |

| <sup>t</sup> LDDO | Propagation delay from falling edge of LOADN to DOUT[31:0] P/N valid (When CONFIGN is held low) |       | 8.5  | ns     |

| DI <sub>MPW</sub> | Pulse width of DIN[31:0] P/N                                                                    | 0.650 |      | ns     |

| F <sub>MAX</sub>  | Data rate                                                                                       | 1250  | 1250 | Mbit/s |

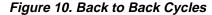

| t <sub>PER</sub>  | Configuration cycle time                                                                        | 10    |      | ns     |

| t <sub>BTB</sub>  | Back to back cycle time                                                                         | 5     |      | ns     |

<sup>1.</sup> All timing measured from the  $\ensuremath{V_{\text{CC}}}$  -1.3V point on the signals.

Typical limits are at 25°C, V<sub>CC</sub> = 5.0V.

These input levels provide a zero noise immunity and should only be tested in a static, noise-free environment.

S2028

Table 11. Reconfiguration Timing<sup>1</sup>

| Symbol            | Description                                                                                   |     | Max. | Units |

|-------------------|-----------------------------------------------------------------------------------------------|-----|------|-------|

| <sup>t</sup> SUD  | Setup time of CRFDATA before falling edge of LOADN                                            | 2   |      | ns    |

| t <sub>HD</sub>   | Hold time of CRFDATA after rising edge of LOADN                                               | 2   |      | ns    |

| <sup>t</sup> SUA  | Setup time of CRFADDR before falling edge of LOADN                                            | 2   |      | ns    |

| t <sub>HA</sub>   | Hold time of CRFADDR after rising edge of LOADN                                               | 1.5 |      | ns    |

| tsucs             | Setup time of CSN before falling edge of LOADN                                                | 2   |      | ns    |

| t <sub>HCS</sub>  | Hold time of CSN after rising edge of LOADN                                                   | 2   |      | ns    |

| <sup>t</sup> SULC | Setup time of LOADN to CONFIGN so that the falling edge of CONFIGN will start reconfiguration | 1.5 |      | ns    |

| tPWLD             | Pulse width low of LOADN                                                                      | 2   |      | ns    |

| t <sub>PWCF</sub> | Pulse width low of CONFIGN                                                                    | 2   |      | ns    |

<sup>1.</sup> All timing measured from the 1.5V point on the signals.

Figure 9. Data Transfer Timing

Figure 11. Back to Back Multicast Cycles with CONFIG Low

Figure 12. Back to Back Unicast Cycles with CONFIGN Low

## 33 x 32 1.25 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

#### Ordering Information

| PREFIX                 | DEVICE        |                |              | PACKAGE                          |  |

|------------------------|---------------|----------------|--------------|----------------------------------|--|

| S – Integrated Circuit |               | 2028A          |              | A – 224 LDCC with straight leads |  |

|                        | X<br>Prefix D | XXXX<br>Device | X<br>Package |                                  |  |

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (619) 450-9333 • (800)755-2622 • Fax: (619) 450-9885 http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1999 Applied Micro Circuits Corporation