# SARA®-2 ATM Cell Processing IC Device TXC-05551

DATA SHEET PRODUCT PREVIEW

#### FEATURES I

- Functionality enabled by application-specific microcode (e.g., SARA-*Lite*™ Microcode)

- Full-duplex segmentation and reassembly of multiple VCs up to 155 Mbit/s in each direction

- Integrated SONET/SDH 155 Mbit/s framer

- · Optional 8-bit UTOPIA interface

- PCI bus master and slave interface supports efficient, low latency burst transfers

- Complete SAR functions for AAL5, AAL3/4 and AAL0 (null) in host memory

- Support for AAL1

- Provides over 64,000 virtual connections on transmit and receive

- Includes non-contiguous variable size packet buffers providing scatter and gather function with arbitrary byte alignment and byte order.

- Flexible scheduler provides per-connection rate management for VBR and CBR

- Programmable RISC core supports customization and vendor-specific additional features

- Supports ATM Forum UBR traffic flow control.

- Reassembly on the basis of any arbitrary subfield of the 24/28-bit VPI/VCI field

- Provides host-controlled OAM/Signalling cell insertion and extraction

- Supports ATM Forum MIB

- Boundary scan capability (IEEE 1149.1)

- Single +3.3 V, ± 5% power supply

- · 225-lead plastic ball grid array package

### **DESCRIPTION**

The SARA-2 device is intended to be used with feature/ application-specific microcode that gives it a particular set of ATM segmentation and reassembly (SAR) performance characteristics. It can be used to implement low-cost ATM adapter cards, legacy LAN to ATM hubs, and routers. It provides a PCI-based host interface to segment and reassemble packets directly in the host memory. In the transmit direction, it generates cells that conform to the ATM Forum traffic management service classes, such as CBR, VBR, and UBR. On the receive side, the SARA-2 allows simultaneous reassembly of over 64,000 connections directly in the host memory. The host buffers may be arbitrarily-sized blocks placed on arbitrary byte boundaries. An integrated SONET/SDH STS-1/STS-3c/ STM-1 framer and overhead termination supports complete framing, cell delineation and cell rate decoupling functions. The UTOPIA interface supports connection to other line rates or ATM layer devices.

### **APPLICATIONS**

- ATM LAN hub

- Router

- Adapter cards

Copyright © 1998 TranSwitch Corporation

SARA-2, SARA-Lite, and CellBus are trademarks of TranSwitch Corporation

TranSwitch, TXC, CUBIT and SARA are registered trademarks of TranSwitch Corporation

Document Number: PRODUCT PREVIEW TXC-05551-MB Ed. 4, January 1998

PRODUCT PREVIEW information documents contain information on products in their formative or design phase of development. Features, characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

# **TABLE OF CONTENTS**

| SECTION                                                 | <u>PAGE</u> |

|---------------------------------------------------------|-------------|

| List of Figures                                         | 3           |

| Overview                                                | 4           |

| Block Diagram                                           | 6           |

| Block Diagram Description                               | 6           |

| Lead Diagram                                            | 8           |

| Lead Descriptions                                       | 9           |

| Absolute Maximum Ratings and Environmental Limitations  | 17          |

| Thermal Characteristics                                 | 17          |

| Recommended Operating Conditions and Power Requirements | 17          |

| Input, Output and I/O Parameters                        | 18          |

| Operation                                               |             |

| Segmentation and Reassembly Overview                    |             |

| Line Interface                                          |             |

| The ATM Communications Processor (ACP)                  | 31          |

| DMA Controller                                          | 33          |

| Traffic Shaping                                         |             |

| Memory Controller                                       | 34          |

| PCI Interface                                           |             |

| PCI Bus Master                                          | 34          |

| PCI Bus Slave                                           |             |

| Serial EEPROM Interface                                 | 35          |

| Data Alignment                                          |             |

| PCI Bus Performance                                     | 36          |

| PCI Configuration Register Descriptions                 |             |

| PCI Host Address Map                                    |             |

| Register Descriptions                                   |             |

| Status Register                                         |             |

| Control/Enable Register                                 |             |

| Interrupt Holdoff Timer Control Register (ITIMER)       |             |

| Instruction RAM Write Enable Register (IRAM_WE/PROTECT) |             |

| Host Communication Ring Registers                       |             |

| Memory Access Control Registers                         |             |

| Mode Register 0                                         |             |

| Mode Register 1                                         |             |

| Mode Register 2                                         |             |

| Memory Access Violation Status Registers (MACCVS)       |             |

| Memory Access Violation Address Register (MACCVA)       |             |

| Framer Control and Status Registers                     |             |

| Data Structures                                         |             |

| Segmentation VC Structure                               |             |

| Rate Control Table                                      |             |

| Buffer Descriptor Table                                 |             |

| Reassembly Hash Table                                   |             |

| Reassembly VC Structure                                 |             |

| Reassembly Buffer Pool                                  |             |

| Message Pool                                            |             |

| Cell Buffers                                            |             |

| Request Ring / Indicate Ring                            |             |

| External Circuit Requirements                           |             |

| Test Access Port                                        |             |

| Timing Characteristics                                  |             |

| Line Interface                                          | 65          |

| Serial EEPROM Interface                 | 76 |

|-----------------------------------------|----|

| PCI Interface                           | 77 |

| Control Memory Interface                | 79 |

| Applications                            | 81 |

| Package Information                     | 82 |

| Ordering Information                    | 83 |

| Related Products                        | 83 |

| Standards Documentation Sources         | 84 |

| List of Data Sheet Changes              | 86 |

| Documentation Update Registration Form* | 91 |

# **LIST OF FIGURES**

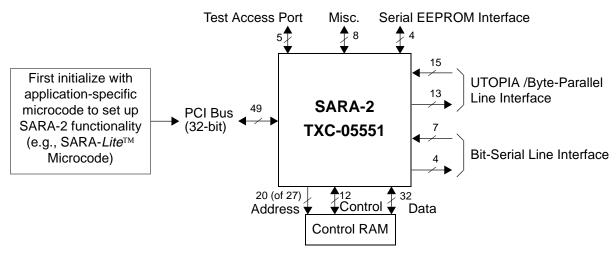

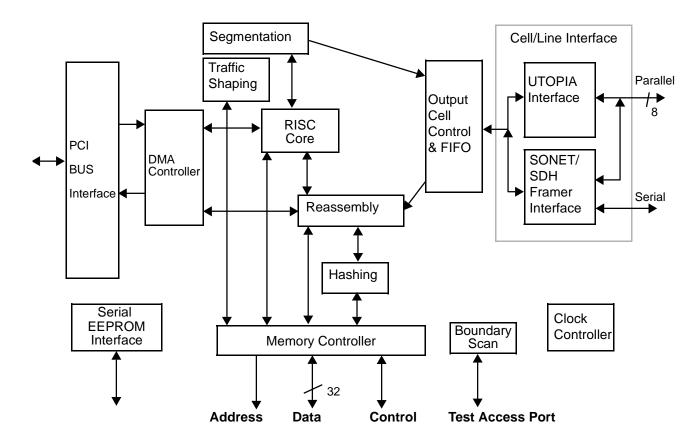

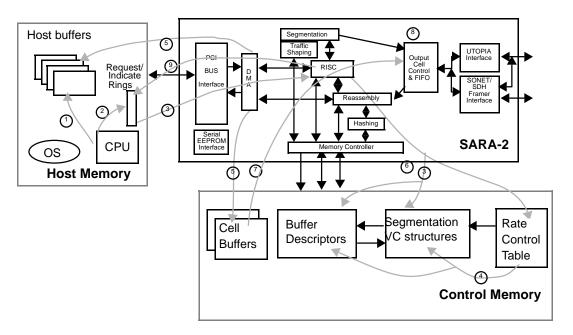

| Figure 1.  | SARA-2 TXC-05551 Block Diagram                                    | 6    |

|------------|-------------------------------------------------------------------|------|

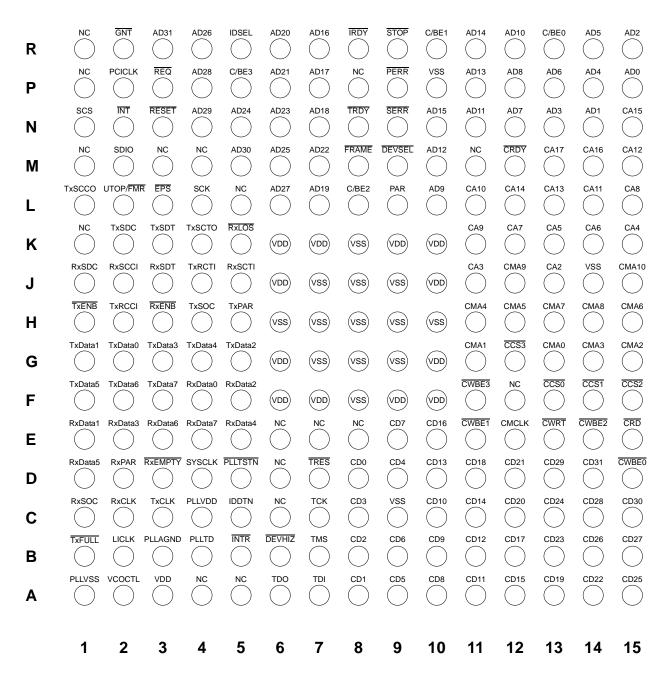

| Figure 2.  | SARA-2 TXC-05551 Lead Diagram                                     |      |

| Figure 3.  | Segmentation Data Flow                                            |      |

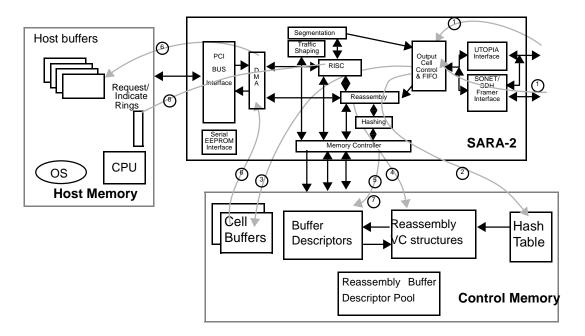

| Figure 4.  | Reassembly Data Flow                                              | . 24 |

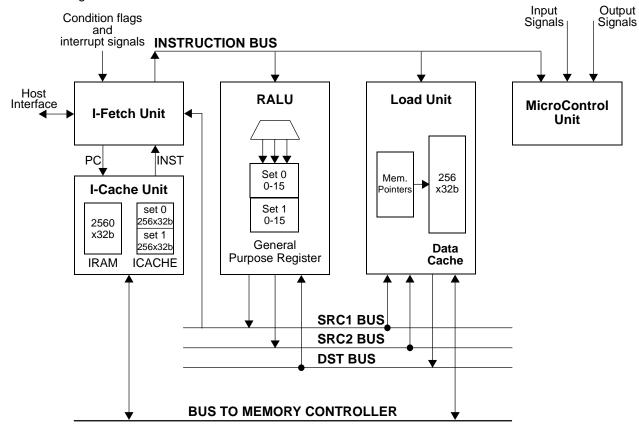

| Figure 5.  | ACP RISC Core Architecture                                        | . 31 |

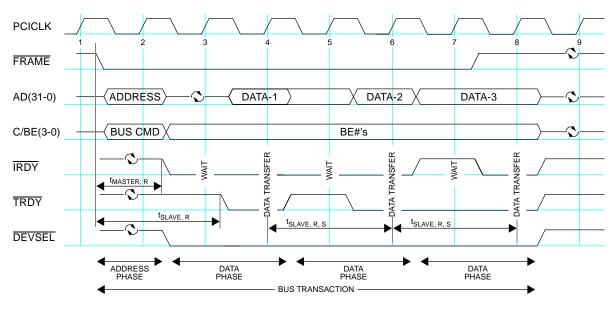

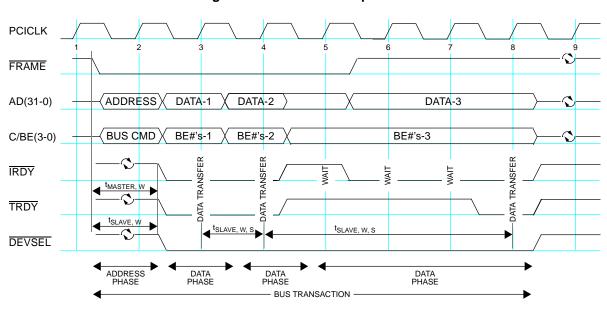

| Figure 6.  | PCI Bus Read Operation                                            | . 37 |

| Figure 7.  | PCI Bus Write Operation                                           |      |

| Figure 8.  | PCI Bus Master Performance                                        | . 38 |

| Figure 9.  | PCI Bus Slave Performance                                         |      |

| Figure 10. | PCI Configuration Space                                           | . 39 |

| Figure 11. | PCI Host Address Memory Map                                       |      |

| Figure 12. | Segmentation Virtual Circuit Parameters                           | . 55 |

| Figure 13. | Rate Control Table                                                |      |

| Figure 14. | Buffer Descriptor Parameters for Segmentation                     | . 59 |

| Figure 15. | Buffer Descriptor Parameters for Reassembly                       | . 59 |

| Figure 16. | Reassembly Hash Table                                             |      |

| Figure 17. | Hash Index Computation Logic                                      |      |

| Figure 18. | Reassembly Virtual Circuit Parameters                             | 62   |

| Figure 19. |                                                                   |      |

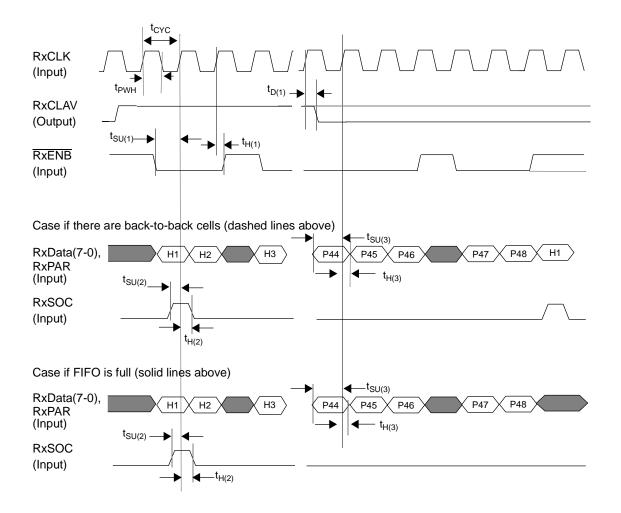

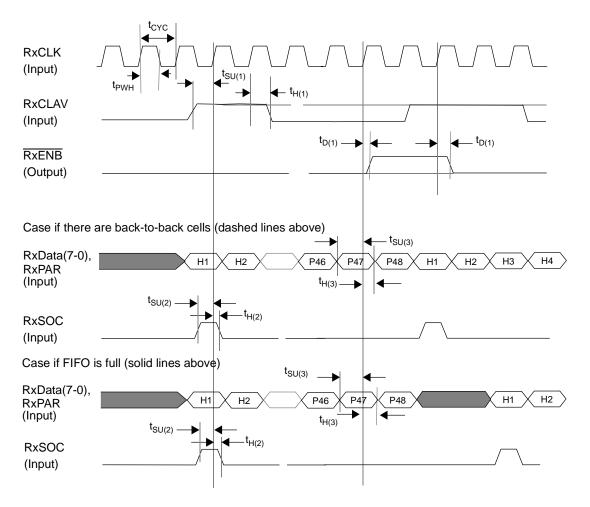

| Figure 20. | Cell Receive Timing - Cell Level Handshake for UTOPIA-PHY Mode    | 65   |

| Figure 21. | Cell Transmit Timing - Cell Level Handshake for UTOPIA-PHY Mode   | 67   |

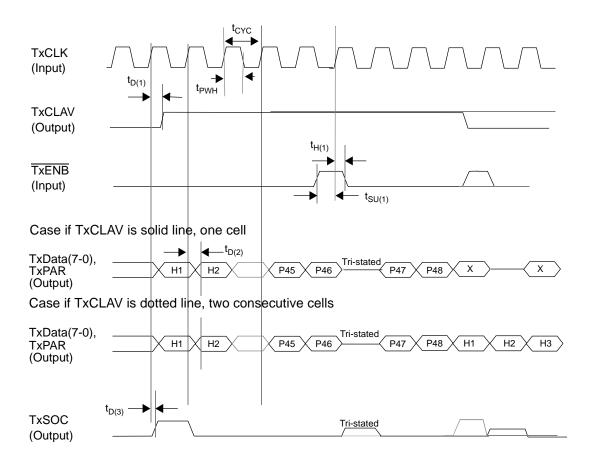

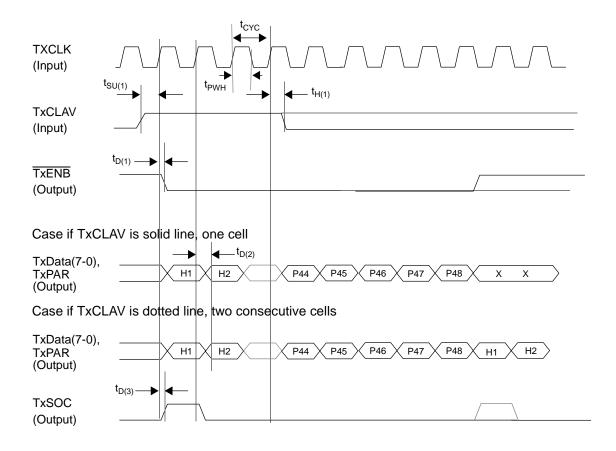

| Figure 22. | Cell Receive Timing - Octet Level Handshake for UTOPIA-PHY Mode   | . 68 |

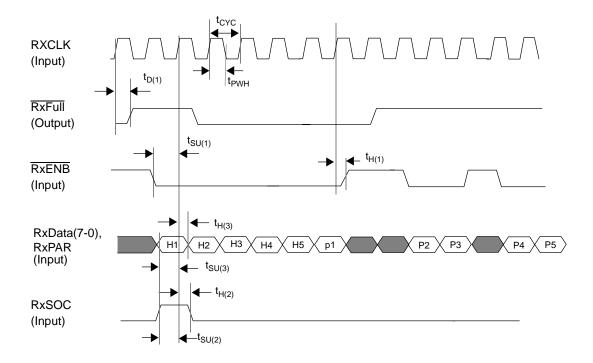

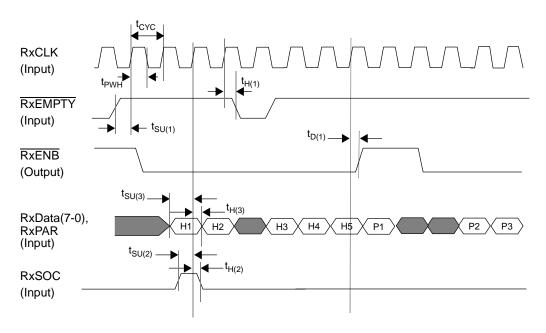

| Figure 23. | Cell Transmit Timing - Octet Level Handshake for UTOPIA-PHY Mode  | 69   |

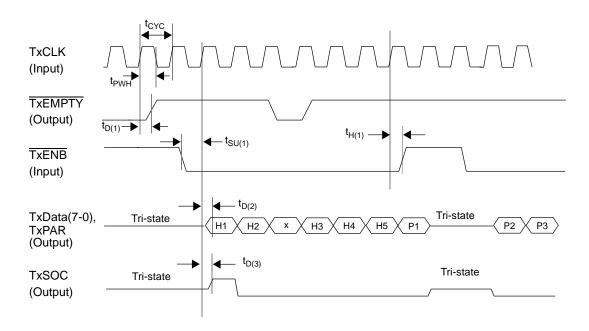

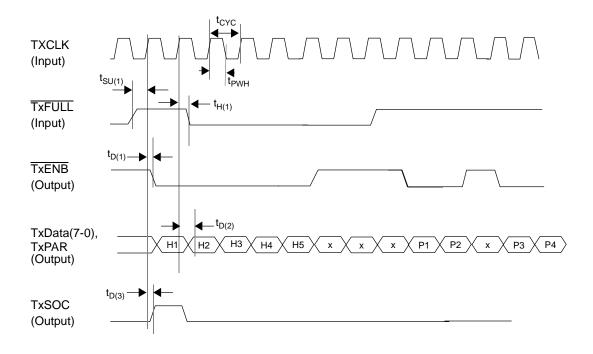

| Figure 24. | Cell Receive Timing - Cell Level Handshake for UTOPIA-ATM Mode    | . 70 |

| Figure 25. | Cell Transmit Timing - Cell Level Handshake for UTOPIA-ATM Mode   | 71   |

| Figure 26. | Cell Receive Timing - Octet Level Handshake for UTOPIA - ATM Mode | 72   |

| Figure 27. | Cell Transmit Timing - Octet Level Handshake for UTOPIA-ATM Mode  | 73   |

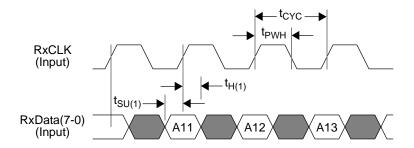

| Figure 28. | Byte-Parallel Receive Line Interface Timing                       | . 74 |

| Figure 29. | Byte-Parallel Transmit Line Interface Timing                      | 74   |

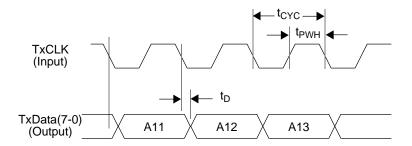

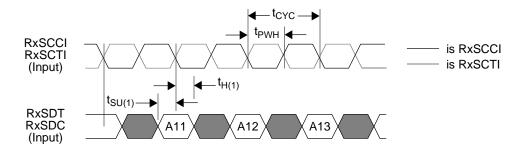

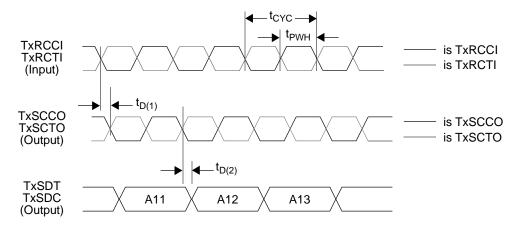

| Figure 30. | Bit-Serial Receive Line Interface Timing                          | . 75 |

| Figure 31. | Bit-Serial Transmit Line Interface Timing                         | . 75 |

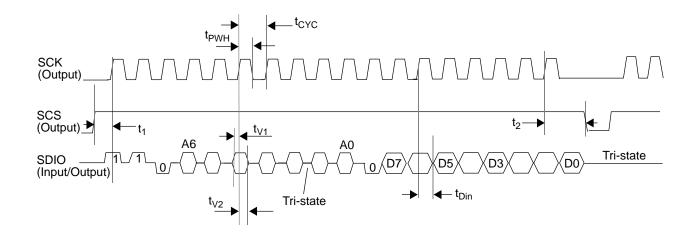

| Figure 32. | Read Instruction Timing for Serial EEPROM Interface               | . 76 |

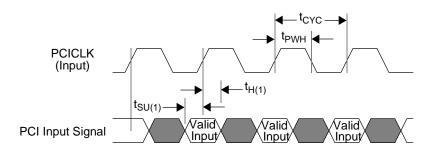

| Figure 33. | PCI Signals Input Timing                                          | . 77 |

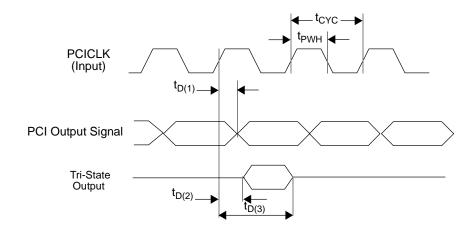

| Figure 34. | PCI Signals Output Timing                                         | . 78 |

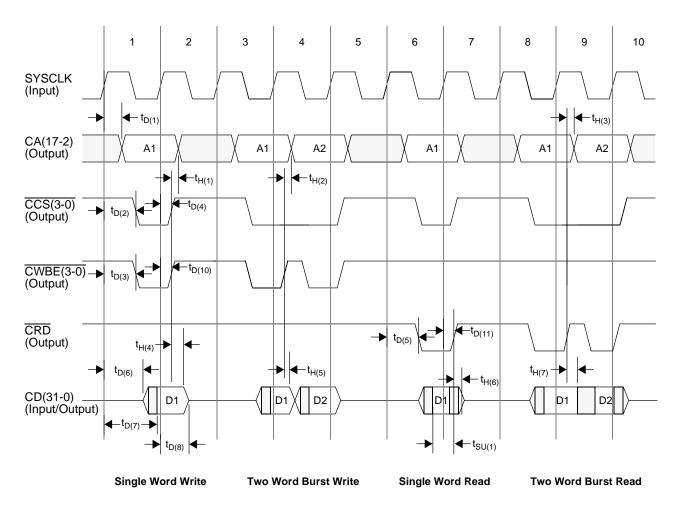

| Figure 35. | Control Memory Read/Write Timing                                  |      |

| Figure 36. | SARA-2 in an ATM Access Hub Application                           | . 81 |

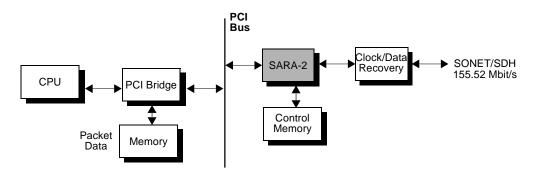

| Figure 37. |                                                                   |      |

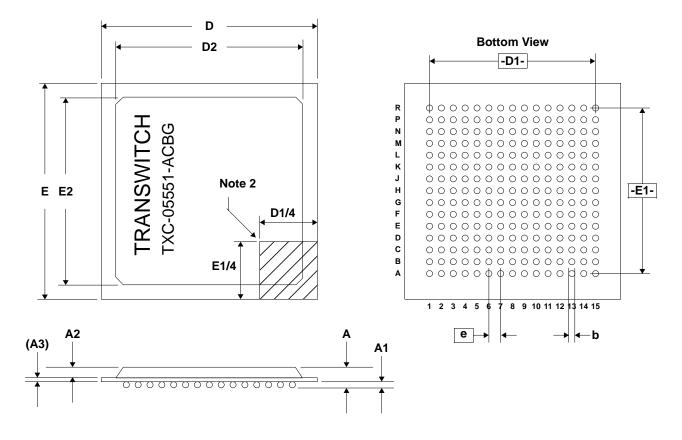

| Figure 38. | SARA-2 TXC-05551 225-Lead Plastic Ball Grid Array Package         | . 82 |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

### **OVERVIEW**

The SARA-2 device is intended to be used with feature/application-specific microcode for its integral RISC CPU core that gives it a particular set of ATM segmentation and reassembly (SAR) performance characteristics. It can be used to implement low-cost ATM adapter cards, legacy LAN to ATM hubs, and routers. This Data Sheet describes the performance of the device, but in some areas it describes characteristics which are present only when the microcode is installed. The Data Sheet describes the characteristics that support the first such microcode introduced by TranSwitch, which is the SARA-*Lite*™ Microcode. The combination of the SARA-2 device and the SARA-*Lite*™ Microcode provides for AAL type 0 or type 5 segmentation and reassembly with Constant Bit Rate (CBR), Variable Bit Rate (VBR) and Unspecified Bit Rate (UBR) traffic management, and supports frame relay and LAN emulation applications, which may be implemented via software. Further information on this combination is provided in the SARA-*Lite* Product Summary document, number TXC-05551-SCDA-PS1.

The SARA-2 device is provided in a 225-lead plastic ball grid array package with solder ball leads and operates from a single +3.3 V supply. The device incorporates AAL processing for full-duplex operation up to 155 Mbit/s. The SARA-2 integrates a PCI-based host interface to segment and reassemble packets directly in the host memory. The device is capable of supporting over 64,000 connections simultaneously in the transmit and receive directions. In the transmit direction, the SARA-2 generates cells that conform to the ATM Forum traffic management service classes, such as CBR, VBR, and UBR. On the receive side, the SARA-2 allows simultaneous reassembly of over 64,000 connections directly in the host memory. The host buffers may be arbitrarily-sized blocks placed on arbitrary byte boundaries. An integrated SONET/SDH STS-1/STS-3c/STM-1 framer and overhead termination supports complete framing, cell delineation and cell rate decoupling functions. The UTOPIA interface supports connection to other line rates or ATM layer devices.

### **Major Features**

- Full-duplex cell processing at 155.52 Mbit/s data rates: Concurrent, uninterrupted, bidirectional data streams can be supported by the SARA-2 at a maximum bit rate of 155.52 Mbit/s. The autonomous operational model used by the SARA-2, together with an efficient message-passing host interface, minimizes the host device driver overhead required to support these data rates.

- 50 MHz RISC CPU core: The RISC core executes up to 50 million instructions per second, allowing it to perform many of the ATM and AAL protocol functions in firmware. The firmware for the core resides in on-chip RAM for maximum flexibility and easy upgrades. The RISC core also contains a 2048-byte instruction cache for executing instructions from external memory and a 1024-byte hardware-managed data cache to speed up loads and stores. The core communicates with the remainder of the logic via on-chip queues and device registers, which are mapped into the core register set to permit fast, low-overhead access. The RISC core performs most of the host communication tasks, allowing for a highly flexible implementation that can perform full-duplex segmentation and reassembly of 53-byte ATM cells at a 155.52 Mbit/s data rate.

- Support for multiple AAL protocols: The SARA-2 permits the AAL5, AAL3/4, AAL1 and AAL0 (raw cells) protocols to be assigned on a per-virtual-circuit basis, regardless of the number of active virtual circuits. For AAL1, the SARA-2 generates and verifies a header conforming to AAL 1 protocol without clock recovery. In AAL0 mode, either 64 bytes or 48 bytes of information may be copied between external host memory and internal cell buffers. Full transfer bandwidth can be maintained for all AAL types supported.

- Support for Convergence Sublayer protocols: The SARA-2 provides complete AAL3/4 and AAL5

Convergence Sublayer (CS) protocols encapsulation and termination in hardware. The AAL1 CS protocol is performed in firmware. The SARA-2 inserts a CSI bit provided by the host for transmit and extracts a received CSI bit for forwarding to the host. Firmware running on the RISC core facilitates flexible implementation and application specific customization for Frame Relay, LAN Emulation and video distribution applications.

- Traffic Shaper: The SARA-2 implements hardware-based traffic shaping for CBR and VBR traffic classes and provides hardware-assisted, firmware-controlled traffic shaping for UBR traffic classes.

- PCI-based host interface port. A fully compliant (PCI Local Bus Specification revision 2.1) PCI bus interface unit is provided to allow interfacing to host processors that support the PCI bus. All internal device registers and local memory resources available to the SARA-2 are also visible from the host interface port. Two 64-byte burst FIFOs allow the PCI bus interface to operate with PCI bus clock rates of up to 33 MHz with no wait states, yielding a peak transfer bandwidth of 132 Mbyte/s. A set of on-chip communication registers and hardware communication queue logic are provided to facilitate communications between the SARA-2 and a host processor.

- Non-Volatile Memory Interface for PCI configuration: The SARA-2 provides a serial EEPROM interface to support optional customization of the PCI configuration space.

- Integrated SONET/SDH Framer: The SARA-2 contains an on-chip SONET/SDH framer unit, which

frames incoming and outgoing serial/parallel data at 51.84 Mbit/s and 155.52 Mbit/s rates using the

STS-1 and STS-3c/STM-1 line codes, respectively. An external clock and data recovery device and

appropriate transceivers (optical or electrical) are the only additional components needed to interface

to the physical medium. It also contains functional blocks that perform cell delineation, payload descrambling, HEC single bit error correction and cell rate decoupling.

- UTOPIA Interface: The device contains a full-duplex, byte-wide cell interface compliant to the ATM

Forum Level 1 UTOPIA specification. The cell interface can be programmed to operate as either a

UTOPIA PHY-layer interface or an ATM-layer interface to allow seamless connection to an ATM

switching port or to other physical layer devices. The device also supports both cell-level handshake

and byte-level handshake.

- Number of active virtual circuits limited only by external memory: The SARA-2 imposes no internal hardware limit on the number of active virtual circuits for either transmit or receive; the number of virtual circuits is limited only by the local memory space required to hold segmentation and reassembly data structures.

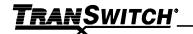

- Hashing Function: The SARA-2 implements a programmable hashing function to support arbitrary VPI/VCI assignment and to speed up virtual circuit table lookups for reassembly functions.

- Low-latency cell processing algorithms: Novel recirculating cell buffer algorithms, coupled with a

dedicated cell buffer queue, are used to allow high-throughput, low-latency cell processing without

complex firmware or host device driver interactions. The on-demand, low-latency processing also

permits the use of a small number of constantly recycled cell buffers, rather than a large number of

expensive data buffers, without compromising performance.

#### **BLOCK DIAGRAM**

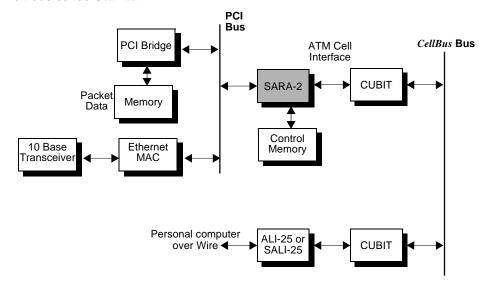

Figure 1. SARA-2 TXC-05551 Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

A block diagram of the SARA-2 ATM Cell Processing IC device is shown in Figure 1. The SARA-2 consists of several functional blocks which are described in the following paragraphs.

- The PCI Bus Interface block implements the complete PCI bus protocol and acts as both a bus master and slave on the PCI bus. It provides access to the SARA-2 registers and the local memory, allowing the host processor to configure, control and communicate with the SARA-2. The interface is a bus-master interface for reading and writing cells from/to the packet memory for segmentation and reassembly.

- The DMA Controller block handles concurrent bidirectional transfers between the host and the SARA-2, supporting segmentation and reassembly directly in the host memory. The DMA controller incorporates powerful scatter-gather mechanisms using chains of linked buffer descriptors to describe the locations of arbitrarily-sized blocks of transmit or receive data placed on arbitrary byte boundaries.

- The Memory Controller block arbitrates access to the local control memory and generates the data transfer signals for the control memory. It is used to access VC structure, buffer descriptor (BD) and cell buffers maintained in the control memory. It provides a direct interface to high speed SRAM memory devices, with no requirement for intermediate 'glue' logic circuits.

- The Output Cell Control & FIFO block supports concurrent bidirectional transfer of data to and from the external line/cell interface. Two-cell deep buffers in the transmit direction and two-cell deep buffers in the receive direction absorb system latencies, enhancing throughput.

- The Hashing block implements a hardware hash table lookup mechanism that uses hash buckets in the local memory to locate the VC state information required for reassembly of received cells. The hashing mechanisms allow support of arbitrary VPI/VCI assignment when a connection is established.

- The Cell/Line Interface block can be configured as either a UTOPIA interface or a byte-parallel or bitserial SONET/SDH interface. When configured as a UTOPIA interface, it is used for transferring ATM cells to the external logic. Optionally, a built-in STS-1/STS-3c/STM-1 framer can be used to interface to external clock recovery devices. The built-in framer performs complete line framing, cell delineation and cell rate decoupling functions. When the internal framer is used, a serial interface is also supported.

- The Segmentation and Reassembly blocks perform all functions related to AAL3/4 and AAL5 processing and a majority of the functions required for AAL1 processing.

- The Traffic Shaping block is responsible for scheduling and rate management for all connections.

- The *RISC Core* block is responsible for control and supervisory functions and for communication with the host.

- The *Serial EEPROM Interface* block is used to support optional customization of PCI configuration space on power-up reset.

- The Boundary Scan block provides a Test Access Port capability conforming to the IEEE 1149.1 standard.

Further information on device operation and the interfaces to external circuits is provided below in the Operation section.

### **LEAD DIAGRAM**

Notes: This is the bottom view. The leads are solder balls. See Figure 38 for package information. Some signal Symbols have been abbreviated to fit the space available.

Figure 2. SARA-2 TXC-05551 Lead Diagram

# **LEAD DESCRIPTIONS**

# POWER SUPPLY, GROUND AND NO CONNECT LEADS

| Symbol  | Solder Ball No.                                                               | I/O/P * | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-------------------------------------------------------------------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD     | A3, F6, F7, F9, F10, G6,<br>G10, J6, J10, K6, K7,<br>K9, K10                  | Р       |      | $V_{DD}$ : +3.3 volt supply voltage, $\pm$ 5%                                                                                                                                                                                                                                                                                                                                                                                |

| VSS     | C9, F8, G7, G8, G9, H6,<br>H7, H8, H9, H10, J7, J8,<br>J9, J14, K8, P10       | Р       |      | V <sub>SS</sub> : Ground, 0 volt reference.                                                                                                                                                                                                                                                                                                                                                                                  |

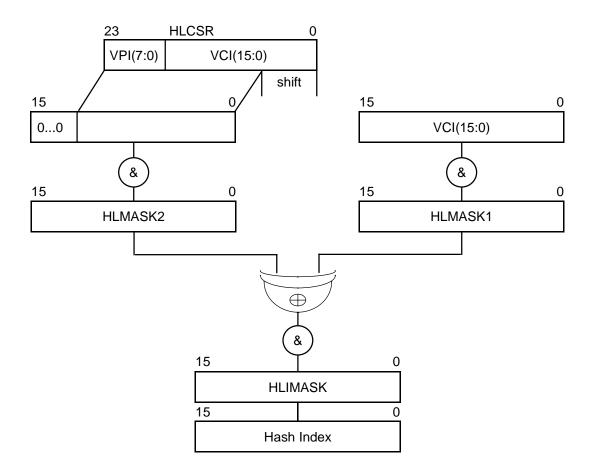

| PLLVDD  | C4                                                                            | Р       |      | <b>PLL <math>V_{DD}</math>:</b> RC-decoupled +3 volt supply voltage, for analog section $V_{DD}$ of device.                                                                                                                                                                                                                                                                                                                  |

| PLLAGND | В3                                                                            | Р       |      | <b>PLL AGND:</b> Ground, 0 volt reference, for analog section ground of device.                                                                                                                                                                                                                                                                                                                                              |

| PLLVSS  | A1                                                                            | Р       |      | <b>PLL V<sub>SS</sub>:</b> Ground, 0 volt reference, for analog section V <sub>SS</sub> of device.                                                                                                                                                                                                                                                                                                                           |

| NC      | A4, A5, C6, D6, E6, E7,<br>E8, F12, K1, L5, M1,<br>M3, M4, M11, P1, P8,<br>R1 |         |      | No Connect: NC leads are not to be connected, not even to another NC lead, but must be left floating. Connection of NC leads may impair performance or cause damage to the device. Some NC leads may be assigned functions for manufacturing test purposes or in future upgrades of the device. Backwards compatibility of the upgraded device in existing applications may rely upon these leads having been left floating. |

<sup>\*</sup>Note: I = Input; O = Output; P = Power; (T) = Tri-state

### **PCI INTERFACE**

| Symbol    | Solder Ball No.                                                                                                                                                     | I/O/P  | Type *          | Name/Function                                                                                                                                                                                                                                                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK    | P2                                                                                                                                                                  | I      | LVPCI-5         | <b>PCI Bus Clock:</b> Provides the timing for all transactions on the PCI bus. All other bus signals are sampled on the rising edge of this clock.                                                                                                                                                                                       |

| AD(31-0)  | R3, M5, N4, P4, L6,<br>R4, M6, N5, N6, M7,<br>P6, R6, L7, N7, P7,<br>R7, N10, R11, P11,<br>M10, N11, R12, L10,<br>P12, N12, P13, R14,<br>P14, N13, R15, N14,<br>P15 | I/O(T) | LVPCI-5/<br>PCI | Address/Data Bus: Bidirectional multiplexed Address and Data leads for the PCI bus. Each bus transaction consists of an address phase followed by one or more data phases. Address phases are identified when the control signal FRAME is asserted. Data is transferred during those clock cycles where both IRDY and TRDY are asserted. |

| C/BE(3-0) | P5<br>L8<br>R10<br>R13                                                                                                                                              | I/O(T) | LVPCI-5/<br>PCI | Command/Byte Enable: During the address phase of a transaction, these leads supply the bus command. During the data phase these leads are used as byte enables for each bus transaction.                                                                                                                                                 |

<sup>\*</sup>See the Input, Output and I/O Parameters section for Type descriptions.

| Symbol | Solder Ball No. | I/O/P  | Type *          | Name/Function                                                                                                                                                                                                                                                             |

|--------|-----------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAR    | L9              | I/O(T) | LVPCI-5/<br>PCI | Parity: Even parity across AD(31-0) and C/BE(3-0) during valid data and address phases. PAR is stable and valid one clock time after the completion of the data or address phase.                                                                                         |

| FRAME  | M8              | I/O(T) | LVPCI-5/<br>PCI | <b>Cycle Frame:</b> A falling edge indicates the beginning of a bus transaction with an address phase. A rising edge indicates that the next data phase marks the end of the current transaction.                                                                         |

| ĪRDY   | R8              | I/O(T) | LVPCI-5/<br>PCI | Initiator Ready: A low indicates the bus master's ability to complete the current data phase of the transaction. A valid data phase is completed on a clock edge when both $\overline{\text{IRDY}}$ and $\overline{\text{TRDY}}$ are sampled as asserted.                 |

| TRDY   | N8              | I/O(T) | LVPCI-5/<br>PCI | Target Ready: A low indicates the target's ability to complete the current data phase of the transaction. A valid data phase is completed on a clock edge when both $\overline{\text{IRDY}}$ and $\overline{\text{TRDY}}$ are sampled as asserted.                        |

| STOP   | R9              | I/O(T) | LVPCI-5/<br>PCI | <b>Stop:</b> Driven low by the current target to request the master to abort, disconnect or retry the current transaction.                                                                                                                                                |

| IDSEL  | R5              | I      | LVPCI-5         | Initialization Device Select: Used as a chip select to select SARA-2 during configuration read and write transactions.                                                                                                                                                    |

| DEVSEL | М9              | I/O(T) | LVPCI-5/<br>PCI | <b>Device Select:</b> When actively driven low, indicates the driving device has decoded the address placed on AD(31-0) as a valid reference to the target's address space. When SARA-2 acts as a bus target, this signal is held asserted low until FRAME is deasserted. |

| REQ    | P3              | O(T)   | PCI             | <b>Request:</b> Asserted low by SARA-2 to request control of the bus.                                                                                                                                                                                                     |

| GNT    | R2              | I      | LVPCI-5         | <b>Grant:</b> The PCI bus arbiter asserts this signal low to indicate to SARA-2 that it has been granted control of the PCI bus and may begin a new transaction after the current transaction has completed.                                                              |

| ĪNT    | N2              | OD     | PCI             | Interrupt: This active low signal is used by SARA-2 to signal an interrupt request. This lead must be connected to the INTA line on the PCI bus.                                                                                                                          |

| PERR   | P9              | I/O(T) | LVPCI-5/<br>PCI | Parity Error: This active low signal indicates a parity error on the 36 AD(31-0) and C/BE(3-0) lines.                                                                                                                                                                     |

| SERR   | N9              | OD     | PCI             | <b>System Error</b> : A low indicates that a parity error has occurred on the 36 AD(31-0) and C/BE(3-0) lines during the address phase.                                                                                                                                   |

| RESET  | N3              | I      | LVPCI-5         | <b>Reset:</b> This lead, when driven low for a minimum of 64 system clock cycles, will reset all state machines in the device.                                                                                                                                            |

# PARALLEL LINE INTERFACE

| Symbol                         | Solder<br>Ball No.                      | I/O/P | Туре           | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|-----------------------------------------|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxCLK                          | C2                                      | I     | LVTTL-5        | Receive Input Clock: Receive clock input used to write data into SARA-2.  Framer Mode: Byte-wide data RxData(7-0) is clocked in on the rising edge of this clock whose rate is either 6.48 MHz (STS-1), or 19.44 MHz (STS-3c/STM-1), when control bit RCS in Mode Register 2 is a 0. When control bit RCS is a 1, data is clocked in on the falling edge.                                                                                                                                                                                                                                                                                                           |

| RxData(7-0)                    | E4, E3,<br>D1, E5,<br>E2, F5,<br>E1, F4 | I     | LVTTL-5        | Receive Input Data Bus: <u>UTOPIA Mode:</u> The input data bus carries the ATM cell octets that are written into SARA-2. RxData(7-0) is sampled on the rising edge of RxCLK. <u>Framer Mode</u> : Byte-wide data. The data present on RxData7 is the MSB and the first bit received in the SDH/SONET format. RxData0 is the LSB and the last bit received in the byte.                                                                                                                                                                                                                                                                                              |

| RxPAR                          | D2                                      | I     | LVTTL-5        | <b>Receive Input Data Parity</b> : This line serves as the odd parity bit over RxData(7-0). Used only in the UTOPIA mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RxSOC                          | C1                                      | I     | LVTTL-5        | Receive Input Start of Cell: Used in the UTOPIA mode, the cell input start of cell signal marks the first byte of a cell. RxSOC is sampled on the rising edge of RxCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RXEMPTY /<br>RXCLAV /<br>RXENB | D3                                      | I     | LVTTL-5        | UTOPIA-ATM Octet Handshake Mode: Receive Buffer Empty: In this mode, the external device should assert this signal low if its receive buffer is empty and no more data can be transferred. It is sampled on the rising edge of RxCLK. UTOPIA-ATM Cell Handshake Mode: Cell Available Signal: In this mode, the external device should assert this signal high if it has at least one complete cell to send. UTOPIA-PHY Mode: Enable Signal: In this mode (both octet and cell level), the lead acts as an enable signal for the data transfer. The external device should assert this signal low to indicate valid data on the RxData(7-0), RxSOC and RxPAR inputs. |

| RXENB /<br>RXFULL /<br>RXCLAV  | H3                                      | 0     | LVTTL-5<br>4mA | UTOPIA-ATM Mode: Receive Enable Signal: In this mode (both octet and cell level), the lead acts as an enable signal for the data transfer. Driven low by the SARA-2 to indicate that it is ready to receive data on the RxData(7-0), RxSOC and RxPAR inputs. UTOPIA-PHY Octet Handshake Mode: Receive Buffer Full: In this mode, the SARA-2 asserts this signal low if its receive buffer can accept at most 4 bytes. UTOPIA-PHY Cell Handshake Mode: Cell Available Signal: In this mode, the SARA-2 asserts this signal high if it can accept a complete cell.                                                                                                    |

| Symbol                        | Solder<br>Ball No.                      | I/O/P | Туре           | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|-----------------------------------------|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxCLK                         | C3                                      | I     | LVTTL-5        | Transmit Clock Input: Transmit clock input used to read data from SARA-2. Data is output on the rising edge of this clock. Eramer Mode: Byte-wide data TxData(7-0) is clocked out on the rising edge of this clock whose rate is either 6.48 MHz (STS-1), or 19.44 MHz (STS-3c/STM-1), when control bit TCS in Mode Register 2 is a 0. When control bit TCS is a 1, data is clocked out on the falling edge.                                                                                                                                                                                                                                                                                                                                 |

| TxData(7-0)                   | F3, F2,<br>F1, G4,<br>G3, G5,<br>G1, G2 | O(T)  | LVTTL-5<br>4mA | Transmit Output Data:  UTOPIA Mode The cell output data bus carries the ATM cell octets that are read from SARA-2. TxData(7-0) is output on the rising edge of TxCLK.  Eramer Mode Byte-wide data. The data present on TxData7 is the MSB and the first bit transmitted in the SDH/SONET format. TxData0 is the LSB and the last bit transmitted in the byte. See Note 1.                                                                                                                                                                                                                                                                                                                                                                    |

| TxPAR                         | H5                                      | O(T)  | LVTTL-5<br>4mA | <b>Transmit Output Data Parity</b> : This line serves as the odd parity bit over TxData(7-0). Used only in the UTOPIA mode. See Note 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TxSOC                         | H4                                      | O(T)  | LVTTL-5<br>4mA | Transmit Output Start of Cell: In UTOPIA mode, this signal marks the first byte of a data transfer. This signal is asserted high during the first byte of a 53-byte cell. See Note 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TxFULL /<br>TxCLAV /<br>TxENB | B1                                      | I     | LVTTL-5        | UTOPIA-ATM Octet Handshake Mode: Transmit Output Buffer Full: In this mode, the external device should assert this signal low to indicate that it can accept at most 4 bytes.  UTOPIA-ATM Cell Handshake Mode: Cell Available Signal: In this mode, the external device should assert this signal high to indicate that it can accept a full cell.  UTOPIA-PHY Mode: Transmit Enable Signal: In this mode (both octet and cell level), the lead acts as an enable signal for the data transfer. It should be driven low by the external device to indicate that it is ready to accept the TxData(7-0), TxSOC and TxPAR outputs. This lead may also be set high to place the TxData(7-0), TxPAR and TxSOC outputs in the tri-state condition. |

Note 1: These leads are tri-stated for PHY layer operation when TXENB is deactivated. They are not tri-stated during ATM layer operation.

| Symbol                         | Solder<br>Ball No. | I/O/P | Туре           | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|--------------------|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXENB /<br>TXEMPTY /<br>TXCLAV | H1                 | 0     | LVTTL-5<br>4mA | UTOPIA-ATM Mode: Transmit Enable Signal: In this mode (both octet and cell level), this signal is asserted low by SARA-2 whenever valid data has been placed on the TxData(7-0), TxSOC and TxPAR leads. UTOPIA-PHY Octet Handshake Mode: Transmit FIFO Empty: In this mode, the SARA-2 asserts this signal low if its transmit buffer is empty and no more data can be sent. UTOPIA-PHY Cell Handshake Mode: Cell Available Signal: In this mode, the SARA-2 asserts this signal high if it can send a complete cell. |

| UTOP/FMR                       | L2                 | I     | LVTTL-5p       | Utopia / Framer Mode Select: Set high for UTOPIA mode, low for Framer mode.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LICLK                          | B2                 | 0     | LVTTL-5<br>4mA | Line Interface Clock: This asymmetric clock is an output clock derived from SYSCLK and may be used to drive the line interface clock input of external devices. The frequency is two-fifths the frequency of SYSCLK.                                                                                                                                                                                                                                                                                                  |

# **SERIAL LINE INTERFACE**

| Symbol | Solder<br>Ball No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                |

|--------|--------------------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxSCTI | J5                 | I     | PECL    | Receive Serial Clock True Input: (pseudo-ECL Level). True and complementary data are clocked in on the rising edge of this clock whose rate is either 51.84 MHz (STS-1), or 155.52 MHz (STS-3c/STM-1).                                                                                                                       |

| RxSCCI | J2                 | I     | PECL    | Receive Serial Clock Complement Input: This lead, with its complement RxSCTI, is the input clock that accompanies the data on RxSDT and RxSDC.                                                                                                                                                                               |

| RxSDT  | J3                 | I     | PECL    | <b>Receive Serial Data True:</b> This lead, with its complement RxSDC, is the input data to SARA-2.                                                                                                                                                                                                                          |

| RxSDC  | J1                 | I     | PECL    | Receive Serial Data Complement: This lead, with its complement RxSDT, is the input data to SARA-2.                                                                                                                                                                                                                           |

| RxLOS  | K5                 | I     | LVTTL-5 | Receive Loss Of Signal In. An external active low signal from upstream circuitry that indicates a loss of signal condition. This signal is reported as a loss of signal alarm indication.                                                                                                                                    |

| TxRCTI | J4                 | ı     | PECL    | <b>Transmit Serial Reference Clock True Input:</b> (pseudo-ECL Level). This lead, with its complement TxRCCI, is used to derive the transmit output clock, and to synchronize the transmit data. The clock rate is either 51.84 MHz (STS-1), or 155.52 MHz (STS-3c/STM-1). The retimed clock is output on TxSCTO and TxSCCO. |

| Symbol | Solder<br>Ball No. | I/O/P | Туре           | Name/Function                                                                                                                                                                                                                                                                                                               |

|--------|--------------------|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxRCCI | H2                 | I     | PECL           | Transmit Serial Reference Clock Complement Input: (pseudo-ECL Level). This lead, with its complement TxRCTI, is used to derive the transmit output clock, and to synchronize the transmit data. The clock rate is either 51.84 MHz (STS-1), or 155.52 MHz (STS-3c/STM-1). The retimed clock is output on TxSCCO and TxSCTO. |

| TxSCTO | K4                 | 0     | PECL<br>50 ohm | Transmit Serial Clock True Output: (pseudo-ECL Level). This lead, with its complement TxSCCO, clocks out data on the rising edge of this clock whose rate is either 51.84 MHz (STS-1), or 155.52 MHz (STS-3c/STM-1). This clock is derived from the transmit input clock TxRCTI.                                            |

| TxSCCO | L1                 | 0     | PECL<br>50 ohm | Transmit Serial Clock Complement Output: This lead, with its complement TxSCTO, is the retimed output of TxRCTI and TxRCCI.                                                                                                                                                                                                 |

| TxSDT  | K3                 | 0     | PECL<br>50 ohm | Transmit Serial Data True: This lead, with its complement TxSDC, is the output SONET/SDH data.                                                                                                                                                                                                                              |

| TxSDC  | K2                 | 0     | PECL<br>50 ohm | Transmit Serial Data Complement: This lead, with its complement TxSDT, is the output SONET/SDH data.                                                                                                                                                                                                                        |

### **CONTROL MEMORY INTERFACE**

| Symbol    | Solder Ball No.                                                                                                                                                                   | I/O/P | Туре                       | Name/Function                                                                                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CD(31-0)  | D14, C15, D13,<br>C14, B15, B14,<br>A15, C13, B13,<br>A14, D12, C12,<br>A13, D11, B12,<br>E10, A12, C11,<br>D10, B11, A11,<br>C10, B10, A10,<br>E9, B9, A9, D9,<br>C8, B8, A8, D8 | I/O   | LVTTL-5/<br>LVTTL-5<br>6mA | Control Memory Data Bus: Bidirectional data path to external control memory.                                                                                   |

| CA(17-2)  | M13, M14, N15,<br>L12, L13, M15,<br>L14, L11, K11, L15,<br>K12, K14, K13,<br>K15, J11, J13                                                                                        | 0     | LVTTL-5<br>6mA             | Control Memory Address Bus: Provides bits 17 through 2 of the 24-bit byte address to the external memory devices. In essence, this is the 32-bit word address. |

| CWBE(3-0) | F11, E14, E11, D15                                                                                                                                                                | 0     | LVTTL-5<br>6mA             | Control Memory Write Byte Enable: These active low signals are the byte enables during write operation for each of the four bytes of CD(31-0).                 |

| Symbol    | Solder Ball No.                                                | I/O/P | Туре           | Name/Function                                                                                                                                                                                                                                         |

|-----------|----------------------------------------------------------------|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMA(10-0) | J15, J12, H14,<br>H13, H15, H12,<br>H11, G14, G15,<br>G11, G13 | 0     | LVTTL-5<br>6mA | Multiplexed Control Memory Address Bus: These lines can present additional control memory address bits when SRAM is being accessed. The specific bits placed on the bus depend on the MXSEL bits. Please refer to the description of Mode Register 0. |

| CCS(3-0)  | G12,<br>F15,<br>F14,<br>F13                                    | 0     | LVTTL-5<br>6mA | <b>Control Memory Chip Select:</b> These active low signals select one of four memory banks and correspond to the bits 23 and 22 of the 24-bit physical byte address.                                                                                 |

| CRD       | E15                                                            | 0     | LVTTL-5<br>6mA | <b>Control Memory Read</b> : This active low lead provides the read signal to the external control memory.                                                                                                                                            |

| CWRT      | E13                                                            | 0     | LVTTL-5<br>6mA | Control Memory Write: This active low lead provides the write signal to the external control memory. The individual byte enable signals are provided by CWBE(3-0).                                                                                    |

| CRDY      | M12                                                            | I     | LVTTL-5        | <b>Control Memory Ready</b> : This input is not used and should be tied low.                                                                                                                                                                          |

| CMCLK     | E12                                                            | 0     | LVTTL-5<br>6mA | <b>Control Memory Clock Output:</b> This clock is a synthesized version of SYSCLK and is used for timing the control memory interface.                                                                                                                |

# **SERIAL EEPROM INTERFACE**

| Symbol | Solder<br>Ball No. | I/O/P | Туре                       | Name/Function                                                                                                   |

|--------|--------------------|-------|----------------------------|-----------------------------------------------------------------------------------------------------------------|

| EPS    | L3                 | I     | LVTTL-5p                   | <b>EEPROM Select:</b> This active low lead is used to select the external EEPROM for configuring PCI registers. |

| SCK    | L4                 | 0     | LVTTL-5<br>4mA             | Serial EEPROM Clock: This clock lead is used for the serial EEPROM interface.                                   |

| SCS    | N1                 | 0     | LVTTL-5<br>4mA             | Serial EEPROM Chip Select: Chip select lead for serial EEPROM interface.                                        |

| SDIO   | M2                 | I/O   | LVTTL-5/<br>LVTTL-5<br>4mA | Serial EEPROM Address Output/Data Input: Address and Data lead for the serial EEPROM interface.                 |

### **MISCELLANEOUS SIGNALS**

| Symbol  | Solder<br>Ball No. | I/O/P | Туре     | Name/Function                                                                                                                                                                                                                                               |  |  |  |

|---------|--------------------|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYSCLK  | D4                 | I     | LVTTL    | <b>System Clock:</b> This clock is used by the device to run the internal state machines and control memory interface. The SYSCLK clock rate must be between 21 MHz and 50 MHz and the duty cycle must be (50±10) %.                                        |  |  |  |

| ĪNTR    | B5                 | Ι     | LVTTL-5  | <b>Interrupt:</b> This active low signal enables an external device to interrupt the RISC processor within SARA-2.                                                                                                                                          |  |  |  |

| DEVHIZ  | B6                 | I     | LVTTL-5p | <b>Device High Impedance:</b> This asynchronous input lead, whe driven low, will place all of the SARA-2 output leads in a high impedance state, except for TDO, TxSCTO, TxSCCO, TxSDT TxSDC and VCOCTL.                                                    |  |  |  |

| VCOCTL  | A2                 | I/O   | LVCMOS   | VCO Control Voltage Lead: This is the VCO control voltage lead for connection to an external loop filter.                                                                                                                                                   |  |  |  |

| IDDTN   | C5                 | I     | LVTTL-5  | IDD Test Enable: This is an active high test lead for IDD. For normal operation it MUST be held low.                                                                                                                                                        |  |  |  |

| PLLTD   | B4                 | I     | LVTTL    | PLL ByPass Clock: Input clock bypassing PLL.                                                                                                                                                                                                                |  |  |  |

| PLLTSTN | D5                 | l     | LVTTL-5d | System Clock Selection: The clock from pin SYSCLK is selected if this pin is tied low. The clock from pin PLLTD is selected if this pin is tied high. If the system clock frequency is less than 50 MHz, this pin should be tied high for proper operation. |  |  |  |

# **BOUNDARY SCAN INTERFACE**

| Symbol | Solder<br>Ball No. | I/O/P | Туре           | Name/Function                                                                                                                                                                                                                                      |

|--------|--------------------|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK    | C7                 | I     | LVTTL-5        | <b>IEEE 1149.1 Test Access Port Serial Scan Clock:</b> This signal is used to shift data into TDI and out of TDO.                                                                                                                                  |

| TMS    | В7                 | I     | LVTTL-5p       | <b>IEEE 1149.1 Test Access Port Mode Select:</b> TMS is sampled on the rising edge of TCK, and is used to place the Test Access Port controller into various states as defined in IEEE 1149.1.                                                     |

| TDI    | A7                 | I     | LVTTL-5p       | <b>IEEE 1149.1 Test Access Port Serial Scan Data In:</b> Serial test instructions and data are clocked into this lead on the rising edge of TCK.                                                                                                   |

| TDO    | A6                 | O(T)  | LVTTL-5<br>4mA | IEEE 1149.1 Test Access Port Serial Scan Data Out: Serial test instructions and data are clocked out of this lead on the falling edge of TCK.                                                                                                      |

| TRES   | D7                 | I     | LVTTL-5p       | IEEE 1149.1 Test Access Port Reset Lead: This signal will asynchronously reset the Test Access Port (TAP) controller. Upon power-up, TRES must be set low then high; this will set the device into boundary scan bypass mode for normal operation. |

# ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS

| Parameter                               | Symbol         | Min  | Max                  | Unit   | Conditions                        |

|-----------------------------------------|----------------|------|----------------------|--------|-----------------------------------|

| Supply voltage                          | $V_{DD}$       | -0.3 | 3.9                  | V      | Note 1                            |

| DC input voltage                        | $V_{IN}$       | -0.5 | V <sub>DD</sub> +0.5 | V      | Note 1                            |

| Operating junction temperature          | $T_J$          |      | 125                  | °C     | Note 1                            |

| Storage temperature range               | T <sub>S</sub> | -40  | 125                  | °C     | Note 1                            |

| Ambient operating temperature           | T <sub>A</sub> | 0    | 70                   | °C     | 0 ft/min linear airflow           |

| Lead Temperature x Time                 | <u></u>        |      | 270 x 5              | °C x s |                                   |

| Moisture Expos <mark>ure Level \</mark> | ME             | 5    |                      | Level  | per EIA/JEDEC<br>JESD22-A112-A    |

| Relative Humidity, non-condensing       | RH             |      | 100                  | %      | Note 2                            |

| ESD Classification                      | ESD            |      | ±2000                | V      | per MIL-STD-883D<br>Method 3015.7 |

#### Notes:

- 1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

- 2. Pre-assembly storage in non-drypack conditions is not recommended or warranted.

### THERMAL CHARACTERISTICS

| Parameter                                  | Min | Тур_ | Max        | Unit | Test Conditions          |

|--------------------------------------------|-----|------|------------|------|--------------------------|

| Thermal Resistance:<br>junction to ambient |     |      | <b>2</b> 2 | °C/W | 0 ft/min linear airflow. |

# RECOMMENDED OPERATING CONDITIONS AND POWER REQUIREMENTS

| Parameter                          | Min  | Тур  | Max         | Unit | Test Conditions  |

|------------------------------------|------|------|-------------|------|------------------|

| $V_{DD}$                           | 3.15 | 3.30 | 3.45        | V    | K '              |

| I <sub>DD</sub>                    | FL   |      | <b>7</b> 20 | mA   |                  |

| Power dissipation, P <sub>DD</sub> |      |      | 2.5         | W    | Inputs Switching |

# **INPUT, OUTPUT AND I/O PARAMETERS**

# Input Parameters for LVCMOS (Low Voltage CMOS)

| Parameter             | Min                   | Тур | Max                   | Unit | Test Conditions               |

|-----------------------|-----------------------|-----|-----------------------|------|-------------------------------|

| V <sub>IH</sub>       | 0.7 * V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45 |

| V <sub>IL</sub>       | -0.5                  |     | 0.2 * V <sub>DD</sub> | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45 |

| Input leakage current | -10                   |     | 10                    | μΑ   | V <sub>DD</sub> = 3.45        |

| Input capacitance     |                       | 5   |                       | pF   |                               |

# Input Parameters for LVTTL (Low Voltage TTL)

| Parameter                            | Min | Тур | Max                   | Unit | Test Conditions               |

|--------------------------------------|-----|-----|-----------------------|------|-------------------------------|

| V <sub>IH</sub>                      | 2.0 |     | V <sub>DD</sub> + 0.3 | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45 |

| V <sub>IL</sub>                      |     |     | 0.8                   | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45 |

| Input leakage c <mark>urren</mark> t | -10 |     | 10                    | μΑ   | V <sub>DD</sub> = 3.45        |

| Input capacitance                    |     | 5   |                       | pF   |                               |

### Input Parameters for LVTTL-5 (Low Voltage TTL, 5 volt tolerant)

| Parameter             | Min | Тур | Max | Unit | Test Conditions                                    |

|-----------------------|-----|-----|-----|------|----------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     | 5.5 | V    | 3.15 <u>≤</u> V <sub>DD</sub> ≤ <mark>3.4</mark> 5 |

| V <sub>IL</sub>       |     |     | 0.8 | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45                      |

| Input leakage current | -10 |     | 10  | μΑ   | V <sub>DD</sub> = 3.45                             |

| Input capacitance     |     | 5   |     | pF   |                                                    |

# Input Parameters for LVTTL-5d (Low Voltage TTL, 5 volt tolerant with pull-down resistor)

| Parameter             | Min | Тур | Max   | Unit | Test Conditions                            |

|-----------------------|-----|-----|-------|------|--------------------------------------------|

| V <sub>IH</sub>       | 2.0 |     | 5.5   | V    | 3.15 <u>≤ V<sub>DD</sub> ≤ 3.45</u>        |

| V <sub>IL</sub>       |     |     | _0.8_ | V    | 3.15 <mark>≤ V<sub>DD</sub> ≤ 3.</mark> 45 |

| Input leakage current | 35  | 115 | 222   | μΑ   | $V_{DD} = 3.45; V_{IN} = V_{DD}$           |

| Input leakage current | DF  |     | 10    | μΑ   | $V_{IN} = V_{SS}$                          |

| Input capacitance     |     | 5   |       | pF   |                                            |

# Input Parameters for LVTTL-5p (Low Voltage TTL, 5 volt tolerant with pull-up resistor)

| Parameter             | Min | Тур  | Max  | Unit | Test Conditions                  |

|-----------------------|-----|------|------|------|----------------------------------|

| V <sub>IH</sub>       | 2.0 |      | 5.5  | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45    |

| V <sub>IL</sub>       |     |      | 0.8  | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45    |

| Input leakage current | -35 | -115 | -214 | μΑ   | $V_{DD} = 3.45; V_{IN} = V_{SS}$ |

| Input leakage current | R   |      | 10   | μΑ   | $V_{IN} = V_{DD}$                |

| Input capacitance     |     | 5    |      | pF   |                                  |

# Input Parameters for LVPCI-5 (Low Voltage PCI-compliant, 5 volt tolerant)

| Parameter             | Min                   | Тур | Max                   | Unit | Test Conditions                       |

|-----------------------|-----------------------|-----|-----------------------|------|---------------------------------------|

| V <sub>IH</sub>       | 0.5 * V <sub>DD</sub> |     | 5.5                   | V    | 3.15 ≤ V <sub>DD</sub> ≤ 3.45         |

| V <sub>IL</sub>       | -0.5                  |     | 0.3 * V <sub>DD</sub> | V    | <b>3</b> .15 ≤ V <sub>DD</sub> ≤ 3.45 |

| Input leakage current | -10                   | L   | 10                    | μΑ   | V <sub>DD</sub> = 3.45                |

| Input capacitance     |                       | 5   |                       | pF   |                                       |

# Input Parameters for PECL (Differential Input, Pseudo-ECL)

| Parameter                     | Min                     | Min Typ |                         | Unit | Test Conditions                                        |

|-------------------------------|-------------------------|---------|-------------------------|------|--------------------------------------------------------|

| V <sub>REF</sub>              |                         | 2.0     |                         | V    | Midpoint of V <sub>A</sub> and V <sub>AN</sub>         |

| V <sub>IH</sub>               | V <sub>REF</sub> + 0.05 |         |                         | V    | V <sub>A</sub> - V <sub>AN</sub> = 50 <mark>m</mark> V |

| V <sub>IL</sub>               |                         |         | V <sub>REF</sub> - 0.05 | V    | V <sub>A</sub> - V <sub>AN</sub> = 50 mV               |

| V <sub>CM</sub> (common mode) | TBD                     | TBD     | TBD                     | V    | TBD                                                    |

| I <sub>IL</sub>               | -10                     |         |                         | μΑ   | $V_{IN} = V_{CC}$                                      |

| I <sub>OH</sub>               |                         |         | 10                      | μΑ   | $V_{IN} = V_{SS}$                                      |

# Output Parameters for LVTTL-5 4mA (Low Voltage TTL, 5 volt tolerant, 4mA)

| Parameter       | Min | Тур      | Max      | Unit | Test Conditions                                |

|-----------------|-----|----------|----------|------|------------------------------------------------|

| V <sub>OH</sub> | 2.4 |          | $V_{DD}$ | V    | V <sub>DD</sub> = 3.15; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub> | 0   |          | 0.4      | V    | V <sub>DD</sub> = 3.15; I <sub>OL</sub> = -4.0 |

| I <sub>OL</sub> |     | <u>.</u> | 4.0      | mA   | $V_{OL} = 0.4$                                 |

| I <sub>OH</sub> |     |          | -4.0     | mA   | V <sub>OH</sub> = 2.4                          |

| I <sub>OZ</sub> | -10 |          | 10       | μΑ   |                                                |

# Output Parameters for LVTTL-5 6mA (Low Voltage TTL, 5 volt tolerant, 6mA)

| Parameter       | Min      | Тур      | Max             | Unit | Test Conditions                                |

|-----------------|----------|----------|-----------------|------|------------------------------------------------|

| V <sub>OH</sub> | 2.4      | 1        | V <sub>DD</sub> | V    | V <sub>DD</sub> = 3.15; I <sub>OH</sub> = -6.0 |

| V <sub>OL</sub> | 0        |          | 0.4             | V    | $V_{DD} = 3.15; I_{OL} = -6.0$                 |

| I <sub>OL</sub> | <b>U</b> | <u>.</u> | 6.0             | mA   | $V_{OL} = 0.4$                                 |

| I <sub>ОН</sub> |          |          | -6.0            | mA   | V <sub>OH</sub> = 2.4                          |

| I <sub>OZ</sub> | -10      |          | 10              | μΑ   |                                                |

# Output Parameters for PCI (PCI-compliant output at 6mA)

| Parameter       | Min                   | Тур | Max | Unit | Test Conditions                                |

|-----------------|-----------------------|-----|-----|------|------------------------------------------------|

| V <sub>OH</sub> | V <sub>DD</sub> - 0.5 |     |     | V    | V <sub>DD</sub> = 3.15; I <sub>OH</sub> = -4.0 |

| $V_{OL}$        |                       |     | 0.4 | V    | V <sub>DD</sub> = 3.15; I <sub>OL</sub> = 4.0  |

| I <sub>OL</sub> | RE                    |     | 12  | mA   | V <sub>OL</sub> = 0.4                          |

| I <sub>OH</sub> |                       |     | -12 | mA   | V <sub>OH</sub> = 2.4                          |

### Output Parameters for PECL 50 ohm (Differential Output, Pseudo-ECL, 50 ohms)

| Parameter       | Min  | Тур  | Max  | Unit | Test Conditions                                    |

|-----------------|------|------|------|------|----------------------------------------------------|

| V <sub>OH</sub> | 2.21 | 2.51 | 2.78 | V    | $R_T = 50 \text{ ohms}, VT = 1.7 V$                |

| V <sub>OL</sub> | 1.54 | 1.70 | 1.86 | V    | R <sub>T</sub> = <mark>50 o</mark> hms, VT = 1.7 V |

| I <sub>NN</sub> |      | 10   |      | μΑ   |                                                    |

| I <sub>ОН</sub> | ? E  | -16  |      | mA   | R <sub>T</sub> = 50 ohms, VT = 1.7 V               |

| V <sub>T</sub>  |      | 1.7  |      | V    | Termination Voltage                                |

### **OPERATION**

#### SEGMENTATION AND REASSEMBLY OVERVIEW